Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 407302

Авторы: Бабушкин, Братальский, Златников, Золотаревский, Катковска

Текст

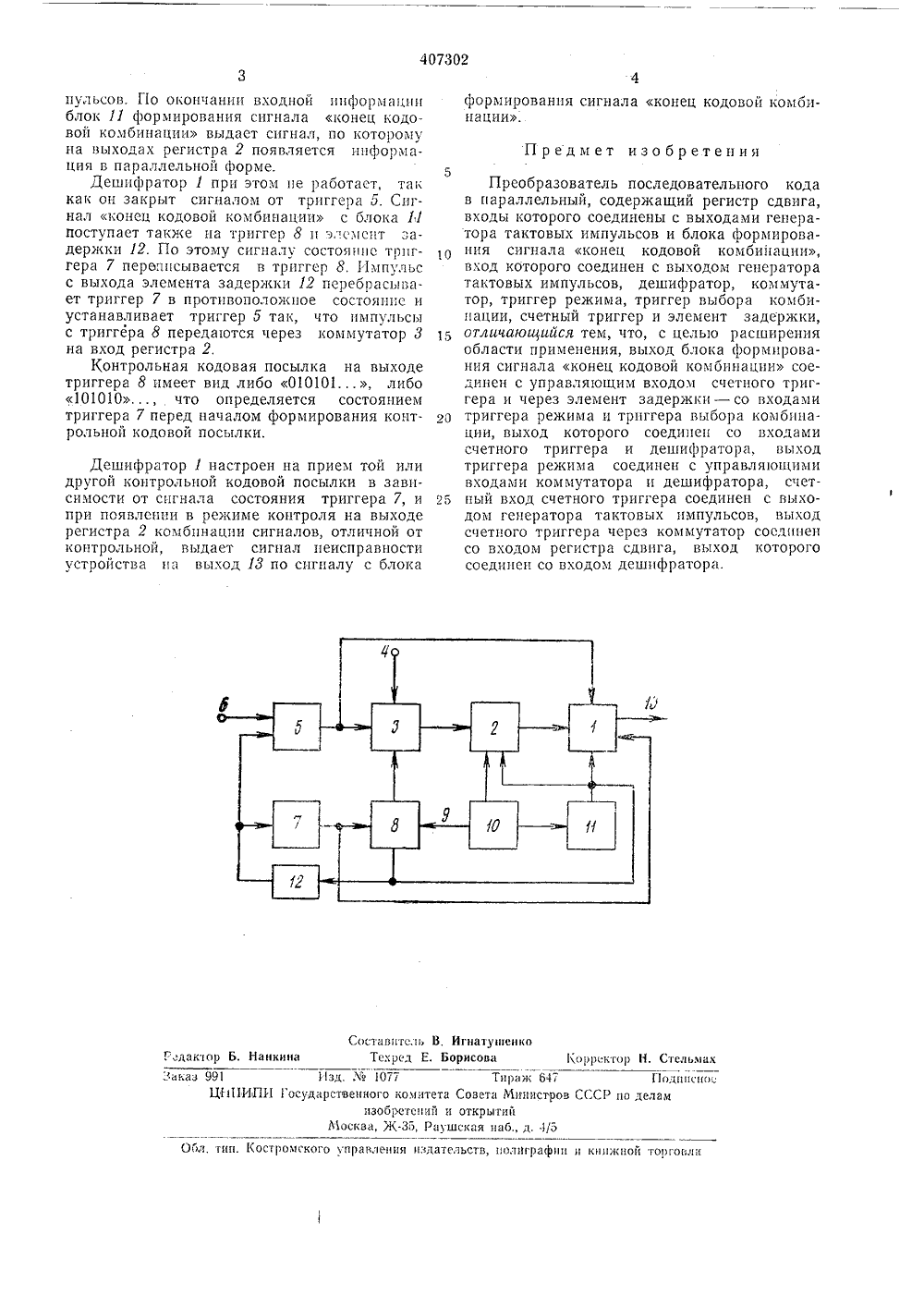

ОПИСАНИЕИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Реслублик407302 Зависц:ое от вт. свидетель.тва М -Заявлено 041972 (1733179/18-24) М.1;л. 6 061 5/04 с присоединением заявки М -Гасудврственна 1 й камитет Савете Министрав СССР аа делам иэааретений и аткратийЗаявитель ПРЕОБРАЗОВАТЕЛЬ ПОСЛ ЕДОВАТЕЛ Ь 10 ГО КОДА В ПАРАЛЛЕЛЬИЫЙИзооретецис Относите к ОЙ.аст Втох 1- тики ц вычислительной техники и предназначено для преобразования последовательных двоичных кодов в параллельные.Известны преобразователи последовательного кода в параллельный, содержащие регистр сдвига, генератор тактовых импульсов и блок формирования сигнала конец кодовой комбинации, вход которого соединен с Выходом генератора тактовых импульсов, дешифратор, коммутатор, триггер режима, триггер выбора комбинации, счетньш триггер и элемент задержки,Предложенный преобразователь отличается тем, что выход блока формирования сигнала коцсц кодовой комбинации соединен с управляющим входом счетного триггера и через элемент задержки - со входами триггера режима и триггера выбора комбинации, выход которого соединен со входами счетного триггера и дешцфратора; выход триггера режима соединен с управляющими входами коммутатора и дешифратора, счетный вход счетного триггера соединен с выходом генератора тактовых импульсов, выход счетного триггера через коммутатор соединен со входом регистра сдвига, выход которого соединен со входом дешифратора.Это позволяет расширить область применения устройства за счет возможности контроля его работоспособности ц использования его, таким образом, в системах с повышенными требованиям: к надежности функццоцпрогация.Схема устройства изображена на чертеже.Устройство содержит дешифратор 1 (длядешифрации контрольных состояний устройства), регистр сдвига 2, коммутатор 3 со входом 4 для подачи входной информации, триггер режима 5 со входом 6 для подачи сигнала начало сообщения, триггер 7 выбора комбинации, счетный триггер 8 со счетным входом 9, генератор 10 тактовых импульсов, блок 11 формирогания сигнала конец кодовой комбинации, эленент задержки 12 и контрольный Выход 13.Коммутатор 3 коммутирует информационный вход регистра сдвига 2 либо ца вход 4, через который на устройство передается пре О образуемый последовательный код, либо навыход счетного триггера 8, в зависимости от состояния триггера режима 5.Устройство работает следующим образом.При подаче сигнала начало сообщения 25 на вход 6 триггера 5 коммутатор 3 переключается на прием кодовой комбинации со входа 4, и информация пропускается на вход регистра сдвига 2. Импульсы входной информации запоминаются в регистре сдвига при по- ЗО мощи импульсов генератора 10 тактовых цм407302 Составитель В. Игнатушенко Тсхред Е. Борисова Корректор Н. Стельмах Р.дактор Б. Нанкина акал 991 1 вд, Ла 077 Тираж 647 Подписное ЦЫ 1 ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий Москва, Ж, Раушская наб., д. 15Обл. тип. Костромского управления ивдательств, полиграфии и книжной торговли пульсов. По окончании входной информацш блок 11 формирования сигнала конец кодовой комбинации выдает сигнал, по которому на выходах регистра 2 появляется информация в параллельной форме.Дешифратор 1 при этом не работаст, так как он закрыт сигналом от триггера 5. Сигнал конец кодовой комбинации с блока 11 поступает также на триггер 8 и элсасит задержки 12. По этому сигналу состояние триггера 7 переписывается в триггер 8. Импульс с выхода элемента задержки 12 перебрасывает триггер 7 в противоположное состояние и устанавливает триггер 5 так, что импульсы с триггера 8 передаотся через коммутатор 3 на вход регистра 2.Контрольная кодовая посылка на выходе триггера 8 имеет вид либо 010101, либо 101010, что определяется состоянием триггера 7 перед началом формирования контрольной кодовой посылки,Дешифратор 1 настроен на прием той или другой контрольной кодовой посылки в зависимости от сигнала состояния триггера 7, и при появлении в режиме контроля на выходе регистра 2 комбинации сигналов, отличной от контрольной, выдает сигнал неисправности устройства н выход 13 по сигналу с блока формирования сигнала конец кодовой комоинации. Предмет изобретения 5Преобразователь последовательного кодав параллельный, содержащий регистр сдвига, входы которого соединены с выходами генератора тактовых импульсов и блока формирования сигнала конец кодовой комбинации, вход которого соединен с выходом генератора тактовых импульсов, дешифратор, коммутатор, триггер режима, триггер выбора комбинации, счетный триггер и элемент задержки, отличающийся тем, что, с целью расширения области применения, выход блока формирования сигнала конец кодовой комбинации соединен с управляющим входом счетного триггера и через элемент задержки - со входами 20 триггера режима и триггера выбора комбинации, выход которого соединен со входами счетного триггера и дешифратора, выход триггера режима соединен с управляющими входами коммутатора и дешифратора, счет ный вход счетного триггера соединен с выходом генератора тактовых импульсов, выход счетного триггера через коммутатор соединен со входом регистра сдвига, выход которого соединен со входом дешифратор.

СмотретьЗаявка

1733179

О. Е. Бабушкин, Е. А. Братальский, В. М. Златников, Б. Л. Золотаревский, Е. Г. Катковска

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/2-407302-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кодов из остаточной системы счисления в полиадическую

Следующий патент: Устройство для сравнения чисел

Случайный патент: Устройство для защиты дискретных сигналов от помех