Устройство коррекции систематических ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1339496

Автор: Петрунин

Текст

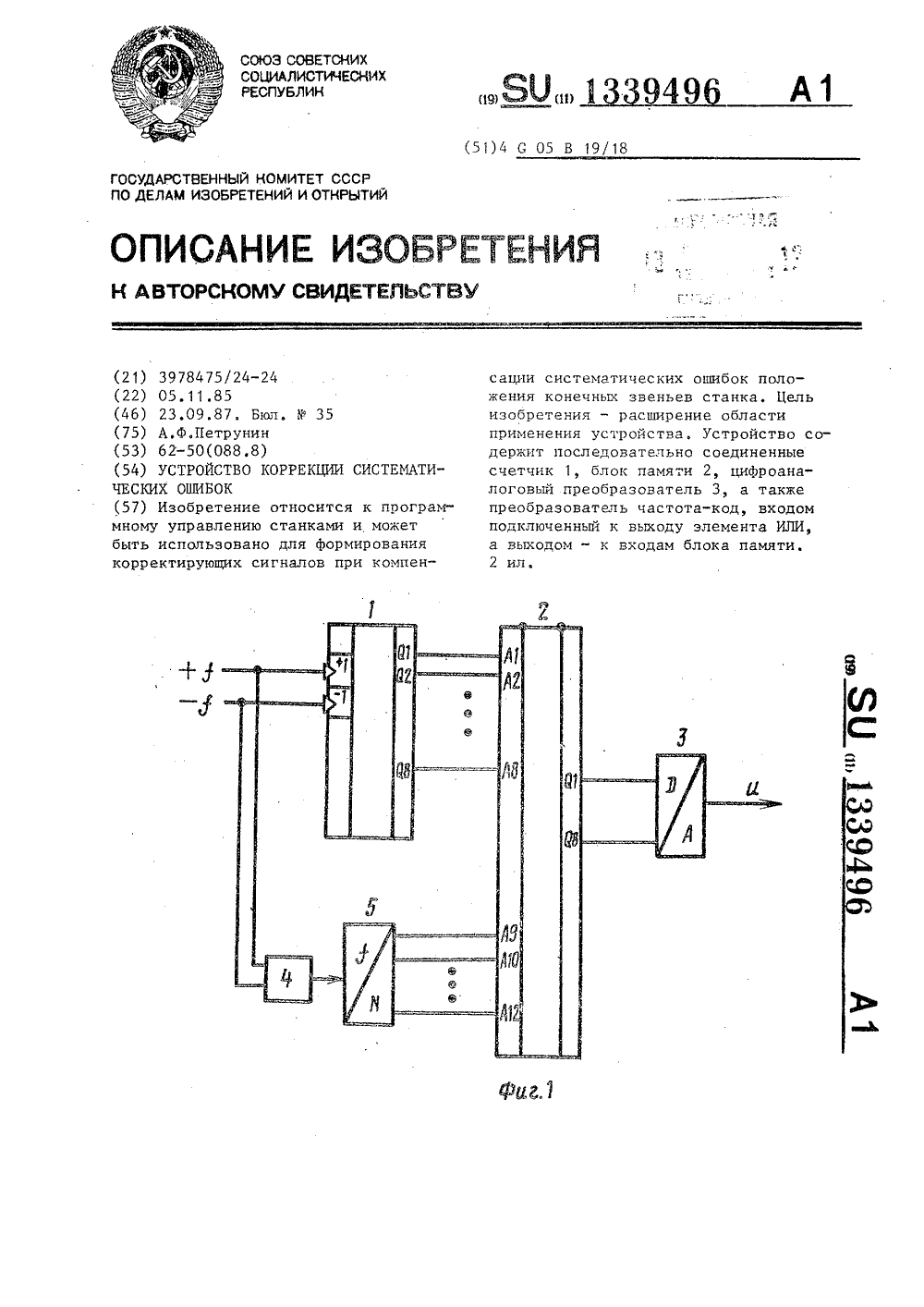

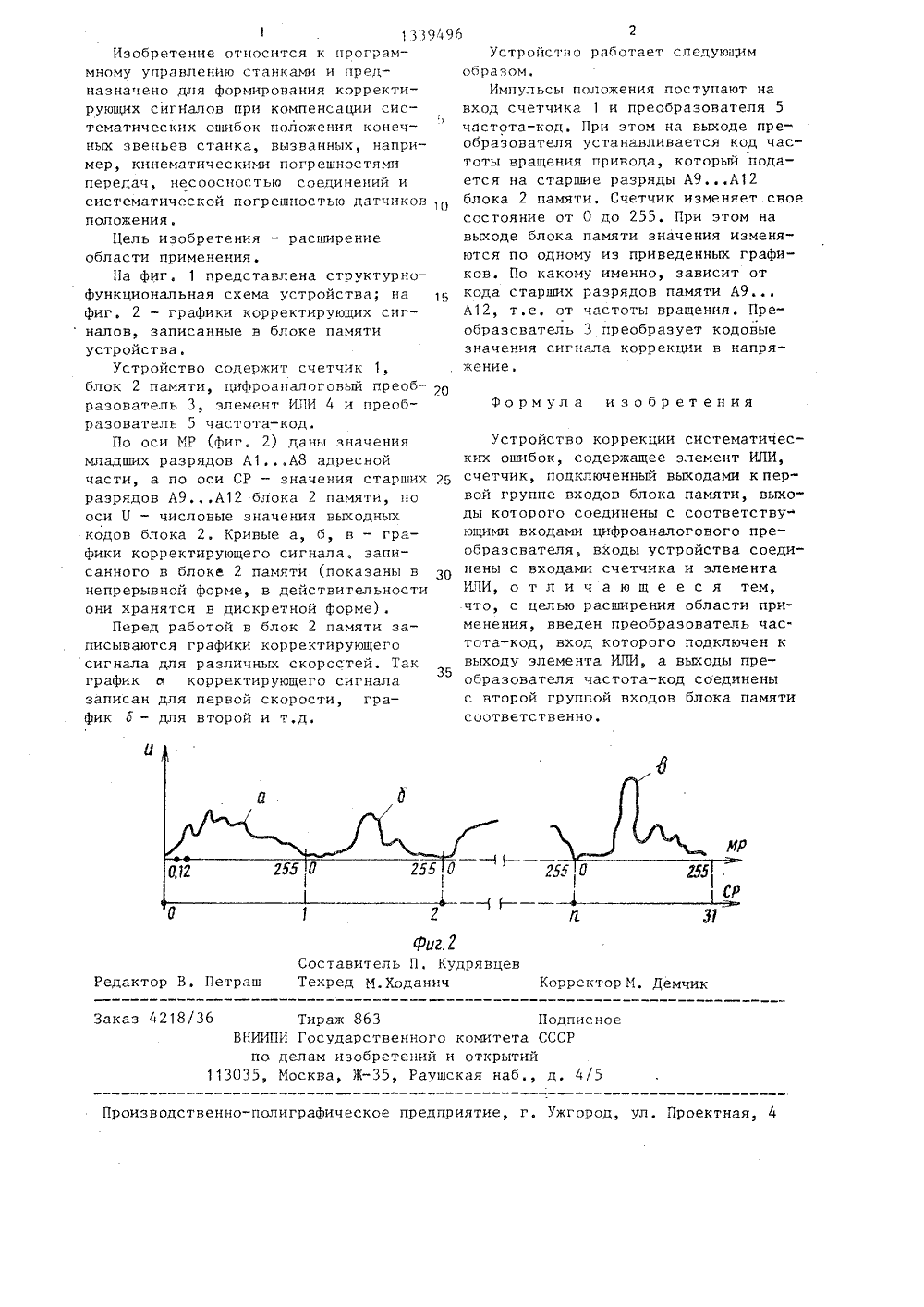

)4 С 05 В 19 дии ния оло к а. ел изобр приме ластиойство соиненные цифроанаа также ержи четч огов реоб одкл СИСТЕМА к програмвходом нта ИЛИ памяти. же вания пен СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИРЕСПУБЛИК ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(54) УСТРОЙСТВО КОРРЕКЦИИЧЕСКИХ ОШИБОК(57) Изобретение относитсямному управлению станками ибыть использовано для формикорректирующих сигналов при систематических оши конечных звеньев ста етения - расширение о нения устройства, Уст т последовательно сое ик 1, блок памяти 2, ый преобразователь 3, разователь частота-ко юченный к выходу элем ыходом - к входам блокаФормула изобретения соответственно. Р 55С Составитель П, КудрявцевТехред М.Ходанич едактор В, Пе рректор М. Демчик ш Заказ 4218/3 Тираж 863И Государстведелам изобретМосква, Ж,Подписнного комитета СССРний и открытийРаушская наб д, 4/5 113035 Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная,1 133949Изобретение относится к ирограммному управлению станками и предназначено для формирования корректирующих сигналов при компенсации сис) тематических ошибок положения конечных звеньев станка, вызванных, например, кинематическими погрешностямипередач, несоосностью соединений исистематической погрешностью датчиков 10положения.Цель изобретения - расширениеобласти применения,На фиг, 1 представлена структурнофункциональная схема устройства; на 15фиг. 2 - графики корректирующих сигналов, записанные в блоке памятиустройства,Устройство содержит счетчикблок 2 памяти, цифроаналоговый преобразователь 3, элемент ИЛИ 4 и преобразователь 5 частота-код.По оси МР (фиг, 2) даны значениямладших разрядов А 1 А 8 адреснойчасти, а по оси СР - значения старших 25разрядов А 9 А 12 блока 2 памяти, нооси П - числовые значения выходныхкодов блока 2. Кривые а, б, в - графики корректирующего сигнала, записанного в блоке 2 памяти (показаны внепрерывной форме, в действительностиони хранятся в дискретной форме).Перед работой в блок 2 памяти записываются графики корректирующегосигнала для различных скоростей. Так35график в корректирующего сигналазаписан для первой скорости, график Е - для второй и т,д. б 2Устройство работает следующим образом.Импульсы положения поступают на вход счетчика 1 и преобразователя 5 частота-код. При этом на выходе преобразователя устанавливается код частоты вращения привода, который подается на старшие разряды А 9 А 12 блока 2 памяти, Счетчик изменяет. свое состояние от 0 до 255, При этом на выходе блока памяти значения изменяются по одному из приведенных графиков. По какому именно, зависит от кода старших разрядов памяти А 9 А 12, т.е. от частоты вращения. Преобразователь 3 преобразует кодовые значения сигнала коррекции в напряжение,Устройство коррекции систематических ошибок, содержащее элемент ИЛИ, счетчик, подключенный выходами к первой группе входов блока памяти, выходы которого соединены с соответству" ющими входами цифроаналогового преобразователя, входы устройства соединены с входами счетчика и элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения, введен преобразователь час тота-код, вход которого подключен к выходу элемента ИЛИ, а выходы преобразователя частота-код соединены с второй группой входов блока памяти

СмотретьЗаявка

3978475, 05.11.1985

А. ФоПетрунин

ПЕТРУНИН АНАТОЛИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G05B 19/18, G05B 19/404

Метки: коррекции, ошибок, систематических

Опубликовано: 23.09.1987

Код ссылки

<a href="https://patents.su/2-1339496-ustrojjstvo-korrekcii-sistematicheskikh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство коррекции систематических ошибок</a>

Предыдущий патент: Устройство для управления нагружением при ресурсных испытаниях

Следующий патент: Устройство для управления шаговым двигателем

Случайный патент: Автоматический пресс для формовки торфовегетационных горшков