Потоковый параллельный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1608682

Автор: Александров

Текст

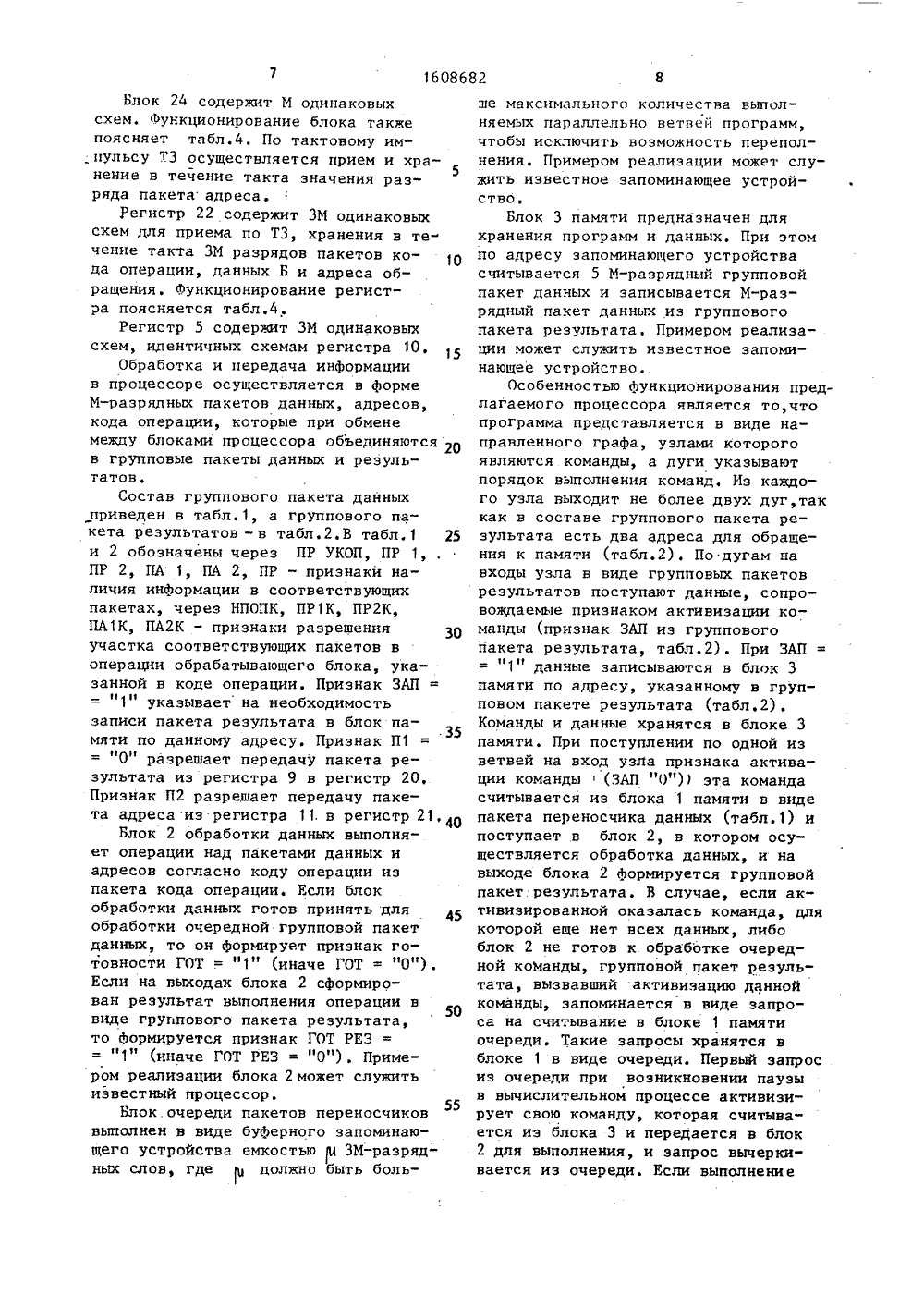

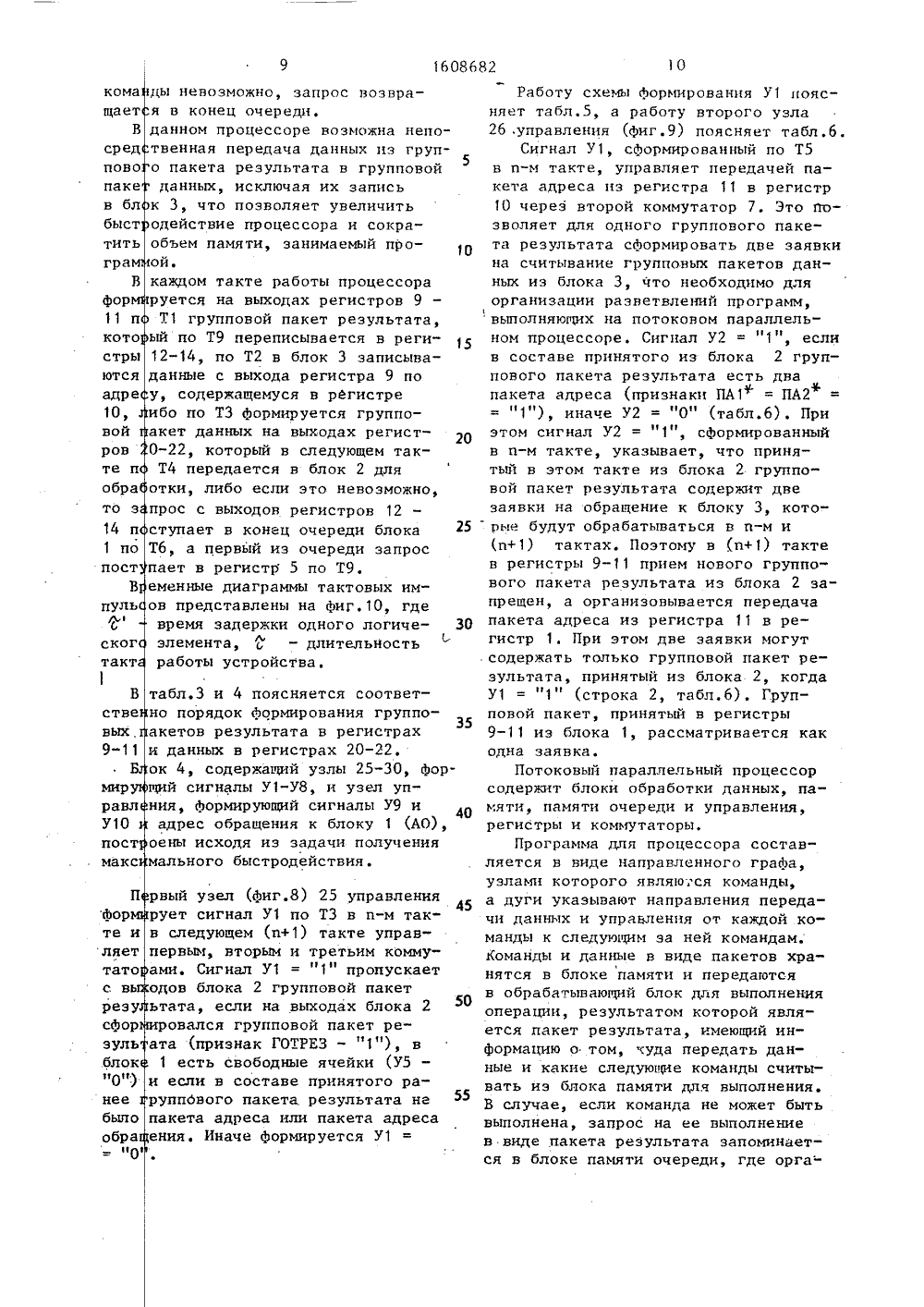

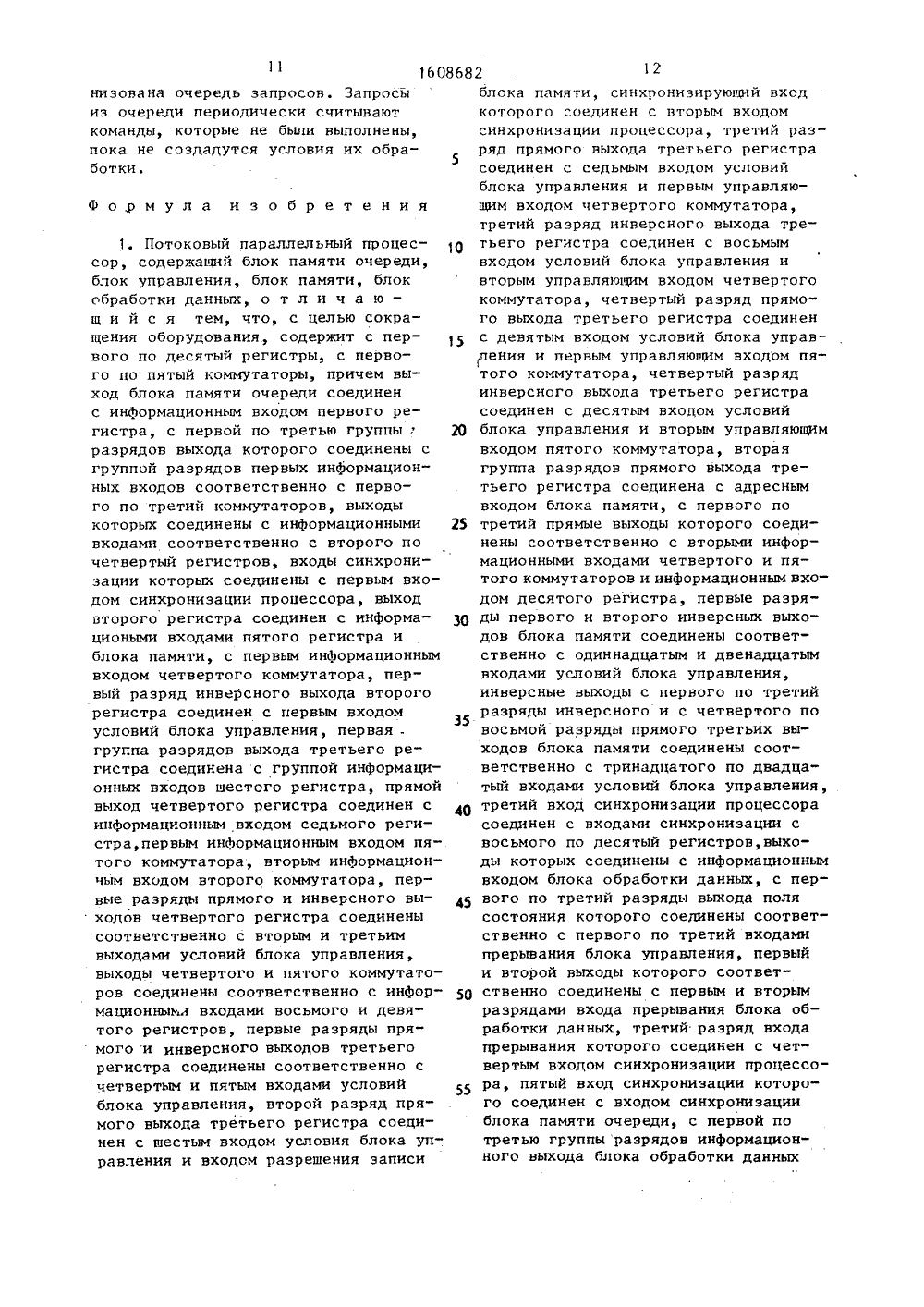

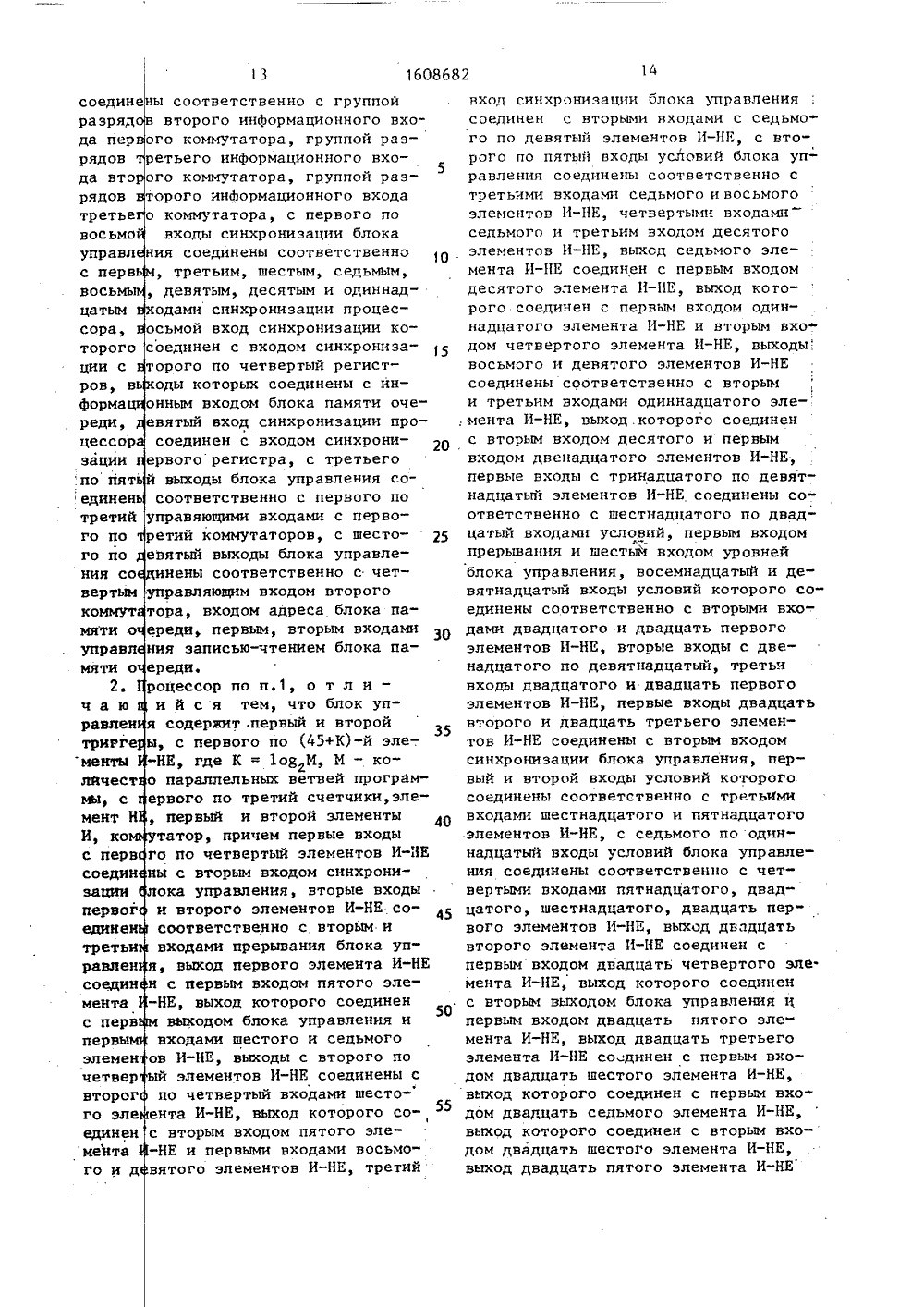

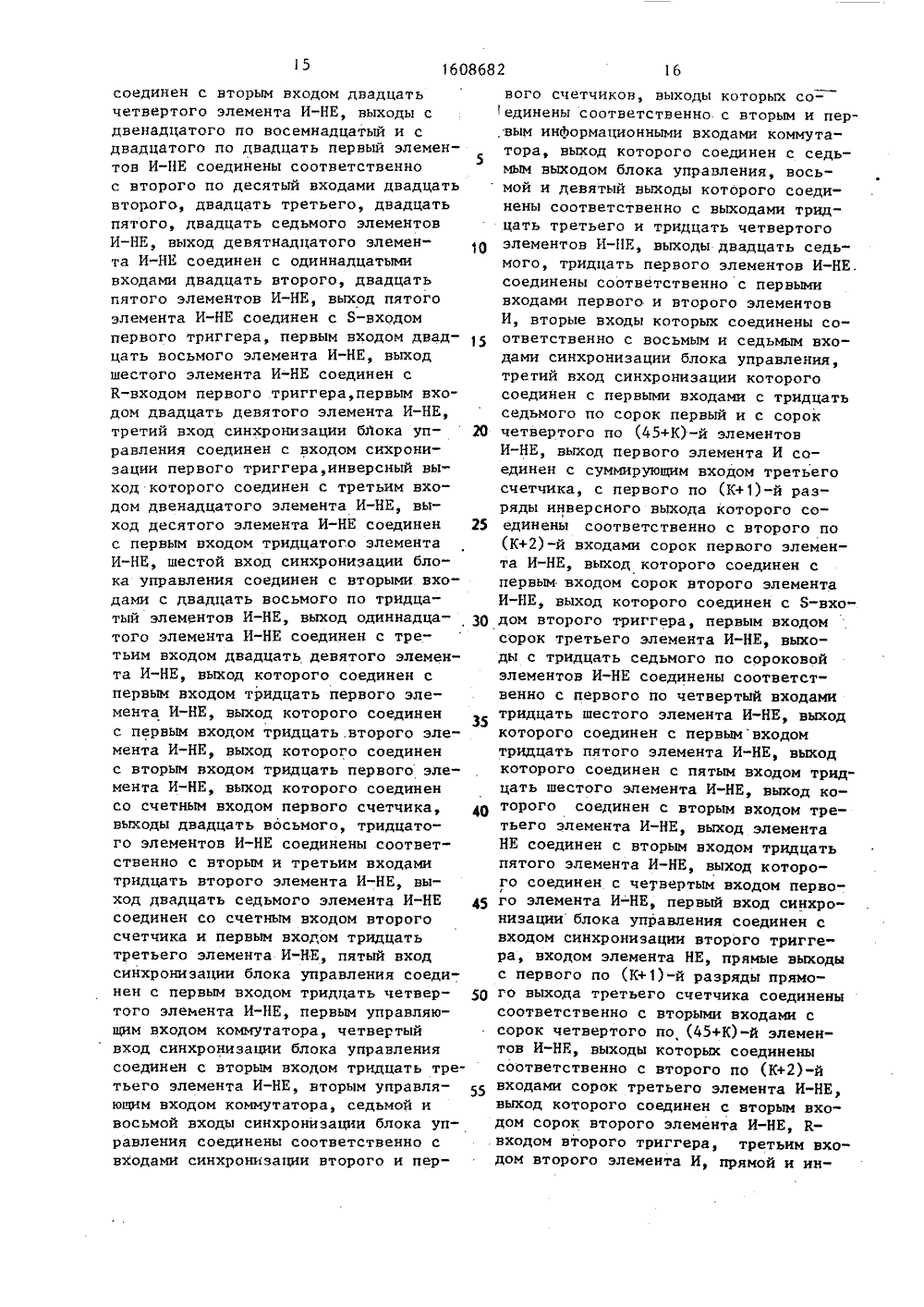

(51) (т .06 ( 15/00 ТВЕННЫЙ КОМИТЕТРЕТЕНИЯМ И ОТКРЫТИЯМТ СССР ГОСУД ПО ИЗО ПРИ ГН НАВ на потоков данных, проектив Массачусетском технологиченституте, с.233, рис.22.12.ислительная техника за рубе году. / Под ред. В,С.Бур., ИТМ и ВТ ьН СССР, 1981, труктура потоковой ЭВМ, с,50. ев М,А. Архитектура цифровых тельных машин. М,: Главная рефизико-математической литеразд-ва "Наука", 1978 .н Б.М. Электронные вычислимашины и системы, Учеб. поля вузов, 2-е изд. перераб. - М.; Энергоатомиздат, 1985. ОТОКОВ 11 Я ПАРАЛЛЕЛЬНЬЙ ПРОЦЕСзобре исли ОО г,1 предст схема пото На ф нальнаяИз бретенивмчис ительно авлена фукового па а фиг,2-9 на фиг,10 о лель- схема ного пр блока у ная диа сора,Проц 1 памят овано в темах вь испол ных с ностиЦ рудов проце ессора авления; амма син- време процесронизации ения - сокращение о лельного потокового ь изобрния парсора.(57)вой вь СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСНИХ Ф:.:-" РЕСПУБЛИК с ОРСКОМУ СВИДЕТЕЛЬСТВУ 3.11 713/24-24,И,Александров81. 3 (088. 8)рхитектура современных ЭВМ;с англ., Кн. 2, М,: Мир,ние относится к цифроельной технике и может относится к цифровой технике и может быть цифровых вычислитель сокой производитель 2 быть использовано в ЭВМ или в вычис= лительных системах высокой производительности. Целью изобретения является сокращение оборудования потокового процессора за счет исключения ассоциативного ЗУ, Процессор содержит блок обработки данных, блок памяти, блок памяти очереди, блок управления, десять регистров, пять коммутаторов, Для выполнения операции групповой пакет данных считывается из блока памяти и проверяется возможность выполнения операции в блоке обработки данных. Готовые к выполнению групповые пакеты передаются в блок обработки данных, где формируется групповой пакет результата. Пакет резуль- Е тата передается в блок памяти. Если пакет данных не был передан в блок обработки данных, то заявка на его С формирование в виде группового паке- та результата запоминается в блоке памяти очереди для того, чтобы повторить формирование группового пакета данных и его передачу в обрабатывающий блок. 1 з.п. ф-лы, 10 ил., 9 табл. ссор (фиг,1) содержит бло очереди, блок 2 обработк19 20Таблица 3 1 б 08 б 82 У 1 О О Значение управляющих сигналов 0 У 2 Порядок приема группового Пакета В резадан- гистрных 9 пакета результата, Нет приема В регистр10 адресаобращения Пакета адресаобращения Из ре- Из блокагистра 2 обра 11 ботки Из регистра5 Пакета адреса В регистр11 адреса Нет приема Т а б л и ц а 4 Порядок приема пакетаданныхА в регистр 20 П 2 Из блока3 памятиИз регистра 11 Из блока 3памяти Из блока 3памятиИз регистра 9 Таблица 5 Г Входы1 Ь 08682г.д ПА ад гмУГ П пдги1608 Б 82 Фаг Составитель А.СошкиРедактор Н.Тупица Техред М.дидик ектор М,шар 618 исное осуда нно-издательский комбинат "Патент", г. Ужгород, ул. Гагарин роизвод ЗаказВНИИПИ Тираж 565 Подтвенного комитета по изобретен 113035, Иосква, Ж, Раушска и открытиям при ГКНТ СС6., д. 4/51608682 У 9 = У 6 ЛТ 8,адрес обращения (АО) к блоку 1 для записи в конце очереди сопровождается сигналом У 10 = У 4 ЛТ 8 У 10 = У 4 Ь Т. данных, блок 3 памяти, блок 4 управления, первый регистр 5, с первого 6 по третий 8 коммутаторы, с второго 9 по седьмой 14 регистры, блок 15 пакета результата, блок 16 пакета адреса, блок 17 адреса, четвертый 18 и пятый 19 коммутаторы, с восьмого 20 по десятый 22 регистры, блок 23 пакета данных, блок 24 пакета адреса. 10Блок 4 управления (фиг.2) содержит с первого 25 по седьмой 31 узлы управления и пину 32 входов синхронизации, при этом третий узел 27 управления блока управления содержит 15 (фиг.З) с двенадцатого 33 по двадцать седьмой 48 элементы И-НЕ, пятый узел управления (фиг.4) содержит первый триггер 49, шестой узел управления (фиг.5) содержит элементы И-НЕ с двад 20 цать восьмого 50 по тридцать второй 54, седьмой узел управления (фиг,б) содержит первый 55 и второй 56 К-разрядные суммирующие счетчики, коммутатор 57, тридцать третий 58 и трид цать четвертый 59 элементы И-НЕ, четвертый узел управления (Фиг.7) содержит первый 60 и второй 61 элементы И, реверсивный (К+1)-разрядный третий счетчик 62, с тридцать седьмого 63 по сороковой 66 элементы И-НЕ, элемент НЕ 67, сорок первый элемент И-НЕ 68, элементы И-НЕ 69.1-69.К+1, тридцать пятый 70, тридцать шестой 711 сорок второй 72 сорок третий 73 35 элементы И-НЕ, второй триггер 74, первый узел управления (фиг.8) содержит с первого 75 по шестой 80 элементы И-НЕ, второй узел управления (фиг.9) содержит с седьмого 81 по 40 одиннадцатый 85 элементы И-НЕ.Рассмотрим некоторые особенности формирования управляющих сигналов.Управляющие сигналы УЗ и У 4 формируются в блоке 3 в и-м такте по так товому импульсу ТЗ, как указано в табл.8, и в следующем (и+1) такте управляют передачей информации из регистров 20-22 в блок 2 или блок 1. Сигнал УЗ - "1" разрешает передачу группового пакета данных в блок 2, если выполнены условия: состав группового пакета соответствует заданному (строки 1-27, табл.), при этом учитывается , с какого направленияУ 55 принимаются пакеты данных А и адреса (строки 2, 3 и 7, 8, табл.7) в соответствии с признаками П 1 и П 2 из пакета. адреса обращения; блок 2 готов к приему информации (ГОТ = 1), вданном (и+1) такте принята в регистры 20-22 новая информация из блока3 (ЗАП = "0") или из блока 1, ко гдаочередь пакетов не пуста (У 2 = Уб= У 7 = "0") . Если в данном (и+ 1) такте не было передачи группового пакетаданных в блок 2, то запрос на егоформирование заносится на конец оче-,реди в форме группового пакета результата в блоке очереди пакетов4переносчиков по сигналу У 4 = "1",кроме случая, если в данном тактебыла запись пакета результата в блок3 (строка 16, табл.7),Сигнал У 7, сформированный в пятом узле по Т 5 в и-м такте, как указано в табл.8, сохраняет в следующем(и+1) такте значение сигнала У 1,Сигнал У 8 = "1", сформированныйпо Т 9 в шестом узле в и-м такте(табл.9), указывает в (и+1) такте,чтов и-м такте работы устройства былпринят групповой пакет результата изблока 1 очереди пакетов переносчиков.Обращение к блоку 1 производитсядва раза за такт работы устройствапо тактовому импульсу Тб для записии считывания согласно У 9 и У 10 (управляющие входы записи и считыванияблока 1 являются инверсными).При наличии в блоке 11 очередипакетов на выходе коммутатора 57формируется в каждом такте работыустройства адрес обращения (АО) кблоку 1 для считывания информации изначала очереди и сопровождается сигналом На выходах первого счетчика Формируется текущий адрес первой ячейки, из которой в и-м такте будет считывание по У 9 = "0" группового пакета результата и передача его в регистр 5 по Т 9, Если в предыдущем (и) такте была передача группового пакета данных из регистра 5 в регистры5 60868 я его обработки в этом такте, -м такте по Т 11, поданному на низируюгдй вход первого счет адрес считывания будет уве- Э5 на единицу по сигналу У 8 = "1", ому на суммирующий вход первотчика. Таким образом, считываи-м такте будет производиться дующей ячейки блока 1, котоанет первой в очереди.и сформированный в (и) такповой пакет данных в и-м такбудет передан в блок 2 то заа его формирование будет зав конец очереди пакетов в 1 по адресу, сформированному на х второго советчика в и-м таки в и-м такте не было передаормации в блок 1, то в следую +1) такте запись будет произвов ту же ячейку. Если в и-м така передача информации в блок 1, том же и-м такте по управляющеналу У 4 = "1", поданному на 25 й вход второго счетчика, по ому импульсу Т 10, поданному хронизирующий вход второго счеадрес записи увеличится на у, указывая первую свободную блока 1 (конец очереди паке 9-11 то в синхрчика. ЛСС.).где С - значение 1-го разряда тре"тьего счетчика. Значение сигнала У 5формируется в каждом такте работыкоммутатора по Т 5 (по Т 1 устанавливается значение У 5 = "0"),Значение третьего счетчика указывает количество занятых ячеек .блока 1.При передаче информации регистров 12 -14 в блок 1 (У 4 = "1") на выходе элемента И 60 и по Т 11 формируется импульс, подаваемый на суммирующий входреверсивного третьего счетчика, Приприеме информации в регистр 5 из бло-ка (У 8 = "1") на выходе элемента И 61и по Т 10 формируется импульс, подаваемый на вычитающий вход реверсивного третьего счетчика. Если очередьпакетов в блоке 1 пуста (значение третьего счетчика равно "0"), то на выходе элемента И-НЕ 73 формируетсясигнал "0", подаваемый на вход элемента И 61 и запрещающий дальнейшеевычитание из третьего счетчика. Значе"ние сигналов на выходах элементовИ-НЕ, задержанные на один такт поТ 1, формируют управляющий сигнал Уб,запрещающий обработку запросов считанных из пустой очереди пакетов вблоке 1 (строка 14, табл.7). Такимобразом, сигнал Уб, задержанный наодин такт, формируется в соответствии с формулой личен подан го сч ние в из сл рая сЕ те гр те не явка несен блоке выход те. Е чи ин щем ( дитьс те бь то в му си счеты такто на си чика, едини ячейк тов),Дл полне фор111 пакет У 5Уб = С Ч С. Ч СзЧ ЧСЧ Ск.Необходимость задержки формирования сигнала Уб вызвана тем, что обработка заявки, передача сформированного пакета данных в блок 2 производится в следующем (и+1) такте работы устройства.Блок 15 (17) предназначен для приема ио Т 1 и для хранения М-разряд" ного пакета результата пакета адреса),содержит М одинаковых схем. Функционирование схемы поясняет табл.3.Блок 16 предназначен для приемаТ 1 и хранения М-разрядного пакета адреса обращения и содержит М одинаковых схем. Функционирование схемы также поясняет табл.3.Блок 23 содержит М одинаковых схем. По тактовому импульсу ТЗ блок принимает и хранит в течение такта значение разряда адреса, как указано в табл. 4. тельн пакет 40 дится в бло ков,осущевыпол14.боты 45 нят г рый м макси 50 до по бы ис форма свобо вие в 55,Л исключения возможности переия очереди пакетов в блоке 1 уется управляющий сигнал У 5запрещающий прием групповых в результатов из блока 2, При 1" осуществляется последовай перебор заявок из очереди в в блоке 1, пока не освободостаточное количество ячеек е 1 очереди пакетов переносчитакте работы коммутатора может твляться запись в очередь неенной заявки из регистров 12 роме того, в этом же такте рарегистры 9-11 может быть приупповой пакет результата, котожет быть рассмотрен как ещедве заявки. Таким образом, вления сигнала У 5 = "1", чтолючить возможность потери ини, надо иметь не менее трех ных ячеек в блоке 1. Это услоражается формулой кЧ(С к Л С Л С, Л . Ь С) Ч (С, Л СЛС,Л6 ЛС,)Ч(С А СЬС, АБлок 24 содержит М одинаковыхсхем. Функционирование блока такжепоясняет табл.4. По тактовому импульсу ТЗ осуществляется прием и хра 5нение в течение такта значения разряда пакета адреса.Регистр 22 содержит ЗМ одинаковыхсхем для приема по ТЗ, хранения в те"чение такта ЗМ разрядов пакетов кода операции, данных Б и адреса обращения. Функционирование регистра поясняется табл,4.Регистр 5 содержит ЗМ одинаковыхсхем, идентичных схемам регистра 10.Обработка и передача информациив процессоре осуществляется в формеМ-разрядных пакетов данных, адресов,кода операции, которые при обменемежду блоками процессора объединяются 2 Ов групповые пакеты данных и результатов,Состав группового пакета данныхприведен в табл,1, а группового пакета результатов - в табл,2,В табл, 1 25и 2 обозначены через ПР УКОП, ПР 1,ПР 2, ПА 1, ПА 2, НР - признаки наличия информации в соответствующихпакетах, через НПОПК, ПР 1 К, ПР 2 К,ПА 1 К, ПА 2 К - признаки разрешенияучастка соответствующих пакетов воперации обрабатывающего блока, указанной в коде операции. Признак ЗАП == "1" указывает на необходимостьзаписи пакета результата в блок памяти по данному адресу. Признак П 1= "О" разрешает передачу пакета результата из регистра 9 в регистр 20.Признак П 2 разрешает передачу пакета адреса из регистра 11. в регистр 21.40Блок 2 обработки данных выполняет операции над пакетами данных иадресов согласно коду операции изпакета кода операции. Если блокобработки данных готов принять для 45обработки очередной групповой пакетданных, то он формирует признак готовности ГОТ = "1" (иначе ГОТ = "О").Если на выходах блока 2 сформирован результат выполнения операции ввиде группового пакета результата,то формируется признак ГОТ РЕЗ= "1" (иначе ГОТ РЕЗ = "О"). Примером реализации блока 2 может служитьизвестный процессор.Блок. очереди пакетов переносчиков55выполнен в виде буферного запоминающего устройства емкостью р ЗМ-разрядных слов, где ц должно быть больше максимального количества выполняемых параллельно ветвей программ, чтобы исключить возможность переполнения. Примером реализации может служить известное запоминающее устройство.Блок 3 памяти предназначен для хранения программ и данных. При этом по адресу запоминающего устройства считывается 5 М-раэрядный групповой пакет данных и записывается М-разрядный пакет данных из группового пакета результата. Примером реализации может служить известное запоминающее устройство.Особенностью функционирования предлагаемого процессора является то,что программа представляется в виде направленного графа, узлами которого являются команды, а дуги указывают порядок выполнения команд, Из каждого узла выходит не более двух дуг,так как в составе группового пакета результата есть два адреса для обращения к памяти (табл.2), По дугам на входы узла в виде групповых пакетов результатов поступают данные, сопровождаемые признаком активизации команды (признак ЗАП из группового пакета результата, табл.2). При ЗАП = = "1" данные записываются в блок 3 памяти по адресу, указанному в групповом пакете результата (табл.2). Команды и данные хранятся в блоке 3 памяти, При поступлении по одной из ветвей на вход узла признака активации команды(ЗАП "О" эта команда считывается иэ блока 1 памяти в виде пакета переносчика данных (табл.1) и поступает в блок 2, в котором осуществляется обработка данных, и на выходе блока 2 формируется групповой пакет результата, В случае, если ак" тивизированной оказалась команда, для которой еще нет всех данных, либо блок 2 не готов к обработке очередной койанды, групповой пакет результата, вызвавший активизацию данной команды, запоминается в виде запроса на считывание в блоке 1 памяти очереди, Такие запросы хранятся в блоке 1 в виде очереди. Первый запрос из очереди при возникновении паузы в вычислительном процессе активизирует свою команду, которая считывается из блока 3 и передается в блок 2 для выполнения, и запрос вычеркивается из очереди. Если выполнениесред пово паке в бл быст тить грамВ фор 11 п кото стры ются адре10,вой ров те п обра то з 14 п 1 по пост Впуль /скогтакт 1В табл.З и 4 поясняется соответно порядок формирования группо 35акетов результата в регистрахи данных н регистрах 20-22,ок 4, содержащий узлы 25-30, форщий сигналы У 1-У 8, и узел упния, формирующий сигналы У 9 иадрес обращения к блоку 1 (АО),оены исходя из задачи получениямального быстродействия. стве вых.9-11Б мирравлУ 10 пост макс рвый узел (фиг.8) 25 управления рует сигнал У 1 по ТЗ в п-м такв следующем (и+1) такте управпервьм, нторым и третьим коммуами. Сигнал У 1 = "1" пропускает одон блока 2 групповой пакет ьтата, если на выходах блока 2 ровался групповой пакет реата (признак ГОТРЕЗ - "1"), н1 есть свободные ячейки (У 5 и если в составе принятого раруппбного пакета результата нг пакета адреса или пакета адреса ения. Иначе формируется У 1 П фор те и ляет тато с вь реэусфорзуль"0 ды невозможно, запрос возврая в конец очереди.данном процессоре возможна непотвенная передача данных из групо пакета результата н групповой5 данных, исключая их запись к 3, что позволяет увеличить одействие процессора и сокраобъем памяти, занимаемый проой.каждом такте работы процессора руется на выходах регистров 9 Т 1 групповой пакет результата, ый по Т 9 переписывается в реги-14, по Т 2 в блок 3 записываданные с выхода регистра 9 по у, содержащемуся в регистре ибо по ТЗ формируется группоакет данных на выходах регист-22, который в следующем такТ 4 передается н блок 2 для отки, либо если это невозможно, прос с выходов регистров 12 ступает в конец очереди блока Т 6, а первый из очереди запрос пает в регистр 5 по Т 9.еменные диаграммы тактовых имов представлены на фиг.10, где время задержки одного логиче элемента, "; - длительность работы устройстваРаботу схемы формирования У 1 поясняет табл.5, а работу второго узла 26,управления (фиг.9) поясняет табл,б.Сигнал У 1, сформированный по Т 5 в и-м такте, управляет передачей пакета адреса нз регистра 11 в регистр 10 через второй коммутатор 7. Это позволяет для одного группового пакета результата сформировать дне заявки на считывание групповых пакетов данных из блока 3, что необходимо для организации разветвлений программ, выполняющих на потоковом параллельном процессоре. Сигнал У 2 = "1", если н составе принятого из блока 2 группового пакета результата есть два пакета адреса (признаки ПА 1+ = ПА 2"1"), иначе У 2 = "0" (табл,6). При этом сигнал У 2 = "1", сформированный в и-м такте, указывает, что принятый в этом такте из блока 2 групповой пакет результата содержит дне заявки на обращение к блоку 3, которые будут обрабатываться в и-м и (и+1) тактах. Поэтому в (и+1) такте н регистры 9-11 прием нового группового пакета результата из блока 2 запрещен, а организовынается передача пакета адреса из регистра 11 в регистр 1. При этом две заявки могут содержать только групповой пакет результата, принятый из блока 2, когда У 1 = "1" (строка 2, табл.б). Групповой пакет, принятый н регистры 9-11 из блока 1, рассматривается как одна заявка.Потоковый параллельный процессор содержит блоки обработки данных, памяти, памяти очереди и управления, регистры и коммутаторы.Программа для процессора составляется в виде направленного графа, узлами которого являю;ся команды, а дуги указывают направления передачи данных и управления от каждой команды к следующим за ней командам. Команды и данные н виде пакетов хранятся в блоке памяти и передаются в обрабатывающий блок для выполнения операции, результатом которой является пакет результата, имеющий информацию о том, уда передать данные и какие следующие команды считывать иэ блока памяти для выполнения. В случае, если команда не может быть выполнена, запрос на ее выполнение в виде пакета результата запоминается н блоке памяти очереди, где орга 11 б 0868 низонана очередь запросов. Запросы из очереди периодически считывают команды, которые не были выполнены, пока не создадутся условия их обработки.5Формула изобретения. Потоковый параллельный процессор, содержащий блок памяти очереди, блок управления, блок памяти, блок обработки данных, о т л и ч а ю - щ и й с я тем, что, с целью сокращения оборудования, содержит с первого по десятый регистры, с первого по пятый коммутаторы, причем выход блока памяти очереди соединен с информационным входом первого регистра, с первой по третью группы; 20 разрядов выхода которого соединены с группой разрядов первых информационных входов соответственно с первого по третий коммутаторов, выходы которых соединены с информационными 25 входами соответственно с второго по четвертый регистров, входы синхронизации которых соединены с первым входом синхронизации процессора, выход второго регистра соединен с информа О циоными входами пятого регистра и блока памяти, с первым информационным входом четвертого коммутатора, первый разряд инверсного выхода второго регистра соединен с первым входом условий блока управления, первая .группа разрядов выхода третьего регистра соединена с группой информационных входов шестого регистра, прямой выход четвертого регистра соединен с информационным входом седьмого регистра, первым информационным входом пятого коммутатора, вторым информациончым входом второго коммутатора, первые разряды прямого и инверсного вы ходов четвертого регистра соединены соответственно с вторым и третьим выходами условий блока управления, выходы четвертого и пятого коммутаторов соединены соответственно с информационнымл входами восьмого и девятого регистров, первые разряды прямого и инверсного выходов третьего регистра соединены соответственно с четвертым и пятым входами условий блока управления, второй разряд прямого выхода третьего регистра соединен с шестым входом условия блока управления и входом разрешения записи 2 12блока памяти, синхронизирующий входкоторого соединен с вторым входомсинхронизации процессора, третий разряд прямого выхода третьего регистрасоединен с седьмым входом условийблока управления и первым управляющим входом четвертого коммутатора,третий разряд инверсного выхода третьего регистра соединен с восьмымвходом условий блока управления ивторым управляющим входом четвертогокоммутатора, четвертый разряд прямого выхода третьего регистра соединенс девятым входом условий блока управ 1ления и первым управляющим входом пятого коммутатора, четвертый разрядинверсного выхода третьего регистрасоединен с десятым входом условийблока управления и вторым управляющимвходом пятого коммутатора, втораягруппа разрядов прямого выхода третьего регистра соединена с адреснымвходом блока памяти, с первого потретий прямые выходы которого соединены соответственно с вторыми информационными входами четвертого и пятого коммутаторов и информационным входом десятого регистра, первые разряды первого и второго инверсных выходов блока памяти соединены соответственно с одиннадцатым и двенадцатымвходами условий блока управления,инверсные выходы с первого по третийразряды инверсного и с четвертого повосьмой разряды прямого третьих выходов блока памяти соединены соответственно с тринадцатого по двадцатый входами условий блока управления,третий вход синхронизации процессорасоединен с входами синхронизации свосьмого по десятый регистров,выходы которых соединены с информационнымвходом блока обработки данных, с первого по третий разряды выхода полясостояниИ которого соединены соответственно с первого по третий входамипрерывания блока управления, первыйи второй выходы которого соответственно соединены с первым и вторымразрядами входа прерывания блока обработки данных, третий разряд входапрерывания которого соединен с четвертым входом синхронизации процессора, пятый вход синхронизации которого соединен с входом синхронизацииблока памяти очереди, с первой потретью группы разрядов информационного выхода блока обработки данныхы соответственно с группой второго информационного вхосоединеразрядда перрядовда вторядовтретьевосьмо"управлс первьвосьмыцатымсора,торогоции сров, вьформацреди,цессорзации. по пятьединеньтретийго по ого коммутатора, группой разретьего информационного вхоого коммутатора, группой разторого информационного входао коммутатора, с первого повходы синхронизации блока ния соединены соответственно третьим, шестым, седьмым,девятым, десятым и одиннадодами синхронизации процес- осьмой вход синхронизации косоединен с входом синхронизаторого по четвертый регистоды которых соединены с инонным входом блока памяти очеевятый вход синхронизации просоединен с входом синхрониервогорегистра, с третьего й выходы блока управления сосоответственно с первого по управяющими входами с перноретий коммутаторов, с шестоевятый выходы блока управлеинены соответственно с четуправляющим входом второго тора, входом адреса блока паго пония совертымкоммутмяти оуправлмяти о2.чаюравлеитриргементылйчестмы, смент НИ, кос первсоединэациипервогединентретьиравленсоединментас первпервыэлеменчетвервторогго элеединенмеитаго и д ереди, первым, вторым входами ния записью-чтением блока паереди,роцессор по п.1, о т л и - и й с я тем, что блок упя содержит, первый и второй ы, с первого по (45+К)-й эле-.-НЕ, где К = 1 одМ, М - коо параллельных ветвей програмервого по третий счетчики,элепервый и второй элементытатор, причем первые входы го по четвертый элементов И-НЕны с вторым входом синхронилока управления, вторые входы н с первым входом пятого эле-НЕ, выход которого соединенвыходом блока управления ивходами шестого и седьмогоов И-НЕ, выходы с второго по ый элементов И-НЕ соединены с по четвертый входами шестоента И-НЕ, выход которого со с вторым входом пятого эле-НЕ и первыми входами восьмовятого элементов И-НЕ, третий и второго элементов И-НЕ сосоответственно с вторым и входами прерывания блока упя, выход первого элемента И-НЕ вход синхронизации блока управлениясоединен с вторыми входами с седьмого по девятый элементов И-НЕ, с второго по пятый входи условий блока управления соединены соответственно стретьими входами седьмого и восьмогоэлементов И-НЕ, четвертыми входамиседьмого и третьим входом десятого 10. элементов И-НЕ выход седьмого эле 9мента И-НЕ соединен с первым входомдесятого элемента И-НЕ, выход которого соединен с первым входом одиннадцатого элемента И-НЕ и вторым входом четвертого элемента И-НЕ, выходы,восьмого и девятого элементов И-НЕсоединены соответственно с вторыми третьим входами одиннадцатого эле-:мента И-НЕ, выход, которого соединенс вторым входом десятого и первымвходом двенадцатого элементов И-НЕ,первые входы с тринадцатого по девятнадцатьп элементов И-НЕ соединены соответственно с шестнадцатого по двадцатый входами условий, первым входомпрерывания и шестьй входом уровнейблока управления, восемнадцатый и девятнадцатый входы условий которого соединены соответственно с вторыми входамн двадцатого и двадцать первогоэлементов И-НЕ, вторые входы с двенадцатого по девятнадцатый, третьивходы двадцатого и двадцать первогоэлементов И-НЕ, первые входы двадцатьвторого и двадцать третьего элементов И-НЕ соединены с вторым входомсинхронизации блока управления, первый и второй входы условий которогосоединены соответственно с третьими.40 входами шестнадцатого и пятнадцатогоэлементов И-НЕ, с седьмого по одиннадцатый входы условий блока управления соединены соответственно с четвертыми входами пятнадцатого, двад цатого, шестнадцатого, двадцать пер"вого элементов И-НЕ, выход двадцатьвторого элемента И-НЕ соединен спервым входом двадцать четвертого элемента И-НЕ, выход которого соединенс вторым выходом блока управления цпервым входом двадцать пятого элемента И-НЕ, выход двадцать третьегоэлемента И-НЕ со динен с первым входом двадцать шестого элемента И-НЕ,выход которого соединен с первым входом двадцать седьмого элемента И-НЕ,выход которого соединен с вторым входом двадцать шестого элемента И-НЕ, выход двадцать пятого элемента И-НЕсоединен с вторым входом двадцать четвертого элемента И-НЕ, выходы с двенадцатого по восемнадцатый и с двадцатого по двадцать первый элементов И-НЕ соединены соответственно5 с второго по десятый входами двадцать второго, двадцать третьего, двадцать пятого, двадцать седьмого элементов И-НЕ, выход девятнадцатого элемента И-НЕ соединен с одиннадцатыми входами двадцать второго, двадцать пятого элементов И-НЕ, выход пятого элемента И-НЕ соединен с Я-входом первого триггера, первым входом двадцать восьмого элемента И-НЕ, выход шестого элемента И-НЕ соединен с К-входом первого .триггера, первым входом двадцать девятого элемента И-НЕ, третий вход синхронизации блока уп равления соединен с входом сихронизации первого триггера, инверсный выход которого соединен с третьим входом двенадцатого элемента И-НЕ, выход десятого элемента И-НЕ соединен 25 с первым входом тридцатого элемента И-НЕ, шестой вход синхронизации блока управления соединен с вторыми входами с двадцать восьмого по тридцатый элементов И-НЕ, выход одиннадцатого элемента И-НЕ соединен с третьим входом двадцать девятого элемента И-НЕ, выход которого соединен с первым входом тридцать первого элемента И-НЕ, выход которого соединен с первым входом тридцать .второго элемента И-НЕ, выход которого соединен с вторым входом тридцать первого элемента И-НЕ, выход которого соединен со счетным входом первого счетчика, 4 О выходы двадцать восьмого, тридцатого элементов И-НЕ соединены соответственно с вторым и третьим входами тридцать второго элемента И-НЕ, выход двадцать седьмого элемента И-НЕ 4 соединен со счетным входом второго счетчика и первым входом тридцать третьего элемента И-НЕ, пятый вход синхронизации блока управления соединен с первым входом тридцать четвер того элемента И-НЕ, первым управляющим входом коммутатора, четвертый вход синхронизации блока управления соединен с вторым входом тридцать третьего элемента И-НЕ, вторым управля ющим входом коммутатора, седьмой и восьмой входы синхронизации блока управления соединены соответственно с входами синхронизации второго и первого счетчиков, выходы которых соединены соответственно с вторым и пер,вым информационными входами коммутатора, выход которого соединен с седьмым выходом блока управления, восьмой и девятый выходы которого соединены соответственно с выходами тридцать третьего и тридцать четвертого элементов И-НЕ, выходы двадцать седьмого, тридцать первого элементов И-НЕ. соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с восьмым и седьмым входами синхронизации блока управления, третий вход синхронизации которого соединен с первыми входами с тридцать седьмого по сорок первый и с сорок четвертого по (45+К)-й элементов И-НЕ, выход первого элемента И соединен с суммирующим входом третьего счетчика, с первого по (К+ 1)-й разряды инверсного выхода которого соединены соответственно с второго по (К+2)-й входами сорок первого элемента И-НЕ, выход которого соединен с первым входом сорок второго элемента И-НЕ, выход которого соединен с 8-входом второго триггера, первым входом сорок третьего элемента И-НЕ, выходы с тридцать седьмого по сороковой элементов И-НЕ соединены соответственно с первого по четвертый входами тридцать шестого элемента И-НЕ, выход которого соединен с первымвходом тридцать пятого элемента И-НЕ, выход которого соединен с пятым входом трид" цать шестого элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, выход элемента НЕ соединен с вторым входом тридцать пятого элемента И-НЕ, выход которого соединен с четвертым входом первого элемента И-НЕ, первый вход синхронизации блока управления соединен с входом синхронизации второго триггера, входом элемента НЕ, прямые выходы с первого по (К+1)-й разряды прямого выхода третьего счетчика соединены соответственно с вторыми входами с сорок четвертого по (45+К)-й элементов И-НЕ, выходы которых соединены соответственно с второго по (К+2)-й входами сорок третьего элемента И-НЕ, выход которого соединен с вторым входом сорок второго элемента И-НЕ, К- входом второго триггера, третьим входом второго элемента И, прямой и ин18 08682 д К с Разряды Пакет данных А Пакет кода операции 1 Г 11111. 2 3 4 5 б 7-М 1 2-М функцио- ПР КСППР КОПК ПР 1 К ПР 2 К ПА 1 К ПА 2 К Код опе- ПР 1 нальное рации назна- обрабачение тывающегоблока Информация вПродолжение табл.1 Пакет адреса 1: 1 1 акет адреса обращения Пакет данных 2 2-М Ин П 2 Инфор- мация ЗАП П ПА 1 ЗАП ПР 2 Инфор мация"абл са обращения Пакет адреса 3 4 5-М 1 2нкцио- ПР Инфорльное мациязначеИнфор мация 17 1 рсный выходы второго триггера соинены соответственно с четвертым одом двенадцатого элемента И-НЕ и орым входом тридцать четвертого емента И-НЕ, (К+1) -й разряд прямо- выхода третьего счетчика соедин с вторым входом сорокового элента И-НЕ, первый и (К+1)-й разря-инверсного выхода и с второго по й разряды прямого выхода третьего етчика соединены соответственно с орого по (К+2)-й входами тридцать седьмого элемента И-НЕ, второй и (К+ 1)-й разряды инверсного выхода, первый и с третьего по К-й разря- , - ды прямого выхода третьего счетчика соединены соответственнос второго по (К+2)-й входами тридцать восьмого элемента И-НЕ, с первого по К-й разряды прямого выхода (К+1)-й разряд инверсного выхода третьего счетчика соединены соответственно с второго по (К+2)-й входами тридцать девятого элемента И-НЕ.Таблица 4 5-М 5

СмотретьЗаявка

4311713, 18.08.1987

АЛЕКСАНДРОВ ПАВЕЛ ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: параллельный, потоковый, процессор

Опубликовано: 23.11.1990

Код ссылки

<a href="https://patents.su/18-1608682-potokovyjj-parallelnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Потоковый параллельный процессор</a>

Предыдущий патент: Устройство для подключения абонентов к магистрали эвм

Следующий патент: Устройство для решения задач на графах

Случайный патент: Способ ввода магния в чугун