Микропрограммное устройство управления с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1142832

Авторы: Никольский, Тимонькин, Ткаченко, Харченко

Текст

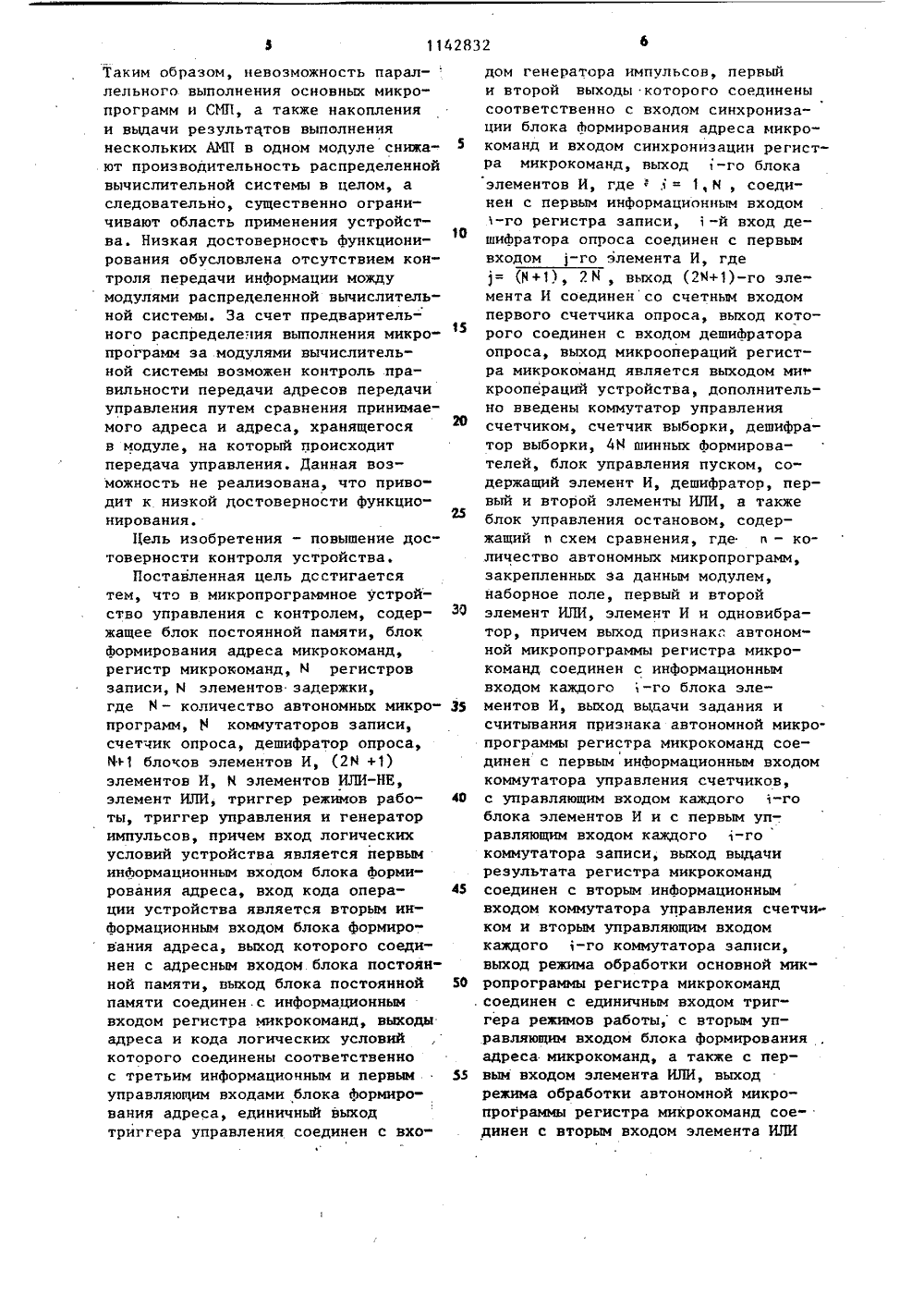

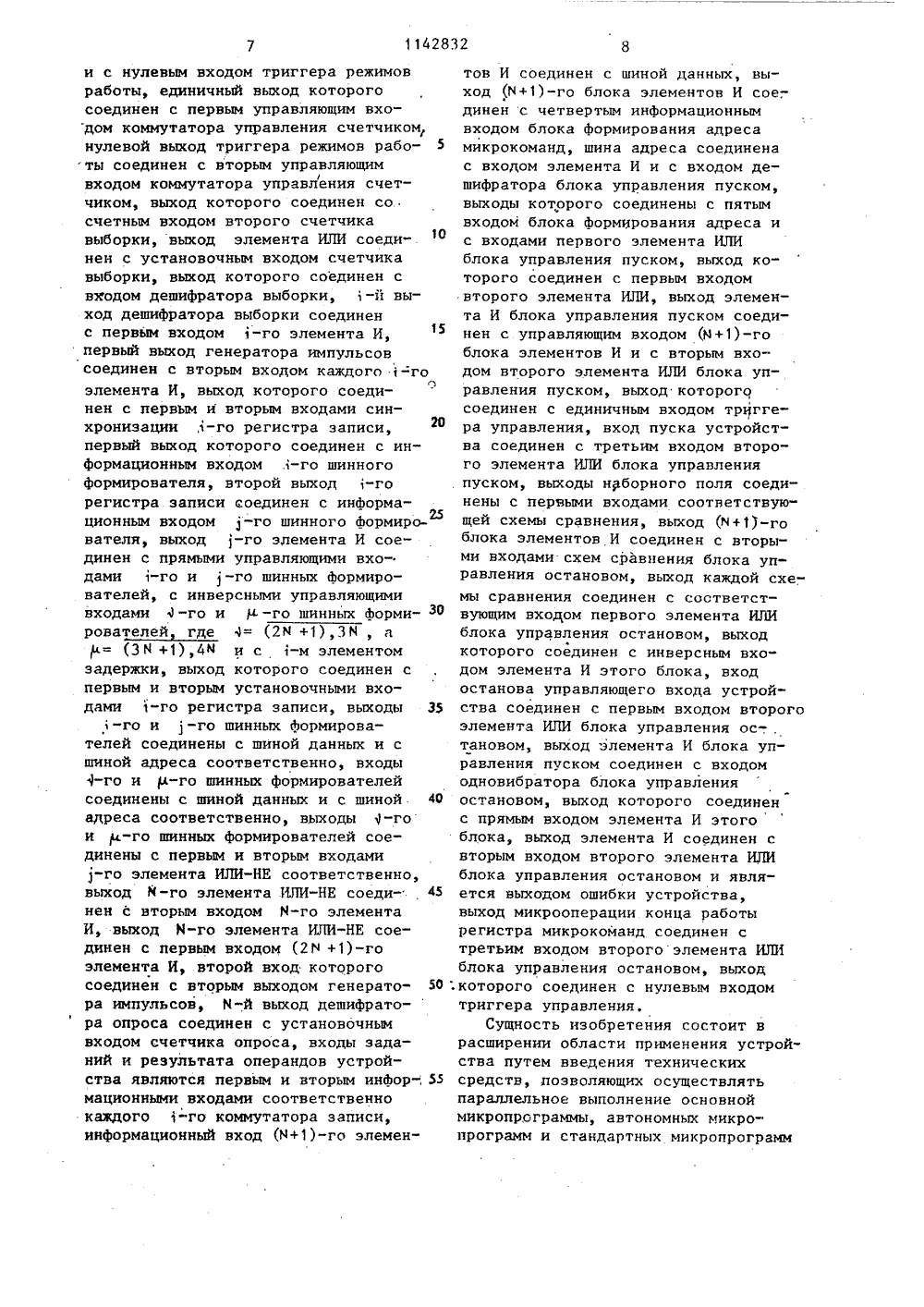

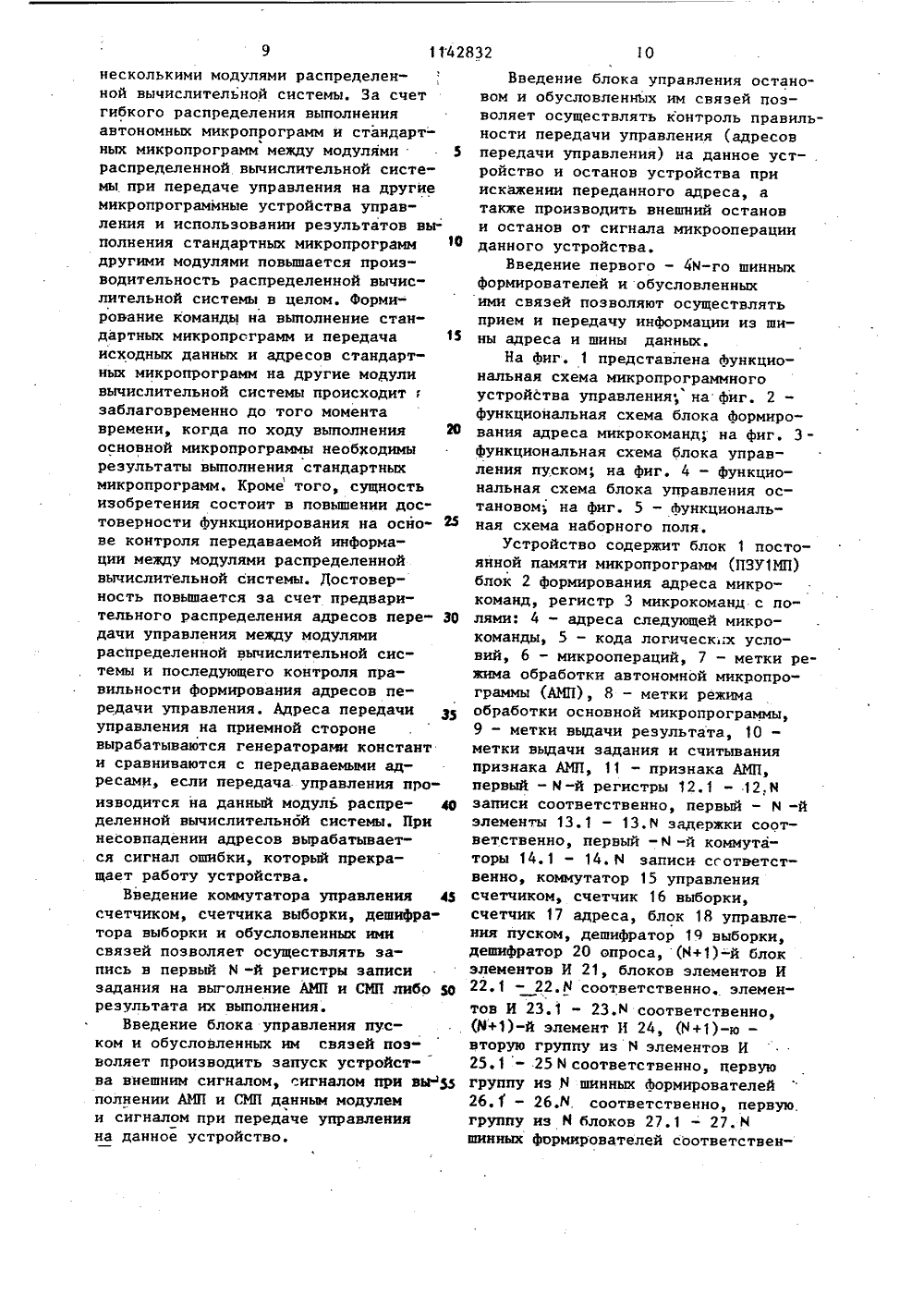

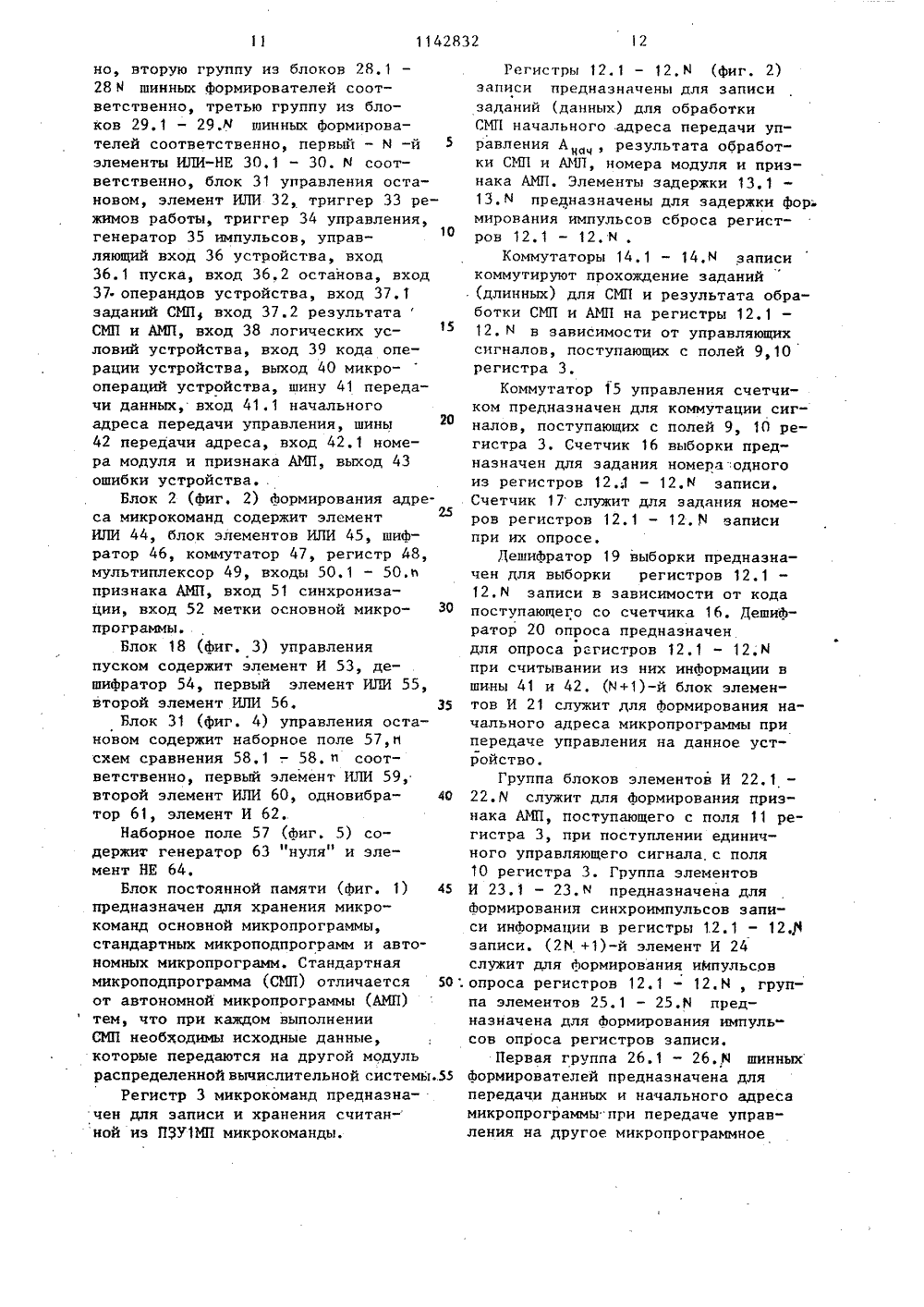

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬ(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ С КОНТРОЛЕМ, содержащееблок постоянной памяти, блок Формирования адреса микрокоманд, регистрмикрокоманд, К регистров записи,где Н - количество автономных микропрограмм, Н элементов задержки, Мкоммутаторов записи, счетчик опроса;дешифратор опроса, (К+1) блоковэлементов И, (2 М +1) элементов И,М элементов ИЛИ-НЕ, элемент ИЛИ,триггер режимов работы, триггеруправления и генератор импульсовпричем вход логических условийустройства является первым информационным входом блока Формированияадреса, вход кода операции устройства является вторым информационнымвходом блока Формирования адреса,.выход которого соединен с адреснымвходом блока постоянной памяти,выход блока постоянной памяти соединен с информационным входом регистра микрокоманд, выходы адреса и кодалогических условий которого соединены соответственно с третьим инфорЯО 1142832 4(1) С 06 Р 9/22 С 06 Р в 11/00 мационным и первым управляющим входами блока Аормирования адреса, единичный выход триггера управления соединен с входом генератора импульсов, первый и второй выходы которого соединены соответственно с входом синхронизации блока Формирования адреса микрокоманд и входом синхронизации регистра микрокоманд, выход1 -го блока элементов И, где= 1,М, соединен с первым информационным входом 1-го регистра записи, 1-й вход .дешифратора опроса соединен а первым входам -га элемента И, где = (К+1),2 й, выход (28+1)-го элемента И соединен со счетным входом первого счетчика опроса, выход которого соединен с входом дешифратора опроса, выход микро- С: операций регистра микрокоманд является выходом микроопераций устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в устройство вве- Ддены коммутатор управления счетчи- р ком, счетчик выборки, дешифратор выборки, 4 К шинных Формирователей, блок управления пуском, содержащий элемент И, дешифратор, первый и второй элементы ИЛИ, а такжеблок управления остановом, содержа. щий наборное поле, й схем сравнения, где .о - количество автономных микропрограмм, первый и второй элементы Ъф ИЛИ, элемент И и одновибратор, причем выход признака автономной микропрограммы регистра микрокоманд соединен с информационным входом каждого -го блока элементов И, выход выдачи задания и считываниятельной системы с контролем, передаче управления на данное устройство для выполнения АМП и СМП.Блок 31 (фиг. 5) предназначен для управления остановом устройства пос ле окончания выполнения основной микропрограммы, стандартных микро- подпрограмм и автономных микропрограмм, а также выключает устройство при внешнем останове, Кроме того, блок 31 производит контроль правильности передачи управления на данное устройство путем сравнения кода начального адреса микропрограммы Адч, поступающего с шины 41 (фиг, 1 и 2) 15 передачи данных, с кодами, формируемыми на наборном поле 57 (фиг. 5). При искажении кода, поступающего с шины 41, блок 31 (фиг, 5) формирует сигнал ошибки, который включает 20 устройство и поступает в шину 41 передачи данных, Работа блока 31 начинается с момента прихода кода начального адреса микропрограммы на входы схем сравнения 58.1 - 58,п 2- с выхода блока элементов И 21 (фиг.1), На другие входы схем сравнения поступают коды начальных адресов А с наборного поля 57. Количество схем сравнения и генераторов кон стант равно количеству различных начальных адресов При совпадении кодов схема сравнения 58 выдает единичный сигнал, который постуйает на инверсный вход элемента И 62. 35 Одновременно с поступлением на вход блока 31 кода начального адреса А на другой вход блока 31 поступает сигнал от блока 18 (фиг. 1). Этот сигнал, поступая на вход одновибратора 61 и задерживаясь на время срабатывания первого элемента ИЛИ 59 и схемы сравнения 58.1., подается на прямой вход элемента И 62. В результате на выходе элемента И 62 не 45 формируется единичный сигнал. Таким. образом, при совпадении кодов элемент И 62 не формирует сигнала ошибки. При несовпадении кодов на инверсный вход элемента И 62 посту О пает нулевой сигнал. Жри поступлении на прямой вход элемента И 62 единичного сигнала на выходе элемента И 62 формируется сигнал ошибки, который поступает на выход 40 55 устройства (фиг, 1) и через второй элемент ИЛИ 60 - на Й -вход триггера 34 управления (фиг, 1). Кроме того, второй элемент ИЛИ 60 позволяет формировать сигнал остановаМПУУ при внешнем выключении устройства, а также при поступлении сигнала останова от своего МПУУ.Наборное поле 57 (фиг. 6) предназначено для формирования кода -го начального адреса А ц, понауч ф которому запускается основная микропрограмма, при передаче управления на данное МПУУ. Генератор 63 "нуля" формирует нулевой сигнал. Элемент НЕ 64 инвертирует нулевой сигнал, поступающий с генератора 63, В данном случае с генераторного поля поступает трехразрядный код 110, который соответствует одному из разрешенных адресов передачи управления на данный модуль.Микропрограммное устройство управления функционирует в следующих режимах: выполнения основной микропрограммы и выдачи задания на выполнение АМП и СМП, выполнения АМП и СМП и выдачи результата выполнения АМП и СМП,Режим выполнения основной микропрограммы и выдачи задания на выполнение АМП или СМП, В исходном состоянии все триггеры, регистры и счетчики МПУУ находятся в нулевом состоянии. В ПЗУ 1 МК записаны микрокоманды основной микропрограммы, стандартных мнкроподпрограмми автономных микропрограмм.Работа устройства начинается сподачей сигнала "Пуск" на вход 36устройства. Сигнал с входа 36.1через блок 18 управления пуском поступает на 5 -Вход триггера34 управления и устанавливает егов единичное состояние. Единичныйсигнал, поступая с триггера 34 управления на вход генератора 35, разрешает формирование двух последовательностей синхроимпульсови Т1 сдвинутых друг относительно друга.Код операции, поступающий на вход 39 устройства и задающий начальный адрес основной микропрограммы, дается на первый информационный вход коммутатора 47 блока 2 Формирования адреса (фиг. 3), На инверсный управляющий вход коммутатора 47 поступает нулевой сигнал с поля 8 регистра 3 микрокоманд, который разрешает прохождение кода операции, поступающего с входа 39,устройства. Код опеф.10 рации, пройдя через блок элементов ЮП 1 45, поступает на информационный вход регистра 48, С приходом с входа 51 блока формирования адреса на вход регистра 48 синхроимпульсаь5 в регистр 48 (фиг. 3) производится запись кода операции - начального адреса основной микропрограммы. В результате записи в регистр 48 начального адреса на выходе блока 2 (фиг. 1) формирования адреса сформирован адрес первой микрокоманды основной микропрограммы. Первая микрокоманда считывается из ПЗУ 1 МК и записывается в регистр 3 микрокоманд с приходом на,его вход синхроимпульса ь . После записи в регистр 3 первой микрокоманды с поля 4 регист- ра 3 на вход 4 блока 2 (фиг. 3) поступает адрес следующей микрокоман ды, а с поля 5 регистра 3 на вход 5 блока поступает код логических условий. С поля 6 регистра 3 на выход 40 МПУУ поступают сигналы микроопераций, С поля 8 регистра 3 на вход 52 блока 2 поступает единичный сигнал. Этот единичный сигнал поступает на единичный вход триггера 33 режимов работы и через элемент ИЛИ 32 на установочный вход счетчи- ЗО ка 16 выборки. В результате триггер 33 устанавливается в единичное состояние, а счетчик 16 выборки подтверждает свое исходное (нулевое) состояние, 35На вход 38 устройства поступают значения логических условий, которые поступают на информационный вход мультиплексора 49 (фиг. 3) На управляющий вход мультиплексора 40 49 с входа 5 поступает код логического условия. Значение логического условия с выхода мультиплексора 49 поступает на вход элемента ИЛИ 44 В точках ветвления микропрограммы в 45 элементе ИЛИ 44 происходит модификация разряда в соответствии со значением логического условия на выходе мультиплексора 49. Модифицирован-. ный адрес, пройдя через блок элемен- БО тов ИЛИ 45, поступает на. информационный вход регистра 48 и с приходом: синхроимпульса Т записывается в регистр 48. Таким образом, из ПЗУ 1 МП считывается следующая, вторая, мик рокоманда и записывается в регистр 3 микрокоманд (фиг. 1) по синхроимпульсу 2 . В последующем работа МПУУ по выполнению основной микропрограммы происходит аналогично,Основная микропрограмма можетвыполняться в данном модуле распределенной вычислительной системыс контролем параллельно со стандартными микроподпрограммами и автономными микропрограммами в других модулях вычислительной системы.Задание на выполнение АМП отличается от задания на выполнение СМПтем, что,в регистрах 2.1 - 12,й записи записаны только признаки АМП,т.е. по вине адреса передаются кодпризнака АМП, а по шине данных -нулевой код. Если выдается заданиена выполнение СМП, то в регистрах12.1 - 12.М кроме признака АМП записываются и исходные данные;Во время выдачи задания на выполнение АМП или СМП с поля 10 регистра 3 микрокоманд единичный сигналпоступает на управляющие входы коммутаторов 14.1 - 14, М , на управляющие входы группы блоков элементов И 22,1 - 22. К и на первыйинформационный вход коммутатора15 управления счетчиком. Одновременно с выхода поля 11 регистра .3 признак АМП, пройдя через группу блоков элементов И 221 - 22. М, поступает на 3 -входы регистров 12,1 - 12 Й. Управляющий сигнал г выхода поля 10 регистра 3, пройдя через коммутатор 15, записывается в счетчик 16 выборки, Код со счетчика 16 поступает на дешифратор 19 выборки, преобразуется и выбирает для записи информации регистр 12.1, Сигнал выборки с первого входа дешифратора 19 поступает на вход элемента И 23,1 и, пройдя через него после прихода на второй вход элемента И 23.1 синхросигнала Т, поступает на синхровходы регистра 12,1. Таким образом, в регистр 12,1 записывается признак АМП. Одновременно с записью признака АМП в регистр 12.1 по 3 -входу может производиться запись исходных данных, необходимых при выполнении СМП, если они поступают на вход 37 устройства и на вход 37.1 заданий СМП. Данные с входа 37,1, проходя через коммутаторы 14,1 - 14. М , поступают на 3 1-входы регистров 12,1 - 12,8, но записываются только в регистр 12.1.Данные, записанные в регистре12,1, по первому выходу регистра12, 1 поступают па информационныйвход блока магистральных элементов26.1, а признак АМП по второму выходу регистра 12.1 на информационный вход блока магистральных элементов 27.1.Если шины 41 и 42 не заняты переда,Очей информации, то на входы группышинных формирователей 28,1 - 28. Ми 29.1 - 29,М , а следовательно, ина входы группы элементов ИЛИ-НЕ30.1 - 30.11 постУпают нулевые сигналы. С выходов группы элементов ИЛИ-НЕ1530.1 - 30. М единичные сигналы поступают на входы группы элементов И25,1 - 25. М соответственно. Крометого, единичный сигнал с выхода элементов ИЛИ-НЕ 30 поступает на входэлемента И 24, на второй вход которого поступают синхроимпульсыВ результате синхроимпульсы поступают на счетный вход счетчика 17опроса, В счетчике 17 записываются25коды номеров регистров 12,1 - 12 Изаписи, которые преобразуются дешыфратором 20. Сигналы с первого -Н-го выхода дешифратора 20 опросапоступают на первый - М -й регистрызаписи соответственно. При записи всчетчик 17 опроса "1" с первоговыхода дешифратор 20 на вход элемента И 25,1 поступает единичныйсигнал опроса, который, пройдя 35через элемент И 25.1, разрешаетвыдачу ичформации из регистра 12.1в шину 41 и 42 через шинные формирователи 261 и 27.1 соответственно.Сигнал опроса, пройдя через. элементзадержки 13.1, сбрасывает регистр12.1 в нулевое исходное состояние,Счетчик 17 устанавливается в нулевое состояние,Во время выполнения основной45микропрограммы могут выдаватьсяследующие задания на выполнение АМПи СИП другими модулями распределенной вычислительной системы, в то время,как информация, которая записана 5 Ов регистре 12.1, не передана ввидузанятости шин 41 и 42. Тогда информация для выполнения АМП и СМПзаписывается в следующий регистр 12,2,Таким образом, счетчик 16 выборки и 55дешифратор 19 выборки служат для управления записи информации в регистры 12.1 - 12.Й, а счетчик 17 опроса и дев ифратор 20 опроса предназначены для управления выдачи информации из регистров 12. 1 - 12, М . Выдача заданий на выполнение АИП и СИП и выполнение основной микропрограммы происходит параллельно. По окончании выполнения основной микропрограммы происходит останов (выключение) МПУУ и передача управления на другой модуль распределенной вычислительной системы. Сигнал с выхода поля 6 микрооперацин регистра 3 микрокоманд через блок 31 управления остановом поступает на Р -вход триггера 34 управления и устанавливает его в нулевое состояние. В результате генератор 35 прекращает выдачу синхросигналовии блоки1 2 рует работу МПУУ. Передача управления на другое МПУУ происходит следующим образом. Перед выдачей сигнала останова из регистра 3 микрокоманд в регистр 12.1 по входу 3 1 происходит запись начального адреса передачи управления А, а по входу 3 2 происходит запись номера модуля М ,д на который необходимо передать управление. Выдача Аныч на шину 41 передачи данных и М ,в шину 42 передачи адреса происходит аналогично выдаче данных и признака АМП для выполнения СМП или АИП другим модулем. Номер модуля М, с входа 42.1 поступает в блок 18 управления пуском, Элемент И 53 (фп . 4) анализирует принадлежность И данному ИПУУ, При совпадении кода, поступающего с входа 421, с инверсными и прямыми входами элемента И 53 последний формирует сигнал пуска, который, проходя через элемент ИЛИ 56, поступает на единичный вход триггера 34 управления. Одновременно с пуском устройства с выхода блока 18 на вход блока элементов И 21 и вход блока 31 управления остановом поступает управляющий сигнал, который разрешает прохождение начального адреса Ас выхода блока элементов И 21 на вход блока 2 формирования адреса и на вход блока 31 управления остановом.В блоке 31 производится проверка соответствия полученного кода Анц, разрешенным кодовым комбинациям, если полученный код не входит в число разрешенных, то формируется сигналотказа, который йоступает на выход40 устройства,Режим выполнения АИП нли СИПси выдачи результата их выполнения. 3 отличается от предыдущего следующим. ИПУУ в данном режиме запускается с моментом прихода признака АИП с входа 42.1 на вход блока 18 управления пуском. Признак АИП поступает на вход 1 дешифратора 54 (фиг. 4). Дешифратор 54 преобразует код признака АИП в сигнал, который поступает на пятИ информационный вход блока 2 формирования адреса микрокоманд. По 1 З этому сигналу шиФратор 46 формирует начальный адрес. Кроме то 1 о, преобра эованный код с одного из выходов дешифратора 54 через элементы ИЛИ 55 и 56 поступает на единичный фО вход триггера 34 (фиг. 1) управле- ния. Отличием является также то, что в регистр 12.1 по входу 91 записывается вместо данных результат выполнения ЙЧП или СИП.Таким образом, данное микропрот граммное устройство управления модуля распределенной вычислительной ;:системы обеспечивает возможность параллельного выполнения основной микропрограммы, автономных и стайдартных микроподпрограмм, сохране ния информации в регистрах при занятых шинах передачи и осуществляет контроль правильности передачи,управления на данное устройство на основе проверки соответствия адреса передачи управления заданному множеству;Применение изобретения позволит строить более производительные и надежные распределенные вычислительные системы.1142832 Составитель И. Сигалдактор О, Колесникова Техред СМигунова орректор Л, Пилипенко 10 ГГодписное 113035,д ПП "Патент", г. Ужгород, ул. Проект каз 138/42ВНИИПИ Тираж осударственного ам изобретений и осква Ж, Рау митета ткрытий кан набпризнака автономной микропрограммы регистра микрокоманд соединен с первым информационным входом коммутатора управления счетчиком, с управляющим входом каждого -го блока элементов И и с первым управляющим входом каждого -го коммутато. ра записи, выход выдачи результата регистра микрокоманд соединен с вто+ рым информационным входом коммута" тора управления счетчиком и вторым управляющим входом каждого-го коммутатора записи, выход режима обработки основной микропрограммы регистра микрокоманд соединен с единичным входом триггера режимов работы, с вторым управляющим входом блока формирования адреса микрокоманд, а также с первым входом элемента ИЛИ, выход режима обработки автономной микрокоманды регистра микрокоманд соединен с вторым входом элемента ИЛИ и с нулевым входом триггера режимов работы, единичный выход которого соединен с первым, управляющим входом коммутатора управления счетчиком, нулевой вьпсод триггера режимов работы соединен с вторым управляющим входом коммутатора управления счетчиком, выход которого соединен со счетным входом счетчика выборки, выход элемента ИЛИ соединен с установочным входом счетчика выборки, выход которого соединен свходом дешифратора выборки, -й выход дешифратора выборки соединен с первым входом 1-го элемента И, первый выход генератора импульсов соединен с вторым входом каждого -го элемента И, выход которого соединен с первым и вторым входами синхронизации -го регистра, записи, первый выход которого соединен с информационным входом -го шинного формирователя, второй выход -го регистра записи соединен с информационным входом-го шинного формирователя, выход1-го элемента И соединен с прямыми управляющими входами -го и 1-го шинных формирователей, с инверснымиуправляющими входами 1-го и с-гошинных формирователей, гдеГОГОВ 3, . 7 ЛТТД 7с входом 3-го элемента задержки,выход которого соединен с первыми вторым установочными входами1-го регистра записи, выходы -гои ,1 -го шинных формирователей сое ди" чнены с шиной данных и с шиной адреса соответственно, входы 4-го и ц-го шинных формирователей соединены с шиной данных и с Йиной адреса соответственно, выходы-го и р-го шинных формирователей соединены с первым и вторым входами 1-го элемента ИЛИ-НЕ соответственно,1выход М-го элемента ИЛИ-НЕ соединен с вторым входом М-го элемента И, выход Й-го элемента ИЛИ-НЕ соединен с первым входом (2 М +1)-го элемента И, второй вход которого соединен с вторым выходом генератора импульсов, М-й выход дешифратора опроса . соединен с установочным входом счетчика опроса, входы заданий и результата операндов устройства являются первым и вторым информационными входами соответственно каждого -го коммутатора записи, информационный вход (М+1)-го блока элементов И соединен с шиной данных, выход (К+1)-го блока элементов И соединен с четвертым информационным входом блока формирования адреса микрокоманд, шина адреса соединенас входом элемента И и с входом дешифратора блока управления пуском, выходы дешифратора блока управления пуском соединены с пятым информационнымвходом блока формирования адреса и с соответствующими входами первого элемента ИЛИ блока управления пуском, выход которого соединен с первым входом второго элемента ИЛИ, выход элемента И блока управления пуском соединен с управляющим входом (М+1)-го блока элементов И и с вторым входом второго элемента ИЛИ блока управления пуском, выход которого соединен с единичным входом триггера управления, вход пуска устройства соединен с третьим входом второго элемента ИЛИ блока управления пуском, выходы наборного поля блока управления остановом соединены с первыми входами соответствующих схем сравнения, выход (М+1)-го блока элементов И соединен с вторыми входами схем сравнения блокауправления остановом, выход каждойсхемы сравнения соединен с соответствующим входом первого элемента ИЛИ блока управления остановом, выход первого элемента ИЛИ соединен с инсным входом элеменокаравления останова, вход остановатройства соединен с первым входом1142832 второго элемента ИЛИ блока управления остановом, выход элемента Иблока управления пуском соединенс входом одновибратора блока управления остановом, выход одновибратора соединен с прямым входом элемента И блока управления остановом,выход элемента И соединен с вторымИзобретение относится к области цифровой вычислительной техники и может быть использовано при построении микропрограммных устройств управления распределенных вычислительных систем, проектируемых на однотипных БИС.Известно микропрограммное устройство управления, содержащее арифметический блок, блоки памяти адресов и микроопераций, счетчик команд, регистры, дешифратор, логические элементы И и ИЛИ 11.Недостатком известного устройства-являются низкие функциональные возможности, обусловленные тем, что структура устройства не позволяет увеличивать объем реализуемых программ путем введения дополнительных однотипных устройств.Известно также микропрограммное устройство управления, содержащее арифметический блок, матрицу микропрограмм, счетчик команд, регистр адреса передачи управления, дешифратор, регистр адреса возврата, элементы И и ИЛИ Г 23.Недостатком данного устройства является низкое быстродействие, обусловленное нерациональным использованием каждого микропрограммного устройства управления, что приводит к большому времени простоя устройства и вычислительной системы в целом.Наиболее близким к изобретению по технической сущности и достигае.мому положительному эффекту является микропрограммное устройство управления, содержащее арифметический блок, выход которого соединен с первым входом первого блока элементов И,входом второго элемента ИЛИ блокауправления остансвом и являетсявыходом ошибки устройства, выходмикрооперации конца работы регистра микоокоманд соединен с третьимвходом второго элемента ИЛИ блока управления остановом,выход которого соединенснулевым входом триггера управления. 2 фвыход которого соединен с адреснымвходом блока памяти адресов, первыйвыход которого соединен с .адресным,входом блока памяти микроопераций,выход которого соединен с входомарифметического блока и первымивходами второго и третьего блоковэлементов И, выход второго блокаэлементов И через регистр адреса,возврата соединен с вторым входомтретьего блока элементов И, выходкоторого соединен с первым информационным входом счетчика команд,выход которого соединен с вторымвходом второго блока элементов Ии с первыми входами группы блоковэлементов И, вторые входы которыхподключены к выходам дешифраторасоответственно, выходы группы блоковэлементов И являются информационными выходами устройства, вход дешифратора соединен с выходом регистраадреса передачи. управления, выходыдешифратора подключены к входам пер вого элемента ИЛИ, выход которогосоединен с инверсным входом четвертого блока элементов И,п;ямой входкоторого соединен с вторым выходомблока памяти адресов, а выход четвертого блока элементов,И подключенк второму информационному входусчетчика команд, третий информационный вход которого соединен с выходомпятого блока элементов И, первый входкоторого соединен с выходом первого 35 элемента ИЛИ, второй вход - с выходом первого блока элементов ИЛИ,входы которого подключены к первымадресным входам устройства, выходвторого блока элементов ИЛИ соединен 40с вторым входом первого блока эле. ментов И, первый вход второго блокаэлементов ИЛИ соединен с выходомсчетчика команд, второй вход - с вы-,ходом регистра автономных микропрограмм. установочный вход которого соединен с установочным входом 5регистра адреса передачи управления,инверсным входом шестого блока элементов И и выхоДом второго элемента ИЛИ, выход которого соединен с выходом первого блока элементов ИЛИ, 1 Овьжод шестого блока элементов Исоединен с первым входом третьегоблока элементов ИЛИ; второй входкоторого подключен к вькоду седьмогоблока элементов И, третий вход - 15к второму адресному входу устройства,четвертый вход - к выходу восьмого .блока элементов И, выход третьегоблока элементов ИЛИ соединен с информационным входом регистра автономных программ, третий выход блокапамяти адресов соединен с первымивходами девятого, десятого, одиннадцатого и вторым входом шестогоблоков элементов И, третий вход 25последнего соединен с выходом первого элемента ИЛИ, четвертый входшестого блока элементов И соединенс четвертым выходом блока памяти адресов, пятый выход которого соединен З 0с инверсным входом десятого блокаэлементов И, с первым входом восьмого блока элементов И, с вторымвходом одиннадцатого блока элементов И и через последовательно соединенные элемент НЕ и первый элементзадержки с установочным входомбуферного регистра, информационныйвход которого подключен к выходуодиннадцатого блока элементов И, а)вькод буферного регистра соединен свторым входом восьмого блока элементов И, третий вход которого подключен к выходу арифметическогоблока, шестой выход блока памятиадресов подключен к второму входудевятого блока элементов И, выходкоторого является адресным выходомустройства, выход десятого блокаэлементов И соединен с информационным входом регистра адреса передачи управления, выход первого элемента ИЛИ через второй элементзадержки подключен к первому входуседьмого блока элементов И, второй 55вход которого соединен с вторым выходом блока памяти адресов С 31. Недостатками указанного устройства являются узкая область применения и низкая достоверность функционирования, Узкая область применения обусловлена тем, что структура устройства ограничивает производительность системы, построенной на однотипных модулях, ввиду отсутствия технических средств, позволяющих гибко перераспределять выполнение вычислительных задач и связанных с ними задач управления, Нерациональное использование каждого модуля распределенной вычислительной системы снижает ее потенциальные возможности. Структура микропрограммного устройства управления такова, что при выполнении основньк микропрограмм в данном модуле другие модули распределенной вычислительной системы могут реализовать автономные микропрограммы (АИП) в соответствии с передаваемыми на них адресами. Основной микропрограммой назовем микропрограмму, которая вызывает выполнение автономных микро-программ и стандартных микропрограмм в других модулях распределенной вычислительной системы и использует результаты их выполнения для своей реализации. АМП будет называть микропрограмму, результат выполнения которой одинаков для всех модулей вычислительной системы и не зависит от результата выполнения предыдущих микрокоманд основной микропрограммы. АИП является частнымслучаем стандартной микропрограммы (СИП). За счет распределенной реализации АМП повьппается быстродей- ствие удтройства, Однако при вызове СИП модуль распределенной вычислительной системы приостанавливает выполнение основной микропрограммы и выполняет СИП. При этом не реализует возможность одновременного (параллельного) выполнения основной микропрограммы и СИП разными модулями вычислительной системы. Область применения устройства ограничи- вается также,тем, что в нем отсутствуют технические средства, способ- . ные управлять накоплением и выдачей результатов выполнения нескольких автономных микропрограмм. Это уменьшает число закрепленных за 1-м модулем микропрограмм, которые могут - быть отнесены к числу автономных.15 Таким образом, невозможность парал-лельного выполнения основных микропрограмм и СМП, а также накопленияи выдачи результатов выполнениянескольких АМП в одном модуле снижают производительность распределеннойвычислительной системы в целом, аследовательно, существенно ограничивают область применения устройства. Низкая достоверность функционирования обусловлена отсутствием контроля передачи информации мождумодулями распределенной вычислительной системы. За счет предварительного распределения выполнения микропрограмм за модулями вычислительной системы возможен контроль .правильности передачи адресов передачиуправления путем сравнения принимаемого адреса и адреса, хранящегосяв модуле, на который происходитпередача управления, Данная возможность не реализована, что приводит к низкой достоверности функционирования.Цель изобретения - повышение дос"товерности контроля устройства,Поставленная цель дсстигаетсятем, что в микропрограммное устройство управления с контролем, содержащее блок постоянной памяти, блокформирования адреса микрокоманд,регистр микрономанд, й регистровзаписи, М элементов задержки,где М - количество автономных микропрограмм, М коммутаторов записи,счетчик опроса, дешифратор опроса,М+1 блоков элементов И, (2 й +1)элементов И, М элементов ИЛИ-НЕ,элемент ИЛИ, триггер режимов работы, триггер управления и генераторимпульсов, причем вход логическихусловий устройства является первыминформационным входом блока формирования адреса, вход кода операции устройства является вторым информационным входом блока формирования адреса, выход которого соединен с адресным входом блока постоянной памяти, выход блока постояннойпамяти соединен.с информационнымвходом регистра микрокоманд, выходыадреса и кода логических условийкоторого соединены соответственнос третьим информационным и первымуправляющим входами блока формирования адреса, единичный выходтриггера управления соединен с вхо 5 20 25 30 35 40 45 50 55 дом генератора импульсов, первый и второй выходы которого соединены соответственно с входом синхронизации блока формирования адреса микро- команд и входом синхронизации регистра микрокоманд, выход -го блока элементов И, где ф, = 1, М, соединен с первым информационным входом -го регистра записи, 1 -й вход дешифратора опроса соединен с первым входом 1-го элемента И, где(8+1), 2 М, выход (2 й+1)-го элемента И соединенсо счетным входом первого счетчика опроса, выход которого соединен с входом дешифратора опроса, выход микроопераций регистра микрокоманд является выходом миг кроопераций устройства, дополнительно введены коммутатор управления счетчиком, счетчик выборки, дешифратор выборки, 48 шинных формирователей, блок управления пуском, содержащий элемент И, дешифратор, первый и второй элементы ИЛИ, а также блок управления остановом, содержащий п схем сравнения, где и - количество автономных микропрограмм, закрепленных за данным модулем, наборное поле, первый и второй элемент ИЛИ, элемент И и одновибратор, причем выход признака автономной микропрограммы регистра микро- команд соединен с информационным входом каждого 1-го блока элементов И, выход выдачи задания и считывания признака автономной микропрограммы регистра мнкрокоманд соединен с первым информационным входом коммутатора управления счетчиков, с управляющим входом каждого -го блока элементов И и с первым управляющим входом каждого -го коммутатора записи, выход выдачи результата регистра микрокоманд соединен с вторым информационным входом коммутатора управления счетчиком и вторым управляющим входом каждого 1-го коммутатора записи, выход режима обработки основной микропрограммы регистра микрокоманд соединен с единичным входом триггера режимов работы, с вторым управляющим входом блока формирования адреса микрокоманд, а также с первым входом элемента ИЛИ, выход режима обработки автономной микропрограммы регистра микрокоманд соединен с вторым входом элемента ИЛИи с нулевым входом триггера режимовработы, единичный выход которогосоединен с первым управляющим входом коммутатора управления счетчиком,нулевой выход триггера режимов работы соединен с вторым управляющимвходом коммутатора управления счетчиком, выход которого соединен со .счетным входом второго счетчикавыборки, выход элемента ИЛИ соединен с установочным входом счетчикавыборки, выход которого соединен свходом дешифратора выборки, 1-и выход дешифратора выборки соединенс первым входом -го элемента И,первый выход генератора импульсовсоединен с вторым входом каждого 1-гоэлемента И, выход которого соединен с первым и вторым входами синхронизации ,-го регистра записи,первый выход которого соединен с информационным входом .2-го шинногоформирователя, второй выход 1-горегистра записи соединен с информационным входом 1-го шинного формиро 25вателя, выход 1-го элемента И соединен с прямыми управляющими входами 2-го и 1 -го шинных формирователей, с инверсными управляющимивходами 4 -го и р -го шинных форми- ЗОроеателей где 4= 12 М +1),3 М,13 М т 1),4 м н о 1-м элементомзадержки, выход которого соединен спервым и вторым установочными входами 1-го регистра записи, выходы 351-го и 1-го шинных формирователей соединены с шиной данных и сшиной адреса соответственно, входы1-го и -го шинных формирователейсоединены с шиной данных и с шиной 40адреса соответственно, выходы -гои м-го шинных формирователей соединены с первым и вторым входами1-го элемента ИЛИ-НЕ соответственно,выход К-го элемента ИЛИ-НЕ соединен с вторым входом М-го элементаИ, выход Н-го элемента ИЛИ-НЕ соединен с первым входом (2 г 1 +1)-гоэлемента И, второй вход которогосоединен с вторым выходом генератора импульсов, М-й выход дешифратора опроса соединен с установочнымвходом счетчика опроса, входы заданий и результата операндов устройства являются первым и вторым инфор-, 55мационными входами соответственнокаждого 1-го коммутатора записи,информационный вход (М+1)-го элементов И соединен с шиной данных, выход м 4+1)-го блока элементов И сое-, динен с четвертым информационным входом блока формирования адреса микрокоманд, шина адреса соединена с входом элемента И и с входом дешифратора блока управления пуском, выходы которого соединены с пятым входом блока формирования адреса и с входами первого элемента ИЛИ блока управления пуском, выход которого соединен с первым входом второго элемента ИЛИ, выход элемента И блока управления пуском соединен с управляющим входом (М+1)-го блока элементов И и с вторым входом второго элемента ИЛИ блока управления пуском, выход которог соединен с единичным входом триггера управления, вход пуска устройства соединен с третьим входом второго элемента ИЛИ блока управления пуском, выходы наборного поля соединены с первыми входами соответствующей схемы сравнения, выход 1+1)-го блока элементов И соединен с вторыми входами схем сравнения блока управления остановом, выход каждой схемы сравнения соединен с соответствующим входом первого элемента ИЛИ блока управления остановом, выход которого соединен с инверсным входом элемента И этого блока, входостанова управляющего входа устройства соединен с первым входом второго элемента ИЛИ блока управления ос- тановом, выход элемента И блока управления пуском соединен с входом одновибратора блока управления остановом, выход которого соединен с прямым входом элемента И этого блока, выход элемента И соединен с вторым входом второго элемента ИЛИблока управления остановом и является выходом ошибки устройства, выход микрооперации конца работы регистра микрокоманд соединен стретьим входом второго элемента ИЛИблока управления остановом, выходкоторого соединен с нулевым входомтриггера управления.Сущность изобретения состоит врасширении области применения устройства путем введения технических средств, позволяющих осуществлятьпараллельное выполнение основноймикропрсграммы, автономных микропрограмм и стандартных микропрограммнесколькими модулями распределенной вычислительной системы, За счетгибкого распределения выполненияавтономных микропрограмм и стандартных микропрограмм между модулями 5распределенной вычислительной системы при передаче управления на другиемикропрограммные устройства управления и использовании результатов вьюполнения стандартных микропрограмм 1 фдругими модулями повышается производительность распределенной вычислительной системы в целом. Формирование команды на выполнение стандартных микропрограмм и передача 15исходных данных и адресов стандартных микропрограмм на другие модуливычислительной системы происходитзаблаговременно до того моментавремени, когда по ходу выполнения 20основной микропрограммы необходимырезультаты выполнения стандартныхмикропрограмм, Кроме того, сущностьизобретения состоит в повышении дос"товерности функционирования на осно- фве контроля передаваемой информации между модулями распределеннойвычислительной системы, Достоверность повышается за счет предварительного распределения адресов пере- ЗОдачи управления между модулямираспределенной вычислительной системы и последующего контроля правильности формирования адресов передачи управления. Адреса передачиуправления на приемной стороневырабатываются генераторами константи сравниваются с передаваемыми адресами, если передача управления производится на данный модуль распределенной вычислительной системы. Принесовпадении адресов вырабатывается сигнал ошибки, который прекращает работу устройства,Введение коммутатора управления 43счетчиком, счетчика выборки, дешифратора выборки и обусловленных имисвязей позволяет осуществлять запись в первый Н -й регистры записизадания на выголнение АМП и СИП либо 30результата нх выполнения.Введение блока управления пуском и обусловленных им связей позволяет производить запуск устройства внешним сигналом, сигналом при выуполнении АМП и СИП данным модулемн сигналом при передаче управленияна данное устройство,Введение блока управления остановом и обусловленных им связей позволяет осуществлять контроль правильности передачи управления (адресовпередачи управления) на данное уст- .ройство и останов устройства приискажении переданного адреса, атакже производить внешний останови останов от сигнала микрооперацииданного устройства,Введение первого - 4 М-го шинныхформирователей и обусловленныхими связей позволяют осуществлятьприем и передачу информации из шины адреса и шины данных.На фиг. 1 представлена функциональная схема микропрограммногоустройства управления; на фиг, 2 -функциональная схема блока формирования адреса микрокоманд на фиг. 3 функциональная схема блока управления пуском, на фиг. 4 - функциональная схема блока управления остановом на фиг. 5 - Функциональная схема наборного поля.Устройство содержит блок 1 постоянной памяти микропрограмм (ПЗУ 1 ИП)блок 2 формирования адреса микрокоманд, регистр 3 микрокоманд с полями: 4 - адреса следующей микрокоманды, 5 - кода логическ;х условий, 6 - микроопераций, 7 - метки режима обработки автономной микропрограммы (АМП), 8 - метки режимаобработки основной микропрограммы,9 - метки выдачи результата, 10 -метки выдачи задания и считыванияпризнака АИП, 11 - признака АИП,первый - И -й регистры 12.1 - 12 Нзаписи соответственно, первый - М -йэлементы 13,1 - 13.М задержки соответственно, первый - М -й коммутаторы 14, 1 - 14. М записи соответственно, коммутатор 15 управлениясчетчиком, счетчик 16 выборки,счетчик 17 адреса, блок 18 управле-.ния пуском, дешифратор 19 выборки,дешифратор 20 опроса, (8+1)-й блокэлементов И 21, блоков элементов И22.1 - 22.И соответственно, элементов И 23.1 - 23.М соответственно,(И+1)-й элемент И 24, 04+1)-ю -вторую группу из М элементов И25.1 - 25 М соответственно, первуюгруппу из,М шинных Формирователей26. 1 - 26.К. соответственно, первуюгруппу из Й блоков 27.1 -27. Мшинных формирователей соответствен 1142832 12но, вторую группу из блоков 28,128 й шинных формирователей соответственно, третью группу из блоков 29.1 - 29.М шинных формирователей соответственно, первый - й -й 5элементы ИЛИ-НЕ 30,1 - 30, 1 Ч соответственно, блок 31 управления остановом, элемент ИЛИ 32, триггер 33 режимов работы, триггер 34 управления,генератор 35 импульсов, управ 10ляющий вход 36 устройства, вход361 пуска, вход 36.2 останова, вход37.операндов устройства, вход 37. 1заданий СМП вход 37.2 результатаСМП и АМП, вход 38 логических условий устройства, вход 39 кода операции устройства, выход 40 микроопераций устройства, шину 41 передачи данных, вход 41,1 начальногоадреса передачи управления, шины42 передачи адреса, вход 42.1 номера модуля и признака АМП, выход 43ошибки устройстваБлок 2 (фиг. 2) Формирования адреса микрокоманд содержит элементИЛИ 44, блок элементов ИЛИ 45, шифратор 46, коммутатор 47, регистр 48,мультиплексор 49, входы 50.1 - 50,ьпризнака АМП, вход 51 синхронизации, вход 52 метки основной микро- ЗОпрограммы.Блок 18 (Фиг, 3) управленияпуском содержит элемент И 53, дешифратор 54, первый элемент ИЛИ 55,второй элемент ИЛИ 56, 35Блок 31 (фиг4) управления остановом содержит наборное поле 57,псхем сравнения 58,1 в . 58. и соответственно, первый элемент ИЛИ 59,второй элемент ИЛИ 60, одновибратор 61, элемент И 62.Наборное поле 57 (Фиг. 5) содержит генератор 63 "нуля" и элемент НЕ 64.Блок постоянной памяти (Фиг. 1) 45предназначен для хранения микрокоманд основной микропрограммы,стандартных микроподпрограмм и автономных микропрограмм, Стандартнаямикроподпрограмма (СМП) отличается 50от автономной микропрограммы (АМП)тем, что при каждом выполненииСМП необходимы исходные данные,которые передаются на другой модульраспределенной вычислительной системы.55Регистр 3 микрокоманд предназначен для записи и хранения считанной из ЙЗУ 1 МП микрокоманды. Регистры 12. 1 - 12. М (фиг. 2) записи предназначены для записи заданий (данных) для обработки СМП начального адреса передачи управления Ащч, результата обработки СМП и АМП, номера модуля и признака АМП. Элементы задержки 13,1 13. М предназначены для задержки фор- мирования импульсов сброса регистров 12. 1 - 12. МКоммутаторы 14.1 - 14.М записи коммутируют прохождение заданий (длинных) для СМП и результата обработки СМП и АМП на регистры 12.1 12. М в зависимости от управляющих сигналов, поступающих с полей 9, 10 регистра 3.Коммутатор 15 управления счетчиком предназначен для коммутации сигналов, поступающих с полей 9, 10 регистра 3, Счетчик 16 выборки предназначен для задания номера:одного из регистров 12.1 - 12.М записи. Счетчик 17 служит для задания номеров регистров 12.1 - 12.1 Ч записи при их опросе,Дешифратор 19 выборки предназначен для выборки регистров 12.1 12, М записи в зависимости от кода поступающего со счетчика 16. Дешифратор 20 опроса предназначен для опроса регистров 12,1 - 12.М при считывании из них информации в шины 41 и 42. (8+1)-й блок элементов И 21 служит для Формирования начального адреса микропрограммы при передаче управления на данное устройство.Группа блоков элементов И 22. 1 22,Ю служит для формирования признака АМП, поступающего с поля 11 регистра 3, при поступлении единичного управляющего сигнала с поля 10 регистра 3. Группа элементовИ 23,1 - 23,1 ч предназначена дляФормирования синхроимпульсов записи инФормации в регистры 121 - 1241записи. (2 г 1 +1)-й элемент И 24служит для Формирования импульсовопроса регистров 12,1 - 12.М , группа элементов 25.1 - 25.8 предназначена для Формирования импульсов опроса регистров записи,Первая группа 26,1 - 26.,й шинныхФормирователей предназначена дляпередачи данных и начального адресамикропрограммы"при передаче управления на другое микропрограммное1142832 4 Вторая группа 27.1 - 27.Й шинных М=Ч х Л.формирователей предназначена рпя пе- если в соответствующем разряде поля 5 регистра 3 за.вписана "1"К. - если в соответствующем где 3устройство управления (МПУУ) модуля распределенной вычислительной системы с контролеМ,редачи признака АМП и номера моду. - ляН,при передаче управления на другое МПУУ.Третья группа 28.1 - 28,М шинных Формирователей предназначена для приема информации из шины 41 переда чи данных.Четвертая группа 29.1 - 29.К шинных формирователей предназначена для приема информации из шины 42 адреса. Группа элементов ИЛИ-НЕ 30.130. М служит для формирования управляющих сигналов при наличиисвободных шин 41 и 42.20Элемент ИЛИ 32 предназначендля Формирования импульса сбросасчетчика 16 выборки. Триггер 33 режимов работы служит для задания режимов работы МПУ. Триггер 34 управления предназначен для управленияработой генератора 35 синхроимпульсов. Генератор 35 синхроимпульсовФормирует на своих выходах две последовательности"сдвинутых друг отно-сительно друга синхроимпульсовив.Шина 41 (фиг. 1 и Фиг, 2) передачи данных предназначена для передачи данных и начальных адресов передачи управления А другим аналонаучгичным МПУУ,Шина 42 (фиг. 1 и 2) передачиадреса служит для передачи признака,АМП и передачи номера модуля М модуля.Блок 2 (Фиг. 3) формирования 40адреса микрокоманд предназначен дляформирования исполнительного адресаочередной микрокоманды. С входа 39устройства на вход коммутатора 47:поступает начальный адрес основноймикропрограммы при передаче управления на данные МПУУ, На входы 50.150.М блока 2 поступают признаки АМП,соответствующие АМП, хранящимсяв блоке 1 постоянной памяти (фиг. 1) . ОШифратор 4 б определяет начальныйадрес АМП или СМП (в зависимостиот передачи данных на данный модуль)и посылает его на коммутатор 47.Последний в зависимости от потенциала на входе 52 комментирует прохозсдение информации на вход блока элементов ИЛИ 45. Мультиплексор 49 реализует следующую логическую Функциюгде ; - значение ;-го логического условия на входе 38; разряде поля 5 регистра 3 записан "0",в - разрядность кода логических условий, поступающих на вход блокаФормирования адреса;о - разрядность значенийлогических условий,поступающих на вход 38МПУУ, причем и с 2Элемент"ИЛИ 44 предназначен длямодификации разряда адреса следующей микрокоманды в соответствии созначениями проверяемого логическогоусловия.Блок элементов ИЛИ 45 Формируетисполнительный адрес микрокоманды,а регистр 48 служит для его записи,Блок 18 (Фиг. 4) предназначендля управления пуском устройства,Элемент И 53 служит для Формированиясигнала пуска устройства при передаче управления на данное устройство.Дешифратор 54 Формирует на своемвыходе управляющие сигналы при совпадении кода признака АМП с кодом,который он преобразует. Если в распределенной вычислительной системес контролем общее количество СМП иАМП равно К и за данным модулемзакреплено и СМП и АМП, то дешифратор 54 имеет и выходов,а количестворазрядов кода признака АМП, передающегося по шине адреса, равно 0 о К.Элемент ИЛИ 55 предназначен дляформирования сигнала пуска при передаче управления на данное устройствопри выполнении АМП. Элемент ИЛИ 5 бФормирует сигнал пуска устройствапри внешнем запуске устройства,передаче управления с другогомикропрограммного устройства управления модуля распределенной вычисли

СмотретьЗаявка

3587382, 04.05.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, НИКОЛЬСКИЙ СЕРГЕЙ БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/30, G06F 9/22

Метки: контролем, микропрограммное

Опубликовано: 28.02.1985

Код ссылки

<a href="https://patents.su/16-1142832-mikroprogrammnoe-ustrojjstvo-upravleniya-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления с контролем</a>

Предыдущий патент: Управляемый датчик случайных чисел

Следующий патент: Микропрограммное устройство управления

Случайный патент: Электрохимический способ умягченияводы