Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

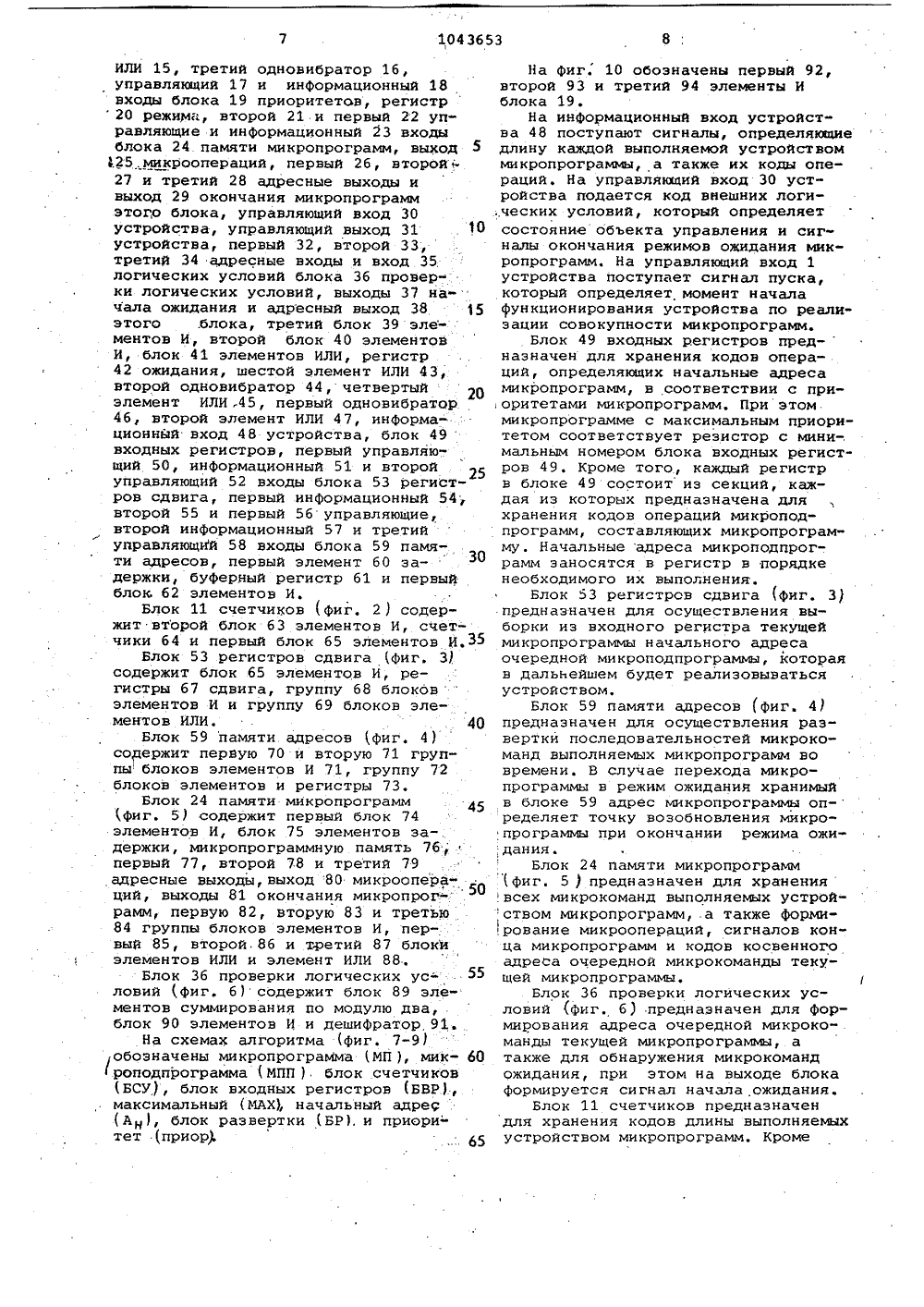

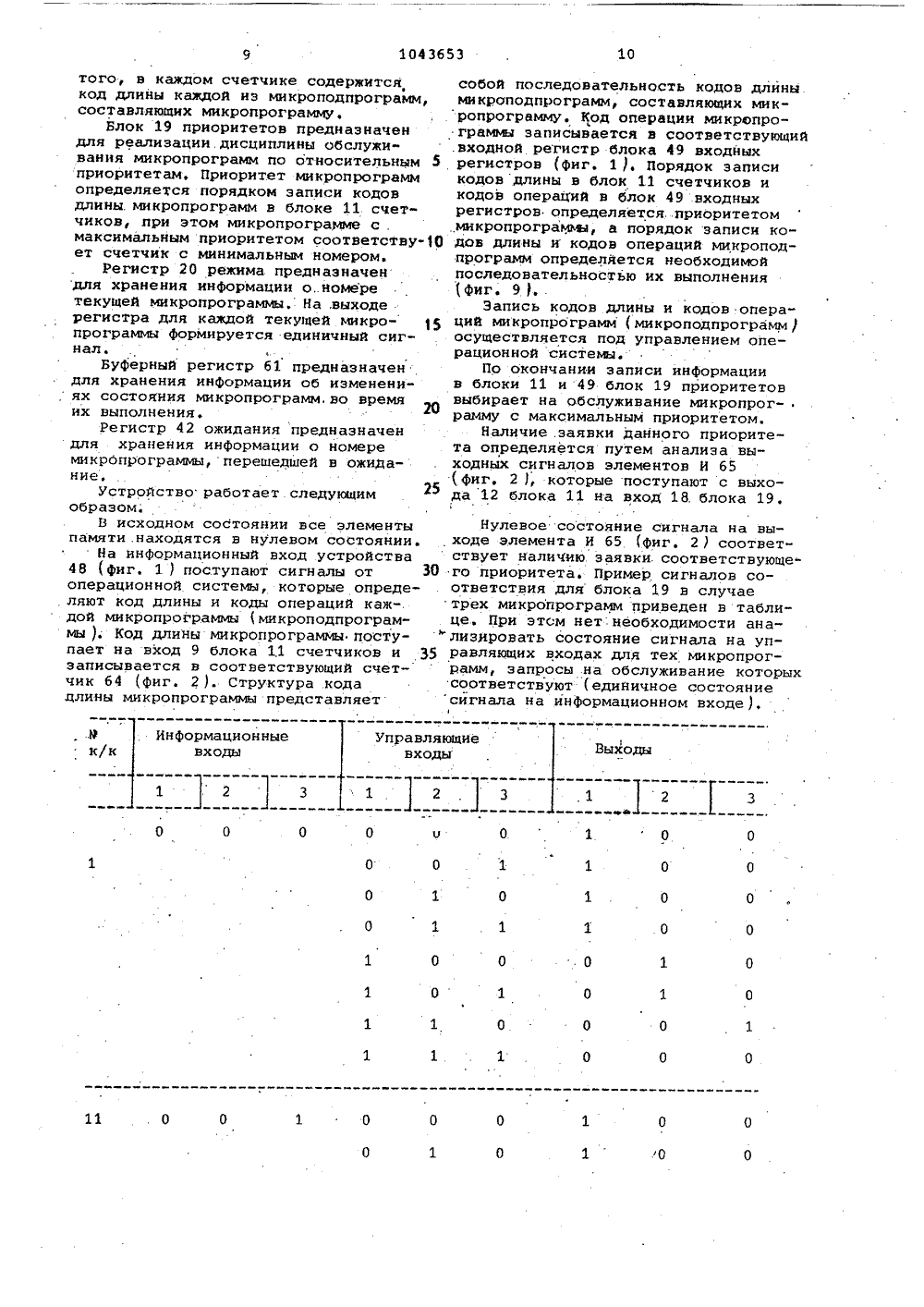

53 А СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9/2 ПИСАНИ БРЕ о ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ВТОРСНОМУ СВИДЕТЕЛЬСТВУ(56) 1. Патент США Р 3636522,кл. 340-172, 18,01.72.2, Авторское свидетельство ССВ 583434, кл, 0 06 Г 9/22, 1977(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блоксчетчиков, блок входных регистров,блок памяти адресов, блок памятимикропрограмм, первый блок элементовИ, блок элементов ИЛИ, генераторимпульсов, элемент И, триггер пускаи первый элемент ИЛИ, причем входпуска устройства соединен с первымуправляющим входом блока памяти адресов и первым входом первого. элемента ИЛИ, выход которого подключен кединичному входу триггера пуска,выход блока памяти адресов соединенс адресным входом блока памяти микропрограмм,выход микроопераций которого является выходом устройства,выход генератора импульсов соедийенс первым входом первого элемента И,второй вход которого соединен с единичным выходом триггера пуска, выход элемента И соединен с первымуправляющим входом блока счетчиков,выход блока элементов И соединен свходами блока элементов ИЛИ, информационный вход устройства соединенс входом блока входных регистров,о т л и ч а ю щ е е с я тем, что,.с целью повышения быстродействия,в него введены второй, третий, четвертый и пятый элементы ИЛИ, первый,второй и третий элементы задержки,первый, второй и третий одновибраторы, блок приоритетов, регистр режима, блок регистров сдвига, регистр ожидания, второй и третий блокиэлементов И, буферный регистр и блокпроверки логических условий, причемадресные выходы и выход ожиданияблока проверки логических условийсоединены с первыми входами соответственно второго и третьего блоковэлементов И, выход которого соединен.с первым входом блока элементов ИЛИ,выход регистра режима соединен спервым управляющим входом блока памяти микропрограмм, .вторым управляющим входом блока памяти адресов,первым управляющим входом блока регистров сдвига, вторыми входами второго и третьего блоков элементов Ии вторым управляющим входом блокасчетчиков информационный вход которого соединен с информационным вхо- ффдом устройства, выход второго блока ффэлементов И соединен с первым инфор- (мационным входом блока памяти адре-сов, второй информационный вход ка-,. Яторого подключен к выходу блока регистров сдвига, третий управляющий Ывход блока памяти адресов соединенс выходом окончания микропрограммыблока памяти микропрограмм, вторым ф,управляющим входом блока регистровсдвига, первыми входами второго и Ффтретьего элементов ИЛИ, информаци н- фный вход блока регистров сдвига сое- в-динен с выходом блока входных регистров, выход четвертого элемента фИЛИ соединен с вторыми входами второго и третьего элементов ИЛИ, пер-вым входом первого блока элементовИ и через первый элемент задержкисоединен с нулевым входом .буферного юсефрегистра, единичный вход буферногорегистра соединен с управляющимвходом устройства и входом логических условий блока проверки логических условий, выход буферноГо регистра соединен с вторым входом первогоблока элементов И, выход второгоэлемента ИЛИ через второй элемент104 3653 У 7 т Заказ 7339/52ВНИИП Тираж 706 Подписосударственного комитета СССРелам изобретений ы открытийсква, Ж, Раушская наб., д. е. 13035 Эилиал ППП "Патент", г. Ужгород, ул. Проектная, 4 Составитель И,СигаловГ,Безвершенко Техред С.Мигунова КорректорЛ. БокшанФее е а Фш аааааае е аа аеашее а1043653 задержки соединен с вторым входомпервого элемента ИЛИ, выход третьего элемента ИЛИ соединен с нулевымвходом триггера пуска, первый управляющий выход блока счетчиков черезпервый одновибратор подключен ктретьему входу третьего элементаИЛИ, группа управляющих выходов блока счетчиков соединена с входамипятого элемента ИЛИ и группой нходовблока приоритетов, управляющий входкоторого соединен с выходом регистра ожидания и входами шестого элемента ИЛИ, выход шестого элементаИЛИ через второй одновибратор соединен с первым входом четвертого эле 1Изобретение относится к вычислительной технике и может быть использовано в вычислительной технике для построения микропрограммных систем.Известно устройство программного управления для систем дальней телефонной связи, содержащее блок регист-, ров, дешифраторы микропрограммную память, элементы И и ИЛИ, генератор импульсов и блок развертки1 ).Недостатком этого устройства является низкая производительность, обусловленная длительным выбором микропрограмм для выполнения.Наиболее близким по технической сущности и достигаемому эффекту к изобретению является микропрограммное устройство управления, содержащее блок счетчиков, блок входных регистров, блок развертки, блок ламяти адресов блок памяти микропрограмм, 20 блок элементов И, блок элементов ИЛИ, генератор импульсов, элемент И, триггер пуска, элемент ИЛИ выход которого подключен к единичному входу триггера пуска, а первый вход к управляющим входам устройства и блока развертки, выход которого соединен, с информационным входом блока памяти микропрограмм, выход микро- операций которого соединен с выходом 30 устройства. Выход генератора импульсов соединен с первым входом элемента И, второй вход которого соединен с единичным выходом триггера пуска. Выход элемента И соединен с Управ ляющим входом блока счетчиков, выход блока элементов И с первым входом блока элементов ИЛИ, вход блока входных регистров - с информационным входом устройства Г 2 3.40Недостатками этого устройства являются значительные временные затраты на выборку и реализацию микропр. грамм н произвольной последовамента ИЛИ, второй вход которого подключен к выходу третьего одновибратора, вход третьего одновибраторасоединен с выходом пятого элементаИЛИ, выход блока приоритетов соединен с входом регистра режима, выходэлемента И через третий элемент задержки соединен с нторым управляю"щим входом блока памяти микропрограмм, первый, второй и третий адресные выходы блока памяти микропрограмм соединены соответственно с первым, вторым 6 третьими адреснымивходами блока проверки логическихусловий, а выход блока элементов ИЛИсоединей с входом регистра ожидания. 3тельности для каждого цикла работы,а также узкая область примененияустройства.Эти недостатки обусловлены тем,что переход к выполнению очередноймикроподпрограммы после окончаниявыполнения любой предыдущей жесткопредопределен заложенной в схемеустройства организацией включенияМикропрограмм в соответствии с заранее заданными частотами обращения кподпрограммам в течение цикла работы процессора, При этом приоритетмикропрограммы также жестко фиксирован и определяется частотой обращения к ней.Поэтому в случае необходимостивыполнения микропрограммы с другим,отличным от заданного, приоритетомнеобходимо вводить "холостые" циклы работы устройства, Так, например,если необходимо реализовать микропрограмму, фиксированную н устройстве как микропрограмму с низшим приоритетом, требуется осуществить запись заявки только в младший входной регистр, Далее устройство должно "фиктивно" ( без развертки ) отработать микропрограммы старших приоритетов,Наихудшую оценку времени выполнения всех микропрограмм ( цикла работы устройства )можно получить дляслучая, когда требуется выполнитьвсе заложенные в устройство микропрограммы с обратным (инверсным )приоритетом,Таким образом, высокое значениевыполнения всех микропрограмм обуславливает большое время выборки и реализации микропрограмм и недостаточную область применения устройства. Цель изобретения - повышениебыстродействия устройства.Цель достигается тем, что в устройство управления, содержащее блоксчетчиков, блок входных регистров,блок памяти адресов, блок памятимикропрограмм, блок элементов И,блок элементов ИЛИ, генератор импуль,сов, элемент И, триггер пуска ипервый элемент ИЛИ, причем выходпуска устройства соединен с первымуправляющим входом блока памяти адресов и первым входом первого элемента ИЛИ, выход которого подключенк единичному входу триггера пуска,выход блока памяти адресов соединенс адресным входом блока памяти микпропрограмм, выход микроопераций которого является выходом устройства,выход генератора импульсов соединенс первым входом первого элемента И,второй вход которого соединен седииичным выходом триггера пуска,выход элемента И соединен с первымуправляющим входом блока счетчиков,выход первого блока элементов Исоединен с входами блока элементовИЛИ, инФормационный вход устройствасоединен с входом блока входных регистров, введены второй, третий,четвертый и пятый элементы ИЛИ, пер"вый, второй и третий элементы задержки, первый, второй и третий одновибраторы,блок приоритетов, регистр режима, блок регистров сдвига,регистр ожидания, второй и третийблоки элементов И, буферный регистр,блок проверки логических условий,причем адресные выходы и выход ожидания блока проверки логических условий соединены с первыми входамисоответственно второго и третьегоблоков элементов И., выход которогосоединен с первым входом блока 40элементов ИЛИ, выход регистра режимасоединен с первым управляющим входом блока памяти микропрограмм,. вторым управляющим входом блока памяти.адресов, первым управляющим входом 45блока регистров сдвига, вторыми входами второго и третьего блоков элементов И и вторым управляющим входомблока счетчиков, информационный входкоторого соединен с информационнымвходом устройства, выход второгоблока элементов И соединен с первыминформационным входом блока памятиадресов, второй информационнцйвход которого подключен к выходублока регистров сдвига, третий управляющий вход блока памяти адресовсоединен с выходом окончания микро-,программы блока памяти микропрограмм,вторым управляющим входом блока регистров сдвига, первыми входами 60второго и третьего. элементов ИЛИ,информационный вход блока регистровсдвига соединен с выходом блока1 входных регистров, выход четвертого1элемента ИЛИ соединен с вторыми вхО.- 65 дами второго и третьего элементовИЛИ, первым входом первого блокаэлементов И и через первый элементзадержки соединен с нулевым входомбуферного регистра, единичный входбуферного регистра соединен с управляющим входом устройства.и входомлогических условий блока проверкилогических условий, выход буферногорегистра соединен с вторым входомпервого блока элементов И, выход второго элемента ИЛИ через второй элемент задержки соединен с вторым входом первого элемента ИЛИ, выходтретьего элемента ИЛИ соединен с нулевым входом триггера пуска, первыйуправляющий вход блока счетчиковчерез первый одновибратор подключенк третьему входу третьего элементаИЛИ, группа управляющих выходов бло-ка счетчиков соединена с входами пятого элемента ИЛИ и группой входовблока приоритетов, управляющий входкоторого соединен с выходом регистраожидания и входами шестого элементаИЛИ, выход шестого элемента ИЛИ через второй одновибратор соединен спервым входом четвертого элементаИЛИ," второй вход которого подключенк выходу третьего одновибратора,вход третьего одновибратора соединенс выходом пятого элемента ИЛИ, выходблока приоритетов соединен с входомрегистра режима, выход элемента Ичерез третий элемент задержки соединен с вторым управляющим входом блока памяти, микропрограмм, первый,второй и третий адресные выходы блока памяти микропрограмм соединенысоответственно с первым, вторым итретьеим адресными входами блокапроверки логических условий, а выходблока элементов ИЛИ соединен с входом регистра ожидания,Изобретение обеспечивает повышение быстродействия устройствапутемреализации дисциплины обслуживаниямикропрограмм по относительным приоритетам с полезным использованием времени ожидания микропрограмм, Утилизация режимовожидания обеспечиваетсяв устройстве введением блока проверки логических условий, блока регистров сдвига, второго и третьего блоков элементов И, регистра ожидания,буферного регистра, второго, третьего, четвертого, пятого и шестогоэлементов ИЛИ, второго и третьегоодновибраторов, первого, второго итретьего элементов задержки и соответствующих связей,Устройство предназначено для реализации совокупности микропрограмм,каждая их которых представляетсяпоследовательностью микроподпрограмм.В предлагаемом устройстве кодыдлины микроподпрограмм, составляющих микропрограмму данного приоритета, заносятся в соответствующий счет.,чик числа,микрокоманд блока счетчиков. При этом приоритет микропрограмьы определяется положением кода, ее длины в блоке счетчиков.: наивысшему приоритету микропрограммы соответствует счетчик числа микрокоманд с наименьшим (первым ) номером в блоке счетчиков.Счетчикам микрокоманд в блоке счетчиков сооветствуют входные ре гистры в блоке входных регистров, в каждый из которых записываются коды операций последовательности микрбподпрограмм, составляющих соответствующую микропрограмму, 15формирование совокупности микро.- программ, которая, будет реализована устройством в данном цикле работы, осуществляется до поступления сигнала пуска. По поступлении сигнала рО пуска устройство переходит к реализации совокупности готовых микропрограмм,которая определяется содержимым блока счетчиков и блока входных регистров, При этом поступление заявок на обслуживание прекрацается до окончания реализации этой совокупности микропрограмм (цикл работы ), после чего возможно, заполнение входных регистров и счетчиков микро" команд информацией о новой совокупности микропрограмм.Сущнбсть новой дисциплины обслуживания заявкок по относительным приоритетам с утилизацией полезным использованием ) времени ожидания микропрограмм состоит в следующем.При пуске устройства начальные .адреса всех микропрограмм заносятся в регистры блока развертки, Выбор микропрограммы с наивысшим приорите том из совокупности готовых микропрограмм осуществляется блоком приоритетов.Во время выполнения текущей мик-. ропрограммы могут произойти следующие три события: закончиться текуцая микропрограмма; закончиться одна из микроподпрограмм текуцей микропрограммы; начаться режим ожидания текущей микРопРогРаммы. ОВ первом случае осуществляется .блокирование адресных цепей записи и считывания для закончившейся текущей микроПрограммы, а блок приоритетов выбирает на обслуживание очередную по приоритету микропрограмму и устройство переходит к ее реализации. Если же закончившаяся микропрограмма была последней в реализуемой совокупности микропрограмм, устройство прекращает работу, далее цикл бО Функционирования повторяется для новой совокупности микропрограмм.В случае окончания одной из микро" подпрограмм текущей микропрограммы выбирается начальный адрес очередной у мйкроподпрограммы текуцей микропрограммы и устройство переходит к реализации этой микроподпрограммы (продолжает реализацию текущей микропрограммы,). Если закончившаяся микро- .подпрограмма была последней в последовательности микроподпрограмм текуцей микропрограммы .(т,е. закончилась текущая микропрограмма ), устрой-, .ство функционирует аналогично описанному.В случае начала режима ожидания текущей микропрограммы .в устройстве предусмотрена возможность выполнения готовых микропрограмм, приоритет которых ниже, чем в текуцей.При этом блок приоритетов выбирает на обслуживание микропрограмму с ближайшим высшим приоритетом (она становится текущей ) и устройство реализует ее аналоги по описанному,В процессе выполнения этой микропрограммы также может возникнуть ожидание ( вложение ожиданий). При этом выбор на обслуживание очередной по приоритету микропрограммы осуществляется аналогично рассмотренномуеВозобновление микропрограммы после окончания ее режима ожидания возможно в случае начала режима ожидания текущей микропрограммы, а также в случае окончания выполнения текущей микропрограммы.В обоих случаях блок приоритетов выбирает на обслуживание микропрограмму с высшим приоритетом, т.епри дообслуживании также реализуется дисциплина обслуживания по относительным приоритетам.Таким образом, новая дисциплина функционирования устройства позволяет существенно снизить суммарное время выборки и реализации микро- . программ.Нафиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - схема блока счетчиков; на фиг, 3 - схема блока регистров,сдвига; на Фиг. 4 в схема блока памяти адресов; на фиг. 5 схема блока памяти микропрограмм; на фиг,6 - схема блока проверкй логических условий;на фиг. 7-9 - схема алгоритма Функционирования устройства; на фиг. 10 - функциональная схема блока приоритетов.Устройство (Фиг. 1) содержит вход 1 пуска устройства, второй элемент ИЛИ 2, второй элемент 3 задержки, первый элемент ИЛИ 4, триггер 5 пуска, генератор 6 тактовых импульсов, первый элемент И 7, первый управляющий 8, информационный 9 и второй управляющий 10 входы блока 11 счетчиков, второй 12 и первый 13 управляющие выходы блока 11, третий элемент 14 задержки, пятый элементИЛИ 15, третий одновибратор 16,управляющий 17 и информационный 18входы блока 19 приоритетов, регистр20 режима, второй 21 и первый 22 управляющие и информационный 23 входыблока 24 памяти микропрограмм, выход 525.микроопераций, первый 26, второй:27 и третий 28 адресные выходы ивыход 29 окончания микропрограммэтого блока, управляющий вход 30устройства, управляющий выход 31 10устройства, первый 32, второй 33,третий 34 адресные входы и вход 35.логических условий блока 36 проверки логических условий, выходы 37 начала ожидания и адресный выход 38 15этого .блока, третий блок 39 элементов И, второй блок 40 элементовИ, блок 41 элементов ИЛИ, регистр42 ожидания, шестой элемент ИЛИ 43,второй одновибратор 44,четвертыйэлемент ИЛИ,45, первый одновибратор46, второй элемент ИЛИ 47, информационный вход 48 устройства, блок 49входных регистров, первый управляющий 50, информационный 51 и второйуправляющий 52 входы блока 53 регистров сдвига, первый информационный 54,второй 55 и первый 56 управляющие,второй информационный 57 и третийуправляющий 58 входы блока 59 памяти адресов, первый элемент 60 задержки, буферный регистр 61 и первыйблок 62 элементов И.Блок 11 счетчиков ( Фиг, 2 ) содержит второй блок 63 элементов И, счетчики 64 и первый блок 65 элементов И.З 5Блок 53 регистров сдвига (Фиг. 3)содержит блок 65 элементов И, регистры 67 сдвига, группу 68 блоковэлементов И и группу 69 блоков элементов ИЛИ. 40Блок 59 памяти адресов (фиг. 4)содержит первую 70 и вторую 71 группы блоков элементов И 71, группу 72блоков элементов и регистры 73.Блок 24 памяти микропрограмм 45(фиг, 5) содержит первый блок 74элементов И, блок 75 элементов задержки, микропрограммную память 76,первый 77, второй 78 и третий 79адресные выходы, выход 80 микроопераций, выходы 81 окончания микропрог:-рамм, первую 82, вторую 83 и третью84 группы блоков элементов И, пер- .вый 85, второй.86 и третий 87 блокиэлементов ИЛИ и элемент ИЛИ 88.Блок 36 проверки логических ус-ловий (фиг, 6) содержит блок 89 элементов суммирования по модулю два,блок 90 элементов И и дешифратор,91.На схемах алгоритма (фиг. 7"9)обозначены микропрограмма (МП ), микроподпрограмма ( МПП ). блок счетчиков(БСУ), блок входных регистров (БВР),максимальный (МАХ), начальный адрес( Ан), блок развертки (БР),и приори-тет (приор65 На фиг. 10 обозначены первый 92,второй 93 и третий 94 элементы Иблока 19,На информационный вход устройства 48 поступают сигналы, определяющиедлину каждой выполняемой устройствоммикропрограммы, а также их коды операций. На управляющий вход 30 устройства подается код внешних логи,ческих условий, который определяетсостояние объекта управления и сигналы окончания режимов ожидания микропрограмм. На управляющий вход 1устройства поступает сигнал пуска,который определяет момент началафункционирования устройства по реализации совокупности микропрограмм.Блок 49 входных регистров пред-назначен для хранения кодов операций, определяющих начальные адресамикропрограмм, в соответствии с приоритетами микропрограмм, При этоммикропрограмме с максимальным приоритетом соответствует резистор с мини-.мальным номером блока входных регистров 49. Кроме того, каждый регистрв блоке 49 состоит из секций, каждая из которых предназначена дляхранения кодов операций микроподпрограмм, составляющих микропрограмму. Начальные адреса микроподпрог-.рамм заносятся в регистр в порядкенеобходимого их выполнения.Блок 53 регистров сдвига (фиг, 3)предназначен для осуществления выборки из входного регистра текущеймикропрограммы начального адресаочередной микроподпрограммы, котораяв дальнейшем будет реализовыватьсяустройством.Блок 59 памяти адресов (фиг. 4)предназначен для осуществления развертки последовательностей микрокоманд выполняемых микропрограмм вовремени, В случае перехода микропрограммы в режим ожидания хранимыйв блоке 59 адрес микропрограммы оп-ределяет точку возобновления микропрограммы при окончании режима ожи,дания.Блок 24 памяти микропрограмм(фиг, 5 ) предназначен для хранениявсех микрокоманд выполняемых устройством микропрограмм, а также форми 1 рование микроопераций, сигналов конца микропрограмм и кодов косвенногоадреса очередной микрокоманды текущей микропрограммы, /Блок 36 проверки логических условий (фиг. 6) предназначен для формирования адреса очередной микрокоманды текущей микропрограммы, атакже для обнаружения микрокомандожидания, при этом на выходе блокаформируется сигнал начала ожидания.Блок 11 счетчиков предназначендля хранения кодов длины выполняемыхустройством микропрограмм. КромеВыходы 1 231 2, 3 О О О О О О фО О того, в каждом счетчике содержитсякод длины каждой иэ микроподпрограмм,составляющих микропрограмму.Блок 19 приоритетов предназначендля реализации дисциплины обслуживания микропрограмм по относительным 5приоритетам, Приоритет микропрограммопределяется порядком записи кодовдлины. микропрограмм в блоке 11 счетчиков, при этом микропрограмме смаксимальным приоритетом соответству-Оет счетчик с минимальным номером.Регистр 20 режима предназначендля хранения информации о,.номеретекущей микропрограммы, На,выходерегистра для каждой текущей микропрограммы Формируется единичный сигнал.Буферный регистр 61 предназначендля хранения информации об изменени.ях состояния микропрограмм,во времяих выполнения,Регистр 42 ожидания предназначендля хранения информации о номеремикропрограммы, перешедшей в ожидание,Устройство работает следующимобразом,В исходном состоянии все элементыпамяти .находятся в нулевом состоянии.На информационный вход устройства4 В (фиг. 1 ) поступают сигналы от 30операционной системы, которые опреде.ляют код длины и коды операций каждой микропрограммы (микроподпрограммы ); Код длины микропрограммы поступает на вход 9 блока 11 счетчиков и 35записывается в соответствующий счетчик 64 (фиг. 2 ). Структура кодадлины микропрограммы представляет собой последовательность кодов длины микроподпрограмм, составляющих микропрограмму. Код операции микропрограммы записывается в соответствующий входной регистр блока 49 входных регистров (фиг. 1 ). Порядок записи кодов длины в блок 11 счетчиков и кодов операций в блок 49 входных регистров определяетсяприоритетом микропрограви, а порядок записи кодов длины и кодов операций микроподпрограмм определяется необходимой последовательностью их выполнения (Фиг. 9 ), .Эапись кодов длины и кодов операций микропрограмм (микроподпрограмм ) осуществляется под управлением операционной системы,По окончании записи информации в блоки 11 и 49 блок 19 приоритетов выбирает на обслуживание микропрограмму с максимальным приоритетом.Наличие .заявки данного приоритета определяется путем анализа выходных сигналов элементов И 65 ( фиг. 2 ), которые поступают с выхода 12 блока 11 на вход 18. блока 19. Нулевое состояние сигнала на выходе элемента И 65 (фиг. 2) соответствует наличию заявки. соответствующего приоритета. Пример сигналов соответствия для блока 19 в случае трех микропрограмм приведен в таблице. При этом нет:необходимости ана"лизировать состояние сигнала на управляющих входах для тех микропрограмм, запросы на обслуживание которых соответствуют (единичное состояние сйгнала на информационном входе),Вы 1 оды 1 1 1 2 3 1 2 О1 О 0 0 0 1 0 0 1 1 0 0 0 111 0 0 0 0 0 0 0 0 0 1 У0 1 0 0 0 О. 0 0 0 0 0 0 0 0 0 0 0 0 0: . 0 1 0 0 0 У 1 0: 1 0 0 0 0 0 0 0 0 У 11 0 0 0 0 0 Сигнал с выхода блока. 19 приоритетов устанавливает в единичное сос-. тояние соответствующий выбранной на обслуживание микропрограмме триггер в регистре 20 режима.Единичный сигнал с выхода регист-: ра 20 поступает на вход 22 блока .24, вход 10 блока 11, вход 50 блока 53, вход 55 блока 59 и разрешает прохождение информации в канале, соответствующем выбранной на обслуживание микропрограмме. 60По сигналу пуска, поступающему с входа 1 устройства, начальные адреса микропрограмм, записанных в блоке входных регистров, через блок 53 регистров сдвига поступают 65 1на вход 57 блока 59 и через элементы И 71 и ИЛИ 72 записываются в регистры 73 фиг. 4 ). Одновременно по сигналу пуска производится установка в единичное состояние триггера 5 пуска через элемент ИЛИ 4. Сигналом с единичного выхода триггера 5 открывается элемент И 7 и разрешается прохождение тактовых импульсов с генератора 6 на вход 8 блока счетчиков и через элемент 14 задержки на вход 21 блока памяти микропрограмм (фиг, 1 ), После этого устройство начинает реализацию выбранной на обслуживание (текущей )микропрограммы.Адрес микрокоманды текущей микропрограммы с выхода блока 59 поступает на вход 23 блока 24 памяти микропрограмм ( фиг. 5 ).С выхода 25 блока 24 на выход ,устройства 31 поступают сигналы микпоопераций. С адресных выходов 26- 28 блока 24 памяти микропрограмм 24 на входы 32-34 блока.36 проверки логических условий поступают соответственно коды логических условий, 10 коды неизменяемдй и модифицируемой логическими условиями части адреса микрокоманды текущей микропрограммы (фиг. 1 ).С адресного выхода 38 блока 36 15 код адреса очередной микрокоманды текущей. микропрограммы через коммутатор 40 поступает на вход 54 блока 59 памяти адресов и записывается в соответствующий регистр 73 через элементы ИЛИ блока 72 (фиг, 4).В процессе выполнения текущей микропрограммы возможны следующие ситуации (фиг, 7 ): закончилась текущая микропрограмма", закончилась микроподпрограмма в текущей микропрограмме; начался режим ожидания текущей микропрограммы;В первом случае (фиг. 1)по сигналу с выхода 12 блока 11, поступающему через элемент ИЛИ 15 на одновибратор 16, формируется сигнал перепланирования, который через элемент ИЛИ 47 устанавливает в нулевое состояние триггер 5 пуска на время, необходимое блоку 11 для 35 выбора очередной готовой микропрограммы на обслуживание (фиг. 11), Этим же сигналом через элемент ИЛИ 2 элемент 3 задержки и элемент ИЛИ 4 триггер 5 пуска устанавливается в .единичное состояние и устройство переходит к реализации очередной микропрограммы аналогично описанному. Если закончившаяся микропрограмма оказалась последней в совокупности микропрограмм, по сигналу с выхода 13 блока 11 через одновибратор 46 триггер 5 пуска устанавливается в нулевое состояние и устройство готово к приему новой совокупности микропрограмм,.В случае окончания микроподпрограммы текущей микропрограммы с выхода 29 .блока 24 снимается сигнал окончания микроподпрограмм, который поступает на вход 52 блока 53 и вход 58 блока 59 для реализации процедурывыбора очередной микроподпрограммы текущей микропрограммы на выпол нение (фиг. 7) . На время выбора микроподпрограммы запрещается прохождение тактовых импульсов с генератора б аналогично описанному.В блоке 53 (фиг, 3 ) сигнал окон,чания микроподпрограммы с входа 52 через элемент И бб поступает на 65 вход сдвигающего регистра 67, который перемещает записанную в нем единицу на один разряд. Сигнал с выхода регистра 67 открывает соответствующий блок элементов И 68 и началь-. ный адрес очередной микроподпрограммы через блок элементов ИЛИ 69 поступает на вход 53 сдвига.Далее начальный адрес очередной микроподпрограммы текущей микропрограммы записывается в регистры блока 59 ( фиг, 4 ), На входе 58 блока 59 подается сигнал окончания микроподпрограммы, который открывает соответствующий блок 70 элементов И и разрешает прохождение кода начального адреса очередной микроподпрограммы на запись в соответствующий регистр 73 через элементы И 71 и ИЛИ 72. По окончании процесса выборки очередной микроцодпрограммы и записи ее начального адреса в регистр 73 блока 59 (фиг. 1) триггер 5 пуска задержанным в цепи элемент ИЛИ 2 элемент 3 задержки - элемент ИЛИ 4 сигналом окончания микроподпрограммы с выхода 29 блока 24 устанавливается в единичное состояние и разрешает прохождение тактовых импульсов с генератора 6 через элемент И 7 в соответствующие блоки устройства. Устройство продолжает реализацию те" кущей микропрограммы.Если закончившаяся микроподпрограмма оказалась последней в текущей микропрограмме (фиг. 7 устройство выбирает на обслуживание очередную по приоритету микропрограмму аналогично описанному.В случае начала режима ожидания текущей микропрограммы (фиг, 7 и 8) устройство функционирует следующим образом. Сигнал начала ожидания с выхода 37 блока 36 поступает на вход блока 39 элементов И .и далее через элемент ИЛИ 41 устанавливает в еди- " ничное состояние соответствующий разряд в регистре 42 ожидания Единичный сигнал с выхода регистра 42 поступает на вход 17 блока приоритетов 19 и маскирует заявку микропрограммы, перешедшей в режим ожидания. По этому же сигналу с регистра 42 через элемент ИЛИ 43 одновибратор 44 формирует сигнал перепланирования, который позволяет выбрать на обслуживание очередную по приоритету микропрограмму аналогично рассмотренному. Выбранная таким рбразом микропрограмма на обслуживание становится текущей и выполняется устройством аналогично рассмотренному. Эта микропрограмма также может, иметь режимы ожидания, которые обрабатываются устройством аналогично рассмотренному.Если возникает ситуация, когда все микропрограммы (или последняя)находятся в режимах ожидания, функционирование устройства приостанавливается до окончания режима ожидания,В случае окончания режима ожидания микропрограммы с приоритетом стар 5 шим, чем у текущей, ее возобновление возможно только в следующих случаях (фиг. 8 ): начался режим ожи-. дания текущей микропрограммы; завершилось выполнение текущей микропрог раммы.Сигнал окончания ожидания микропрограммы с входа 30 устройства фиг, 1 ) поступает на вход регистра 61 и устанавливает в единичное сос тояние соответствующий разряд этого регистра. Состояние этого регистра не изменяется до возникновения ситуации перепланирования, т.е. завершения выполнения или начала режима ожидания текущей микропрограммы.. По сигналу перепланирования с элемента ИЛИ 45 открываются элементы И 62 и единичный сигнал с регистра 61 через элементы И 62 и ИЛИ 41 устанавливает в нулевое состояние соответствующий разряд в регистре 42. При этом снимается маскирующий сигнал с блока 19 приоритетовфиг. 10) и эта микропрограмма вновь выбирается на обслуживание. Задер- ЗО жанным на элементе 60 задержки сигналом перепланирования регистр 61 устанавливается в нулевое состояние.Применение дисциплины обслуживания микропрограмм по относительным приоритетам с утилизацией времени ожидания микропрограмм позволяет существенно сократитв время выполнения микропрограмм как старшего, так и младшего приоритета.Возможность изменять последовательность выполнения микропрограмм в каждом новом цикле работы устройства путем изменения приоритета микропрограмм существенно расширяет область применения устройства.Полезное использование режимов ожидания микропрограмм старших приоритетов для частичного или полного выполнения микропрограмм младших приоритетов приводит к снижению суммарного времени выполнения реализуемой совокупности микропрограмм.При этом дообслуживание микропрограмм по окончании их режимов ожидания производится с точки их последнего прерывания без потери информации.Применение предлагаемого устройс- тва при построении современных вычислительных систем позволит повы сить их производительность.

СмотретьЗаявка

3459922, 29.06.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ЯРМОНОВ ВИКТОР ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.09.1983

Код ссылки

<a href="https://patents.su/14-1043653-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Градирня