Система автоматического контроля параметров электронных схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1700538

Авторы: Бартоломей, Флейш

Текст

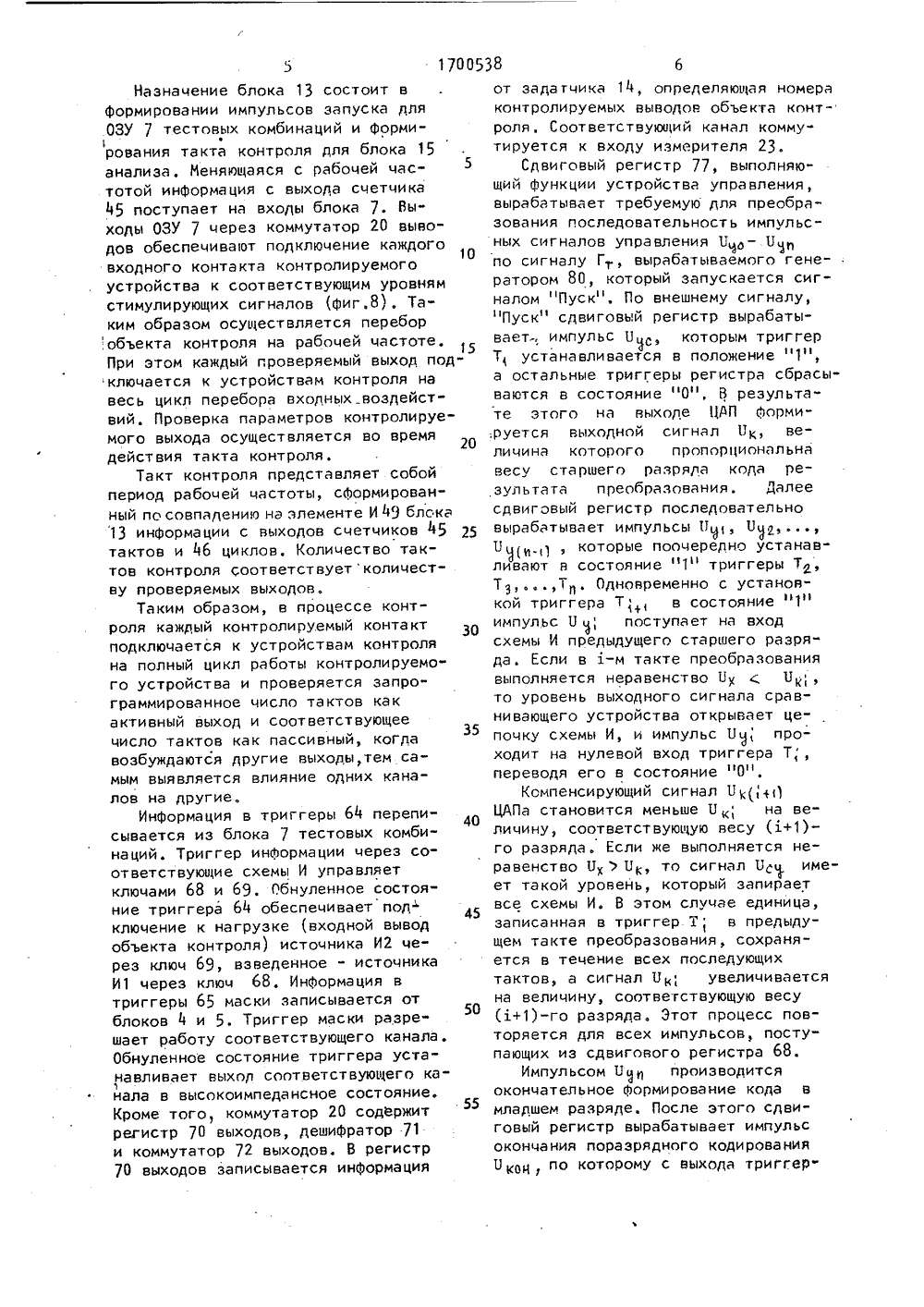

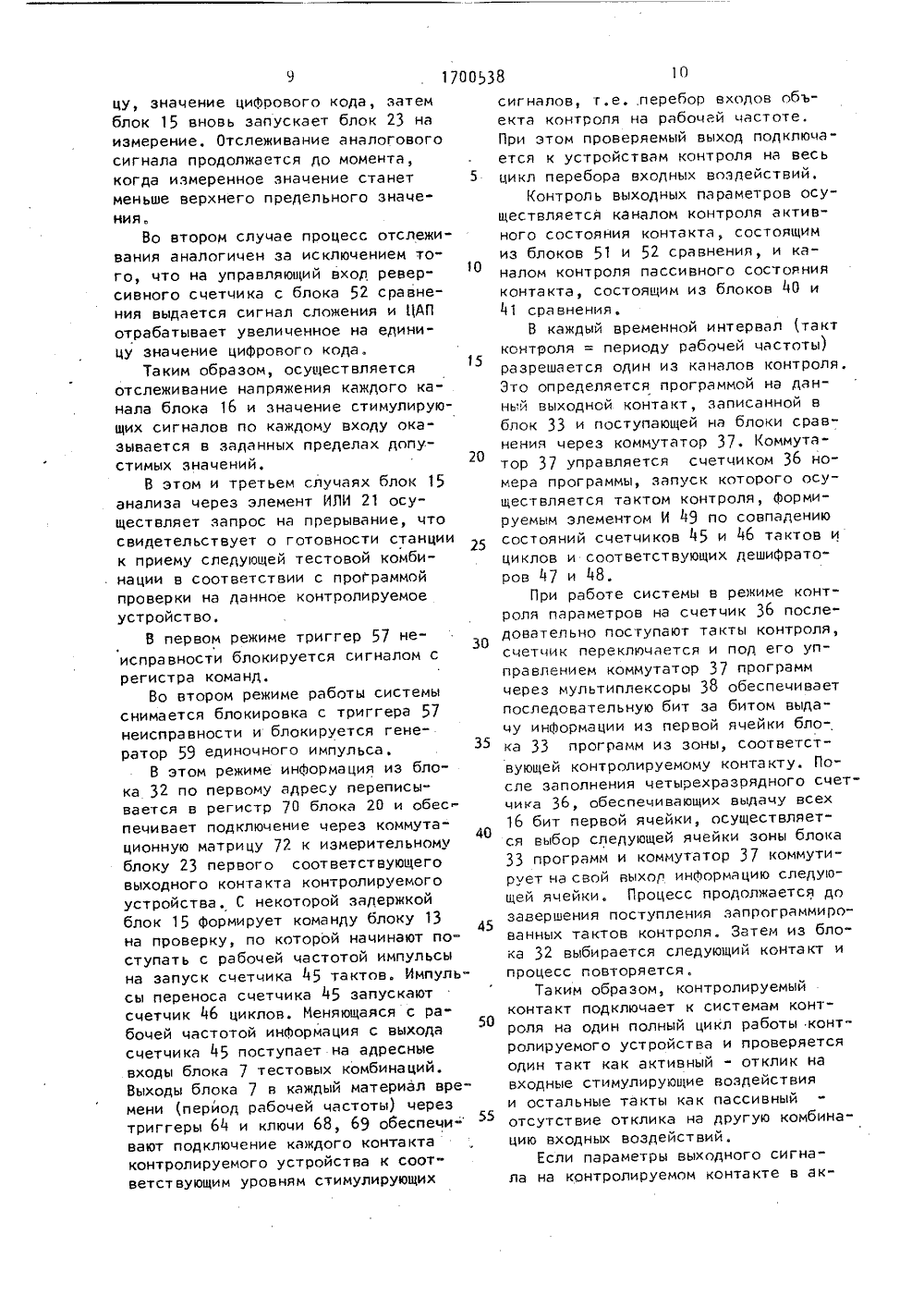

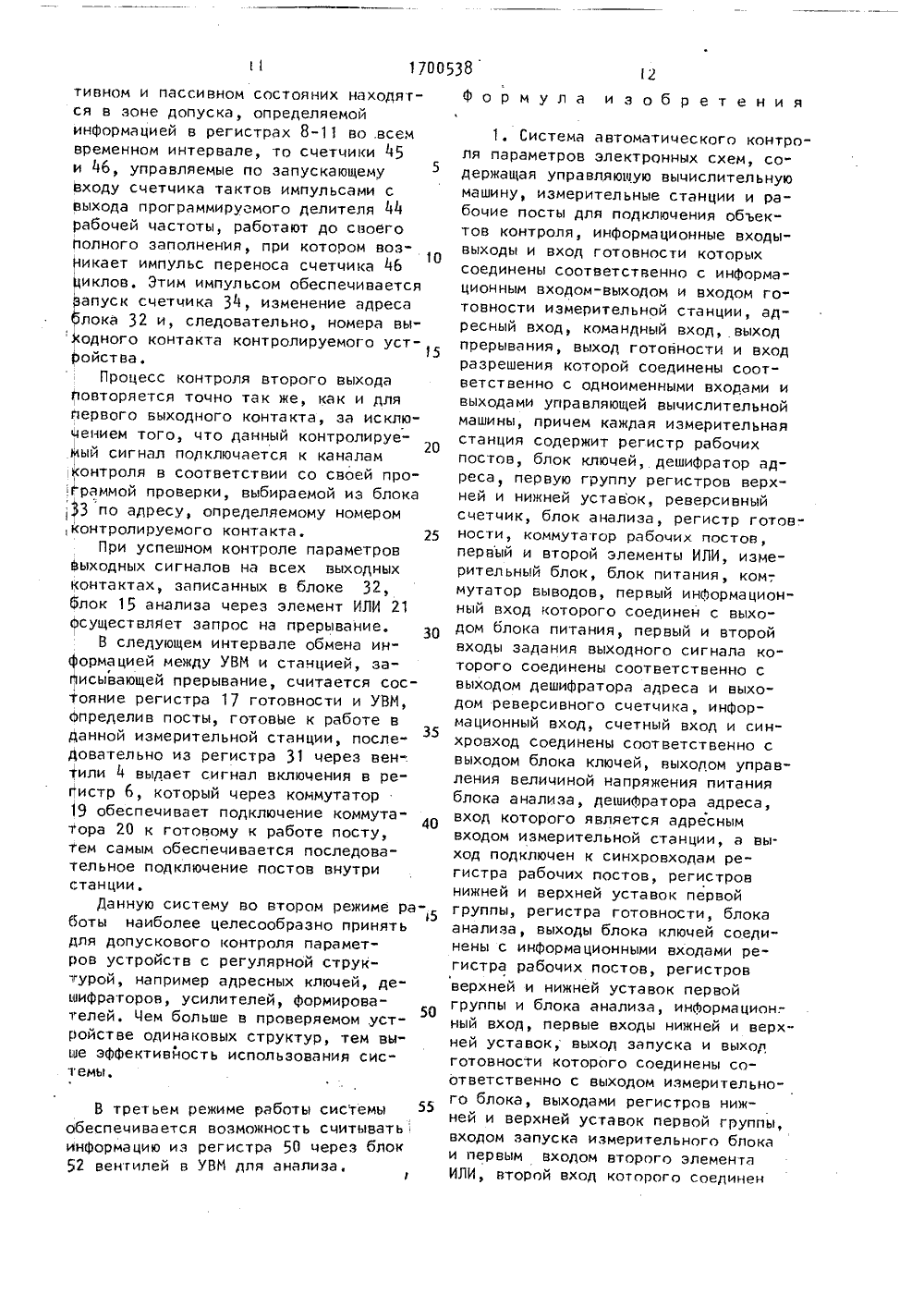

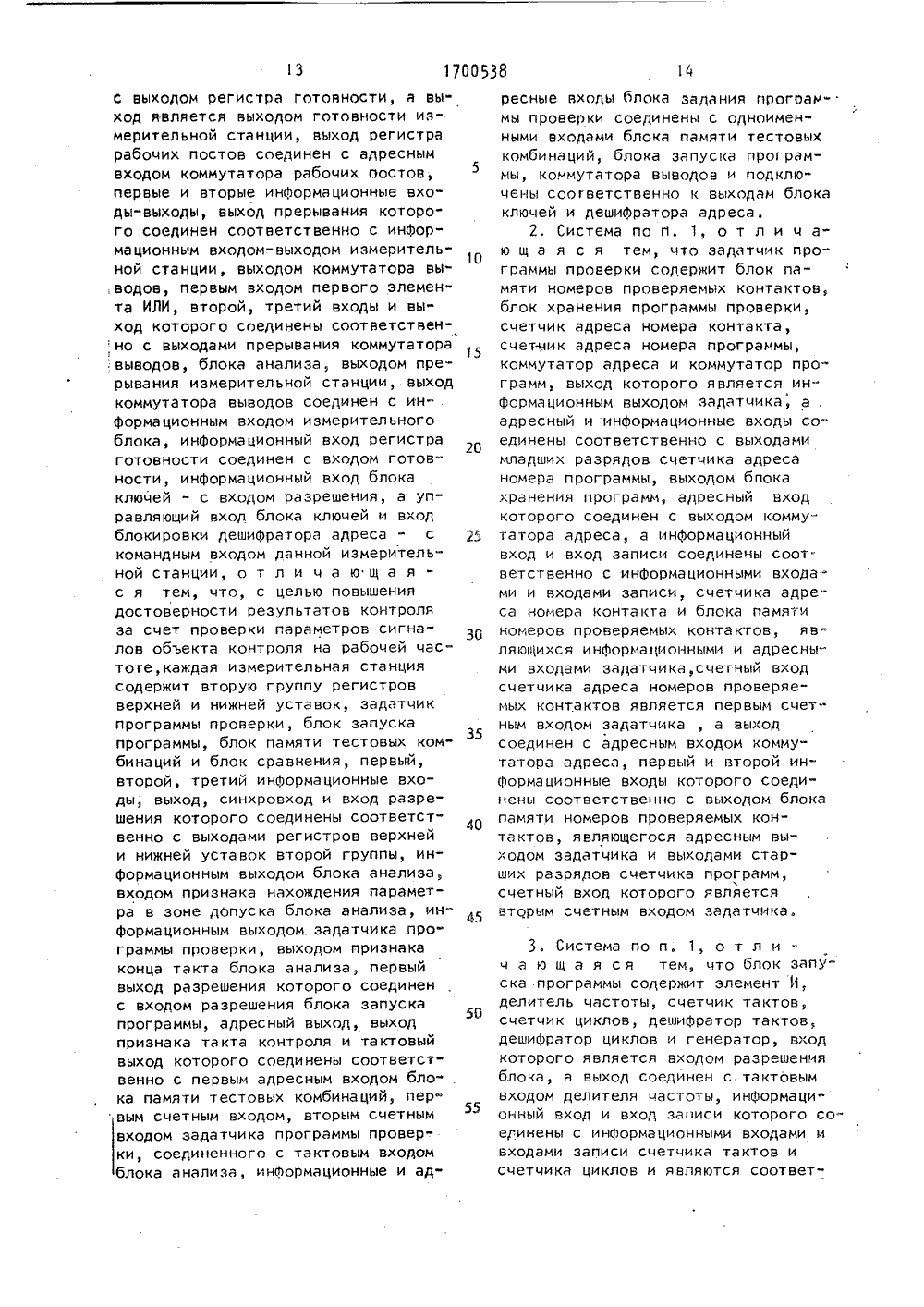

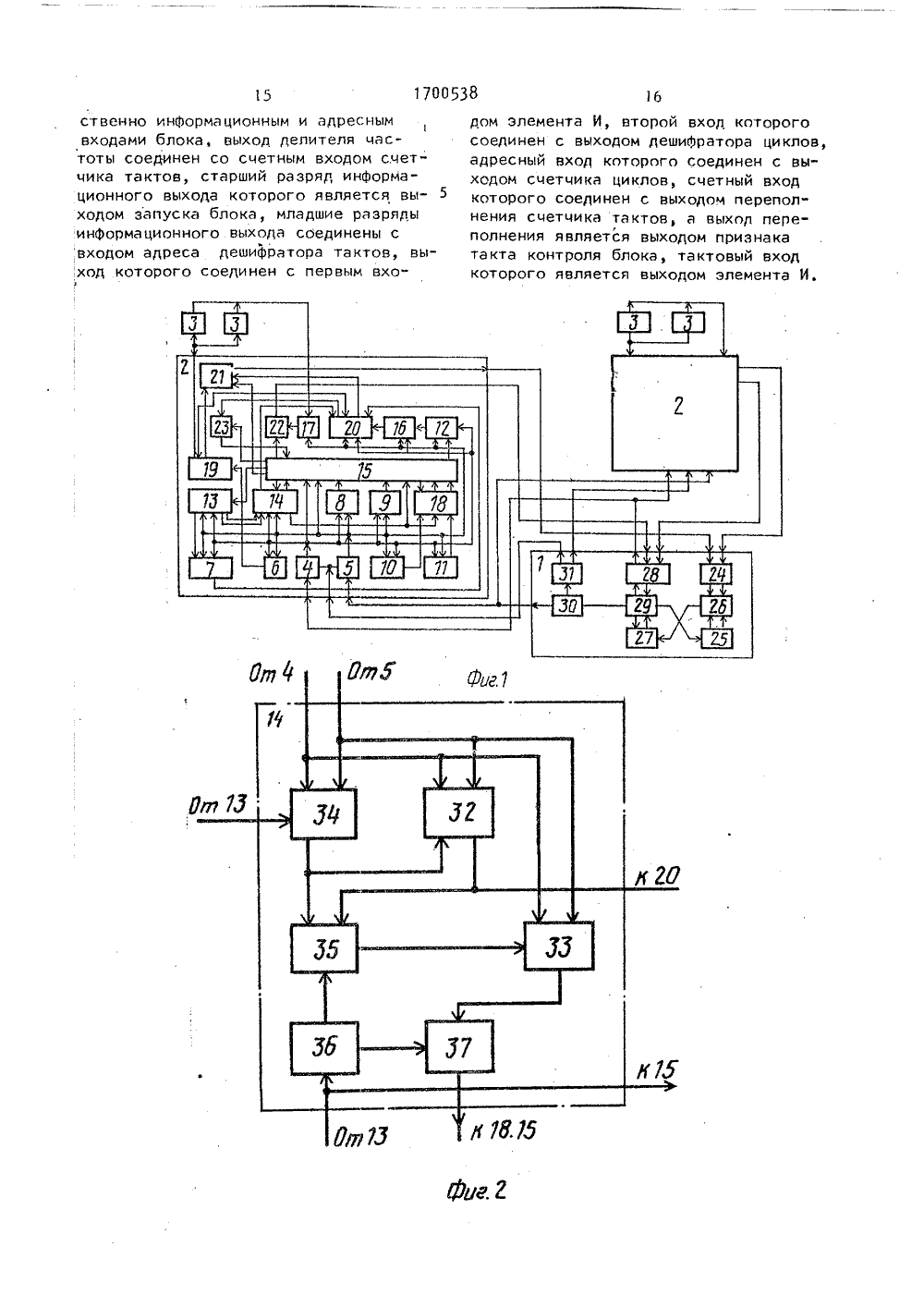

(191 111) 00 23/02 51) ЯМ ОБРЕТ ций,й 8 и ГОСУДАРСТВЕННЫЙ НОМПО ИЗОБРЕТЕНИЯМ И ОТНПРИ ГКНТ СССР ОПИСАНИЕ ИЗ АВТОРСКОМУ СВИДЕТЕ(56) Авторское свидетельство СССР й 302717, кл. Г. 06 Г 11/00, 1969.Авторское свидетельство СССР К 985764, кл. С 05 В 23/02, 1981 (прототип).(54) СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ (57) Изобретение относится к вычисли, тельной технике и может быть исполь" зовано в системах автоматического контроля параметров полупроводниковых приборов, интегральных схем,Изобретение относится к вычислительной технике и может быть исполь"зовано в системах автоматическогоконтроля параметров полупроводнико"вых приборов, интегральных схем, БИС,функциональных узлов, субблоков идругих электронных устройств,Цель изобретения - повышениедостоверности результатов контроляза счет проверки параметров сигналов контролируемого устройства нарабочей частоте,На фиг1 представлена функциональная схема системы автоматического контроля параметров электронныхсхем; на фиг, 2 - Функциональнаясхема задатчика программы проверки;на фиг,3 - структурная схема распределения адресов ОВУ программ, на функциональных узлов, субблоков идругих электронных устройств. Цельизобретения - повышение достоверности результатов контроля за счет проверки параметров сигналов объектаконтроля на рабочей частоте, Система автоматического контроля параметров электронных схем содержитуправляющую вычислительную машину,измерительные станции,рабочие посты. Система позволяет Формироватьна каждый входной контакт контролируемого устройства требуемые стимулирующие воздействия по программе,записанной для каждого входного контакта в ОЗУ тестовых комбинаций,2 з,п,ф-лы, 10 ил,фиг. 4 - схема коммутатора программ, на Фиг, 5 - Функциональная схема устройства сравнения; на Фиг. 6 - функциональная схема блока Формирования запуска программы; на фиг. 7 - Функциональная схема блока анализа, на фиг. 8 - Функциональная схема коммутатора выводов; на Фиг, 9 - функциональная схема коммутатора выходов, на фиг. 10 - функциональная схема измерительного блока.Система содержит управляющую вычислительную машину (УВМ) 1, измерительные станции 2, рабочие посты 3.Каждая измерительная станция 2содержит блок 4 ключей, дешифратор 5 адреса, регистр 6 рабочих постов, :блок 7 памяти тестовых комбина первую группу регистров верхнеЬхсд яОииущатара кцзкерителю 23Фиг.81700538 ставитель В.ГришиТехред А.Кравчук Со едактор И,Янкович Корр Ко ектор А.Обруча аПодписноеизобретениям и открытиям при ГКНРаушская наб., д. 11/5е аказ М 67 Тираж НИИПИ Государственного комитета по113035, Иосква, Жельский комбинат "Патент", г. Ужгород, ул. Гагарина,роиэводственннижней 9 уставки, вторую группу регистров верхней 10 и нижней 11 уставки, реверсивный счетчик 12, блок13 Формирования запуска программы,задатчик 1 ч программы проверки,5блок 15 анализа, блок 16 источниковпитания, регистр 17 готовности,,рабочих постов, коммутатор 20 выво:дов, первый 21 и второй 22 элементы ИЛИ, измерительный блок 23.Управляющая вычислительная машина содержит регистр 2 ч прерывания,регистр 25 защиты, блок 26 сравне ния, блок 27 управления, регистр 28обмена, блок 29 памяти, регистр 30адреса, дешифратор 31 станции.Задатчик 1 ч программы проверкисодеожит блок 32 памяти номеров проверяемых контактов, блок 33 храненияпрограмм, счетчик 3 ч адреса, номеровпроверяемых контактов, коммутатор 35адреса, счетчик 36 адреса номерапрограмм, коммутатор 37 программ,Коммутатор 37 содержит два мультиплекса 38 и схему 39 2 И/ИЛИ.Блок 18 сравнения содержит первый"О и второй ч 1 блоки сравнения, элемент ИЛИ ч 2.Блок 13 Формирования запуска программ содержит генератор 13 спорнойчастоты, программированный делитель1 А рабочей частоты, счетчики тактов5 и циклов 16, дешифраторы тактов7 и циклов 8 и элемент И 19Блок 15 анализа содержит регистр50 информации, первый 51 и второй52 блоки сравнения, блок 53 вентилей,элемент 51 задержки, элемент ИЛИ 55,перьый элемент ИЛИ 56, триггер 57неисправности, второй элемент ИЛИ 58,генератор 59 одиночного импульса,регистр 60 команд, второй элемент 61задержки, элемент И 62,45Коммутатор выводов 20 содержит пканалов 63 Формирования стимулирующих сигналов для объекта контроля,Каждый из каналов включает в себя триг"гер бч информации, триггер 65 маски, 50две схемы И 66 и 67, два аналоговыхключа 68 и 69, управление осуществляется от регистра 70 выходов и дешифра 1 ора 71.Коммутатор 72 выходов (Фиг.9) содержит двухступенчатую дифференциальную матрицу аналоговых коммутаторов73 и буферный усилитель 74. Измерительный блок (Фиг.10) содержит и-разрядный быстродействующий ЦАП75, и триггеров 76, сдвиговый регистр77, и схем И 78, схему 79 сравнения,генератор 80,Назначение эадатчика 1 ч программыпроверки состоит в записи в блок 32 ии блок 33, который в процессе работысистемы в режиме контроля параметровиспользуется для выбора последовательности контролируемых контактов и управления переключением каналов контроля.В системе имеются два канала контроля параметров - активный и пассивный,Активный канал контроля определяет соответствие допустимым значениямамплитуды выбранного для контролявыхода объекта контроля в возбужденном (активном) состоянии, пассивныйсоответсвие этого выхода допустимымзначениям в невоэбужденном (пассив"ном) состоянии.В блок 33 записывается для каждого выходного контакта информация,определяющая для каждого такта контроля его состояние - активное или пассивное, Каждому такту контроля ставится в соответствие один бит памяти,причем "0" соответствует пассивномусостоянию, "1" - активному,Таким образом, каждому выходномуконтакту ставится в соответствие "и"бит информации в блоке 33 (и - максимальное число выводов 0 К). Распределение памяти показано на Фиг.3,Блок 33 разделен на и эон, каждая зона содержит ш (16) разрядныхячеек, причем щ = и/16. Начальный адрес каждой зоны определяется информацией ОЗУ 32, выходы которого через коммутатор 35 адреса при чтении подключены к старшим адресным входам блока 33 программ.Младшие адресные входы блока 33 при чтении подключены через коммутатор 35 адресов к старшим разрядам счетчика 36 программ, младшие разряды которого управляют коммутатором 37 программ. Запись информации в блок 32 и блок 33 осуществляется последовательно под управлением счетчика 31, вь 1 ходы которого подключены к адресным входам блока 32 непосредственно, а к блоку 33 через коммутатор 35 адреса,1700Назначение блока 13 состоит вформировании импульсов запуска дляОЗУ 7 тестовых комбинаций и формирования такта контроля для блока 15анализа. Меняющаяся с рабочей частотой информация с выхода счетчика45 поступает на входы блока 7, Выходы ОЗУ 7 через коммутатор 20 выводов обеспечивают подключение каждого10входного контакта контролируемогоустройства к соответствующим уровнямстимулирующих сигналов (фиг,8), Таким образом осуществляется перебор,объекта контроля на рабочей частоте,При этом каждый проверяемый выход подключается к устройствам контроля навесь цикл перебора входных воздействий. Проверка параметров контролируемого выхода осуществляется во времядействия такта контроля.Такт контроля представляет собойпериод рабочей частоты, сформированный по совпадению на элементе И 49 блска13 информации с выходов счетчиков 45тактов и 46 циклов. Количество тактов контроля соответствуетколичеству проверяемых выходов.Таким образом, в процессе контроля каждый контролируемый контактподключается к устройствам контроляна полный цикл работы контролируемого устройства и проверяется запрограммированное число тактов какактивный выход и соответствующеечисло тактов как пассивный, когдавозбуждаются другие выходы,тем самым выявляется влияние одних каналов на другие,Информация в триггеры 64 переписывается из блока 7 тестовых комбинаций, Триггер информации через соответствующие схемы И управляетключами 68 и 69. Обнуленное состояние триггера 64 обеспечивает подключение к нагрузке (входной выводобъекта контроля) источника И 2 через ключ 69, взведенное - источникаИ 1 через ключ 68, Информация втриггеры 65 маски записывается отблоков 4 и 5. Триггер маски разре 50шает работу соответствующего канала,Обнуленное состояние триггера устанавливает выхол соответствующего кайала в высокоимпедансное состояние,Кроме того, коммутатор 20 содержитрегистр 70 выходов, дешифратор 71и коммутатор 72 выходов. В регистр70 выходов записывается информация 538 6от задатчика 14, определяющая номераконтролируемых выводов объекта контроля, Соответствующий канал коммутируется к входу измерителя 23.Сдвиговый регистр 77, выполняющий функции устройства управления,вырабатывает требуемую для преобразования последовательность импульсных сигналов управления Бо упо сигналу Гт, вырабатываемого гене- .ратором 80, который запускается сигналом "Пуск", По внешнему сигналу,"Пуск" сдвиговь,й регистр вырабатывает-, импульс Б, которым триггеРТ устанавливается в положение "1",а остальные триггеры регистра сбрасываются в состояние "0", В результате этого на выходе ЦДП Форми;руется выходной сигнал 11 к, величина которого пропорциональнавесу старшего Разряда кода результата преобразования. Далеесдвиговый регистр последовательновырабатывает импульсы 11 у, 11 р111.,1, которые поочередно устанавливают в состояние н 1 н триггерыТТп. Одновременно с установкой триггера Т,+, в состояние "1"импульс Б , поступает на входсхемы И предыдущего старшего разряда. Если в 1-м такте преобразованиявыполняется неравенство Бу с 11то уровень выходного сигнала сравнивающего устройства открывает цепочку схемы И, и импульс 11, проходит на нулевой вход триггера Т;,переводя его в состояние "0",Компенсирующий сигнал 11(,1ЦАПа становится меньше Б , на величину, соответствующую весу (+1)го разряда. Если же выполняется неравенство Б) Б, то сигнал 11 с имеет такой уровень, который запираетвсе схемы И. В этом случае единица,записанная в триггер Тв предыдущем такте преобразования, сохраняется в течение всех последующихтактов, а сигнал Бк, увеличиваетсяна величину, соответствующую весу(+1)-го разряда. Этот процесс повторяется для всех импульсов, поступающих из сдвигового регистра 68.Импульсом Б производитсяокончательное Формирование кода вмладшем разряде, После этого сдвиговый регистр вырабатывает импульсокончания поразрядного кодирования11 О,1, по которому с выхода триггер 1700538ного регистра можно снять и-разрядньй код результата преобразования, Так как преобразование выполняется из и таков, то при использовании десятиразрядного ЦАПа типа КМ 1118 ПА 2 с временем установления 50 нс быстродействие измерительного блока 23 может достигать значения 10 6 преобразований в 1 с.Система работает следующим образом.УВМ через дешифратор 31 станции осуществляет последовательное про граммное сканирование готовности , каждой измерительной станции, обес,печивая через дешифратор 21 ад,реса сбегающий опрос регистра готовности и определяя первый рабочий пост, готовый к работе в дан-, , ной измерительной станции. Определив пост, готовый к работе, и вы, брав из блока 29 памяти соответствующую ему программу проверки на данное контролируемое устройство, УВМ начинает запись "загрузку") кодовых комбинаций во все функциональные системы:в блок 32 о номерах проверяемых контактов (выходов проверяемого устройства), которые допжны через коммутатор 20 выводов последователь" но подключаться к измерительномублоку 23,в блок 33 программ о программе проверки на каждый проверяемый контакт во всем временном интервале;в регистры 15 и 16 тактов и циклов о количестве рабочих тактов (периодов рабочей частоты), необходимых для одного полного цикла работы контролируемого устройствамив реверсивный счетчик 12 с последующей перезаписью информации в соответствующий регистр блока 16 программных источников о величине стимулирующего сигналав регистры 8 и 9 в зависимостиот работы системы о предельных значениях аналогового сигнала, который отрабатывается ЦАП блока 16 и определяет велйчину стимулирующего воздействия или о допустимых значениях контролируемого сигнала на активном выходе;в регистры 10 и 11 о допустимыхзначениях контролируемого сигнала на пассивном выходе.25 30 35 40 45 50 55 щего сигнала. В первом режиме регистр 60 команд через элемент ИЛИ 58, второй элемент 61 задержки и элемент И 62 выдает сигнал за запуск измерительного блока 23, Через интервал времени, необходимый для измерения, блок 23 выдает на информационные входы регистра 50 цифровой код измеренного параметра, а на его управляющий вход - сигнал конца измерения. По этому сигналу информация записывается в регистр 50 и с некоторой задержкой, необходимой для надежного установления информации на выходе регистра, разрешается сравнение блоками 51 и 52 цифровых кодов регистра 50 и кодов, поступающих с регистров верхней 8 и нижней 9 уставки и характеризующих,предельные значения стимулирующегосигнала, По линии задатчика 14, в этом режима поступает разрешающий уровень сигнала, При этом возможны три комбинации: измеренное значение больше верхнего предельного значения, измеренное значение меньше нижнего предельного значения и измеренное значение находится в заданном интервале допустимых значений,В первом случае блок 51 выдает на управляющий вход реверсивного счетчика 12 сигнал вычитания, а на счетный вход - одиночный импульс с генератора 59. ЦАП блока 16 отрабатывает новое, уменьшенное на единиЗапись информации в регистрыстанции осуществляется через регистр 28 обмена, блок 1 ключей под управлением дешифратора 5 адреса.После "загрузки" информации в соответствии с программой во все регистры и выполнении подготовительныхопераций по подключению через мат. рицу 63 входных контактов контролируемого изделия к соответствующимисточникам блока 16 УВМ выдает врегистр 60 блока 15 командное слово,определяющее режим работы системы, 15Система под управлением регистра60 работает в трех режимах: отслеживание напряжения ЦАП источника пи;тания; контроль параметра, выдача в УВМ цифрового кода о величине параметра .20Первый режим является вспомогательным и может быть выполнен тогда,когда требуется обеспечить с высокой170053 20 цу, значение цифрового кода, затемблок 15 вновь запускает блок 23 наизмерение. Отслеживание аналоговогосигнала продолжается до момента,когда измеренное значение станет 5меньше верхнего предельного значения.Во втором случае процесс отслеживания аналогичен за исключением того, что на управляющий вход реверсивного счетчика с блока 52 сравнения выдается сигнал сложения и ЦАПотрабатывает увеличенное на единицу значение цифрового кода.Таким образом, осуществляется15отслеживание напряжения каждого канала блока 16 и значение стимулирующих сигналов по каждому входу оказывается в заданных пределах допустимых значений,В этом и третьем случаях блок 15анализа через элемент ИЛИ 21 осуществляет запрос на прерьвание, чтосвидетельствует о готовности станциик приему следующей тестовой комбинации в соответствии с программойпроверки на данное контролируемоеустройство,В первом режиме триггер 57 неисправности блокируется сигналом срегистра команд,Во втором режиме работы системыснимается блокировка с триггера 57неисправности и блокируется генератор 59 единочного импульса,35В этом режиме информация из блока 32 по первому адресу переписывается в регистр 70 блока 20 и обеспечивает подключение через коммутационную матрицу 72 к измерительномублоку 23 первого соответствующеговыходного контакта контролируемогоустройства, С некоторой задержкойблок 15 Формирует команду блоку 13на проверку, по которой начинают поступать с рабочей частотой импульсына запуск счетчика 45 тактов. Импульсы переноса счетчика 45 запускаютсчетчик 46 циклов. Иеняющаяся с ра 50бочей частотой информация с выходасчетчика 45 поступает на адресныевходы блока 7 тестовых комбинаций,Выходы блока 7 в каждый материал времени период рабочей частоты) черезтриггеры 64 и ключи 68, 69 обеспечи-"55вают подключение каждого контактаконтролируемого устройства к соответствующим уровням стимулирующих 8 1 Псигналов, т,е, .перебор входов обьекта контроля на рабочей частоте.При этом проверяемый выход подключается к устройствам контроля на весьцикл перебора входных воздействий.Контроль выходных параметров осуществляется каналом контроля активного состояния контакта, состоящимиз блоков 51 и 52 сравнения, и каналом контроля пассивного состоянияконтакта, состоящим из блоков 40 и41 сравнения,В каждый временной интервал тактконтроля = периоду рабочей частоты)разрешается один из каналов контроля.Это определяется программой на данный выходной контакт, записанной вблок 33 и поступающей на блоки сравнения через коммутатор 37. Коммутатор 37 управляется счетчиком 36 номера программы, запуск которого осуществляется тактом контроля, Формируемым элементом И 49 по совпадениюсостояний счетчиков 45 и 46 тактов ициклов и соответствующих дешифраторов 47 и 48.При работе системы в режиме контроля параметров на счетчик 36 последовательно поступают такты контроля,счетчик переключается и под его упправлением коммутатор 37 программчерез мультиплексоры 38 обеспечиваетпоследовательную бит за битом выдачу информации из первой ячейки блока 33 программ из зоны, соответствующей контролируемому контакту. После заполнения четырехразрядного счетчика 36, обеспечивающих выдачу всех16 бит первой ячейки, осуществляется выбор следующей ячейки зоны блока33 программ и коммутатор 37 коммутирует на свой выход информацию следующей ячейки, Процесс продолжается дозавершения поступления запрограммированных тактов контроля. Затеи из блока 32 выбирается следующий контакт ипроцесс повторяется,Таким образом, контролируемыйконтакт подключает к системам контроля на один полный цикл работы контролируемого устройства и проверяетсяодин такт как активный - отклик навходные стимулирующие воздействияи остальные такты как пассивныйотсутствие отклика на другую комбинацию входных воздействий,Если параметры выходного сигнала на контролируемом контакте в ак 1700538Ф о р м у л а изобретенияВ третьем режиме работы системы 55обесп еци ва ется возмож нос т ь с цитыват ьинформацию из регистра 50 церез блок52 вентилей в УВМ для анализа,1 1, Система автоматицеского контроля параметров электронных схем, содержащая управляюшую вычислительную машину, измерительные станции и рабочие посты для подключения обьектов контроля, информационные входы- выходы и вход готовности которых соединены соответственно с информационным входом-выходом и входом готовности измерительной станции, адресный вход, командный вход, выход прерывания, выход готовности и вход разрешения которой соединены соответственно с одноименными входами и выходами управляющей выцислительной машины, причем каждая измерительная станция содержит регистр рабочих постов, блок кпюцей, дешифратор адреса, первую группу регистров верхней и нижней уставок, реверсивный счетчик, блок анализа, регистр готовности, коммутатор рабочих постов, первый и второй элементы ИЛИ, измерительный блок, блок питания, комт мутатор выводов, первый информационный вход которого соединен с выходом блока питания, первый и второй входы задания выходного сигнала которого соединены соответственно с выходом дешифратора адреса и выходом реверсивного счетчика, информационный вход, счетный вход и синхровход соединены соответственно с выходом блока ключей, выходом управления величиной напряжения питания блока анализа, дешифратора адреса, вход которого является адресным входом измерительной станции, а выход подключен к синхровходам регистра рабочих постов, регистров нижней и верхней уставок первой группы, регистра готовности, блока анализа выходы блока ключей соединены с информационными входами регистра рабочих постов, регистров верхней и нижней уставок первой группы и блока анализа, информацион.- ный вход, первые входы нижней и верхней уставок; выход запуска и выход готовности которого соединены соответственно с выходом измерительного блока, выходами регистров нижней и верхней уставок первой группы, входом запуска измерительного блока и первым входом второго элемента ИЛИ, второй вход которого соединенс выходом регистра готовности, а выход является выходом готовности измерительной станции, выход регистра рабочих постов соединен с адресным входом коммутатора рабочих постов,первые и вторые информационные входы-выходы, выход прерывания которого соединен соответственно с информационным входом-выходом измерительной станции, выходом коммутатора вы,водов, первым входом первого элемента ИЛИ, второй, третий входы и выход которого соединены соответственно с выходами прерывания коммутаторавыводов, блока анализа, выходом прерывания измерительной станции, выход коммутатора выводов соединен с ин-.формационным входом измерительногоблока, информационный вход регистра готовности соединен с входом готовности, информационный вход блокаключей - с входом разрешения, а управляющий вход блока ключей и входблокировки дешифратора адреса - скомандным входом данной измерительной станции, о т л и ч а ю щ а яс я тем, что, с целью повышениядостоверности результатов контроляза счет проверки параметров сигналов объекта контроля на рабочей частоте,каждая измерительная станциясодержит вторую группу регистровверхней и нижней уставок, задатчикпрограммы проверки, блок запуска программы, блок памяти тестовых комбинаций и блок сравнения, первый,второй, третий информационные входы, выход, синхровход и вход разрешения которого соединены соответственно с выходами регистров верхнейи нижней уставок второй группы, информационным выходом блока анализа,входом признака нахождения параметра в зоне допуска блока анализа, инФормационным выходом задатчика программы проверки, выходом признакаконца такта блока анализа, первыйвыход разрешения которого соединенс входом разрешения блока запускапрограммы, адресный выход, выходпризнака такта контроля и тактовыйвыход которого соединены соответственно с первым адресным входом бло" .ка памяти тестовых комбинаций, первым счетным входом, вторым счетным входом задатчика программы проверки, соединенного с тактовым входом блока анализа, информационные и ад 5 1 О 15 2 О ч 30 35 40 45 ресные входы блока задания программы проверки соединены с одноименными входами блока памяти тестовых комбинаций, блока запуска программы, коммутатора выводов и подключены соответственно к выходам блока ключей и дешифратора адреса.2, Система по и, 1, о т л и ч аю щ а я с я тем, что задатчик программы проверки содержит блок памяти номеров проверяемых контактов, блок хранения программы проверки, счетчик адреса номера контакта, счетчик адреса номера программы, коммутатор адреса и коммутатор программ, выход которого является ин" формационным выходом задатчика, а . адресный и информационные входы соединены соответственно с выходами младших разрядов счетчика адреса номера программы, выходом блока хранения программ, адресный вход которого соединен с выходом коммутатора адреса, а информационный вход и вход записи соединены соот ветственно с информационными входами и входами записи, счетчика адреса номера контакта и блока памяти номеров проверяемых контактов, являющихся информационными и адресными входами задатчика,счетный вход счетчика адреса номеров проверяемых контактов является первым счетным входом задатчика , а выход соединен с адресным входом коммутатора адреса, первый и второй инФормационные входы которого соединены соответственно с выходом блока памяти номеров проверяемых контактов, являющегося адресным выходом задатчика и выходами старших разрядов счетчика программ, счетный вход которого является вторым счетным входом задатчика. 3. Система по и. 1, о т л и ц а ю щ а я с я тем, что блок запуска программы содержит элемент И, делитель частоты, счетчик тактов, счетчик циклов, дешифратор тактов, дешифратор циклов и генератор, вход которого является входом разрешения блока, а выход соединен с тактовым входом делителя частоты, информационный вход и вход записи которого соединены с информационными входами и входами записи счетчика тактов и счетчика циклов и являются соответственно информационным и адреснымвходами блока, выход делителя цастоты соединен со счетным входом сцетцика тактов, старший разряд информационного выхода которого является выходом запуска блока, младшие разрядыинформационного выхода соединены свходом адреса дешифратора тактов, выход которого соединен с первым вхоЭ дом элемента И, второй вход которогосоединен с выходом деширатора циклов,адресный вход которого соединен с выходом счетцика циклов, сцетный входкоторого соединен с выходом переполнения сцетцика тактов, а выход переполнения является выходом признакатакта контроля блока, тактовый входкоторого является выходом элемента И,1700538йы ЮЮЖРЬИа.Яма Ф-и дмгаФжЙ. 3ь азу Рт сюлЧйб 2 О Ю- ЯЮЯ аллу

СмотретьЗаявка

4748307, 11.10.1989

ПРЕДПРИЯТИЕ ПЯ А-1943

ФЛЕЙШ ЛЕЙБА СЕМЕНОВИЧ, БАРТОЛОМЕЙ ЛЮДМИЛА БОРИСОВНА

МПК / Метки

МПК: G05B 23/02

Метки: параметров, схем, электронных

Опубликовано: 23.12.1991

Код ссылки

<a href="https://patents.su/13-1700538-sistema-avtomaticheskogo-kontrolya-parametrov-ehlektronnykh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Система автоматического контроля параметров электронных схем</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Стабилизированный преобразователь постоянного напряжения

Случайный патент: Рекуператор