Программируемый многофазный тактовый генератор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1785069

Автор: Кулаков

Текст

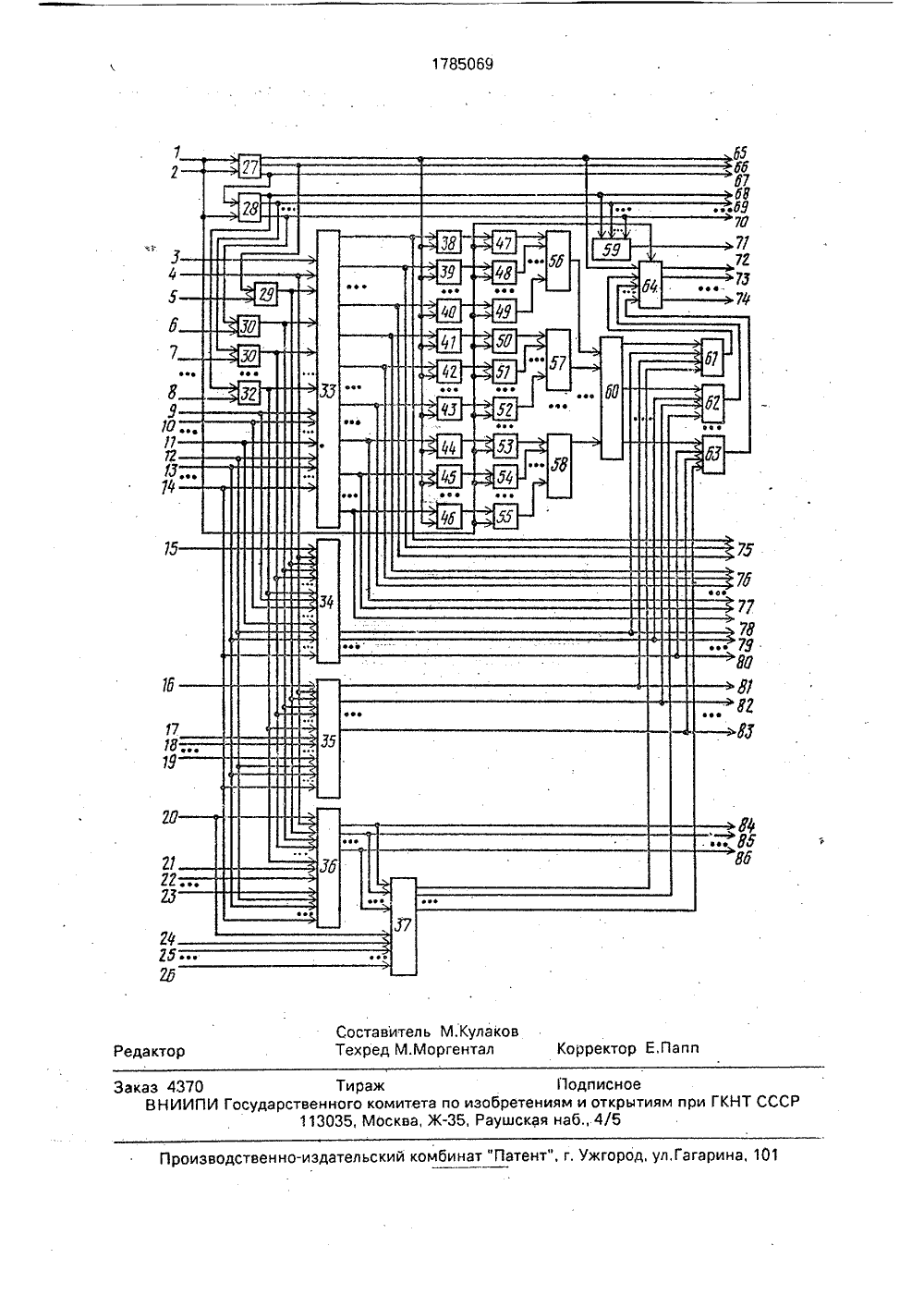

(71) Центральное конструкторское бюро(56) Авторское свидетельство СССРМ 1352627, кл, Н 03 К 3/64, 1986,(54) ПРОГРАММИРУЕМЫЙ МНОГОФАЗНЫЙ ТАКТОВЫЙ ГЕНЕРАТОР исполь й техн троля расш ей. П овый ь имп пы эле мпуль фратор зовано ки, упи региирение рограм- генераульсов, ментов сов, за, схему Изобретение относится к импульснойтехнике и может быть использовано в качестве генератора импульсов с одним входом,который преобразует входные сигналы в импульсы, выдаваемые в требуемые интервалы времени; генератора импульсов, вкотором импульсы образуются в разные моменты времени на различных выходах; распределителя импульсов, генераторамногофазного тактового в различных узлахи устройствах вычислительной техники,средствах управления, регулирования, контроля и оегистоаиии.Известен многофазный тактовый генера"тор по а.с. 1264315 (СССР), кл, Х 03 К 3/64,опубл. 15.10.86 (бюл, М 38), содержащийсчетчик, элемент задержки, селектор-мультиплексор, первый и второй регистры, Отриггер, соединенные с соответствующимобразом, Недостатком этого устройства являются ограниченные функциональные воз- .можности, заключающиеся в формированиивременной диаграммы только одного определенного типа,Известны программируемые многофаз-.тактовые генераторы (ПМП) с гибким ные ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(57) Изобретение может быть в устройствах вычислительно равления, регулирования, кон страции, Цель изобретения - функциональных возможност мируемый многофазный такт тор содержит формировател группы элементов ИЛИ, груп И, группы триггеров, счетчик и поминающие устройства, ши селекции кодов и регистр. 1 и программированием периода следования импульсов на выходных каналах устройства и одновременным запретом появления импульсов на группе выходных каналов устройства, к которым относится ПМТГ по ал1352627 (СССР). Этот ПМТГ является прототипом заявляемого устройства и содержит шину управления, шину разрешения, шины параллельного кода, шину начальной установки, шину тактовых импульсов, второй элемент И, элемент задержки, первый ре- М гистр, элемент ИЛИ, первый триггер, де- С:) шифратор, вторую группу элементов И, О второй регистр, состоящий из триггеров, первый элемент И, первую группу элементов И, второй триггер, выходную тактирующую шину, выходные шины каналов, выходную стробирующую шину, элементй ИЛИ-НЕ,Информационные входы первого регистра соединены с шинами параллельного кода, а выходы подключены к входам дешифратора, шина тактовых импульсов соединена с тактовым входом второго регистра, первыми входами элементов И первой группИ, первым входом псрногоных зонах первого ОЗУ 33.второго ОЗУ 34, третьего ОЗУ 35 и четвертого ОЗУ 36 так и с обновлением управляющей информации.Использование изобретения позволитрасширить функциональные возможностиустройства путем асинхронного или периодического формирования и логического сложения комбинаций импульсов различной программируемой фазы и длительности и логического сложения с кодовыми импульсами на нескольких параллельных выходах устройства при одновременном обозначении длительности импульсов йих фазы синхронно формируемыми стробами и как следствие этого расширение области применения фазных тактовых генераторов, упрощение аппаратуры.Использование изобретения позволитрешить задачу генерации и логического сложения множества разряженных векторов вреальном масштабе времени при минимальных затратах оборудования, обеспечив взаимосвязанную генерацию групп многофазных импульсов, которые являются основой множества векторов, имеющих области пересечения,При этом обеспечивается работа контроллеров и микро-ЭВМ с максимальнымтемпом функционирования объектов управ. ления и внешних устройств,По данному техническому предложению изготовлена рабочая документация и выполнено макетирование устройства.Формула изобретения Программируемый многофазный тактовый генератор, содержащий регистр, первую и вторую группы элементов И, первую группу триггеров, элемент ИЛИ, о тл и ч а ющ и й с я тем, что, с целью расширения функциональных возможностей, в него введены формирователь импульсов, двоичный счетчик, первое, второе, третье, четвертое и пятое запоминающие устройства, схема селекции кода, Мгруппа элементов И, М групп триггеров;" первая, вторая и третья группы элементов ИЛИ и шифратор, причем тактовый вход формирователя импульсов соединен с шиной тактовых импульсов, второй выход формирователя импульсов соединен с второй выходной шиной стробов и с первым входом элемента ИЛИ, выход которого соединен с входами стробов первого запоминающего устройства, второго запоминающего устройства, третьего запоминающего устройства и четвертого запоминающего устройства; каждый определенный выход, входящий в определенную из групп выходов первого запоминающего устройства, соединен с первым входом элемента И, одноименного этому выходу первого запоминающего устройства и входящему в группу элементов И, одноименную группе выходов первого запоминающего устройства; выход каждого определенного элемента 5 И, входящего в определенную из групп элементов И, соединен с тактовым входом одноименного этому элементу И триггера, входящего в одноименную группе элементов И группу триггеров; выход каждого оп ределенного триггера, входящего вопределенную из групп триггеров, соединен с одноименным этомутриггеру входом одноименного группе триггеров элемента ИЛИ второй группы элементов ИЛИ, выход 15 определенного элемента ИЛИ второй группы элементов ИЛИ соединен с одноименным элементу ИЛИ входом шифратора, управляющий вход формирователя импульсов соединен с шиной сброса и входом сбро са счетчика, входом сброса каждоготриггера в каждой из групп триггеров и вхо-, дом сброса регистра, первый выход формирователя импульсов соединен с первой выходной шиной стробов с тактовым входом 25 регистра и с вторым входом каждого элемента И в каждой из групп элементов И третий выход формирователя импульсов соединен с третьей выходной шиной стробов и с тактовым входом счетчика, каждый опре деленный выход которого соединен с одноименной шиной группы выходных шин кода, первым входом одноименного выходу элемента ИЛИ первой группы элементов ИЛИ и с одноименным выходу входом схемы се лекции кода, выход которой соединен с выходной шиной признака, вход выборки первого запоминающего устройства соединен с первой шиной выборки, шина управления записью-чтением соединена с 40 входами Запись-чтение" второго запоминающего устройства, третьего запоминающего устройства, четвертого запоминающего устройства и первого запоминающего устройства, каждый определен ный выход которого соединен содноименной шиной первой группы выходных шин данных, каждый определенный выход шифратора соединен с первым входом одноименного выходу элемента ИЛИ 50 третьей группы элементов ИЛИ, выход каждого определенного элемента ИЛИ третьей группы элементов ИЛИ соединен с одноименным этому элементу ИЛИ входом регистра, каждый определенный выход регистра 55 соединен с одноименной шиной группы выходных шин, вход выборки второо запоми. нающего устройства соединен с второйшиной выборки; каждый определенный выход второго запоминающего устройства соединен с одноименной шиной второйгруппы шин данных и соединен с вторым входом одноименного выходу элемента ИЛИ третьей группы элементов ИЛИ, второй вход первого элемента ИЛИ соединен с шиной стробов, второй вход каждого эле мента ИЛИ первой группы элементов ИЛИ соединен с одноименной шиной первой .группы адресных шин, выход каждого определенного элемента ИЛИ первой группы элементов ИЛИ соединен с одноименным 10 элементу ИЛЙ входом первой группы адресных входов первогозапоминающего устройства, одноименным входом первой группы адресных входов второго запоминающего устройства, одноименным входом первой 15 группы адресных входов третьего запоми; нающего, устройства и одноименйым входом первой группы"адресных цходов четвертого запоминающего устройства, каждый определенный вход второй группыадреснйх входов первого запоминающего устройства соединен с одноименным ва- . дом второй группй адресных входов второ-, го запоминающего устройства и с одноименной шиной второй группы адресных шин, каждый определенный вход дан- .ных первого запоминающего устройства, соединен с одноименным входом данных второго запоминающего устройства, с одноименным входом данных третьего запоми-ЗО нающего устройства, с одноименным входом данных четвертого запоминающего устройства и одноименной шиной группы,шин данных, каждый определенный адресный вход второй группы адресных входов третьего запоминающего устройства соединен с одноименной шиной группы шин настройки, каждый определенный адресный вход второй группы адресных входов четвертого запоминающего устройства соеди.нен с одноименной шиной первой группы шин управления, каждый определенный адресный вход второй группы адресных входов пятого запоминающего устройства соединен с одноименной шиной второй группы шин управления, вход выборки третьего запоминающего устройства соединен с третьей шиной выборки, вход выбевки четвертого запоминающего устройства соединен с четвертой шиной выборки и с входом выборки пятого запоминающего устройства, каждый определенный выход третьего запоминающего устройства соединен с одноименной шиной третьей группы выходных шин данных и с третьим входом одноименного выходу элемента ИЛИ третьей группы элементов ИЛИ, каждый определенный выход четвертого запоминающего устройства соединен с одноименнойшиной четвертой группы выходных шин данных и с одноименным входом первой группы входов пятого запоминающего устройства, каждый определенный выход которого соединен с четвертым входом одноименного .выходу элемента ИЛИ третьей группы элементов ИЛИ,1785069 2 оставитель М.Кулаковехред М. Морге нтал Корректор Е,П дакто оизводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 10 225 Заказ 4370 Т ВНИИПИ Государственн 11303ажкомитета иМосква, ЖПодписноеобретениям и открытиям при ГКНТ СССРаушская наб 4/5элемента И и входом элемента задержки, выход которого подключен к тактовому входу первого триггера, информационный вход сброса которого соединены с шиной начальной установки, а выход подключен к входам 5 сброса первого и второго регистров и первому входу элемента ИЛИ, выход которого соединен с единичным входом второго триггераа; выЖод которого подключен к стробирующей шине, а второй вход соединен с 10 вымодом первого элемента И, первой группы элементов И, выходы элементов И первой группы элементов И соединены с выходными шинами каналов, а вторые входы подключены к выходам второго регистра 15 и входам элемента ИЛИ-НЕ, выход каждого соединен с вторым входом первого элемента И и первым входом первого элемента И второй группы элементов И, третий вход которого подключен к шине, управления, вы ходы дешифратора соедийенц с вторыми входами элементов И второй группы элементов И,. выходы которых подключены к информационным входам второго регистра, выходы триггеров второго регистра соеди нены с первыми входами соответственно элементов И второй группы элементов И, выход первого элемента И подключен к выходной тактирующей шине и вторым входам . элемента ИЛИ и второго элемента И, первый вход которого соединен с шиной разрешения, а выход подключен к тактовому входу первого регистра.Недостатком этого устройства являются ограниченные функциональные возмож ности, заключающиеся в формировании временныхдиаграмм только определенного типа. Широкое распрострайеййе растровых средств отображения информации, работающих в реальном масштабе времени, поста видо задачу генерации и логического сложения разреженных векторов, принадлежащих одной растровой строке, причем возможно наложение на вектора произвольных комбинаций точек. Под разряжен ным вектором понимается вектор от точки А до точки В, заполненной чередующимися группами нулей и единиц. При отображении векторов на несколько растровых строк, идущих подряд, получаются тоновые линии, 50 Использование специальных многофазных тактовых генераторов позволит решить эту задачу в реальном масштабе времени и при минимальных затратах оборудования, обеспечивая взаимосвязанную генерацию групп 55 многофазных импульсов, используемых в качестве основы векторов.Целью изобретенияявляется-расширение функциональных возможностей устройства путем асинхронного или периодического формирования и логического сложения комбинаций импульсов различной программируемой фазы и длительности и логического сложения с кодовыми импульсами на нескольких параллельных выходах устройства при одновременном обозначении длительности импульсов и их фазы синхронно формируемыми стробами,Поставленная цель достигается тем, что в устройство дополнительно введены формирователь импульсов, двоичный счетчик, первая группа элементов ИЛИ, первое ОЗУ, второе ОЗУ, третье ОЗУ, четвертое ОЗУ, схема селекции, кора, ПЗУ, (М) групп элементов И, (М) групп триггеров, вторая группа элементов ИЛИ, шифратор, третья группа элементов ИЛИ, причем тактовый вход формирователя импульсов является входом так-,товых импульсов устройства, второй. выход формирователя импульсов является вторым выходом стробов устройства и соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом стробовпервого ОЗУ, второго ОЗУ, третьего ОЗУ и четвертого ОЗУ; каждый определенный выход, входящий вопределенную из групп выходов первого ОЗУ, соединен с первымвходом элемента И, одноименного этому выходу ОЗУ и входящему в группу элементов И, одноименную группе выходов перво-го ОЗУ; выход каждого определенного элемента И, в одящего в определенную из групп элементов И соединен с тактовым входом одноименного этому элементу.Итриггеоа, входящего в одноименную группе элементов И группу триггеров; выход каждого определенного триггера, входящего в определенную из групп триггеров, соединен с одноименным этому триггеру входом одноименного группе триггеров элементаИЛИ второй группы элементов ИЛЛ, выход определенного элемента ИЛИ второй группы элементов ИЛИ соединен с одноимен- ным .этому элементу ИЛИ входом шифратора, управляющий вход формирователя импульсов является входом управления устройства и соединен с входом сброса счетчика й входом сброса каждого триггера в каждой из групп триггеров и входом сброса регистра, первый выход формирователя импульсов является первым выходом стробов устройства и соединен с тактовым входом регистров и со вторым входом каждого элемента И в каждой из групп элементов И; третий вьход формирователя импульсов является третьим выходом стробов устройства и соединен с тактовым входом счетчика, выходы которого являются выходами кода уст-.ройства и каждый из отдельных выходов которого соединен с первым входом одно55 именного этому выходу элемента ИЛИ первой группы элементов ИЛИ и с одноименным этому выходу входов схемы селекции кода, выход которой является выходом признака устройства, вход выборки первого ОЗУ является входом выборки первого ОЗУ устройства, вход управления записью/чтением устройства соединен с входами запись/чтение второго ОЗУ, третьего ОЗУ, четвертого ОЗУ и первого ОЗУ, выходы всех групп выходов которого являются выходами данных первого ОЗУ устройства, каждый отдельный выход из выходов шифратора соединен с первым входом одноименного этому выходу элемента ИЛИ третьей группы элементов ИЛИ, выход каждого отдельного элемента ИЛИ из третьей группы элементов ИЛИ соединен с одноименным этому элементу ИЛИ входом регистра, каждый отдельный выход регистра является одноименным этому выходу выходом устройства, вход выборки второго ОЗУ является входом выборки второго ОЗУ устройства, каждый отдельный выход второго ОЗУявляется выходом данных второго ОЗУ устройства и соединен с вторым входом одноименного выходу элемента ИЛИ третьей группы элементов ИЛИ, второй вход первого элемента ИЛИ является входом стробов устройства, второй вход каждого элемента ИЛИ первой группы элементов ИЛИ является одноименным элементу ИЛИ младшим адресным входом устройства, выход каждого отдельного элемента ИЛИ первой группы элементов ИЛИ соединен с одноименным этому элементу ИЛИ младшим адресным входом первого ОЗУ, младшим адресным входом второго ОЗУ, младшим адресным входом третьего ОЗУ и младшим адресным входом четвертого ОЗУ, каждый отдельный адресный вход из старших адресных входов первого ОЗУ соединен с одноименным старшим адресным . входом второго ОЗУ и явЛяется одноименным старшим адресным входом устройства, каждый вход данных первого ОЗУ соединен с одноименным входом данных второго ОЗУ, с одноименным входом данных третьего ОЗУ, с одноименным входом данных четвертого ОЗУ и является одноименным входом данных устройств, каждый отдельный адресный вход из старших адресных входов третьего ОЗУ является одноименным старшим адресным входом настройки третьего ОЗУ устройства, каждый отдельный адресный вход из старших адреснйх входов четвертого ОЗУ является одноимен-. ным старшим адресным входом управления четвертого ОЗУ устройства, каждый отдельный адресный вход из старших адресных 5 10 15 20 25 30 35 40 45 50 входов ПЗУ является одноименным старшим адресным входом управления кодомПЗУ устройства, вход выборки третьего ОЗУявляется входом выборки третьего ОЗУ устройства, вход выборки четвертого ОЗУ является входом выборки четвертого ОЗУустройства и соединен с входом выборкиПЗУ, каждый отдельный выход третьего ОЗУявляется одноименным выходом данныхтретьего ОЗУ устройства и соединен с третьим входом одноименного выходу элементаИЛИ третьей группыэлементов ИЛИ, каждый отдельный выход четвертого ОЗУ является одноименным выходом данныхчетвертого ОЗУ устройства и соединен 6 Ьдноименным младшим адресным входомПЗУ, каждый отдельный выход которого соединен с четвертым входом одноименноговыходу элемента ИЛИ третьей группы элементов ИЛИ,П ри этом расш и ря ются фун кци онал ьные возможности устройства путем синхронного или периодического формированияи логического сложения комбийаций импульсов различной программируемой фазыи длительности на нескольких параллель-ных выходах устройства при одновременном обозначении длительности импульсов иих фазы синхронно формируемыми стробами и как следствие этого - расширение области применения многофазных тактовыхгенераторов, упрощение аппаратуры. Этодостигается за счет перехода на иную, посравнению с базовым образцом, структурную схему программируемого многофазного тактового генератора,Использование изобретения позволитсущественно расширить область применения программируемых многофазных тактовых генераторовв контроллерах имикроЭВУ, особенно средств регистрации,обеспечить работу контроллеров и микроЭВМ с максимальным темпом функционирования обьектов управления и внешнихустройств, сократить обьем аппаратуры.На чертеже представлена функциональная схема устройства,На чертежах и в тексте приняты обозначения:1, Вход тактовых импульсов2, Вход управления3, Вход выборки первого ОЗУ4, Вход управления записью/чтением5. Вход стробов6, Первый младший адресный вход7, Второй младший адресный вход8, Последний младший адресный вход9, Первыйстарший адресный вход10, Второй старший адресный вход11, Последний старший адресный вход12, Первый вход данных настройки 46. Последний элемент Итретьей груп 13, Второй вход данных настройки пы элементов И14. Последний вход данных настройки 47. Первый триггер первой группы триг 15, Вход выборки второго ОЗУ геров16. Вход выборки третьего ОЗУ 5 48. Второй триггер первой группы триг 17. Первый старший адресный вход на- геров49. Последний триггер первой группы.18. Второй старший адресный вход на- триггеров50. Первый триггер второй группы триг 19, Последний старший адресный вход 10 геров51, Второй триггер второй группы триг 20. Вход выборки четвертого ОЗУ геров21. Первый старший адресный вход уп. Последний триггер второй группыравления триггеров22. Второй старший адресный вход уп 53, Первый триггер третьей группы триграаления геров23, Последний старший адресный вход 54. Второй триггер третьей группы тригуправления геров24. Первый старший адресный вход уп. Последний триггер третьей группы равления кодом 20 триггеров25. Второй старший адресный вход уп. Первый элемент ИЛИ второй группы рааления кодом элементов ИЛИ26. Последний старший адресный вход 57. Второй элемент ИЛИ второй группы управления кодом элементов ИЛИ27, Формирователь импульсов25 58, Последний элемент ИЛИ второй28, Двоичный счетчик группы элементов ИЛИ29, Элемент ИЛИ . 59. Схема селекции кода30. Первый элемент ИЛИ первой группы 60, Шифратор элементов ИЛИ 61, Первый элемент ИЛИ третьей груп 31. Второй элемент ИЛИ первой группы 30 пы элементов ИЛИ элементов ИЛИ62. Второй элемент ИЛИ третьей груп 32. Последний элемент ИЛИ первой пы элементов ИЛИгрупйы элементовэлементов ИЛИ 63, Последний элемент ИЛИ третьей33. Первое запоминающее устройство: . группы элементов ИЛИ (ОЗУ) . 35 64, Регистр выхода. 34. Второе запоминающее устройство 65. Первый выход стробов (ОЗУ) . 66. Второй выход стробов35. Третье запоминающее устройство 67,Третий выходстробов (ОЗУ) 68. Первый выход кода36, Четвертое запоминающее устройст 69, Второй выход кодаво (ОЗУ) 70. Последний выход кода37. Пятое запоминающее устройство 71. Выход признака (ПЗУ) . 72, Первый выход38. Первый элемент И первой группы 73, Второй выход элементове ентов И 45 74. Последний выходУ39. Второй элемент И первой группы . 7577 Выходы данных первого ОЗ элементов И 7880 Выходы данных второго ОЗУго ЗУ40, Последний элемент И первой группы. 8183 Выходы данных третьего О элементов И 8486 Выходы данных четвертого ОЗУ41, Первый элемент И второй группы 50 Предлагаемое устройство состоит из элементов И формирователя импульсов 21, двоичного42. Второй элемент И второй группы счетчика 28, элемента ИЛИ 29, первой группы элементов ИЛИ 30.32, первого ОЗУ 33,43. Последний элемент И второй группы второго ОЗУ 34, третьего ОЗУ 35, четвертого55 ОЗУ 36, ПЗУ 37, нескольких(М 2) групп элеэлементов И1.43 и44, Первый элемент И последней груп- ментов И; первой 38,40, второи 41 ит.д., последней 44.46; нескольких (М) групп пы элементов И52 и45, Второй элемент И третьей группы триггеров: первой 4749, второй 50 ит.д. последней 5355; второй группы элементов ИЛИ 5658, схемы секции кода 59,шифратора 60, третьей группы элементов ИЛИ 61.63, регистра 64, причем тактовый вход формирователя импульсов 27 является входом 1 тактовых импульсов устройства, второй выход формирователя импульсов 27 5 является вторым выходом стробов 66 устройства и соединен с первым входом первого элемента ИЛИ 29, выход которого соединен с входом стробов первого. ОЗУ 33, второго ОЗУ 34, третьего ОЗУ 35 и четверто го ОЗУ 35, каждый определенный выход, входящий в определенную из групп выходов первого ОЗУ 33 соединен с первым входом элемента И, одноименного этому выходу ОЗУ, и входящему в группу элементов И 15 3840, 4143,.,4446, одноименную группу выходов первого ОЗУ 33, выход каждого определенного элемента И, входящего в определенную из групп элементов И 3840, 4143, 4446 соединен с тактовым входом 20 одноименного этому элементу И триггера, входящего в одноименную группе элементов И группу триггеров 4749, 50.,;52, 53.55; выход каждого определенного триггера, входящего в определенную из групп 25 триггеров 47,49, 5052, , 5355, соединен с одноименным этому триггеру входом одноименного группе триггеров элемента , ИЛИ второй группы элементов ИЛИ 5658, выходопределенного элемента ИЛИ второй 30 группы элементов ИЛИ 5658 соединен с одноименным этому элементу ИЛИ входом шифратора 60, управляющий вход формирователя импульсов 27 является входом 2 управления устройства и соединен с.входом 35 сброса счетчика 28, входом сброса каждого триггера в каждой из групп триггеров 4749, 5052, 5355 и входом сброса регистра 64, первый выход формирователя импульсов 27 является первым выходом 40 стробов 65 устройства и соединен с тактовым входом регистра 64 и со вторым входом каждого элемента И в каждой из групп элементов И 3840, 4143;4446 третий выход формирователя импульсов 27 являет ся третьим выходом стробов устройства 67 и соединен с тактовым входом счетчика 28, выходы которого являются выходами кода устройства 68.70 и каждый из отдельных выходов которого соединен с первым вхо дом одноименного этому выходу элемента ИЛИ первой группы элементов ИЛИ 3032 и с одноименным этому выходу входов схемы селекции кода 59, выход которой является выходом признака устройства 71, вход 55 выборки первого ОЗУ 33 является входом 3 выборки первого ОЗУ - устройства, выход 4 управления записью/чтением устройствасоединен с входами запись/чтение второго ОЗУ 34, третьего ОЗУ 35, четвертого ОЗУ 36 и первого ОЗУ 33, выходы всех групп выходов которого являются выходами данных 7577 первого ОЗУ устройства, Каждый отдельный выход из выходов шифратора 60 соединен с первым входом одноименного этому выходу элемента ИЛИ;ретьей группы элементов ИЛИ 6163, выход каждого отдельного элемента ИЛИ из третьей группы элементов ИЛИ 6163 соединен с одноименным этому элементу ИЛИ входом регистра 64, каждый отдельный выход регистра 64 является одноименным этому выходу выходом 7274 устройства, вход выборки второго ОЗУ 34 является входом 15 выборки второго ОЗУ устройства, каждый отдельный выход второго ОЗУ 34 является выходом . данных второго ОЗУ устройства 7880 и соединен с вторым входом одноименного выходу элемента ИЛИ третьей группы элементов ИЛИ 6164, второй вход первого элемента ИЛИ 29 является входом стробов 5 устройства, второй вход каждого элемента ИЛИ первой группы элементов ИЛИ 3032 является одноименйым элементу ИЛИ младшим адресным 68 входом устройства, выход каждого отдельного элемента ИЛИ первой группы элементов ИЛИ 3032 соединен с одноименным этому элементу ИЛИ младшим адресным входом первого ОЗУ 33, младшим адресным входом второго ОЗУ 34, младшим адресным входом третьего ОЗУ 35 и младшим адресным входом четвертого ОЗУ 36, каждый отдельный адресный вход из старших адресных входов первого ОЗУ 33 соединен с одноименным старшим адресным входом второго ОЗУ 34 и является одноименным СтарШим адресным входом 911 устройства, каждый вход данных первого ОЗУ ЗЗ соединен с одноименным входом данных второго ОЗУ 34, с одноименным входом данных третьего ОЗУ 35, с одноименным входом данных четвертого ОЗУ 36 и является одноименным входом данных 12 14 устройства, Каждый отдельный адресный вход из старших адресных входов третьего ОЗУ 35 является одноименным старшим адресным входом настройки 1719 третьего ОЗУ устройства, каждый отдельный адресный вход из старших адресных входов четвертого ОЗУ 36 является одноименным старшим адресным входом 2123 управления четвертого ОЗУ устройства, каждый отдельный адресчый вход из старших адресных входов ПЗУ 37 является одноименным старшим адресным входом управления кодом 2426 ПЗУ устройства, вход выборки третьего ОЗУ 35 является входом 16 выборки третьего ОЗУ устройства, вход выборки четвертого ОЗУ 36 является входом 20 выборкичетвертого ОЗУ устройства и соединен с входом выборки ПЗУ 37, каждый отдельный выход третьего ОЗУ 35 является одноименйым выходом данных третьего ОЗУ устройства 8183 и соединен стретьим входом одноименного выходу элемента ИЛИ третьей группы элементов ИЛИ 6164, каждый отдельный выход четвертого ОЗУ 36 является одноименным в ходом данных четвертого ОЗУ устройства 8486 и соединен с одноименным младшим адресным входом ПЗУ 37, каждый отдельный выход которого соединен с четверть% -входом" однойменного выходу элемента ИЛИ третьей группы элементов ИЛИ 6164; число элементов И в разных группах элементов И 3840, 4143,4446 в общем случае различно,Устройство имеет три режима: настройки, генерациии очистки, которые чередуются между собой. В режиме настройки на входе управления 2 поддерживается сигнал низкого уровня, блокирующий работу формирователя импульсов 27, двоичного счетчика 28, триггеров всех групп триггеров 4749, 50.525355 регистра 64, при этом на выхбдах каждого из упомянутых устройств поддерживаются нулевые сигналы,В этом режиме в определенные словапервого ОЗУ 33, второго ОЗУ 34, третьего ОЗУ 35 и четвертого ОЗУ 36 заносится управляю щая информация как в обычные ОЗУ (характер этой информации будет пояснен ниже), Для этого, например, при обращении к первому ОЗУ 33 устанавливается двоичный код адреса на младших и старших адресных входах устройства 68, 911. определенный код адреса поддерживается на старших адресных входах 1619 настройки, старших адресных входах управления 21.;,23, старших адресных входах управления кодом 2426; устанавливается сигнал высокого уровня на входе 3 выборки первого ОЗУ 33; двоичный код записываемых данных на входах данных настройки 1214, Затем устанавливается признак записи (высокий уровень) на вход управления записью/чтением 4 устройства, после чего выдается стробиру.ощий импульс на вход 5 стробов устройствз. На входе 15 выборки второго ОЗУ, входе выборки 16 третьего ОЗУ и входе выборки 20 четвертого ОЗУ поддерживается сигнал низкого уровня.При этом прои ойдет запись данных в слово первого ОЗУ 33, За-. л снимаются стробирующий импульс с входа 5 стробов устройства, признак записи с входа управления записью/чтением 4, чем завершается цикл записи данных в первое ОЗУ 33. Этот цикл выполняется ан.логичным образом для всех слов первого О. 33, второго ОЗУ 34, третьего ОЗУ 35, и четвертого ОЗУ 36, в которые заполнится управляющая информация. Для считывания хранящейся в первом ОЗУ 33,втором ОЗУ 34, третьем ОЗУ 35 и четвертомОЗУ 36 информации на вход управления записью/чтением устанавливается в анало 5 гичном цикле признак чтения (низкийуровень), считываемые данные первого ОЗУ33 снимаются с выходов данных 7577 первого ОЗУ устройства, данные второго ОЗУ34 - с выходов 7880 данных второго ОЗУ10 устройства, данные третьего ОЗУ 35 - с выходов данных 8183 третьего ОЗУ, данныечетвертого ОЗУ 36 - с выходов данных8486 четвертого ОЗУ устройства. Доступность информации первого ОЗУ 33, второго15 ОЗУ 34, третьего ОЗУ 35 и четвертого ОЗУ36 на выходах устройства позволяет использовать их в качестве промежуточных буферов для накопления управляющейинформации,20 Характер управляющей информации определяется функцией устройства, т.е. асинхронного или периодического формирования илогического сложения комбинаций ймпульсов различной программируемой фазы и дли 25 тельности на нескольких параллельныхвыходах устройства, Каждая отдельная комбинация импульсов на выходах заранее задана. Длительность импульсов и фазаобозначается синхронно формируемыми30 стробами. Например, для восьмиканального(имеющего восемь выходов) устройства возможны основные параллельные комбинацииимпульсов на выходах:01000100 - первая,11001100 - вторая,35 11101110 - третья,11111111 - четвертая (последняя),где левая цифра соответствует первому выходу 72, а правая последнему выходу 74 устройства,40 В пределахдействия одного синхронногоимпульса эти комбинации могут быть допол нены начальными комбинациями:01000000 - первая,00000100 - вторая,45 11000000 - третья,00001100 - четвертая,11100000 - пятая,00001110 - шестая,11110000 - седьмая,50 00001110 - , восьмая (последняя),где левая цифра соответствует первому выходу 72, а правая - последнему выходу 74 устройства, или произвольными комбинациями.В первом ОЗУ 33, втором ОЗУ 34, третьем55 ОЗУ 35 и четвертом ОЗУ 36 каждомусинхронно формируемому на выходах стробу поставлено в соответствие слово, чей адрес вдвоичном коде соответствует порядковомуномеру строба, Поэтому для формированияна выходах устройства в режиме генерацииосновной комбинации импульсов, например, длительностью в М стробов и начинающейся со строба К, необходимо вопределенный разряд К-го слова и в тот жеразряд (К+М)-го слова первого ОЗУ 33 занести единицу(распределение разрядов будет помещено ниже).Для формирования на выходах устройства в режиме генерации дополнительнойкомбинации импульсов, например второй,необходимо код этой дополнительной комбинации занести в слово второго ОЗУ 34 илитретьего ОЗУ 35, адрес которого соответствует порядковому номеру строба, на котором формируется дополнительнаякомбинация. Основное различие между вторым ОЗУ 34 и третьим ОЗУ 35 состоит в том,что данные каждого слова второго ОЗУ 35каждой зоны данных логически связаны сданными одноименного слова первого ОЗУ33, а у третьего ОЗУ 35 эта связь автоматически действует в пределах одной зоны данных.Третье ОЗУ 35 при этом предназначенодля формирования постоянных комбинацийимпульсов, не изменяющихся в пределахнескольких периодов. Наличие старшихвходов управления 17.19 позволяет выбирать одну определенную комбинацию импульсов из нескольких возможных, заранеезаписанных в третье ОЗУ 35.Четвертое ОЗУ 36 и ПЗУ 37 предназначены для формирования модифицированных комбинаций импульсов (например,наложения на комбинации импульсов кодовсимволов),Функционирование четвертого ОЗУ 36аналогично функционированию третьегоОЗУ 35.Перед переходом из режима настройкив режим генерации на вход выборки 3 первого ОЗУ вход выборки 15 второго ОЗУ, входвыборки 16 третьего ОЗУ и вход выборки 20четвертого ОЗУ подаются сигналы высокогоуровня, Сигналы низкого уровня подаются навход управления записью/чтением 4 и входстробов 5, младшие адресные входы устройства 68.На старшие адресные входы устройства911 старшие адресные входы настройки1719 старшие адресные входы управления2129 и старшие адресные входы управлениякодом 24.26 подаются определенные двоичные коды. Эти сигналы поддерживаются втечении всего режима генерации.В режиме генерации на входуправления2 подается сигнал высокого уровня, разрешающий работу формирователя импульсов 27,двоичного счетчика 28, триггеров всех групптриггеров 4749, 5052,. 53.55, регистра5 10 15 40 45 .третьем выходе собом 50 20 25 30 35 выхода 64. При этом на выходах формирователя импульсов 27 формируются тактовые импульсы, поступающие на тактовый вход счетчика 28, входы стробов первого ОЗУ 33, второго ОЗУ 34, третьего ОЗУ 35, четвертого ОЗУ 36, регистра 64 и все вторые входы элементов И групп элементов И 3540, 4143, ,4446, соответственно. В результате на выходах счетчика 28 будут формироваться адресные коды, произойдет синхронное считывание информации из слов первого ОЗУ 33, второго ОЗУ 34, третьего ОЗУ 35 и четвертого ОЗУ 36, начиная с первого слова. Информация с выходов первого ОЗУ 33 поступит на первые входы элементов И групп элементов И 3840, 4143, ,.4446. Информация с выходов второго ОЗУ 34 поступит на вторые входы элементов ИЛИ 6163, Информация с выходов третьего ОЗУ 35 поступит на третьи входы элементов ИЛИ 6163; Информация с выходов четвертого ОЗУ 36 поступит на младшие адресные входы ПЗУ 37, а с его выхода - на четвертые входы элементов ИЛИ 61,63. Считывание прекращается при снятии с входа управления 2 сигнала высокого уровня, чем устройство переводится в режим настройки. Этот перевод произойдет после того, как адресный код, присутствующий на выходах двоичного счетчика 28, будет преобразован схемой селекции кода 59 в сигнал высокого уровня на выходе признака 71.Формирователь импульсов 27 формирует тактовые импульсы таким образом, что фронт импульса на его третьем выходе опережает по времени фронт импульса на его втором выходе, а фронт импульса на его втором выходе опережает по времени фронт импульса на его первом выходе. Срезы сформированных импульсов имеют обратный порядок, т,е. срез импульса на его первом выходе опережает по времени срез импульса на его втором выходе, а срез импульса на его втором выходе опережает по времени срез импульса на его Формирователь импульсов реализуется в соответствии с а.с. 1264315, кл. Н 03 К 3/64 от 15.10,86, бюл, 38 или каким-либо другим споВ результате такого формирования тактовых импульсов в то время, когда на выходах первого ОЗУ 33 находится код, на вторые входы всех элементов И всех групп элементов И 3840, 4143, 4446 с первого выхода формирователя импульсов 27 поступает тактовый импульс, Этот тактовый импульс поступит на тактовый вход определенного О-триггера из групп триггеров 4749 50.52, .5355 в том случае, если на выходе определенной группы выходов первого ОЗУЗЗ одноименному элементу И и триггеру соответствующих групп, присутствует единичный сигнал. Т,О, элементы И групп элементов И 3840, 41;43, 44,46 пропускаютили не пропускают тактовые импульсы на входы 0-триггеров групп триггеров 4749, 5052, , 5355. Каждый 0 триггер из групп триггеров 4749, 50,52, 5355 работает в счетном режиме, т,е. у каждого 0-триггера на 0-вход подается информация с его обратного выхода (такойвариант называется иногда Т-триггером), если на тактовый вход 0-триггера в счетном режиме подается единичный импульс и О-триггер, находится в единицном состоянии, тоон переводится в нулевое состояние. Если на тактовый вход 0-триггера в счетном режиме пбдаетсяединичный импульс и О-триггер находится в нулевом состоянии, то он переводигся в единичное состояние, В результате езаимодействия первого ОЗУ ЗЗ, элементов И груПп элементов И 38.40, 41.43, , 4446 и триггеров групп триггеров 47.49, 5052;5355 происходит формирование управляющих импульсов на выходах триггербв групп триггерое 4749, 5052, , 5355, которые затем шифратором 60 преобразуются в основные комбинации ймпульсбв. "Определенный выход определенной группы выходов первого ОЗУ 33 управляет одной из основных комбинацийимпульсов на выходах 7274. Основных комбинаций импульсов меньшечем выходов у первого ОЗУ ЗЗ, поэтому выходы первого ОЗУ 33 разделены на груйпы все выходы определенной группы первого ОЗУ 33 управляют одной основной комбйнацией импульсов на выходах 7274; Наличие нескольких выходов у первого ОЗУ 33. управляющих одной и той же комбинацией основных импульсов на выходах обеспечивает многоканальные и независимое управление включейием или выключением этой комбинации на выходах 7274, а наличиенескольких групп выходов у первого ОЗУ 33, управляющйх различными комбинациями основных импульсов на выходах, обеспечивает многоканальное и независимое управление включением или вйключением различных основных комбинаций импульсов на выходах устройства 7274, независимо формируемые комбинации импульсов логически складываются,. Это достигается за счет описанных далее взаимосвязей между первым ОЗУ 33, группами элементов И 38.40, 41,43; 4446 и группами триггеров 47.49, 5052, .,5355;Определенный выход, входящий в определенную из групп выходсе первого ОЗУ 33, соединен с первым входом элемента И, од ноименного выходу и входящему в группу элементов И 3840,4143,;44,46, одноименную группе выходов первого ОЗУ 33. Выход каждого определенного элемента И,входящего в определенную из групп элементов И 3840,4143,;,44.46 соединен с тактовым входомодноименного элементу И триггера, входящего в одноименную группу элементов И 3840, 414344, 46 10 группу триггеров 4749, 50.52, ., 5355 Выход определенного триггера, входящего в определенную из групп триггеров 4749,5052, , 5355, соединен с одноименным триггеру входом одноименного группе григгероа элемента ИЛИ второй группы элемен 15 тов ИЛИ 5658. Выход определенногоэлемента ИЛИ второй группы элементовИЛИ 5658 соединен с одноименным элементу ИЛИ входом шифратора 64,20 Т.О, определенный элемент ИЛИ второй группы элементов ИЛИ 5658 предназначен для сложения по ИЛИ управляющих сигналов на выходах одноименной элементу ИЛИ труппы триггеров, чем и обеспечивается многоканальное и независимое 25 управление включением или выключением определенной" основной комбинации имиульсбв.В качестве стробов импульсов программируемой фазы и длительности используют 30 ся задние фронты импульсбв на выходах стробов 6567.Шифратор 60 предназначен для преобразования. сигналов, присутствующих на выходах элементов ИЛИ группы элементов 35 ИЛИ 5658, в сигналы основной комбинации импульсов, которые логически складываются с информацией на выходах второго ОЗУ 34, третьего ОЗУ 35 и ПЗУ 37 третьей 40 группой элементов ИЛИ 6163.Шифратор 60 представляет из себя комбинационную схему, которая функциониру.; ет по определенному правилу: в том случае, если только на однбм из его входов есть 45 сигнал"высОкого уровня, то формируютсяосновная комбинация импульсов, определяемая группой выходов первого ОЗУ 33, одноименной входу шифратора 60; в том случае, если на нескольких из входов шиф ратора 60 есть сигналы высокого уровня, тоформируется основная комбинация импульсоа, определяемая группой выходов первого ОЗУ 33, одноименной старшему по номерувходу шифратора 60. Причем основ ные комбинации импульсов подобраны так,что основная комбинация импульсов с меньшим номером поглощается при логическом сложении комбинацией с большим номером, т.е, первая поглощается второй, вторая - третьей (понятно, что и первая - третьей),а последняя поглощает любую из основныхкомбинаций импульсов.Если на входах шифратора 60 присутствуют нулевые сигналы, то и на его выходахнулевые сигналы.Параллельный регистр 64 предназна.чен для хранения комбинации импульсов.Запись в регистр 64 - по срезу импульсагенератора 27. Схема селекции кода 59предназначена для формирования сигналапризнака (высокий уровень) при поступлении на ее входы одной определенной комбинации сигналов с выходов счетчика 28 иподдержания низкого уровня на своем выходе в случае остальных комбинаций сигналов с выходов счетчика 28. Схема селекциикода 28, представляет из себя комбинационную схему (например ПЛМ) настроеннуюна эту одну определенную комбинацию сигналов.Наличие младших адресных входов 68и старших адресных входов 9.11 позволяетобеспечить взаимосвязанную генерациюгрупп многофазных импульсов за счет занесения управляющей информации в различные зоны памяти первого ОЗУ 33 и второгоОЗУ 34. Эти зоны получаются за счет независимой подачи управляющих кодов настаршие адресные входы 911.Отдельные старшие входы настройки1719 третьего ОЗУ позволяют использовать наложение одинаковой информациимногофазных импульсов в различные периоды, т,к. отсутствует жесткая привязка к зоне первого ОЗУ 33,Выходы первого ОЗУ 33 пронумерова-.ны таким образом, что первый выход первойгруппы выходов является первым выходомпервого ОЗУ 33, второй выход первой группы выходов - . вторым выходом первого ОЗУ33 и т.д., последний выход первой группывыходов-(и)-м выходом первого ОЗУ 33,первый выход второй группы выходов -(и 1+1)-м выходом первого ОЗУ второй выходвторой группы выходов - (п +2)-м выходомпервого ОЗУ 33, и т.дпоследний - (и г+пг)-мвыходом первого ОЗУ 33, и т,д., первый выход последней группы выходовп 1+п 2+п+1)-м выходом первого ОЗУ 33,второй выход последней группы выходов -(п 1+пгпы+2)-м выходом первого ОЗУ33, последний выход последней группы выходов - (п 1+п 2п-+п)-м выходом первого ОЗУ 33, т.е. этим выходом первого ОЗУйрисвбена сквозная нумерация,Раздельные входы, вход 3 выборки первого ОЗУ, вход 15 выборки второго ОЗУ,вход 16 выборки третьего ОЗУ, вход 20 выборки. четвертого ОЗУ обеспечивают независимое управление каждым ОЗУ с цельюего как заполнения, так и считывания,Перед переходом иэ режима настройкив режим обнуления на вход выборки 3 пер 5 вого ОЗУ, входвыборки 15 второго ОЗУ,входвыборки 16 третьего ОЗУ, вход выборки 20четвертого ОЗУ, подаются сигналы высокого уровня. Сигнал высокого уровня подаетсяна вход управления записью/чтением 4,10 сигналы низкого уровня подаются на входстробов 5 и младшие адресные входы устройства 68,На старшие адресные входы 911 устройства,старшие адресные входы настрой 15 ки 1719, старшие адресные входы 2123управления, старшие адресные входы2426 управления кодом подается определенный двоичный код. На входы данных настройки 12.14 подаются сигналы низкого20 уровня. Эти сигналы поддерживаются в течении всего режима обнуления, В режимеобнуления на вход управления 2 подаетсясигнал высокого уровня, разрешающий работу формирователя ймпульсов 27, двоично 25 го счетчика 28 триггеров всех групптриггеров 4749, 5052, 5355, регистра64. При этом на выходах формирователя импульсов 27 формируются тактовые импульсы, поступающие на тактовый вход счетчика30 28, вход стробов первого ОЗУ 33 второгоОЗУ 34, третьего ОЗУ 35 и четвертого ОЗУ36, все вторые входы элементов И группэлементов И 3840, 414544.46, соответственно. Поскольку первое ОЗУ 33 нахо 35 дится в режиме записи, на выходахприсутствуют только сигналы низкого уровня, которые блокируют прохождение стробов через элементы И групп элементов И3840, 4143, 4446 на входы Э-тригге 40 ров.В результате на выходах счетчика 28.-будут формироваться адресные коды, произойдет синхронная запись нулевой информации в слова первого ОЗУ 33, второго ОЗУ45 34, третьего ОЗУ 35 и четвертого ОЗУ 36,- начиная с первого слова, Считывание прекращается при снятии со входа управления2 сигнала высокого уровня, чем устройствопереводится в режим настройки, Этот пере 50 вод произойдет после того, как адресныйкод, присутствующий на выходах двоичногосчетчика 28, будет преобразован схемой селекции кода 59 в сигнал высокого уровня навыходе признака 71.55 В результате первое ОЗУ 33, второеОЗУ 34, третье ОЗУ 35 и четвертое ОЗУготово к приему новой управляющей информации. Независимое управление режимомочистки позволяет работать как с накоплением управляющей информации в разли

СмотретьЗаявка

4886774, 29.11.1990

ЦЕНТРАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО "АЛМАЗ"

КУЛАКОВ МИХАИЛ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: H03K 3/64

Метки: генератор, многофазный, программируемый, тактовый

Опубликовано: 30.12.1992

Код ссылки

<a href="https://patents.su/12-1785069-programmiruemyjj-mnogofaznyjj-taktovyjj-generator.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый многофазный тактовый генератор</a>

Предыдущий патент: Электростатический генератор

Следующий патент: Преобразователь перемещения в код

Случайный патент: Способ получения -галактозидазы