Резервированная вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

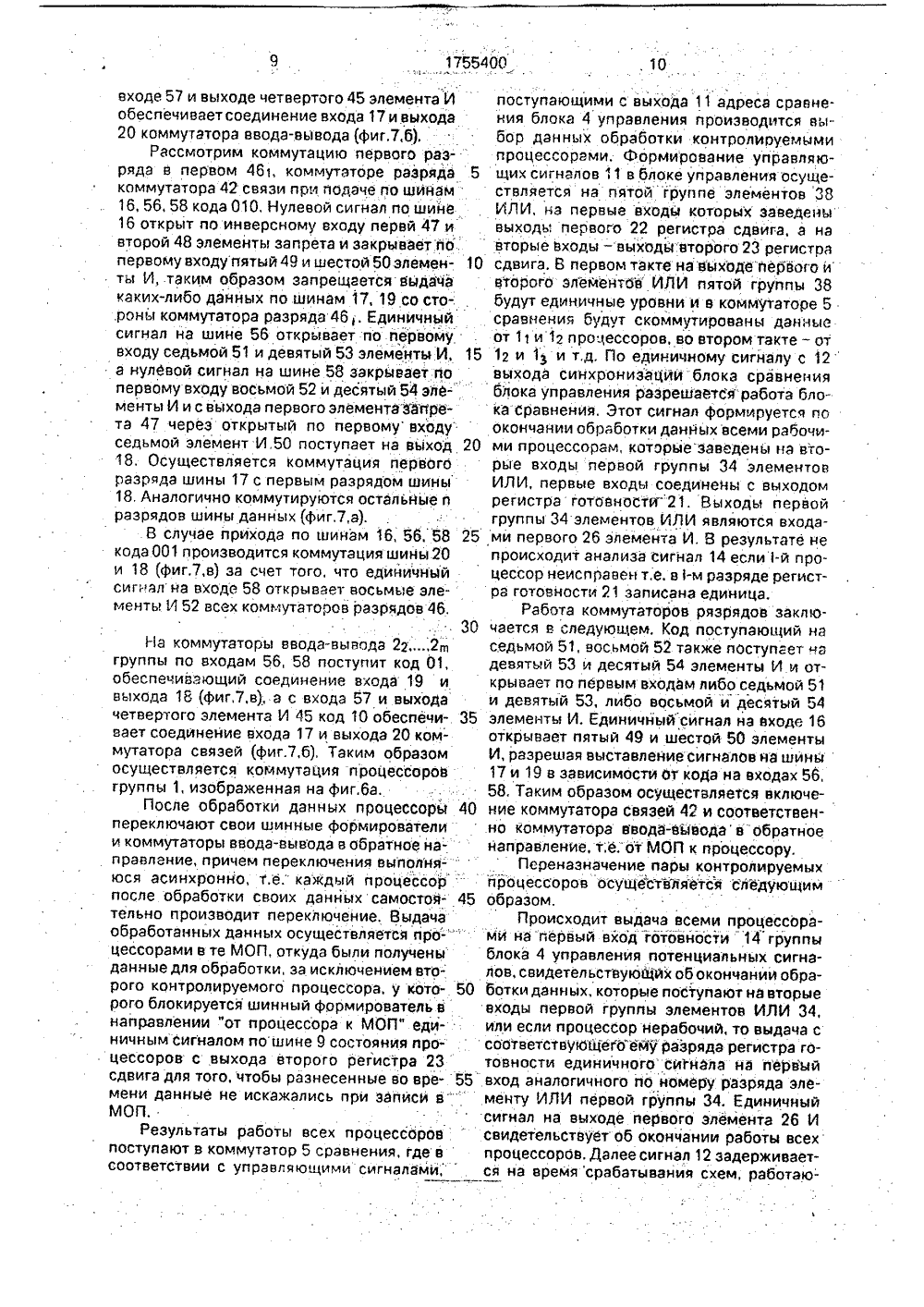

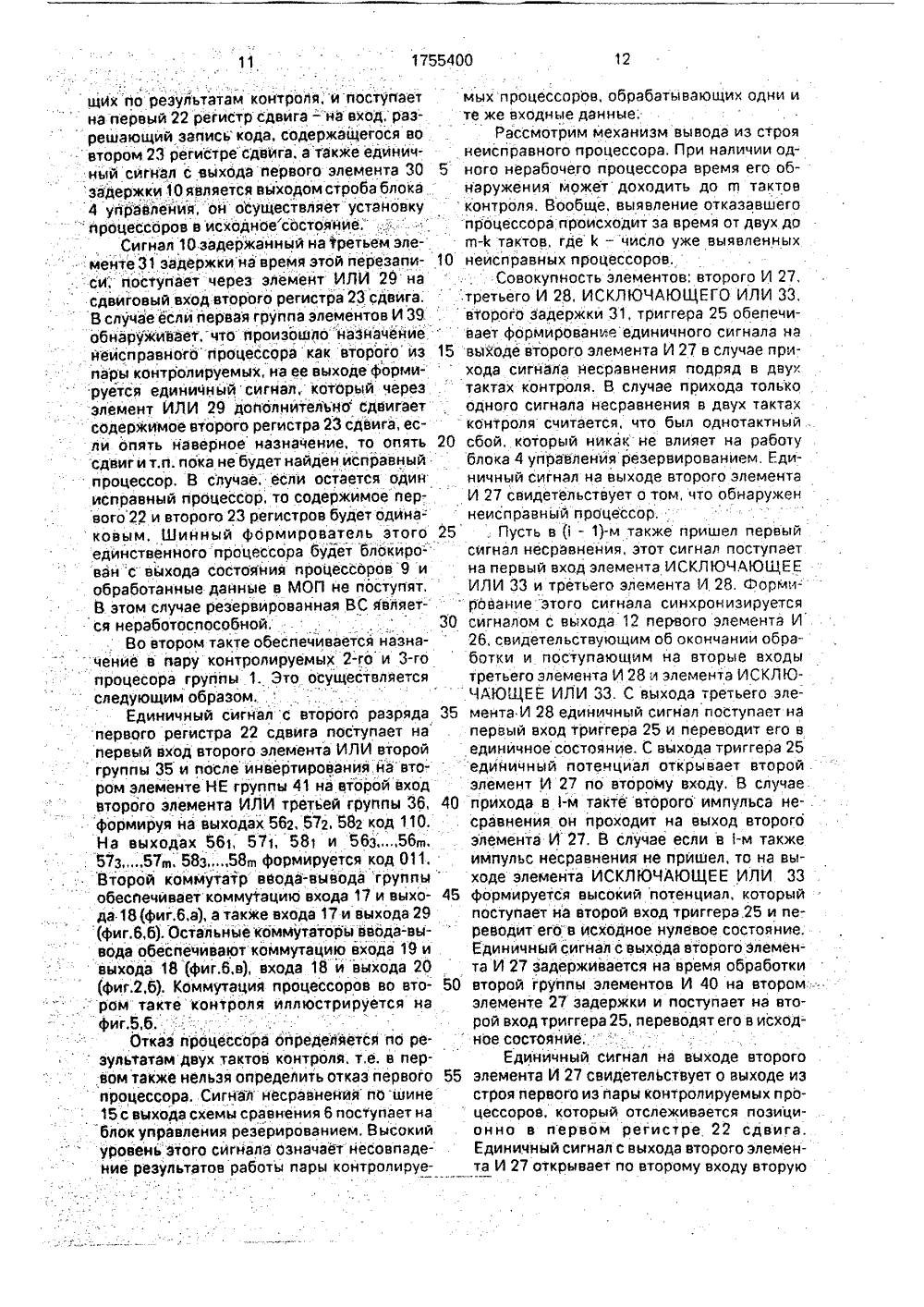

5400 А СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 10/ОО, С 06 ОСУУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯ РИ ГКНТ СССР 51)5 ПИСАНИЕ ИЗОБРЕТЕНИЯ ВИДЕТЕЛ ЬСТВУ АВТОРСКОМ.В.СиНАЯ ВЫЧИСЛИ(54) РЕЗЕ Р В И РО ВА ТЕЛЬНАЯ СИСТЕМА (57) Использование; многопроц,ссорных в мах для обеспечения в отказоустойчивых ычислительных систеперекрестной комму(21) 4838473/24(56) Авторское свидетельство СССРК. 1492973, кл. 6 06 Е 15/16, 1987.Авторское свидетельство СССРМ 1494763, кл. О Об Р 11/20, 1989,Авторское свидетельство СССРК 1579443, кл, 8 Об Г 11/20, 1988. Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых многопроцессооных вычислительных систем (ВС).Известна резервированная ВС, содержащая первый и второй резервируемые процессоры, первый и второй коммутаторы вывода информации, первый и второй модули памяти, устройство управления, первый и второй входы устройства управления, первый и второй коммутаторы авода информации, первый - четвертый входы устройства управления, третий резервируемый процессор, третий коммутатор вывода информации и третий коммутатор ввода информации; пя- тый выход и третий вход устройства управления, четвертый коммутатор вывода информации, шестой выход устройства уп-., равления, блок сравнения, седьмой выход устройства управления. В такой ВС имеютации резервируемых узлов. Сущность изобретения: система содержит 1 группу резервируемых процессоров (1), 1 группу коммутаторов ввода-вывода (2), 1 группу модулей памяти (3), 1 блок управления резервированием (4), 1 группу шинных формирователей (7), 1 коммутатор сравнения (5), 1 блок сравнения (6); блок управления резервированием (4) содержит 1 группу выходов управления коммутацией (8), 1 группу выходов состояния процессоров (9), 1 выход страба (10), 1 выход адреса сравнения (11), 1 выход синхронизации (12), 1 выход готовности (13), 1 группу входов готовности (14), 1 вход сравнения (15). 8-2-7- 5-6-15, .10 1-14, 1-2-3, 1-7, 9-7, 12-6, 11-5, 1 з.п.ф-лы, 2 табл, ф щийся резерв времени разделяется на такты. В каждом такте. параллельно работает пара процессоров; что позволяет путемсравнения результатов их работы выявить наличие отказа одного из этйх других процессоров. Номер отказавшего процессора оп- И ределяется в следующем такте путем Ф анализа параллельной работы следующей С) пары процессоров. Если снова результаты С) насовпали, то отказал тот процессор,"кото- рый работал в предыдущей паре и текущей паре.евайНедостатком данной ВС является ограниченная область применения по количеству одновременно реааемых задач, она содержит лишь два модуля памяти и три процессора.Известна резервированная ВС, содержащая и)+1 резервируемых процессоров, и) коммутаторов вывода информации, и) моду-8-ии аксаю-комФ даРЮф- иеиаамаимй тецевФа. 6:. чятОР сбюгй Составитель В,КоберникТехред М.Моргентал Корректор Н Бучо Редактор А,Яежнина Заказ 2900 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 45 гарина, 1 роизводственно-издательский комбинат "Патент", г. Ужгородлей памяти, устройство управления, группа мается решение о неисправности процессовходов которого подключена к контрольным ра, который контролировался в обеих парах, выходам пч+1 резервируемых процессоров, При обнаружении неисправного процессот коммутаторов ввода информации, первый ра внешний контроль прекращается, неиспивторойвходыкоторыхсоединенысоответ равный процессор восстанавливается, а ственно с выходами первого и второго, и исправные впроцессоров на зто время подтретьего, ., т-го и пз-го, -т-го и первого ключаются только к соответствующим гл момодуля памяти, информационные входы дулям памяти.второго, третьего, , а-го, а+1-го процес- Недостатком ВС является низкая достосоров соединены с выходами соответствен верность контроля, так как в случае отказа но первого, второго, , гп-го и в-го процессоравмоментназначенияеговпару коммутаторов ввода информации, а инфор- контролируемых время обнаружения его отмационный вход первого процессора соеди- каза составит 2 или (оп+1) тактов,нен непосредственно с выходом первого Целью изобре ения является повыше- модуля памяти, информационные выходы 15 ние надежности функционирования резервторого, третьего, е-го, в+1-го резерви- вированной ВС путем обеспечения руемых процессоров соединены соответст- перекрестной коммутации резервируемых венно с входами первого, второго, ., процессоров и модулей памяти.гп-го, т-го коммутаторов вывода информа- Поставленная цель достигается тем, что ции, первый и второй выходы которых сое в резервированную вычислительную систединены соответственно с входами первого му. содержащую группу резервируемых и второго, второго и третьего гл-го ипроцессоров; группу коммутаторов вводае-го, а-го и первого модулей памяти, а ин- вывода, группу модулей памяти, коммутатор формационный выход первого процессора сравнения, блок сравнения и блок управлесоединен непосредственно с входами пер ния резервировайием,входсравнения котового модуля памяти, управляющие входы рого подключен к выходу блока сравнения, резервируемых процессоровподключены к первый и второй информационные входы первой группе выходов устройства управле- которого соединены с одноименными выхония, вторая группа выходов которого под- . дамикоммутаторасравнения, входуправлеключена к управляющим входам 30 ния котооого соединен с выходом адреса коммутатора ввода и вывода информации, сравнения блока управления резервировакоммутатор сравнения. информационные нием, группа входов готовности процессовходы которого соединены с информацион- ров которого подключена соответтсвенно к ными выходами процессоров, управляю- первым выходам готовности резервируещий вход - с выходом устройства 35 мых процессоров группы, а группа выходов управления, блок сравнения, выходы кото- управления коммутацией которого подклюрого подключены к выходам коммутатора чена к входам управления соответствующих сравнения, а выход блока сравнения соеди- коммутаторов ввода-вывода группы. первые нен с входом устройства управления. информационные входы-выходы которыхВ данной системе отказ резервируемых 40 соединены с информационными входамипроцессоров фиксируется внешним контро- выходами соответствующих модулей памялем, э также встроенным контролем, если ти группы, дополнительно содержит группу он позволяет обнаружить этот отказ. Внеш- шинных формирователей, первые информаний контроль правильности функциониро- ционные входы-выходы которых соединены вания процессоров осуществляется 45 с информационными входами-выходами сопосредством устройства управления путемответствующих резервируемых процессореконфигурацииВСвкаждомтэктеконтро- ров группы, вторые информационные ля. Устройство управления обеспечивает входы-выходы шинных формирователей - - назначения пэры проверяемых процессо- группысоединенысодноименнымивыходаров нэ очередной такт контроля, В резуль ми-входами соответствующих коммутатотате реконфигурации ВС зти процессоры ров ввода-вывода группы, входы строба подключаются к одному модулю памяти и которых соединены с одноименными входа- параллельно обрабатывают данные задачи ми соответствующих шинных формироватезтого модуля. В конце такта контроля ре- лейгруппыиподключеныквторымвыходам зультаты работы процессоров сравнивают готовности соответствующих резервируеся в блок сравнения. В следующем такте мых процессоров группы. выходы информаназначается новая пара проверяемых про- ционных входов-выходов которых цессоров, Если в двух тактах подряд про- подключены к соответствующим информаизошло несравнение результатов работы ционным входам коммутатора сравнения, апары проверяемых процессоров, то принц- выходы строба резервируемых процессоров1755400 5 6группы подключены к выходу строба блока групйы элементов И и группу элементов НЕуправления резервированием, выход сийх-: 41.ронизации контроля которого подключен к Коммутатор ввода-вывода(фйг.З) содеовходу синхронизации блска сравнения, ажит первый 42 и второй 43 коммутатор;выход состояния процессоров - к входам 5 связей, группу элемейтов запрета 44, четразрешения соответствующих шинных фор- . вертый элемент И 45,мирователей группы, информационный вы- Коммутатор связей (фиг.4) содержит иход каждого К коммутатора ввода-вывода одинаковыхкоммутаторов 46 разрядов - погруппы соединен с информационным вхо- числу разрядов шиныданных, каждый издом К+1-го коммутатора ввода-вывода груп которых содержитпервый 47, второй 48 элепы, информационный выход последнего из менты запрета, пятый 49, шестой 50, седькоторых подключен к информационному мой 51, восьмой 52, девятый 53 и десятый 54входу первого коммутатора ввоца-вывода, элементы И,группы, а выход готовности блока управле-На временных диаграммах фиг.5) обоэ ния резервированием является одноимен начены: 55 - сигнал на выходе первого эленым выходомсйстемы,.мента 30 задержки; 21121 п - состояниеНа фиг.1 представлена схема резерви-: регистра готовностй йроцессоров; 56 57рованной вычислительной системы; на 58 - сигналы управлния коммутаторамифиг.2 - структурная схема блока управления .ввода-вывода с выхода 8 управления коммурезервирбванием; на фиг.З - коммутатор 20 тацией группы блока 4 управления.ввода-вывода; на фиг,4 - коммутатор свя- Регистр 21 готовности процессоров созей; на фиг.5- временные диаграммы рабо- держит информацию о состоянии процессоты устройства; на фиг,6 - организация ров (исправен или неисправен), чтовозможных каналов связи между процесса- определяется состоянием разрядоврегистрами и модулями памяти ВС; на фиг.7 - 25 ра 2: если 1-й разряд в нулевом состоянии,возможные направления коммутации ком-1 процессор исправенесли в единичноммутатора ввода-вывода, неисправен.Резервированная вычислительная сис-Первый 22 второй 30 регистры сдвигатема (фиг.1) содержит группу резервируе- показываютместоположениепервогоивтомых процессоров 1, коммутаторов 2 30 рого контролируемых-процессоров, работаввода-вывода, модулей 3 памяти, блок 4 уп-; ющих в паре с одним МОП, Единичноеравления резервированием, коммутатор 5 состояние 1-го разряда первого 22 (второгосравнения, блок 6 сравнения, группу шин) регистра сдвига указывает на то, что 1-йных формирователей 7. Блок управления ре- процессор в данном такте является первымзервированием содержит группу выходов 8 35 (вторым) в паре параллельно работающихуправления коммутациями. группу выходов . процессоров,9 состояния процессоров, выход 10 строба Первая группа элементов И 39 предназблока управления резервированием, выход начена для обнаружения ситуации назначе 11 адреса сравнения блока управления ре- ния неисправного йроцесс 6 ра как второгозервированием, выход 12 синхронизаций 40 для пары контролируемых, Вторая группаблока сравнения, выход 13 готовности бло элементов И позволяет выводить в река управления резервированием, первую монт неисправные процессоры, т",е; перевогруппу 14 входов готовности блокауправле-: дить в единичное состоянйе разрядыния, вход 15 сравнения. Группа выходов 8 регистра 21 готовности процессоров.управления коммутацией подключена к од Регистр 21 сдвига предназначен для выноименным управляющим входам коммута- явления момента прекращения работы ВС.торов ввода-вывода группы 2, которые" Это произойдет когда останется один испсодержат также вход строба 16, первый 17 равный процессор.и второй 18 информационные входы-выхо-Контроль правильности функционироды, информационный вход 19 и выход 20. 50 вания процессоров ВС состоит в следую;щем Время выполнения задачиБлок управления фиг,2) содержит"ре- разбивается на такты, при этом в каждомгистр 21 готовности, первый - третий реги- такте назначается пара параллельно рабостры 22, 23 и 24 сдвига, триггер 25, первый тающих (проверяемых) процессоров, кото 26, второй 27 и третий 28 элементы И, эле рые подключаются к одному модулю памятимент ИЛИ 29,первый 30, второй 31 и третий и выполняют одни и те же инструкции надЧАЮ Е32 элементы задержкй, элемент ЗЗ ИСКЛЮ- одинаковыми исходными данным ф,6),и иг,ЩЕЕ ИЛИ, первую 34, вторую 35, ПриэтомвкаждомтактеодинМОПостаетсятретью 36, четвертую 37 и пятую 38 группы необслуженным, Результаты работы проэлементов ИЛИ, первую 39 и вторую 40 цессоров в конце каждого такта сравниваются. На следующий такт назначается новаяпара проверяемых процессоров, Отказавший процессор определяется по результатам его работы в двух смежных тактах. Еслипри работе в двух тактах подряд произошло 5несравнение результатов, то процессор,учавствовавший в работе в двух тактах подряд считается неисправным и выводится времонтную конфигурацию, а соответствующий ему по номеру МОП в дальнейшем ос.тается необслуженным. Если былонесравнение в первой паре, а во второйрезультаты работы совпали, то это значит,что имел место однотактный сбой, либо отказал первый из проверяемых процессоров 15группы, который будет выявлен в следующем цикле контроля. Резервированная ВСостается работоспособной, пока имеетсядва исправных процессора,Подключение процессоров к соответствующим модулям памяти осуществляется спомощыю группы коммутаторов 2 ввода-вывода, уйравление которыми осуществляетсясигналами с блока 4 управления в соответствии с содержимым регистра 22 сдвига и 25регистра 21 состояния процессоров.Возможные каналы связи между процессорами и МОП показаны на фиг,6 и втабл,1,Резервированная ВС работает следующим образом,В исходном состоянии группа 1 процессоров исправна, в МОП группы 3 находятсяданые, необходимые для обработки, во всехразрядах регйстра 21 готовности записаны 35нули, в первом 22 и третьем 24 регистрахсдвига записан код 10,00, во втором регистре сдвига - код 01,00, В этом состояниибудут контролироваться процессоры 11, 12(фиг,б,а). Это осуществляется путем коммутаций этих процессоров к первому 31 модулю памяти группы. Через шинныеформирователи 7 з,.,7 вгруппы процессоры 1 з 1 гпгруппы будут подключены соответственно к 32,3 еМОП группы. 45Шинные формирователи группы 7 управляются процессорами. В исходном состоянииони обеспечивают передачу даных для обработки из МОП в процессоры, После обработки данных процессорами, последние 50переводйт шинные формирователи в состояние, обеспечивающее передачу обрабо- .танных данных из процессора в МОП, Кактолько все обработанные дан ые будут выданы, шинные формирователи будут переведены процессорами в исходное состояние.Таким образом осуществляется связь между процессорами и МОП,Порядок подключения процессоров кмодулям показан в табл,2. Такая коммутация процессоров осуще- ствляе,ся следующим образом и она поясняется с помощью временных диаграмм фиг,4) выдачи управляющих сигналов на коммутаторы 2 ввода-вывода группы.В первом такте контроля контролируются 11 и 12 процессоры группы, С выхода первого регистра 22 сдвига единичный сигнал поступает на первый вход первого элемента ИЛИ 35 второй группы, а также через первый элемент НЕ группы 41 - на второй вход первого элемента ИЛИ 35 второй группы, В результате на выходе 56 первого элемента ИЛИ второй группы 35 формируется единичный сигнал, который поступает на первый входпервого элемента ИЛИ четвертой 37 группы, создавая на его выходе 57 высокий потенциал, На вторые входы первых элементов ИЛИ второй группы 35 и первые. входы первых элементов ИЛИ пятой группы 38 поступает сигнал с первого раз-. ряда регистра 21 готовности процессоров. Так как в исходном состоянии все процессоры исправны. то во всех разрядах регистра 21 готовности будут записаны нули. На выходе 581 первого элемента ИЛИ 36 четвертой группы будет сформирован нулевой сигнал, На первый коммутатор 21 ввода- вывода группы по входам 561, 571, 581, шины 8 поступит код 110, С выходов 2,гп первого регистра 22 сдвига нулевые сигналы поступят на первые входы элементов 352,35 п второй группы ИЛИ и проинвертированные на элементах НЕ 412,".,42 П групппы поступят на элементы 36236 п третьей группы ИЛИ. В результате на выходах элементов 352,35 п ИЛИ, 582,58 п и соответственно на выходах 57257 п элементов 37237 в четвертой группы ИЛИ сформируются единичный потенциалы, на выходах 56256 п - нулевые йотенциалы.На коммутаторы 222 п группы по входам 56, 57 и 58 шины 8 поступает код 011.На коммутаторы авода-вывода по вторым управляющим входам 16 с процессоров поступают нулевые сигналы, свидетельствующие о готовности процессоров принять данные, Так как на выходах 56, 57, 58 не все единицы, то на выходе четвертого элемента И 45 нулевой потенциал, который открывает по запрещающему входу элементы группы запрета 44, разрешая прохождение управляющих сигналов 56 на первый коммутатор 42 связей, 57 - на второй коммутатора 43 связей, 58 - на первый коммутатор 42 связей, На 21 коммутаторе ввода-вывода будет., -. осуществлена следующая коммутация. Код 10 на входах 56, 58 обеспечивает соединение входа 17 и выхода 18 коммутатора ввода-вывода, что показано на фиг.7 а, Код 10 навходе 57 и выходе четвертого 45 элемента Иобеспечивает соединение входа 17 и выхода20 коммутатора ввода-вывода (фиг.7,б).Рассмотрим коммутацию первого разряда в первом 461, коммутаторе разряда 5коммутатора 42 связи при подаче по шинам16, 56, 58 кода 010, Нулевой сигнал по шине16 открыт по инверсному входу первй 47 ивторой 48 элементы запрета и закрывает попервому входупятый 49 и шестой 50 элементы И, таким образом запрещается выдачакаких-либо данных по шинам 17, 19 со сто- ..роны коммутатора разряда 46,. Единичныйсигнал на шине 56 открйвает по.первомувходу седьмой 51 и девятый 53 элементы И, 15а нулевой сигнал на шине 58 закрывает г 1 опервому входу восьмой 52 и десятый 54 элементы И и с выхода первого элементазапрета 47 через открытый по первому входуседьмой элемент И,50 поступает на выход 2018, Осуществляется коммутация первогоразряда шины 17 с первым разрядом шины18, Аналогично коммутируются остальные иразрядов шины данных (фиг.7,а),В случае прйхода по шинам 16, 56, 58 25йода 001 производится коммутация шины.20и 18 (фиг,7,в) за счет того, что единичныйсигнал нэ входе 58 открывает восьмые элементы И 52 всех коммутаторов разрядов 46,30На коммутаторы ввода-вывода 222 гпгруппы по входам 56, 58 поступит код 01,обеспечивающий соединение входа 19 ивыхода 18 (фиг,7,в), э с входа 57 и выходачетвертого элемента И 45 код 10 обеспечивает соединение входа 17 и выхода 20 коммутатора связей (фиг.7,б), Таким образомосуществляется коммутация процессоровгруппы 1, изображенная на фиг,ба.После обработки данных процессоры 40переключают свои шинные формирователии коммутаторы ввода-выводэ в обратное направление, причем переключения выполня- "юся асинхронно, т.е." каждый процессор после обработки своих данных самостоятельно производит переключение, Выдачаобработанных данных осуществляется и ро-"цессорами в те МОП, откуда были полученыданные для обработки, за исключением вто-рого контролируемого процессора. у которого блокируется шинный формирователь внаправлении "от процессора к МОП" единичным сигналом по шине 9 состояния процессоров с выхода второго регистра 23сдвига для того, чтобы разнесенные во времени данные не искажались при записи в"МОП.Результаты работы всех процессоровпоступают в коммутатор 5 сравнения, где всоответствии с управляющими сигналами,поступающими с выхода 11 адреса сравнения блока 4 управления производится выбор данных обработкй контролируемыми процессорами, Формирование управляющих сигналов 1 в блоке управления осуществляется на пятой группе элементов 38 ИЛИ. нэ первые входы которых заведены выходы первого 22 регистра сдвига, э на вторые Входы - выходы второго 23 регистра сдвига. В первом такте на выходе первого и второго элементба ИЛИ пятой группы 38 будут единичные уровни и в коммутаторе 5 сравнения будут скоммутированы данные от 11 и 12 и ро ессоров, во втором такте - от 12 и 1 з и т,д, По единичному сигналу с 12 выхода синхронизации блока сравнения блока управления разрешается-работа блока Сравненйя. Этот сигнал формируется по окончании обработки данйых всеми рабочими процессорам, которые заведены на вторые входы первой группы 34 элементов ИЛИ, первые входы соединены с выходом регистра готовности. Выходы первой группы 34 элементов ИЛИ являются входами первого 26 элемента И. В результате не происходит анализа сигнал 14 если 1-й процессор неисправен т,е. в 1-м разряде регистра готовности 21 записана единица.Работа коммутаторов рязрядов заключается в следующем. Код поступающий на седьмой 51, восьмой 52 также поступает на девятый 53 и десятый 54 элементы И и открывает по первым входам либо седьмой 51 и девятый 53, либо восьмой и десятый 54 элементы И, Единичныйсигнал нэ входе 16 открывает пятый 49 и шестой 50 элементы И, разрешая выставление сигналов йэ шины 17 и 19 в зависимости от коДа на модах 56, 58, Таким образом осуществляется включение коммутатора связей 42 и соответственно коммутатора ввода-выводав обратное направление, т".е. от МОП к процессору.Переназначение пары контролируемых процессоров осуществляется следующим образом.Происходит выдача всеми процессорами на первый входготовности 14 группы блока 4 управления потенциальных сигналов, свидетельствуюЩйх об окончании обработки данных, которые поступают на вторые входы первой группы элементов ИЛИ 34, или если процессор нерабочий, то выдача с соответствукйцегоему разряда регистра готовности единичного сигнала на первый вход аналогичного по номеру разряда элементу ИЛИ первой группы 34. Единичный сигнал на выходе первого элемента 26 И свидетельствует об окончании работы всех процессоров, Далее сигнал 12 задерживается на время срабатывания схем. работаю1755400 12щих по результатам контроля, и поступает мых процессоров, обрабатывающих одни ина первый 22 регистр сдвига -"на вход, раз- те же входные данные;решающий запись кода, содержащегося во Рассмотрим механизм вывода из строявтором 23 регистре сдвйга. а также единйч- неисправного процессора. При наличии одный сигнал с выхода первого элемента 30 5 ного нерабочего процессора время его обзадержки 10 являетсявыходомстробаблока наружения может доходить до п тактов4 уйравления, он осуществляет устайовку контроля. Вообще, выявление отказавшего"процессбров в исходноесостояние. ., - .процессора происходит за время от двух доСигнал 10 задержанныйнаФретьем.эле- гпФ тактов, где 1 с - число уже выявленныхменте 31 задержки на время этой йерезапи неисправных процессоров,си; поступает через элемейт ИЛИ 29 наСовокупность элементов; второго И 27,сдвиговый вход второго регистра 23 сдвига. третьего И 28, ИСКЛЮЧАЮЩЕГО ИЛИ 33,В случае еслй первая группа элементов И 39 .второго задержки 31, триггера 25 обепечиобнаруживает,что произошлоназначение. вает Формирование единичного сигнала на .йеисправного процессора как второго из 15 вь ходе второго элемента И 27 в случае припары контролируемых, на ее выходе форми- хода сигнала несравнения подряд в двухруется единичный сигнал,. который через тактах контроля. В случае прихода толькоэлемент ИЛИ 29 дополнительно сдвигает, одного сигнала несравнения в двух тактахсодержимое второго регистра 23 сдвига, ес- контроля считается, что был однотактныйлй опять йзверное назначение, то опять 20 сбой, который никак не влияет на работу .сдвиг и т.п. пока не будет найден исправный блока 4 управлейия резервированием, Едипроцессор. В случае, если остается один ничный сигнал на выходе второго элементаисправный процессор, то содержимое пер- И 27 свидетельствует о том, что обнаруженвого 22 и второго 23 регистров будет одина- неисправный процессор.ковым, Шинный фбрмирователь этого 25Пусть в ( - 1)-м также пришел первыйединственного процессора будет блокиро- сигнал несравнения. этот сигнал поступаетван с выхода состояния процессоров 9 и на первый вход элемента ИСКЛЮЧАЮЩЕЕобработанные данные в МОП не поступят, ИЛИ 33 и третьего элемента И 28, ФормиВ этом случае резервированная ВС являет-рование этого сигнала синхронизируетсяся неработоспособной, .30 сигналом с выхода 12 первого элемента ИВо втором такте обеспечивается назна, свидетельствующим об окончании обрачение в пару контролируемых 2-го и 3-го ботки и поступающим на вторые входыпроцесора группы 1. Это осуществляется третьего элемента И 28 и элемента ИСКЛЮследующим образом:ЧАЮЩЕЕ ИЛИ 33, С выхода третьего элеЕдиничный сигнал с второго разряда 35 мента И 28 единичный сигнал поступает напервого регистра 22 сдвига поступает на первый вход триггера 25 и переводит его впервый вход второго элемента ИЛИ второй единичное состояние. С выхода триггера 25группы 35 и после инвертирования.на вто-.единичный потенциал открывает второйром элементе НЕ группы 41 на второй вход элемент И 27 по второму входу. В случае.второго элемента ИЛИ третьей группы 36, 40 прихода в -м такте второго импульса не- .формируя на выходах 56 г, 57 г, 58 г код 110 сравненйя он проходит на выход второгоНа выходах 561, 571, 581 и 56 з56 п, элемента И 27. В случае если в 1-м также57 з 57, 58 з,58 формируется код 011. импульс несравнения не пришел, то на выВторой коммутатр ввода-вывода группыходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33обесйечивает коммугацию входа 17 и выхо формируется высокий потенциал, которыйда 18(фиг.б,а), а также входа 17 и выхода 29 поступает на второй вход триггера.25 и пе(фиг.6,б), Остальнйе коммутаторы ввода-вы-реводит его в исходное нулевое состояние.вода обеспечивают коммутацию входа 19 и Единичный сигнал с выхода второго элеменвыхода 18 (фиг.б,в, входа 18 и выхода 20 та И 27 задерживается на время обработки(фиг.2,6). Коммутация процессоров во вто второй группы элементов И 40 на втором -"ром такв контроля иллюстрируется на элементе 27 задержки и поступает на втофиг,5,б..,рой входтриггера 25, переводятего висходОтказ процессора определяется по ре-ное состояние,зультатам двух тактов контроля. т,е, в пер- Единйчный сигнал на выходе второговом также нельзя определить отказ первого 55 элемента И 27 свидетельствует о выходе изпроцессора. Сигнал несравнейия пЬ шине строя первого из пары контролируемых про 15 с выхода схемы сравнения 6 поступает на цессоров, который отслеживается позициблокуправления резерированием, Высокий анно в первом регистре 22 сдвига.уровень этого сйгйала означает несовпаде- . Единичный сигнал с выхода второго элеменние результатов работы пары контролируе- та И 27 открывает по второму входу вторую1755400 14группу элементов И 40 и разрешает запись управления резервированием, труппа вхо единицы с 1-го разряда первого регйстра 22 дов готовности процессоров которого подсдвига в 1-й разряд региСтра 21 готовности ключенэ соответственно к первым вь ходампроцессоров, Теперь 1-й процессор считает готовности резервируемых процесссорс в ся неисправным. Коммутация 1-го коммута группы, а группа выходов управления ком.тора ввода-вывода изменяется следующим мутацией которого подключена к входамупобразом..: :, . равления соответствуюЩих коммутаторовКак только появляется единичный уро- ввода-вывода груйпй первые"ийформацивень на выходе 1-го разряда регистра готов- онные входы-выходы которых соединены с ности он поступает на вторые входы 1-х 10 информациоными входами-выходами соот- элементов ИЛИ второй 35 и третьей 36 груп- ветствующих модулей йамяти груййы, о т л ипы, формируя на их выходах 56, 581 и соот- ч а ю щ а я с я тем, что, с целью повышения ветственнонэвыходе 5711-гоэлементаИЛИ .надежности устройства путем обеспечения четвертой группы 37 высокие уровни, т;е. на перекрестной коммутаций резервируемых 1-й коммутатор ввода-вывода йо входам 56;, 15 процессов и модулей памяти, всистему вве 57;, 58 поступит код 111, Он сформирует дена группа шинныхформирователей, перединичный уровень на выходе четвертого вые информационйые входы-выходы элемента И 45, который закроет по запре- которых соединены с информационными щающемувходу элементы запрета группы входами-выходамисобвтетствующ 1 йх резер, а также осуществляют коммутацию вто вируемых процессоров группы, вторые инрого коммутатора 43 связей, соединяя входформационные входы-выходы шинных 19 и выход 20(фиг.б,г), коммутация первого формирователей группы соединены с одно- коммутатора 42 не происходит. Коммутация, имейными выходами-входами собтветствупроцессоров в а+(1 - 1) и гп+1 тактах изобра- . ющих коммутаторов ввода-вывода-группы, жена на фиг.6 в;г, а также поясняется вре входы строба которых соединены с одноменной диаграммой фиг,5, Коммутацияименными входамисоответствующих шиннеисравного процессора не происходит и ных формирователей группы и подключены его ГАЛОП остается необслуженным к вторым выходам готовности соответствующих резервируемых процессоров группы,Отказ резервированной ВС наступает в 30 выходы информационных входов-выходовслучае, если остается один рабочий процес- котррых подключены к соответствующим сор, об этом сйгнализирует единичный сиг- инфоомационным входам ксммутэтора нал на чевертом выходе 13 готовности блока сравнения, а выходы строба резервируемых 4 управления резервированием. Он форми-процессоров группы подключейы к выходу руется на п-м разряде регистра 24 сдвига, 35 строба блока управления резервированием,. сдвиговый вход которого соединен с выхо-. выход синхронизацйикойтроля- которогодом второго элемента И 27, После приходаподключен к входу синхронизации блока е -1 таких сигналов на щ-м разряде регист- сравнения, а выходы состояния процессора сдвига появляется единица, резервиро- " ров - к входам разрешения соответствую- ванная ВС неработоспособна, Таким 40 щих, шинных формирователей группы, образом, в предлагаемой ВС осуществляет- информационный выход каждого К коммутэся последовательный контроль работоспо- тора ввода-вывода группы соединен с ин. собности всех процессоров, покав. формационным входом К+1-го коммутатораконфигурации .ВС не останется один исп- . ввода-вывода группы, информационный выравный процессор, что обеспечивает павы ход последнего из которых подключен к иншение надежности ВС по сравнению с " формационномувходупервогокоммутатора прототипом. : . ввода-вывода группы; а выход готовйостиФ о р му л а и з о б р е т е н и я . блока управления резервированием являет 1. Резервированйая вычислительная ся одноименным выходом системы.система, содержащая группу резервируе 2. Система поп.1, отл и ча ющ а я с я мых процессоров, группукоммутатороввво- тем; что блок управления резервированием да-вывода, группу модулей памяти, содержитрег)лотрготйФости, первый-трекоммутатор сравнения, блок сравнения и тий регистры сдвига, триггер, три элемента блок управления резервированием, вход И, элемент ИЛИ, три элемента задержки, сравнения которого подключен к выходу 55 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, пять групп блока сравнения, первый и второй инфор-элементов ИЛИ, две группы элементов И и мационные входы которого соединены с од- группу элементов НЕ, причем выход регистноименными выходами коммутаторара готовности подключен к первым входам сравнения, вход управления которогосое- элементов И первой группы и элементов динен с выходом адреса сравненияблока ИЛИ первой группы, вторые входы которых16 1755400 Та бл и ца 1 82 а подключейы к соответствующим входам группы входов готовности процесоров блока; а вйходы - к соответствующим входам первого элемента И, выход которого является выходом синхронизации контроля блока 5 и подключен к первым входам второгоэлемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, через первый элемент задержки"-С"выходом строба и выходом сдвига йервого регистра сдвига и через первый и второй 10 элементы-задержки выход первого элемента И подключен к первому входу элемента ИЛИ; остальные входы которого подключены к выходам элементов И первой гругтпы; вторе входы которых подключены к инфор мацйонному входу второго регистра сдвига, вход сдвига которого подключен к выходу элемента ИЛИ, выход триггера соединен с первым входом третьего элемента И, выход которого "подключен к первым входам зле ментов И второй группы и входу-сдвига третьего регистра сдвига, а также через третий элемент задержки - к входу установки тригера, вход сравнения блока соедййен с вторыми входами второго и третьего эле ментов И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента И подключены к входу установки и входу сбоса триггера соответственно, выход готовности блока явля ется выходом старшего разряда третьего регистра сдвига, соответствующие разряды информационного выхода регистра готовности подключены к первым входам элементов ИЛИ второй и третьей групп, а информационного выхода - к выходам элементов И второй группы, вторые входы которых соединены с соответствующими разрядами информационного выхода первого регистра сдвига, соединенных также с первыми входами соответствующих элементов ИЛИ пятой группы, с вторыми входами соответствующих элементов ИЛИ второй группы и через соответствующие элементы НЕ группы с вторыми входами соответствующих элементов ИЛИ третьей руппы, информационный выход второго регистра сдвига является выходом состояния процессоров блоха, подключен к информационному входу первого регистра сдвига и сеединен с вторыми входами элементов ИЛИ пятой группы, выходы которых образуют выход адреса сравнения блока, выход элементов ИЛИ второй и третьей групп подключены к первому и второму входам соответствующих элементов ИЛИ четвертой группы, выходы которых и выходы соответствующих элементов ИЛИ второй и третьей групп составляют группу выходов управления коммутацией блока,

СмотретьЗаявка

4838473, 12.06.1990

ПУШКИНСКОЕ ВЫСШЕЕ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

КОБЕРНИК ВЛАДИМИР ВАСИЛЬЕВИЧ, НИКОЛАЕВ ВИКТОР ИВАНОВИЧ, СИДОРОВ СЕРГЕЙ ВАЛЕРЬЕВИЧ

МПК / Метки

МПК: G06F 15/16, H05K 10/00

Метки: вычислительная, резервированная

Опубликовано: 15.08.1992

Код ссылки

<a href="https://patents.su/12-1755400-rezervirovannaya-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Резервированная вычислительная система</a>

Предыдущий патент: Устройство для управления резервированной вычислительной системой

Следующий патент: Устройство для формовки выводов радиоэлементов

Случайный патент: Устройство для подачи изделий