Кодек блочной сигнально-кодовой конструкции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

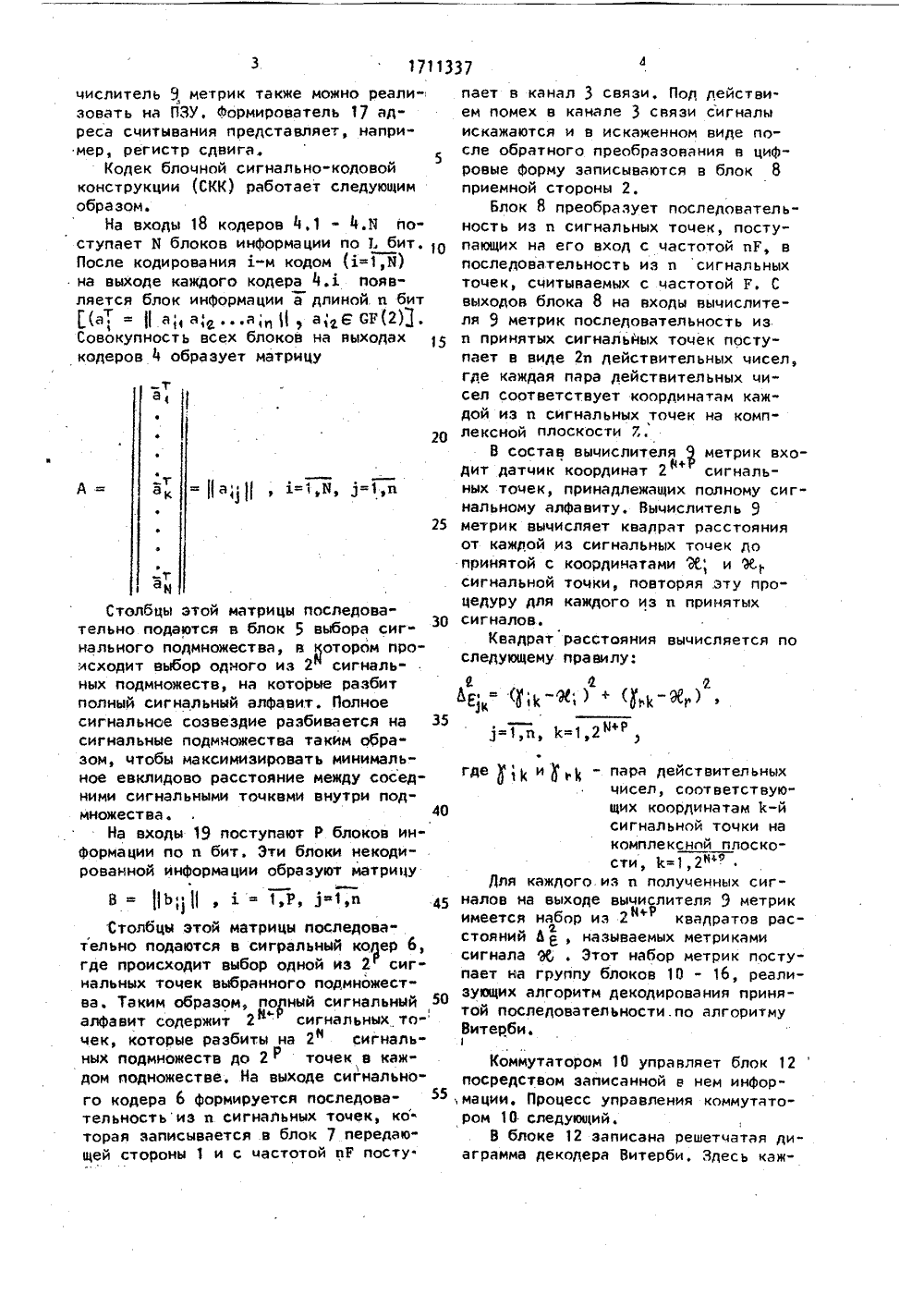

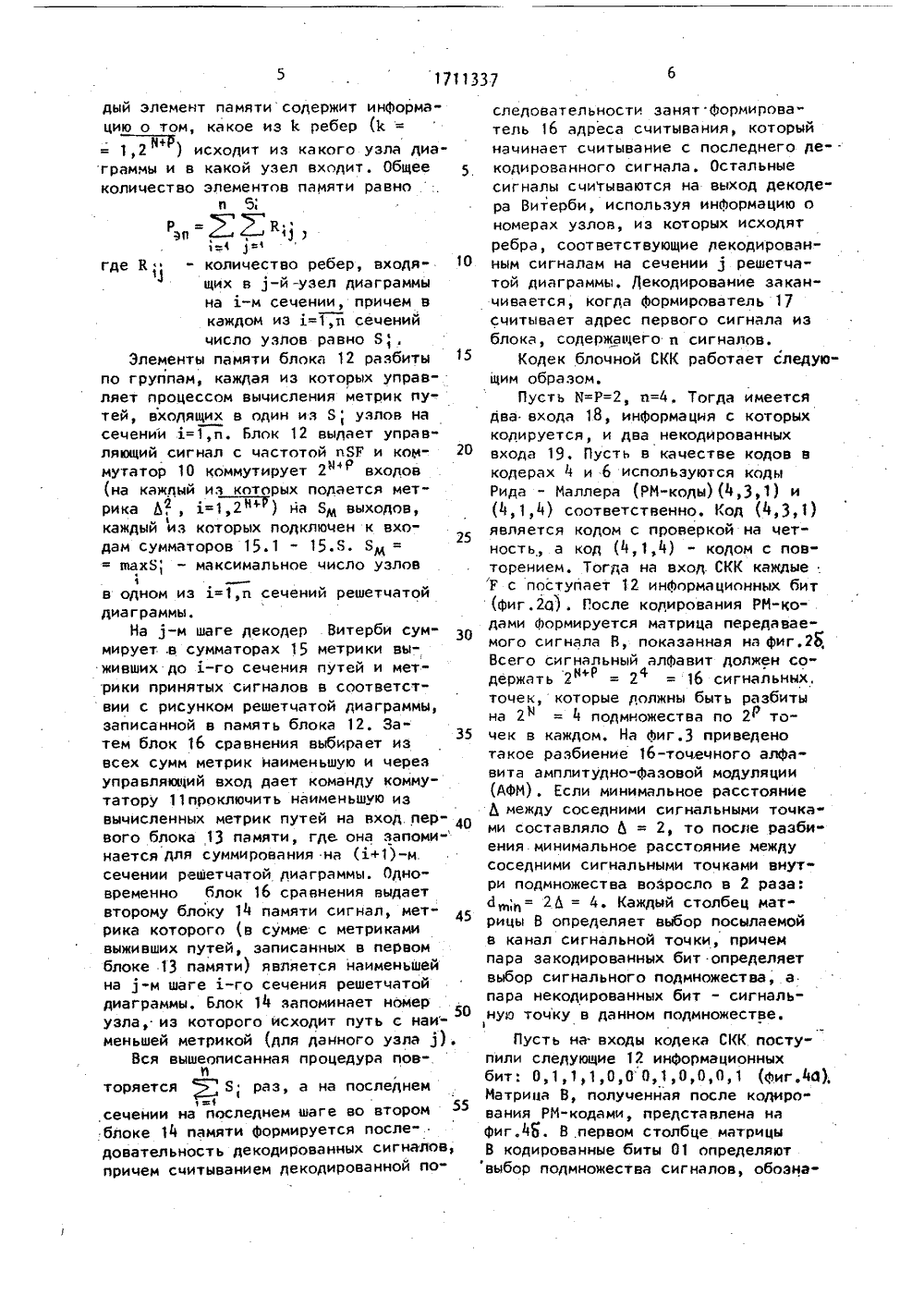

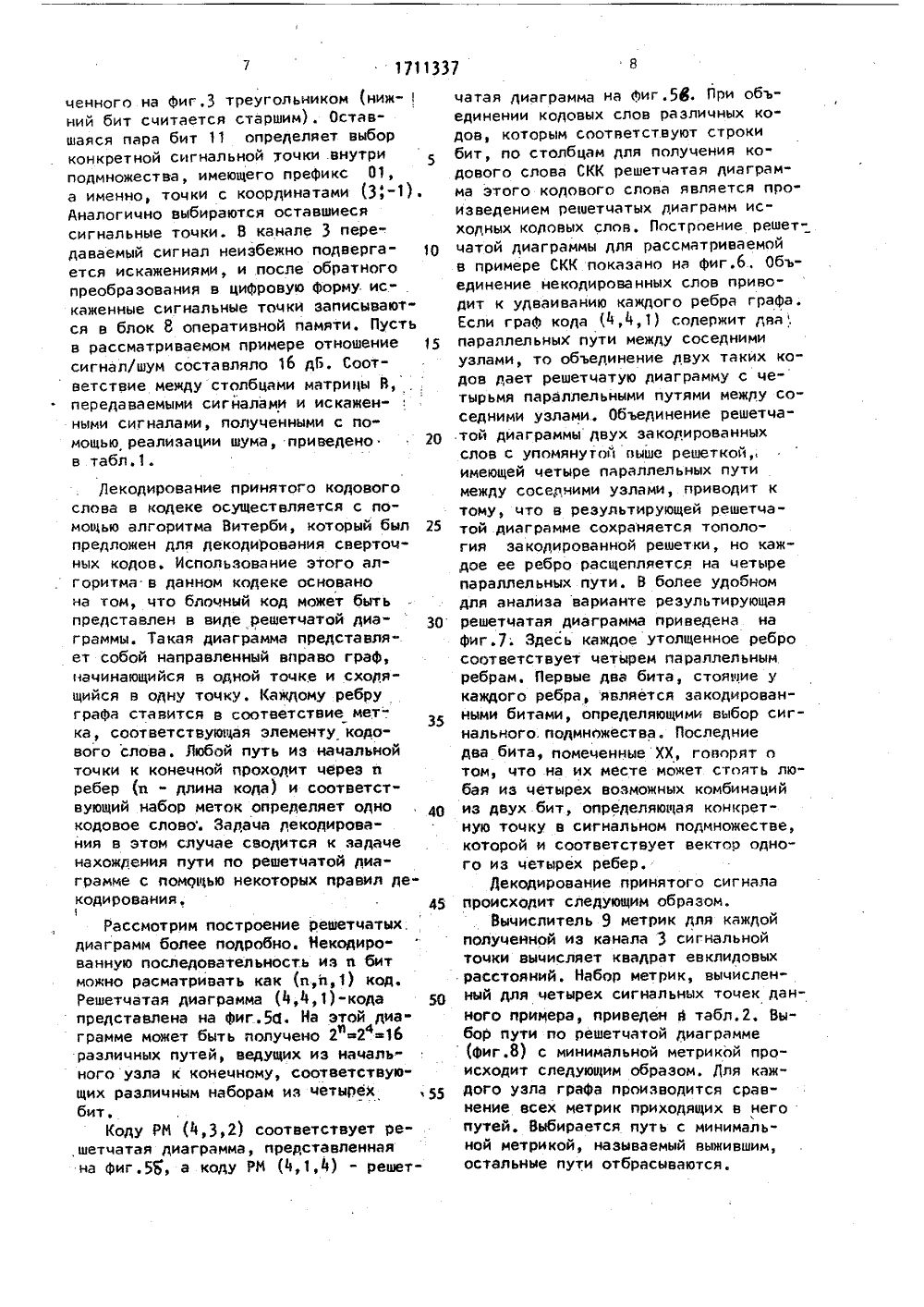

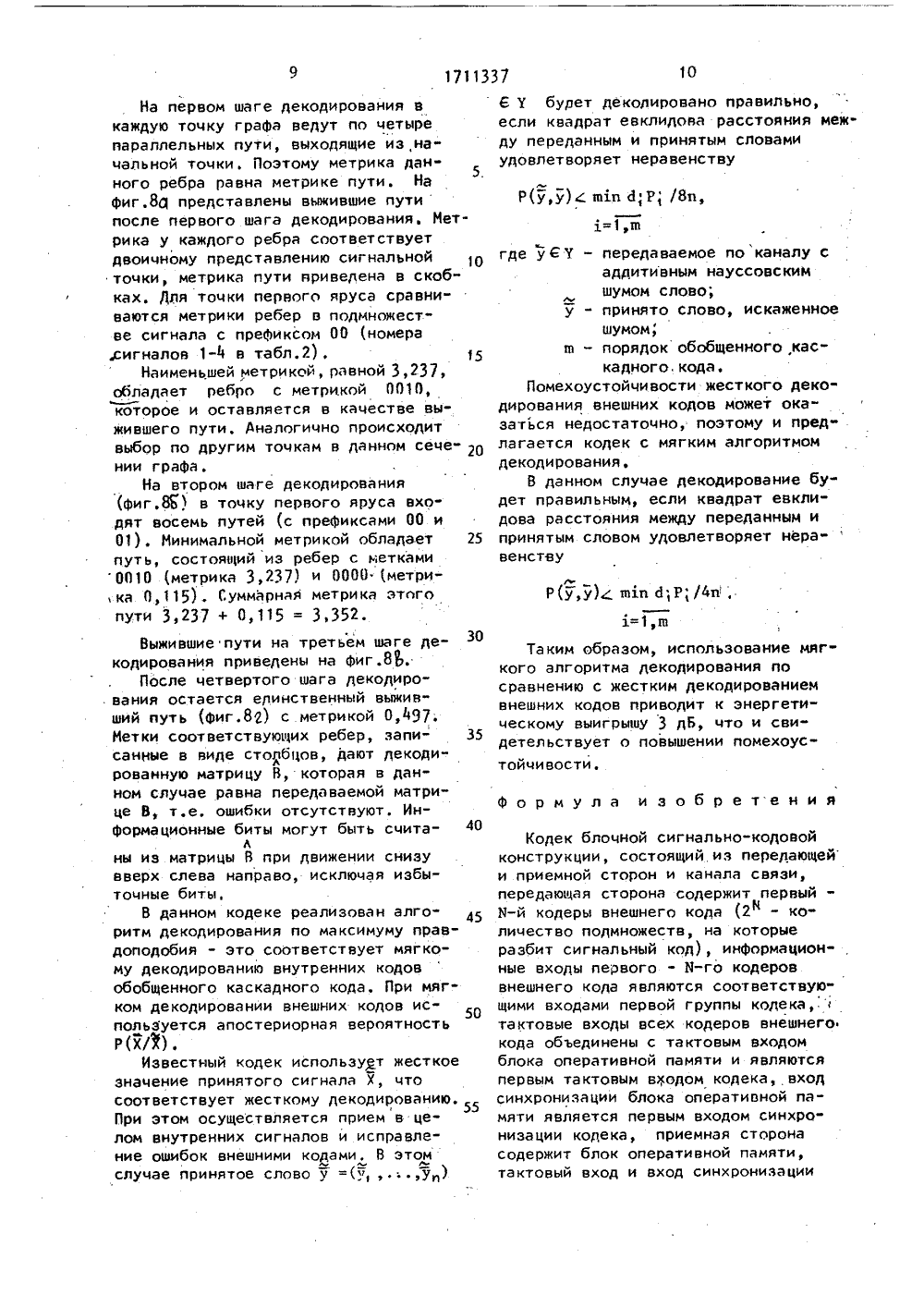

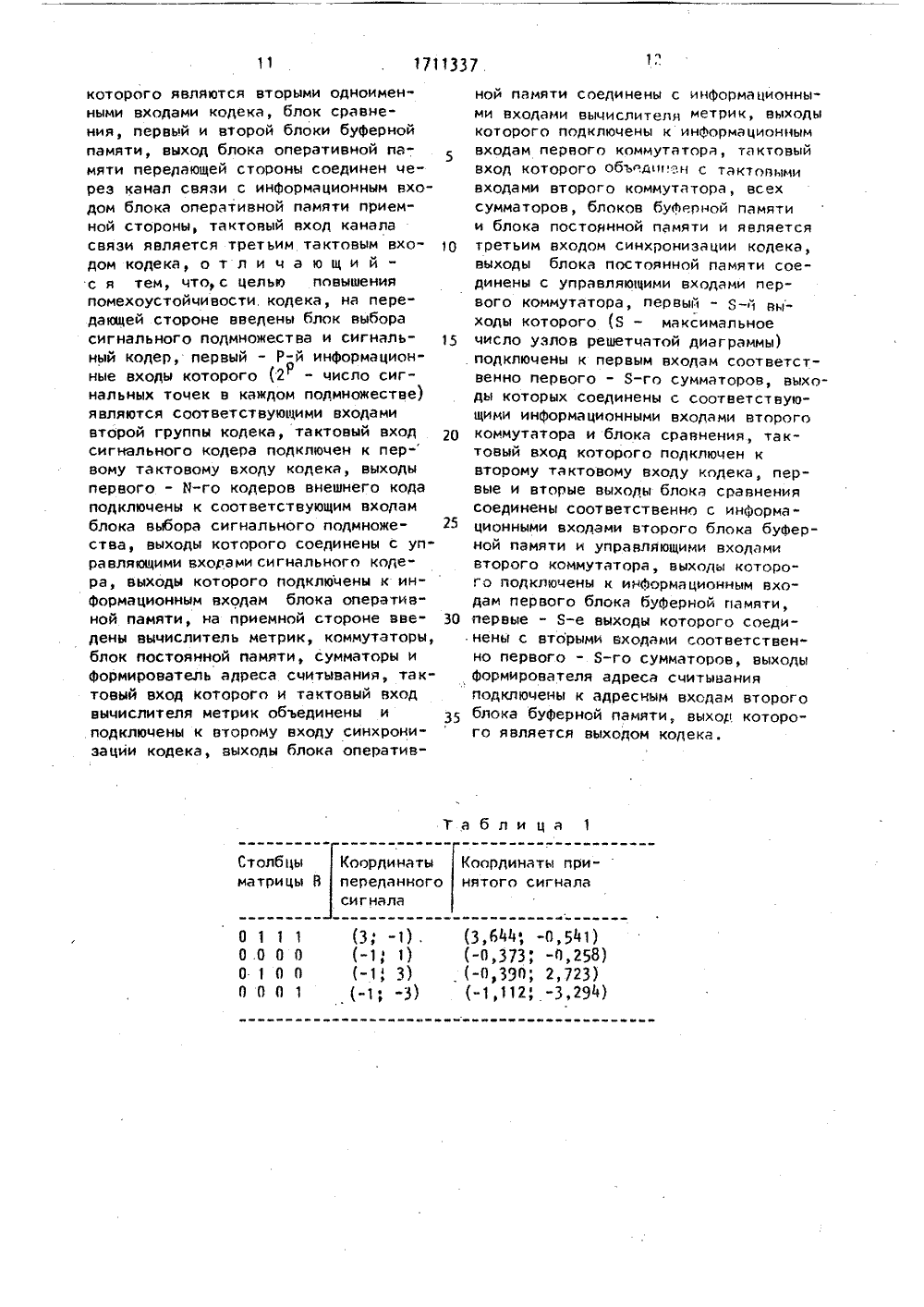

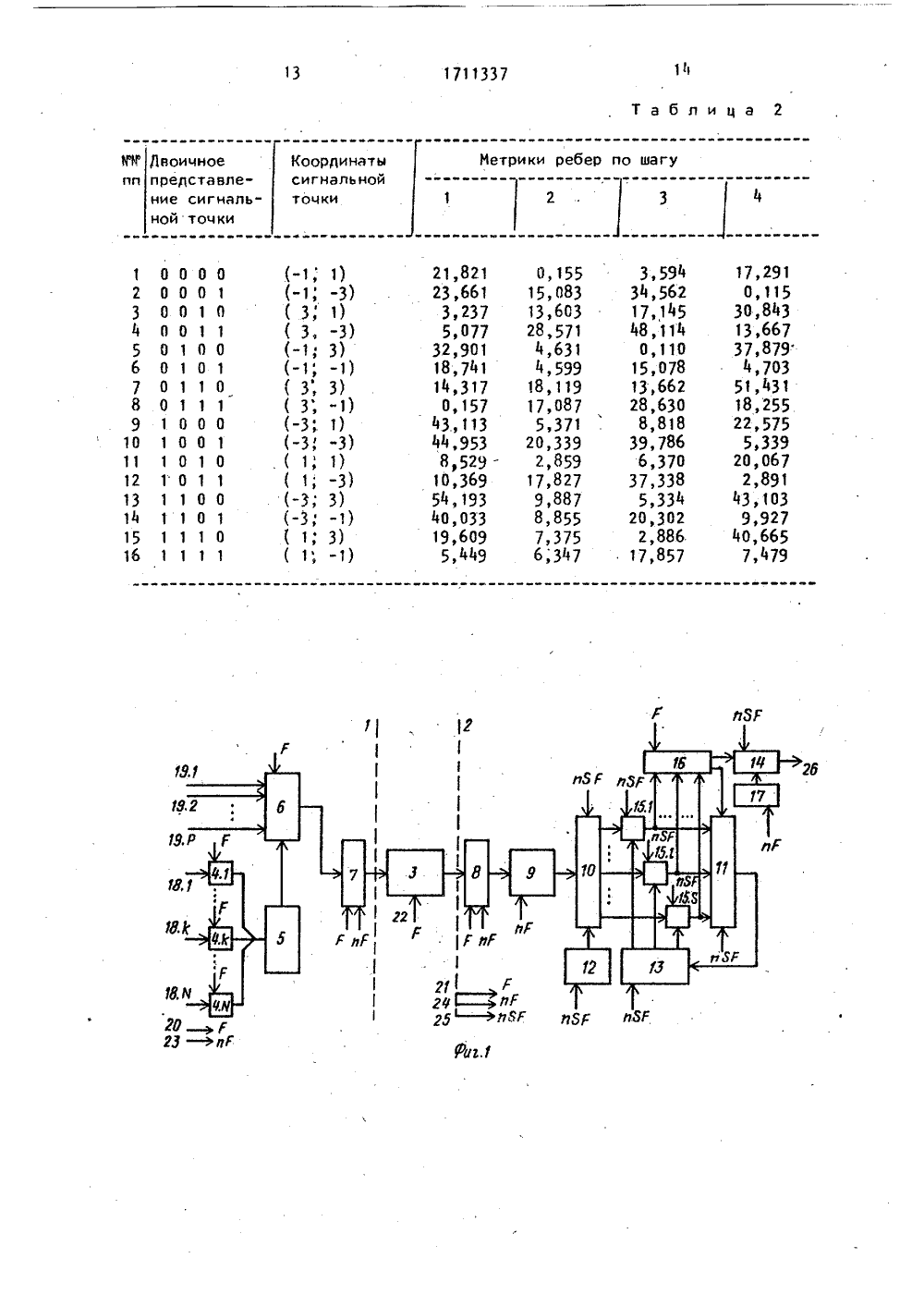

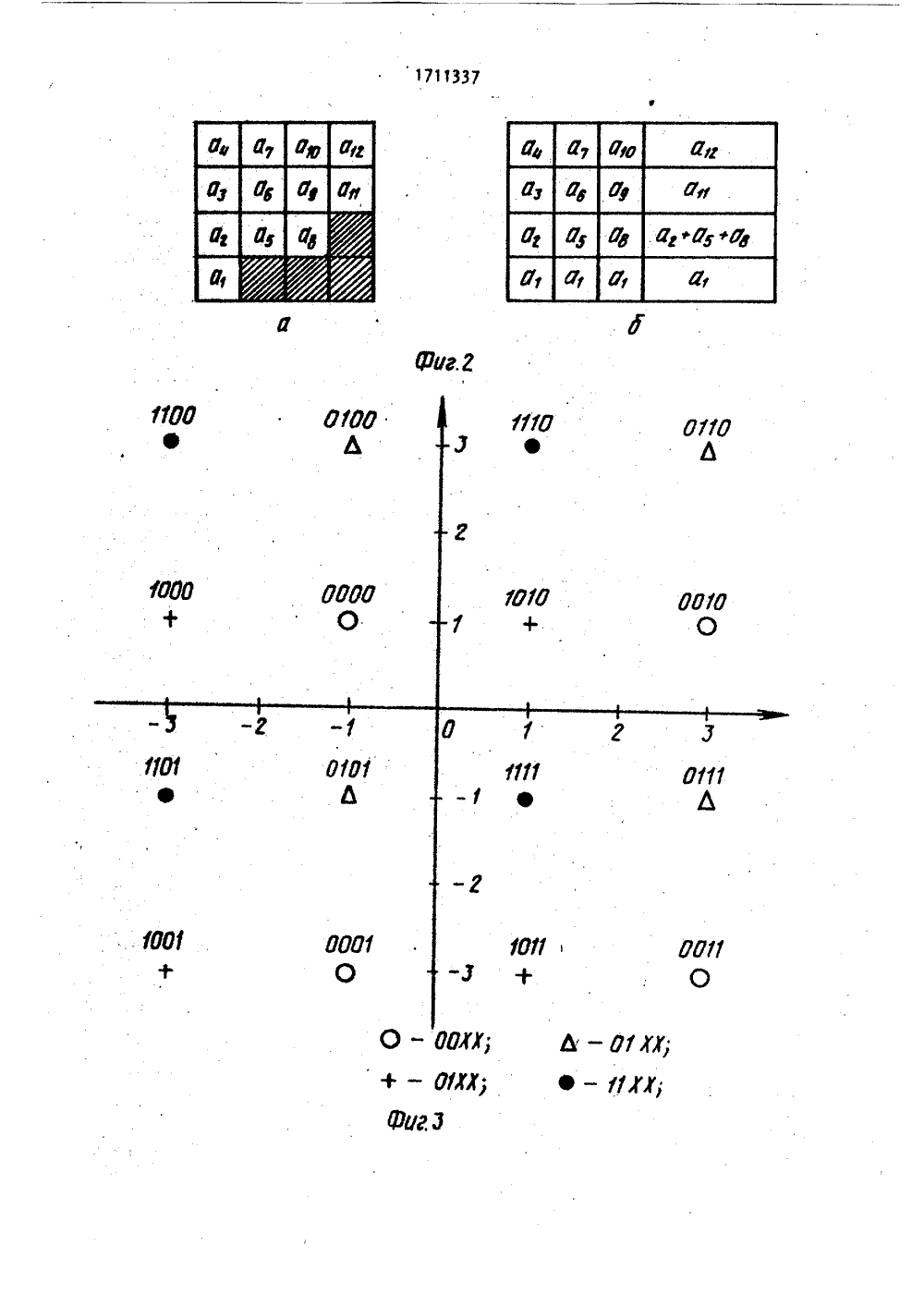

.ЯО.1711337, А 1 СОЮЗ СОВЕТСНИХшинареетипРЕСПУБЛИК Ой)5 " 03.М 13/00 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЩРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССРй 1629992, кл. Н 03 М 13/12, 1987,Авторское свидетельство СССРй 1408532, кл, Н 03 М 13/00, 1986Авторское свидетельство СССРЮф 1401613, кл. Н 03 М 13/00, 1986.(57) Изобретение относится к техни-ке связи и вычислительной техникеЕго использование в аппаратуре пеУИзобретение относится к технике .связи и вычислительной технике и может быть использовано в аппаратурепередачи дискретных сообщений.Цель изобретения - повышение помехоустойчивости кодека,На фиг. 1 приведена блок-схемакодека; на фиг, 2 - матрицы формируе"мых сигналов, общий вид, на фиг, 3 разбиение 16-точечного алфавита дляамплитудно-фазовой модуляции; нафиг. 4 - матрицы на фиг.2 для кон-кретного примера, на фиг,5-8 -;решетчатые диаграммы, поясняющие процесс декодирования,Кодек состоит из перелающей и приемной сторон 1 и 2 и канала 3 связи,Передающая сторонавключает кодеры 2релачи дискретных сообщений позволяет повысить помехоустойчивость кодека. Кодек состоит из передающей .стороны, содержащей кодеры внешнего кода и блок оперативной памяти, канала связи и приемной стороны, содержащей блок оперативной памяти, блоки буФерной памяти и блок сравнения. Благодаря введению на передающей стороне блока выбора сигнального подмножества и сигнального кодера, а на приемной стороне - вычислителя метрик, коммутаторов, блока постоянной памяти, сумматоров и формировате" ля адреса считывания, в кодеке реа" лизуется алгоритммягкого декодиро" вания на основе использования решетчатых диаграмм аналогично алгоритму Витерби. 8 ил., 2 табл. 4 внешнего кода, блок 5 выбора сиг- , фф ф нального подмножества, сигнальный колер 6 и блок 7 оперативной памяти. вава Приемная сторона 2 содержит блок 8 вил оперативной памяти, вычислитель 9 ф,) метрик, первый и второй коммутатор (фф 10 и 11, блок 12 постоянной памяти, первый и второй блоки 13 и 14 буферной. памяти, сумматоры 15, блок 16 сравнения и формирователь 17 адреса считывания, На фиг,1 обозначеныр первая и вторая группы 18 и 19 информационных входов, первый - тре" тий тактовые входы 20 - 22, Первый третий входы 23 - 25 синхронизации. и выход 26 кодека.Кодеры 4 и 6 и блок 5 передающей стороны можно выполнить на ПЗУ. Вычислитель 9 метрик также можно реализовать на ПЗУ. Формирователь 17 адреса считывания представляет, например, регистр сдвига.5Кодек блочной сигнально-кодовой конструкции (СКК) работает следующим образом.На входы 18 кодеров ч,1 - М.И по" ступает И блоков информации по 1, бит. 10 После кодирования -м кодом (=1,Я) на выходе каждого кодера 11. появляется блок информации а длиной и бит (а, = ( а а,а 11 а,Я СР(2). Совокупность всех блоков на выходах кодеров 1 образует матрицу т а, 20 т ак=Да, Ц 1=1,0, 1=1,и 25 йСтолбцы этой матрицы последовательно подаются в блок 5 выбора сиг 30 нального подмножества, в отором про" исходит выбор одного из 2 сигнальных подмножеств, на которые разбит полный сигнальный алфавит. Полное сигнальное созвездие разбивается на 35 сигнальные подмножества таким образом, чтобы максимизировать минимальное евклидово расстояние между соседними сигнальными точквми внутри подмножества.На входы 19 поступают Р блоков инФормации по и бит. Зти блоки некодированной информации образуют матрицуВ Ь," , 1. = 1,Р, 3 1 юи 45 Столбцы этой матрицы последова" тельно подаются в сигральный кодРер 6, где происходит выбор одной из 2 сигнальных точек выбранного подмножества, Таким образом, поРлный сигнальный 50 алфавит содержит 2" сигнальных то- чек, которые разбиты на 2 сигнальйных подмножеств до 2 Р точек в каждом подножестве. На выходе сигнального кодера 6 Формируется иоследова 55 тельностьиз и сигнальных точек, ко торая записывается .в блок 7 передающей стороны 1 и с частотой иР посту. пает в канал 3 связи, Под действием помех в канале 3 связи сигналыискажаются и в искаженном виде после обратного преобразования в цифровые Форму записываются в блок 8приемной стороны 2,Блок 8 преобразует последовательность из и сигнальных точек, поступающих на его вход с частотой иГ, впоследовательность из и сигнальныхточек, считываемых с частотой Г. Свыходов блока 8 на входы вычислителя 9 метрик последовательность изи принятых сигнальных точек поступает в виде 2 и действительных чисел,где каждая пара действительных чисел соответствует координатам каждой из и сигнальных точек на комплексной плоскости 7,.В состав вычислителя ) метрик входит датчик координат 2 " сигнальй+ных точек, принадлежащих полному сигнальному алФавиту. Вычислитель 9метрик вычисляет квадрат расстоянияот каждой из сигнальных точек допринятой с координатами М и Хсигнальной точки, повторяя эту процедуру для каждого из и принятыхсигналов.Квадрат расстояния вычисляется последующему правилу: Ье= Я-и, ) + (ц-Ж),1=1,и, 1 с=1,21 Р)гдеиь - пара действительныхчисел, соответствующих координатам 1-йсигнальной точки накомплексной плоскости, 1 с=1,2"фДля каждого из и полученных сигналов на выходе вычислителя 9 метрик имеется набор из 2" квадратов расйстояний Ь В, называемых метриками сигнала К . Зтот набор метрик поступает на группу блоков 10 - 1 б, реализующих алгоритм декодирования принятой последовательности.по алгоритму Витерби.Коммутатором 10 управляет блок 12 посредством записанной е нем инфор,мации, Процесс управления коммутатором 10 следующий.В блоке 12 записана решетчатая диаграмма декодера Витерби. Здесь каждый элемент памятисодержит информа" цию о тои, какое из к ребер Ис 1,2 ) исходит из какого узла Лиа. граммы и в какой узел входит. Общее количество элементов памяти равноП ;уз р,:;5,р,),1) вы где К - количество ребер, входя" О Ц щих в 1-й -узел диаграммы на -м сечении, причем в каждом из 1=1,п сечений число узлов равно 8,. Элементы памяти блока 12 разбиты 5 по группам, каждая из которых управляет процессом вычисления метрик путей, входящих в один из 3, узлов на сечении =1,п, Блок 12 выдает управ" ляющий сигнал с частотой пЗР и ком мутатор 10 коммутирует 2"Р входов (на кажлый из которых подается метРика ое, з 1,2 асу) иа би выходов, каждый из которых подключен к входам сумматоров 15.1 - 15.ЯБм =25 = п)ахи,- максимальное число узлов в одном из х=1,п сечений решетчатой диаграммы.На 1-м шаге декодер Витерби суммирует .в сумматорах 15 метрики выживших до ь-го сечения путей и метрики принятых сигналов в соответствии с рисунком решетчатой диаграммы, записанной в память блока 12. Затем блок 16 сравнения выбирает из всех сумм метрик наименьшую и через управляющий вход дает команду коммутатору 11 проключить наименьшую извычисленных метрик путей на вход пер вого блока 13 памяти, где она запоми- нается для суммирования на (д+)-м. сечении решетчатой диаграммы. Одновременно блок 16 сравнения выдает второму блоку 14 памяти сигнал, мет" 45 рика которого (в сумме с метриками выживших путей, записанных в первом блоке 13 памяти) является наименьшей на -м шаге -го сечения решетчатой диаграммы. Блок 14 запоминает номер узла, из которого исходит путь с наи- меньшей метрикой (для данного узла 1). Вся вышеописанная процедура пов-.П торяется ъЯ раз, а на последнем 155 сечении на последнем шаге во втором блоке 14 памяти Формируется после" довательность декодированных сигналов, причем считыванием декодированной по" следовательности занят Формирова" тель 16 адреса считывания, который начинает считывание с последнего де- . кодированного сигнала, Остальные сигналы счиТываются на выход декоде" ра Витерби, используя информацию о номерах узлов, из которых исходят ребра, соответствующие декодированным сигналам на сечениирешетчатой диаграммы, Декодирование заканчивается, когда Формирователь 17 считывает адрес первого сигнала из блока, содержащего и сигналов.Кодек блочной СКК работает следую" щим образом.Пусть М=Р=2, п=4, Тогда имеется два входа 18, информация с которых кодируется, и два некодированных входа 19, Пусть в качестве кодов в кодерах 4 и б используются коды Рида " Маллера (РМ"коды)(",3,1) и (4,1,4) соответственно. Код (4,3,1) является кодом с проверкой на четность, а код (4 р 1 р 4) - кодом с пов торением, Тогда на вход. СКК каждые Р с поступает 12 информационных бит (фиг.20). После кодирования РМ-кодами Формируется матрица передаваемого сигнала В, показанная на фиг.2 о, Всего сигнальный алфавит должен со" держать 2" = 2 = 16 сигнальных, точек, которые должны быть разбиты на 2" = 4 подмножества по 2 Р точек в каждом. На Фиг.3 приведено такое разбиение 16-точечного алфавита амплитудно-Фазовой модуляции (АФМ), Если минимальное расстояние Д между соседними сигнальными точками составляло Д = 2, то после разбиения. минимальное расстояние между соседними сигнальными точками внутри подмножества возросло в 2 раза: йПсз 26 = 4. КаждЫй СтОЛбЕц Мат" рицы В определяет выбор посылаемой в канал сигнальной точки, причем пара закодированных бит определяет выбор сигнального подмножества,.а пара некодированных бит - сигнальную точку в данном подмножестве. )Пусть на- входы кодека СКК. поступили следующие 12 информационных бит: 0,1, 1,0,00,1,0,0,0,1 (Фиг.М), Матрица В, полученная после кодирования РМ-кодами, представлена на фиг.4. В .первом столбце матрицы В кодированные биты 01 определяют выбор подмножества сигналов, обознаценного на Фиг,3 треугольником (ниж-ний бит считается старшим). Оставшаяся пара бит 11 определяет выборконкретной сигнальной уочки .внутриподмножества, имеющего префикс 01,а именно, точки с координатами (3-1)Аналогично выбираются оставшиесясигнальные точки. В канале 3 передаваемый сигнал неизбежно подвергается искажениями, и .после обратногопреобразования в цифровую форму ис.- каженные сигнальные точки записываются в блок 8 оперативной памяти. Пустьв рассматриваемом примере отношениесигнал/шум составляло 16 дБ, Соот ветствие между столбцами матрицы В,передаваемыми сигйалами и искаженными сигналами, полученными с помощью реализации шума, приведенов табл.1. Декодирование принятого кодовогослова в кодеке осуществляется с помощью алгоритма Витерби, который былпредложен для декодирования сверточных кодов. Использование этого алгоритма в данном кодеке основанона том, что блочный код может бытьпредставлен в виде решетчатой диаграммы. Такая диаграмма представляет собой направленный вправо граф,начинающийся в одной точке и сходящийся в одну точку. Каждому ребруграфа ставится в соответствие мет-,ка, соответствующая элементу кодового слова. Любой путь из начальнойточки к конечной проходит через пребер (и - длина кода) и соответствующий набор меток определяет однокодовое слово. Задача декодирования в этом случае сводится к задаченахождения пути по решетчатой диаграмме с помощью некоторых правил декодирования,Рассмотрим построение решетчатых.диаграмм более подробно. Некодиро"ванную последовательность из и битможно расматривать как (п,п, 1) код.Решетчатая диаграмма (4,4,1)-кодапредставлена на Фиг 56. На этой диаграмме может быть получено 2" 2 16различных путей, ведущих из началь-"ного узла к конечному, соответствующих различным наборам из четырехбит,Коду РИ (4,3,2) соответствует ре,шетчатая диаграмма, представленнаяна Фиг.5, а коду РИ (4,1,4) " решет 5 1 О 15 20 25 30 35 40 45 50 55 чатая диаграмма на Фиг,58. При объединении кодовых слов различных кодов, которым соответствуют строкибит, по столбцам для получения кодового слова СКК решетчатая диаграмма этого кодового слова является произведением решетчатых диаграмм исходных коловых слов. Построение решетчатой диаграммы для рассматриваемойв примере СКК показано на фиг.б, Объединение некодированных слов приводит к удваиванию каждого ребра графа.Если граф кода (4 4,1) содержит дяа,параллельных пути между соседнимиузлами, то объединение двух таких кодов дает решетчатую диаграмму с четырьмя параллельными путями между соседними узлами. Объединение решетчатой диаграммы двух закодированныхслов с упомянутон выше решеткойимеющей четыре параллельных путимежду соседними узлами, приводит ктому, что в результирующей решетчатой диаграмме сохраняется топология закодированной решетки, но каждое ее ребро расщепляется на четырепараллельных пути. В более удобномдля анализа варианте результирующаярешетчатая диаграмма приведена наФиг.7. Здесь каждое утолщенное ребросоответствует четырем параллельнымребрам. Первые два бита, стоящие укаждого ребра, является закодированными битами, определяющими выбор сигнального. подмножества. Последниедва бита, помеченные ХХ, говорят отом, что на их месте может стоять любая из четырех возможных комбинацийиз двух бит, определяющая конкретную точку в сигнальном подмножестве,которой и соответствует вектор одного из четырех ребер,Декодирование принятого сигналапроисходит следующим образом.Вычислитель 9 метрик для каждойполученной из канала 3 сигнальнойточки вычисляет квадрат евклидовыхрасстояний. Набор метрик, вычисленный для четырех сигнальных точек данного примера, приведен в табл.2, Выбор пути по решетчатой диаграмме(фиг.8) с минимальной метрикой происходит следующим образом. Для каждого узла графа производится сравнение всех метрик приходящих в негопутей. Выбирается путь с минимальной метрикой, называемый выжившим,остальные пути отбрасываются.(3; -1) (-1, 1) (-1, 3) (-1; -3) 01110,0 О О 0100 0001 которого являются вторыми одноименными входами кодека, блок сравнения, первый и второй блоки буфернойпамяти, выход блока оперативной памяти передающей стороны соединен через канал связи с информационным входом блока оперативной памяти приемной стороны, тактовый вход каналасвязи является третьим тактовым входом кодека, о т л и ч а ю щ и йс я тем, что, с целью повышенияпомехоустойчивости. кодека, на передающей стороне введены блок выборасигнального подмножества и сигнальный кодер, первый - Р-й информационные входы которого (2 - число сигнальных точек в каждом подмножестве)являются соответствующими входамивторой группы кодека, тактовый входсигнального кодера подключен к пер-вому тактовому входу кодека, выходыпервого - И-го кодеров внешнего кодаподключены к соответствующим входамблока выбора сигнального подмножества, выходы которого соединены с управляющими входами сигнального кодера, выходы которого подключены к информационным входам блока оперативной памяти, на приемной стороне введены вычислитель метрик, коммутаторы,блок постоянной памяти, сумматоры иФормирователь адреса считывания, тактовый вход которого и тактовый входвычислителя метрик объединены иподключены к второму входу синхронизации кодека, выходы блока оперативСтолбцы Координатыматрицы В переданногосигнала ной памяти соединены с информационными входами вычислителя метрик, выходыкоторого подключены к информационнымвходам первого коммутатора, тактовыйвход которого объ"дизн с тактовымивходами второго коммутатора, всехсумматоров, блоков буферной памятии блока постоянной памяти и является 10 третьим входом синхронизации кодека,выходы блока постоянной памяти соединены с управляющими входами первого коммутатора, первый - я-й выходы которого (Я - максимальное 15 число узлов решетчатой диаграммы). подключены к первым входам соответственно первого - Я-го сумматоров, выходы которых соединены с соответствующими информационными входами второго 20 коммутатора и блока сравнения, тактовый вход которого подключен квторому тактовому входу кодека, первые и вторые выходы блока сравнениясоединены соответственно с информационными входами второго блока буферной памяти и управляющими входамивторого коммутатора, выходы которого подключены к информационным входам первого блока буферной памяти, 30 первые - Я-е выходы которого соединены с вторыми входами соответственно первого - Я-го сумматоров, выходыформирователя адреса считыванияподключены к адресным входам второгоблока буферной памяти, выход которого является выходом кодека.14 1711337 Т а б л и ц а 2 Метрики ребер пп ноито

СмотретьЗаявка

4666115, 24.03.1989

МОСКОВСКИЙ ИНСТИТУТ СВЯЗИ

ЖВАНИЯ АЛЕКСАНДР ГРИГОРЬЕВИЧ, ЗОТКИН ВИКТОР БОРИСОВИЧ, ЗЯБЛОВ ВИКТОР ВАСИЛЬЕВИЧ, КОРОБКОВ ДМИТРИЙ ЛЬВОВИЧ, ПОРТНОЙ СЕРГЕЙ ЛЬВОВИЧ, ШАВГУЛИДЗЕ СЕРГЕЙ АНЗОРОВИЧ

МПК / Метки

МПК: H03M 13/00

Метки: блочной, кодек, конструкции, сигнально-кодовой

Опубликовано: 07.02.1992

Код ссылки

<a href="https://patents.su/12-1711337-kodek-blochnojj-signalno-kodovojj-konstrukcii.html" target="_blank" rel="follow" title="База патентов СССР">Кодек блочной сигнально-кодовой конструкции</a>

Предыдущий патент: Устройство для последовательного контроля кода

Следующий патент: Устройство для кодирования линейных полиномиальных кодов

Случайный патент: Способ приготовления минерального вяжущего