Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1539776

Авторы: Вейц, Дятчина, Жуков, Криворучко, Левертов, Малюгин, Соколов, Сперанская, Шевцов

Текст

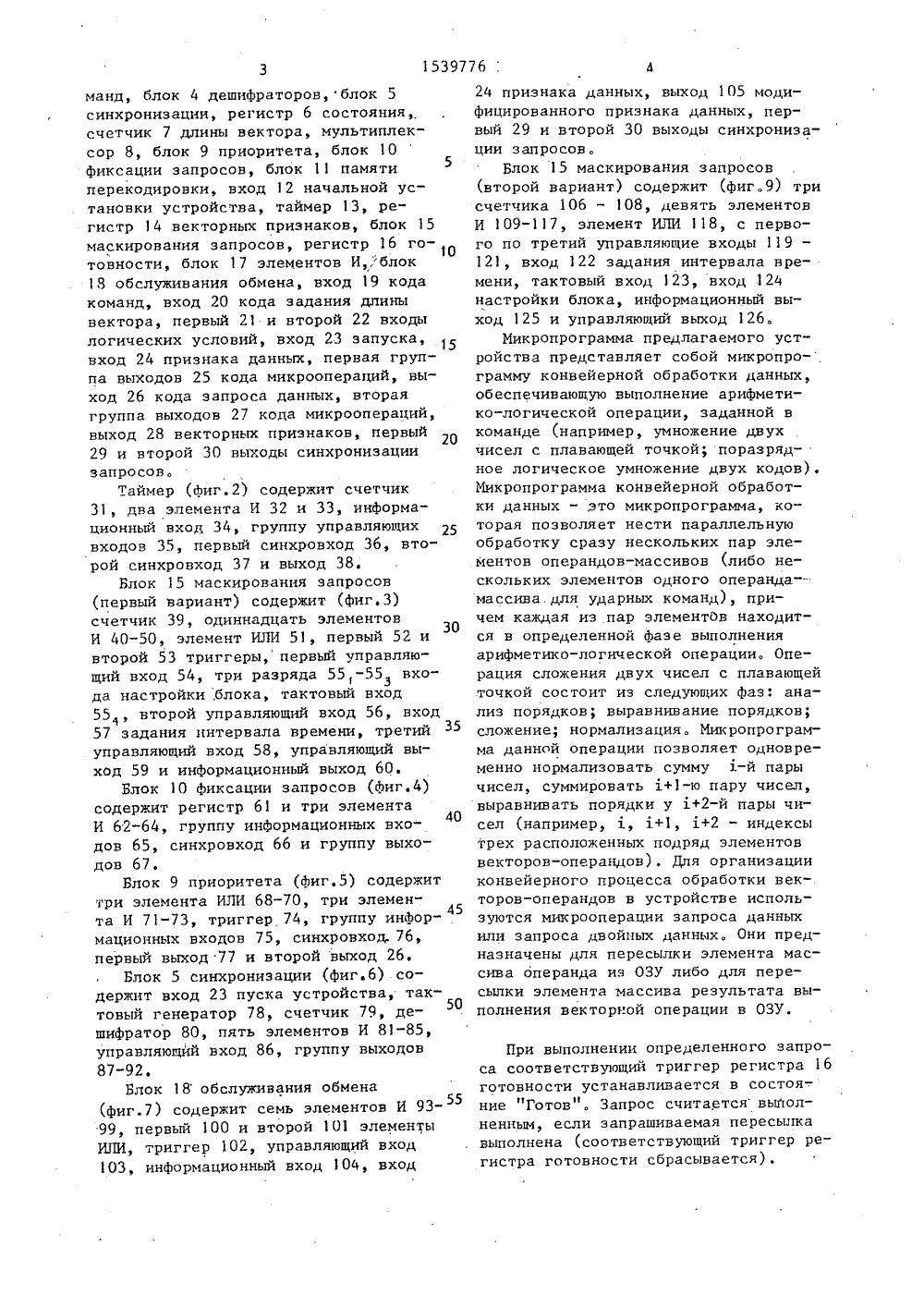

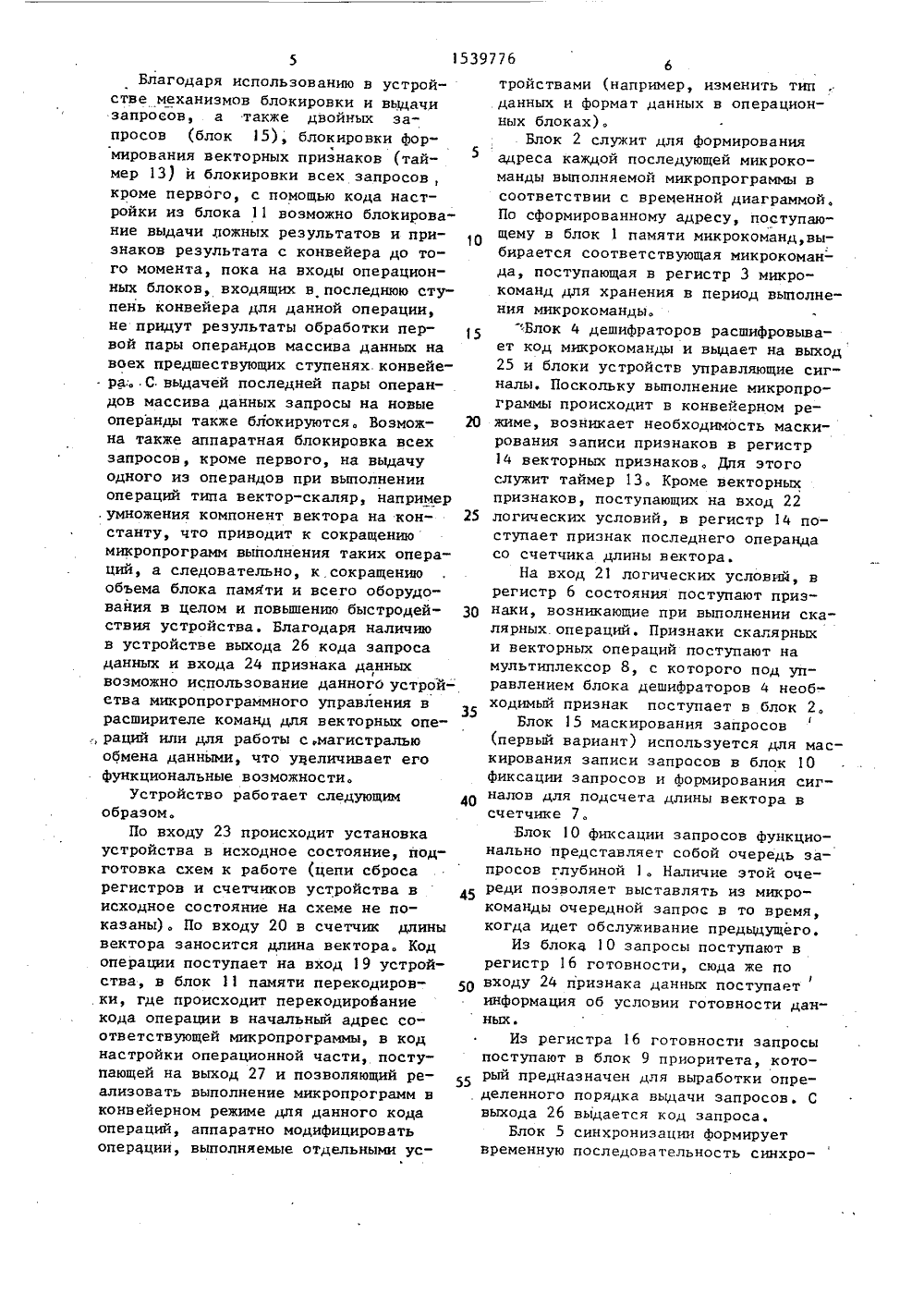

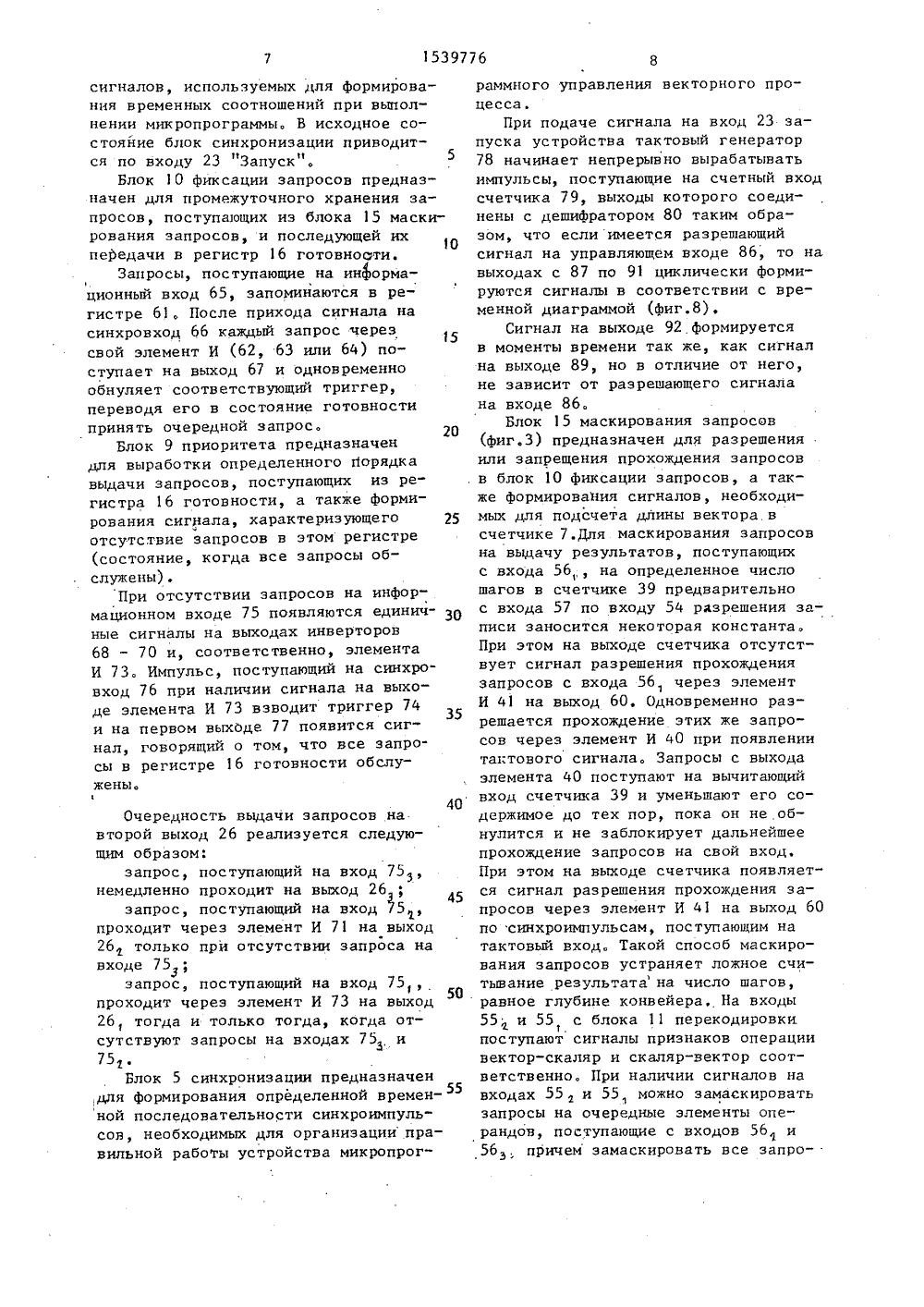

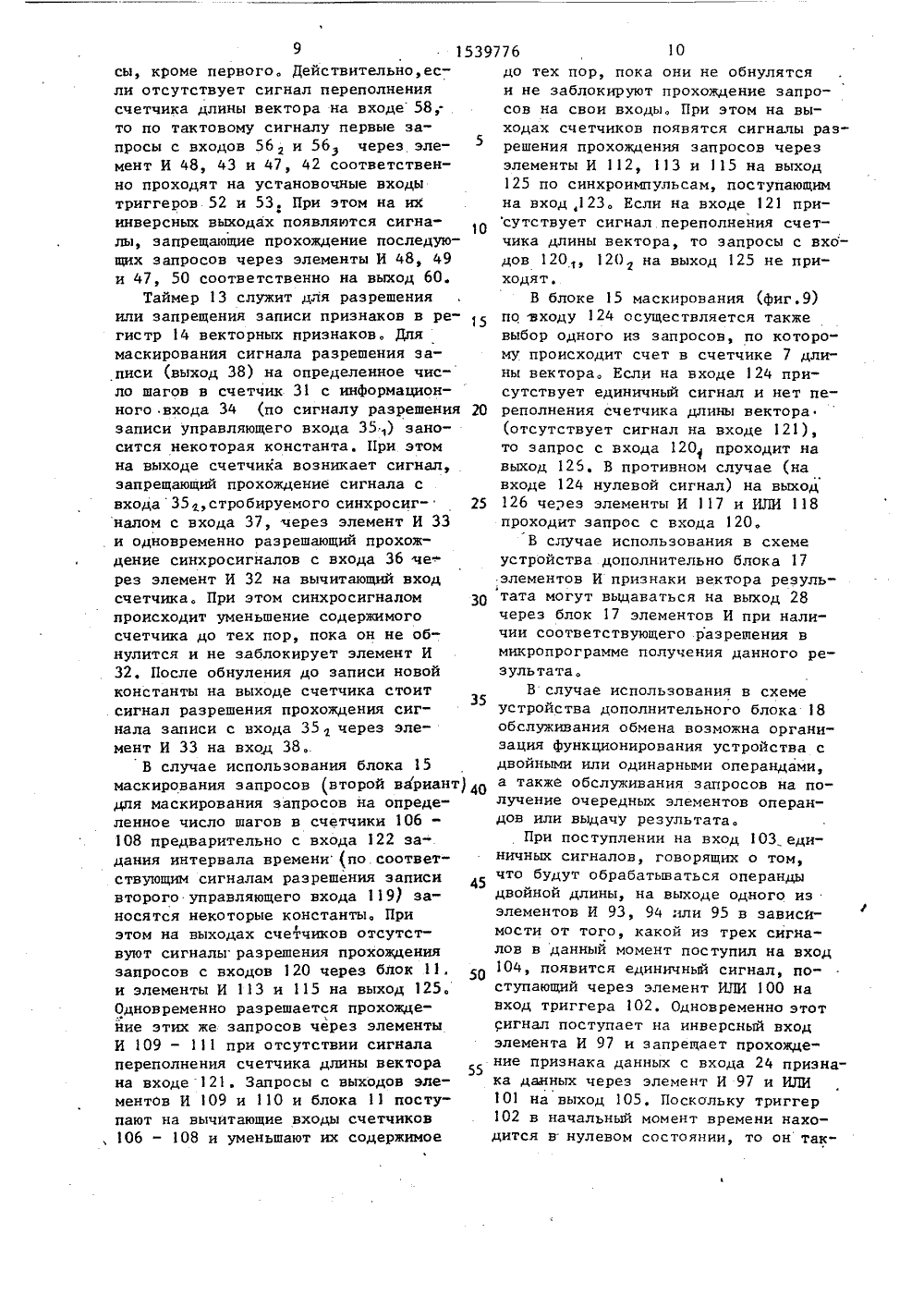

(51)5 С 0 ИСАНИЕ ИЗОБРЕТЕНИ 124-24; 4196703/24-24; СССР 1983. истем на мых БИС/ .ф Радио и ожет быть исустройства уп роцессора или я векторных тения - расшиится к вычислижет быть исполь-.тройства управлеетение отно технике и м качестве у орного проц Изобрьной овано ия ве ссора или расши-.кторных операций.- расширение об- .счет обеспечеля команд для ль зобретения менения за сти возможнос управлени использования ег екторным процесс ботки данных. дставлена стрна Фиг. 2 3 - схема бл онвейерНа фи хема ус аймера; ои обра 1 пре ройствао (Фиг,1) соде рокгманд, блок са, регистр 3 м жит блок2 Формиикрокоуктурная схемаока масрован Фиг ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Институт проблем управления(56) Авторское свидетельство11 1003086, кл. С 06 Р 9/22,Проектирование цифровых скомплектах микропрограммируеПод ред. В,Г. Колесникова. Ми связь, 984, с. 130.(57) Изобретение относится к вычлительной:технике и мпользовано в качестверавления векторного ирасширителя команд длопераций, Цель изобре,1539776 А 1 ение области применения за счет обеспечения возможности использования его для управления векторным процессором конвейерной обработки данных. Устройство содержит блок памяти микрокоманд, блок формирования адреса, регистр микрокоманд, блок дешифраторов, блок синхронизации, регистр состояния, счетчик длины вектора, мультиплексор, блок приоритета, блок фиксации запросов, блок памяти перекодировки, таймер, регистр векторных признаков, блок маскирования запросов, регистр готовности, блок элементов И, блок обслуживания обмена, Благодаря блоку обслуживания обмена аф обеспечивается управление операндами и результатами как одинарной, так и двойной длины, а также обеспечивается возможность работы устройства с маги- С , стралью обмена данными для многопроцессорных устройств и уменьшение раз-. Б рядности кода признаков управлЕния запросами. 4 з.п. Ф-лы, 9 ил. . (д кирования запросов по и. 2 Форму- фф 4 лы); на Фиг, 4 - схема блока Фикса- О ции запросов; на фиг. 5 - схема блока приоритета; на фиг, 6 - схема блока синхронизации; на ,Фиг.7 - схема блока обслуживания обмена; на фиг,8 - временная диаграмма работы блока . Ъф синхронизации; на Фиг, 9 - схема блока маскирования запросов (по п. 3формулы).Устройств Р1 памяти микректор С.йекм Тираж 564 Подписноесударственного комитета по изобретениям и открытиям 113035, Москва, Ж, Раушская наб., д, 4/5 каз 2 КНТ ССС НИИПИ Про одственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 10манд, блок 4 дешифраторов, блок 5синхронизации, регистр 6 состояния,счетчик 7 длины вектора, мультиплексор 8, блок 9 приоритета, блок 10фиксации запросов, блок 11 памятиперекодировки, вход 12 начальной установки устройства, таймер 13, ре"гистр 14 .векторных признаков, блок 15маскирования запросов, регистр 16 готовности, блок 17 элементов И"блок18 обслуживания обмена, вход 19 кодакоманд, вход 20 кода задания длинывектора, первый 21 и второй 22 входылогических условий, вход 23 запуска,вход 24 признака данных, первая группа выходов 25 кода микроопераций, выход 26 кода запроса данных, втораягруппа выходов 27 кода микроопераций,выход 28 векторных признаков, первый29 и второй 30 выходы синхронизациизапросов.Таймер (фиг.2) содержит счетчик31, два элемента И 32 и 33, информационный вход 34, группу управляющихвходов 35, первый синхровход 36, второй синхровход 37 и выход 38,Блок 15 маскирования запросов(первый вариант) содержи (фиг.3)счетчик 39, одиннадцать элементовИ 40-50, элемент ИЛИ 51, первый 52 ивторой 53 триггеры, первый управляющий вход 54, три разряда 55,-55 входа настройки, блока, тактовый вход55, второй управляющий вход 56, вход57 задания интервала времени, третийуправляющий вход 58, управляющий выход 59 и информационный выход 60.Блок 10 Фиксации запросов (фиг.4)содержит регистр 61 и три элементаИ 62-64, группу информационных вхо 40дов 65, синхровход 66 и группу выходов 67.Блок 9 приоритета (фиг.5) содержит45три элемента ИЛИ 68-70, три элемента И 71-73, триггер 74, группу информационных входов 75, синхровход. 76,первый выход 77 и второй выход 26,Блок 5 синхронизации (фиг.б) содержит вход 23 пуска устройства, тактовый генератор 78, счетчик 79, де 50шифратор 80, пять элементов И 81-85,управляющий вход 86, группу выходов87-92.Блок 18 обслуживания обмена(фиг.7) содержит семь элементов И 935599, первый 100 и второй 101 элементыИЛИ, триггер 102, управляющий вход103, информационный вход 1 Ой, вход 24 признака данных, выход 105 модифицированного признака данных, первый 29 и второй 30 выходы синхронизации запросов.Блок 15 маскирования запросов (второй вариант) содержит (фиг.9) три счетчика 106 - 108, девять элементов И 1 09-117, элемент ИЛИ 118, с первого по третий управляющие входы 119 - 121, вход 122 задания интервала времени, тактовый вход 123, вход 12 ч настройки блока, информационный выход 125 и управляющий выход 126,Микропрограмма прецлагаемого устройства представляет собой микропро- грамму конвейерной обработки данных, обеспечивающую выполнение арифметико-логической операции, заданной в команде (например, умножение двух чисел с плавающей точкой; поразрядное логическое умножение двух кодов), Микропрограмма конвейерной обработки данных - это микропрограмма, которая позволяет нести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда массива,для ударных команд), причем каждая из пар элементов находится в определенной фазе выполнения арифметико-логической операции. Операция сложения двух чисел с плавающей .точкой состоит из следующих фаз: анализ порядков; выравнивание порядков; сложение; нормализация. Микропрограмма данной операции позволяет одновременно нормализовать сумму х-й пары чисел, суммировать х+1-ю пару чисел, выравнивать порядки у +2-й пары чисел (например, , 1+1, 1+2 - индексы трех расположенных подряд элементов векторов-операндов), Для организации конвейерного процесса обработки векторов-операндов в устройстве используются микрооперации запроса данных или запроса двойных данных. Они предназначены для пересылки элемента массива операнда из ОЗУ либо для пересылки элемента массива результата выполнения векторной операции в ОЗУ. При выполнении определенного запроса соответствующий триггер регистра 16 готовности устанавливается в состояние Готов. Запрос считается выполненным, если запрашиваемая пересылка выполнена (соответствующий триггер регистра готовности сбрасывается).1539 15 25 30 35 40 45 50 55 5Благодаря использованию в устройстве механизмов блокировки и выдачи запросов, а также двойных запросов (блок 15), блокировки формирования векторных признаков (таймер 13) и блокировки всех запросов, кроме первого, с помощью кода настройки из блока 11 возможно блокирование выдачи ложных результатов и признаков результата с конвейера до того момента, пока на входы операционных блоков, входящих в последнюю ступень конвейера для данной операции,не придут результаты обработки первой пары операндов массива данных навоех предшествующих ступенях конвейера:С. выдачей последней пары операндов массива данных запросы на новыеоперанды также блокируются. Возможна также аппаратная блокировка всехзапросов, кроме первого, на выдачуодного из операндов при выполненииопераций типа вектор-скаляр, например, умножения компонент вектора на константу, что приводит к сокращениюмикропрограмм выполнения таких операций, а следовательно, к,сокращениюобъема блока памяти и всего оборудования в целом и повышению быстродействия устройства. Благодаря наличиюв устройстве выхода 26 кода запросаданных и входа 24 признака данных возможно использование данного устройетва микропрограммного управления в расширителе команд для векторных опе, раций или для работы с,магистралью обмена данными, что увеличивает его функциональные возможности.Устройство работает следующим образом.По входу 23 происходит установка устройства в исходное состояние, подготовка схем к работе (цепи сброса регистров и счетчиков устройства в исходное состояние на схеме не показаны). По входу 20 в счетчик длины вектора заносится длина вектора. Код операции поступает на вход 19 устройства, в блок 11 памяти перекодиров. ки, где происходит перекодирование кода операции в начальный адрес со" ответствующей микропрограммы, в код настройки операционной части, поступающей на выход 27 и позволяющий реализовать выполнение микропрограмм в конвейерном режиме для данного кода операций, аппаратно модифицировать операции, выполняемые отдельными ус 776 6тройствами (например, изменить типданных и формат данных в операционных блоках).Блок 2 служит для формированияадреса каждой последующей микрокоманды выполняемой микропрограммы всоответствии с временной диаграммой,По сформированному адресу, поступающему в блок 1 памяти микрокоманд,выбирается соответствующая микрокоманда, поступающая в регистр 3 микрокоманд для хранения в период выполнения микрокоманды.Блок 4 дешифраторов расшифровывает код микрокоманды и выдает на выход25 и блоки устройств управляющие сигналы. Поскольку выполнение микропрограммы происходит в конвейерном ре жиме, возникает необходимость маскирования записи признаков в регистр14 векторных признаков. Для этогослужит таймер 13. Кроме векторныхпризнаков, поступающих на вход 22логических условий, в регистр 14 поступает признак последнего операндасо счетчика длины вектора.На вход 21 логических условий, врегистр 6 состояния поступают признаки, возникающие при выполнении скалярных операций. Признаки скалярныхи векторных операций поступают намультиплексор 8, с которого под управлением блока дешифраторов 4 необходимый признак поступает в блок 2,Блок 15 маскирования запросов(первый вариант) используется для маскирования записи запросов в блок 10фиксации запросов и формирования сигналов для подсчета длины вектора всчетчике 7.Блок 1 О фиксации запросов функционально представляет собой очередь запросов глубиной 1. Наличие этой очереди позволяет выставлять из микрокоманды очередной запрос в то время,когда идет обслуживание предыдущего,Из блока 10 запросы поступают врегистр 16 готовности, сюда же по/входу 24 признака данных поступаетинформация об условии готовности данных.Из регистра 16 готовности запросыпоступают в блок 9 приоритета, который предназначен для выработки определенного порядка выдачи запросов. Свыхода 26 выдается код запроса.Блок 5 синхронизации формируетвременную последовательность синхро 1539776Очередность выдачи запросов на второй выход 26 реализуется следующим образом:запрос, поступающий на вход 75, немедленно проходит на выход 26запрос, поступающий на вход 15, проходит через элемент И 71 на выход 26 только при отсутствии запроса на входе 75запрос, поступающий на вход 75, проходит через элемент И 73 на выход50 26, тогда и только тогда, когда отсутствуют запросы на входах 75, и 75Блок 5 синхронизации предназначенч55 ,для формирования определеннои временной последовательности синхроимпульсов, необходимых для организацииправильной работы устройства микропрог 45 сигналов, используемых для формирования временных соотношений при выполнении микропрограммы, В исходное состояйие блок синхронизации приводится по входу 23 "Запуск".5Блок 1 0 фиксации запросов предназначен для промежуточного хранения запросов, поступающих из блока 15 маскирования запросов, и последующей ихпередачи в регистр 16 готовности,Запросы, поступающие на информа.ционный вход 65, запоминаются в регистре 61. После прихода сигнала насинхровход 66 каждый запрос черезсвой элемент И (62, 63 или 64) поступает на выход 67 и одновременнообнуляет соответствующий триггер,переводя его в состояние готовностипринять очередной запрос.20Блок 9 приоритета предназначендля выработки определенного г 1 орядкавыдачи запросов, поступающих из регистра 16 готовности, а также формирования сигнала, характеризующегоотсутствие запросов в этом регистре(состояние, когда все запросы обслужены),При отсутствии запросов на информационном входе 75 появляются единичные сигналы на выходах инверторов68 - 70 и, соответственно, элементаИ 73. Импульс, поступающий на синхровход 76 при наличии сигнала на выходе элемента И 73 взводит триггеР 74и на первом выходе 77 появится сигнал, говорящий о том, что все запросы в регистре 16 готовности обслужены,40 раммного управления векторного процесса.При подаче сигнала на вход 23 запуска устройства тактовый генератор78 начинает непрерывно вырабатыватьимпульсы, поступающие на счетный входсчетчика 79, выходы которого соединены с дешифратором 80 таким образом, что еслиимеется разрешающийсигнал на управляющем входе 86; то навыходах с 87 по 91 циклически формируются сигналы в соответствии с временной диаграммой (фиг.8).Сигнал на выходе 92 формируетсяв моменты времени так же, как сигнална выходе 89, но в отличие от него,не зависит от разрешающего сигналана входе 86,Блок 15 маскирования запросов(фиг.3) предназначен для разрешенияили запрещения прохождения запросовв блок 10 фиксации запросов, а также формирования сигналов, необходимых для подсчета длины вектора.всчетчике 7,Для маскирования запросовна выдачу результатов, поступающихс входа 56 на определенное числошагов в счетчике 39 предварительнос входа 57 по входу 54 разрешения записи заносится некоторая константа,При этом на выходе счетчика отсутствует сигнал разрешения прохождениязапросов с входа 56 через элементИ 41 на выход 60. Одновременно разрешается прохождение этих же запросов через элемент И 40 при появлениитактового сигнала. Запросы с выходаэлемента 40 поступают на вычитающийвход счетчика 39 и уменьшают его содержимое до тех пор, пока он не обнулится и не заблокирует дальнейшеепрохождение запросов на свой вход,При этом на выходе счетчика появляется сигнал разрешения прохождения запросов через элемент И 41 на выход 60по синхроимпульсам, поступающим натактовый вход, Такой способ маскирования запросов устраняет ложное считывание результатана число шагов,равное глубине конвейера, На входы55 и 55 с блока 11 перекодировки1.поступают сигналы признаков операциивектор-скаляр и скаляр-вектор соответственно. При наличии сигналов навходах 55и 55 можно замаскироватьзапросы на очередные элементы операндов, поступающие с входов 56 и56, причем замаскировать все запро 1539776 10сы, кроме первого. Действительно,если отсутствует сигнал переполнения счетчика длины вектора на входе 58; то по тактовому сигналу первые запросы с входов 56и 56 э через элемент И 48, 43 и 47, 42 соответственно проходят на установочные входы триггеров 52 и 53. При этом на их инверсных выходах появляются сигналы, запрещающие прохождение последующих запросов через элементы И 48, 49 и 47, 50 соответственно на выход 60.Таймер 13 служит для разрешения или запрещения записи признаков в регистр 14 векторных признаков. Для маскирования сигнала разрешения записи (выход 38) на определенное чис- ло шагов в счетчик 31 с информационного входа 34 (по сигналу разрешения записи управляющего входа 35 ) заносится некоторая константа, При этом на выходе счетчика возникает сигнал, запрещающий прохождение сигнала с входа 35,стробируемого синхросигналом с входа 37, через элемент И 33 и одновременно разрешающий прохождение синхросигналов с входа 36 через элемент И 32 на вычитающий вход счетчика. При этом синхросигналом происходит уменьшение содержимого счетчика до тех пор, пока он не обнулится и не заблокирует элемент И 32. После обнуления до записи новой константы на выходе счетчика стоит сигнал разрешения прохождения сигнала записи с входа 35через элемент И 33 на вход 38.В случае использования блока 15 маскирования запросов (второй вариант ,цля маскирования запросов на определенное число шагов в счетчики 106 - 108 предварительно с входа 122 задания интервала времени(по соответствующим сигналам разрешения записи второго управляющего входа 119) заносятся некоторые константы, При этом на выходах счетчиков отсутствуют сигналы разрешения прохождения запросов с входов 120 через блок 11. и элементы И 113 и 115 на выход 125. Одновременно разрешается прохождейие этих же запросов через элементы И 109 - 111 при отсутствии сигнала переполнения счетчика длины вектора на входе 121. Запросы с выходов элементов И 109 и 110 и блока 11 поступают на вычитающие входы счетчиков 106 - 108 и уменьшают их содержимое до тех пор, пока они не обнулятсяи не заблокируют прохождение запросов на свои входы, При этом на выходах счетчиков появятся сигналы разрешения прохождения запросов черезэлементы И 112, 113 и 115 на выход125 по синхроимпульсам, поступающимна вход,123. Если на входе 121 присутствует сигнал переполнения счетчика длины вектора, то запросы с вхо- дов 120 120 на выход 125 не приходят,В блоке 15 маскирования (фиг.9)по входу 124 осуществляется такжевыбор одного из запросов, по которому происходит счет в счетчике 7 длины вектора. Если на входе 124 присутствует единичный сигнал и нет пе 20 реполнения счетчика длины вектора(отсутствует сигнал на входе 121),то запрос с входа 120 проходит навыход 125. В противном случае (навходе 124 нулевой сигнал) на выход25 126 через элементы И 117 и ИЛИ 118проходит запрос с входа 120,В случае использования в схемеустройства дополнительно блока 17элементов И признаки вектора результата могут выдаваться на выход 28через блок 17 элементов И при наличии соответствующего разрешения вмикропрограмме получения данного результата.В случае использования в схеме35устройства дополнительного блока 18обслуживания обмена возможна организация функционирования устройства сдвойными или одинарными операндами,)40 а также обслуживания запросов на получение очередных элементов операндов или выдачу результатаПри поступлении на вход 103 единичных сигналов, говорящих о том,что будут обрабатываться операндыдвойной длины, на выходе одного изэлементов И 93, 94 или 95 в зависи"мости от того, какой из трех сигналов в данный момент поступил на вход104, появится единичный сигнал, поступающий через элемент ИЛИ 100 навход триггера 102, Одновременно этотсигнал поступает на инверсный входэлемента И 97 и запрещает прохождение признака данных с входа 24 признака данных через элемент И 97 и ИЛИ101 на выход 105. Поскольку триггер102 в начальный момент времени находится в. нулевом состоянии, то он так 15397же запрещает прохождение первого сигнала признака данных через элементыИ 96 и ИЛИ 101 на выход 105. По заднему фронту первого сигнала признакаданных, поступающего на С-вход, триггер 102 перебрасывается в единичное состояние и разрешает прохождение следующего признака данных черезэлементы И 96 и ИЛИ 101 на выход 105,По заднему фронту второго сигналапризнака данных триггер сбрасывается, в нулевое состояние. Таким образом,если обрабатываются операнды двойнойдлины, на выходе 105 появляется каждый второй сигнал признака данных,поступающий на вход регистра готовности. Если же для какого-либо сигнала запроса отсутствует соответствующий сигнал признака операнда двойной 20длины (вход 103), то на выходе элемента ИЛИ 100 присутствует нулевойсигнал, разрешающий прохождение первого сигнала призйака данных с входа24 через элементы И 97 и ИЛИ 101 на 25выход 105Блок 18 обеспечивает также формирование сигналов чтейия (выдачи) результата или записи (приема) операндов. Если на вход элемента И 95 пошине 104 поступает единичный сигнал,соответствующий запросу на выдачу результата, то на выходе элемента И 98по входу 24 признака данных возникает сигнал чтения, поступающий на выход 29. Если же на входе элемента35И 95 отсутствует единичный сигнал,то по сигналам признака данных навыходе элемента И 99 возникают сигналы записи соответствующего операнда, поступающие на выход 30,Таким образом, благодаря блоку 18обслуживания обмена обеспечиваетсяуправление операндами и результатом,как одинарной, так и двойной длины. 45а также обеспечивается возможностьработы устройства с магистралью обмена данными для многопроцессорныхустройств и уменьшение разрядностикода признаков управления запросами.Формула изобретения1. Устройство микропрограммного управления, содержащее блок памяти перекодировки, блок формирования адреса, блок памяти микрокоманд, регистр микрокоманд, блок синхрониза- .ции, блок дешифраторов, регистр век 26торных признаков, регистр состояний и мультиплексор, причем адресный вход блока памяти перекодировки является входом кода команды устройства, выход поля адреса начальной микрокоманды блока памяти перекодировки соединен с первым информационным входом блока формирования адреса, информационный выход которого соединен с адресным входом блока памяти микро- команд, выход которого соединен с информационным входом регистра микрооманд, выход поля микроопераций которого соединен с входом блока дешифраторов, группа, выходов которого является группой выходов кода микро- операций устройства, первый и второй выходы блока дешифраторов соединены соответственно с управляющим входом мультиплексора и первым управляющимвходом блока формирования адреса,второй управляющий, второй информационный и тактовый входы которого соединены соответственно с выходом мультиплексора, выходом поля адреса регистра микрокоманд и первым выходом блока синхронизации, второй выход и вход запуска которого соединены соответственно с тактовым входом реги-. стра микрокоманд и входом запуска устройства, первый и второй входы логических условий устройства подклю" чены к информационным входам соответственно регистра состояний и регистра векторных признаков, выходы которых соединены соответственно с первым и вторым информационными входами мультиплексора, тактовый вход регистра состояний соединен с третьим выходом блока синхронизации, о тл и ч а ю щ е е с я тем, что, с целью расширения области применения. за счет обеспечения использования его для управления векторным процессором конвейерной обработки данных, оно дополнительно содержит счетчик длины вектора, таймер, блок маскирования запросов, блок фиксации запросов, регистр готовности и блок приоритета, информационный выход которого является выходом кода запроса данных устройства, информационный вход блока приоритета соединен с выходом регистра готовности, первый и второй информационные входы которого подключены соответственно к третьему входу логических условий устройства и выходу блока фиксации запросов, ин 13 15 формационный вход которого соединен с.информационным выходом блока маскирования запросов, вход задания интер-. вала времени маскирования которого соединен с выходом поля задания интервала времени регистра микрокоманд и входом задания интервала времени таймера, вход признака режима работы которого соединен с третьим входом блока дешифраторов и первым управляющим входом блока маскирования запросов, второй управляющий вход и вход настройки которого соединен соответственно с четвертым выходом блока дешифраторов и с выходом поля настройки блока памяти перекодировки, третий управляющий вход блока маскирования запросов соединен с выходом переполнения счетчика длины вектора и дополнительным разрядом информационного входа регистра векторных признаков, вход записи которого соединен с выходом таймера, первый тактовый вход которого соединен с тактовым входом блока фиксации запросов и третьим входом блока синхронизации, четвертый, пятый и шестой выходы которого соединены соответственно с вторым тактовым входом таймера, тактовым входом блока маскирования запросов и тактовым входом блока приоритета, выход признака отсутствия запросов которого соединен с входом управления режимами блока синхронизации, управляющий выход блока маскирования запросов соединен со счетным входом счетчика длины вектора, установочный вход которого является входом задания кода длины вектора устройства.2, Устройство по п,1, о т л и - ч а ю щ е е с я тем, что блок маскирования запросов содержит два триггера, одиннадцать элементов И, элемент ИЛИ и счетчик, выход переноса которого соединен с инверсным входом первого и первым входом второго элементов И, выход первого элемента И соединен со счетным входом счетчика, информационный вход которого является входом задания интервала времени блока, первые входы третьего и четсвертого элементов И являются соответственно первым и вторым разрядами входа настройки блока, третий разряд входа настройки которого подключен к первому входу пятого и инверсному входу шестого элементов И, выходы ко 39776 14 5 10 15 20 25 30 35 40 45 50 55 торых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с прямым входом седьмого элемента И, инверсный вход которого соединен с инверсными входами восьмого и девятого элементов И и является третьим управляющим входом блока, тактовый вход которого подключен к первым прямым входам первого, восьмого и девятого элементов И, второй прямой вход первого элемента И соединен с вторым входом второго элемента И и является первым разрядом второго управляющего входа блока, второй разряд второго управ" ляющего входа которого подключен к прямому входу шестого элемента И и второму прямому входу девятого элемента И, выход которого соединен с вторым входом четвертого элемента И и первым входом десятого элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход установки в "1" которого соединен с выходом четвертого элемента И, третий разряд второго управляющего входа блока подключен к второму входу пятого элемента И и второму прямому входу восьмого элемента И, выход которого соединен с вторым входом третьего элемента И и первым входом одиннадцатого элемента И, второй вход которого соединен с инверсным выходом второго триггера, вход установки в "1" которого соединен с выходом третьего элемента И, вход задания режима записи-счета счетчика является первым управляющим входа блока, выходы второго, десятого и одиннадцатого элементов И образуют информационный выход блока, управляющий выход которого подключен к выходу седьмого элемента И, входы установки в О первого и второго триггеров соединены между собой и подключены к входу начальной установки устройства.3. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок маскирования запросов содержит три счетчика, девять элементов И и элемент ИЛИ, причем информационные входы с первого по третий счетчиков образуют вход задания интервалов времени блока, счетные входы с первого по третий счетчиков соединены с выходами соответственно с первого по третий элементов И, первые инверсные входы которых соединены с инверсными входа153977 б 1 бсодержит блок элементов И, первый вход которого соединен с выходом ре- гистра векторных признаков, второй вход и выход блока элементов И подключены соответственно к третьему выходу блока дешифраторов и к выходу векторных признаков устройства. 15 ми с четвертого по шестой элементов И и подключены к третьему управляюще му входу блока, первый управляющий вход которого образуют входы задания режима записи-счета с первого по третий счетчиков, выход переноса пер вого счетчика соединен с вторым инверсным входом первого и первым прямым входом четвертого элементов И, второй прямой вход четвертогф, первый прямой пятого и первый вход седьмого элементов И соединены между собой и подключены к тактовому входу блока, вход настройки которого подключен к первому входу восьмого и инверсному входу девятого элементов И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен 2 О с прямым входом шестого элемента И, выход которого является управляющим ,выходом блока, информациойный выход которого образует выходы четвертого, пятого и аедьмого элементов И, выход 25 переноса второго счетчика соединен с вторым инверсным входом второго и вторым прямым входом пятого элементов И выходы переноса третьего счетчика соединен с вторым инверсным входом третьего и вторым входом седьмого элементов И, первый разряд второго управляющего блока подключен к прямому входу первого, третьему прямому входу четвертого и второму входу восьмого элементов И, второй разряд вто 35 ,рого управляющего входа блока подключен к прямому входувторого,третьему прямому входу пятого и прямому входу девятого элементов И, третий разряд второго управляющего входа блока подключен к прямому входу третьего и третьему входу седьмого элементов И.4 устройство по п.1, 0 т л и ч аю щ е е с я тем, что дополнительно 5, Устройство по п.1, о т л и -ч а ю щ е е с я тем, что дополнительно содержит блок обслуживанияобмена, содержащий семь элементов И,два элемента ИЛИ и триггер, причемдополнительные три разряда выхода поля настройки. блока памяти перекодировки соединены с первыми входами соответственно первого, второго и третьего элементов И, выходы которых соединены соответственно с первым,итретьим входами первого элемента ИЛИ,выход которого соединен с инверснымвходом четвертого элемента И и инфор"мационным входом триггера, вход синхронизации которого соединен с прямыми входами третьего и четвертого элементов И, первыми входами пятого ишестого элементов И и подключены квходу признака данных устройства,выход триггера соединен свторым входомпятого элемента И, выход которогосоединен с первым входом второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и входомсинхронизации регистра готовности,второй информационный вход которогосоединенс информационным выходомблока приоритета и с вторыми входамипервого, второго, третьего и шестогоэлементов И и инверсным входом четвертого элемента И, выходы шестогои четвертого элементов И являютсясоответственно первым и вторым выходами синхронизации запросов устройства,

СмотретьЗаявка

4196704, 19.02.1987

ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

КРИВОРУЧКО ВИТАЛИЙ ФЕДОРОВИЧ, ШЕВЦОВ СЕРГЕЙ ВАЛЕНТИНОВИЧ, СОКОЛОВ ВЛАДИМИР ВЛАДИМИРОВИЧ, ВЕЙЦ АЛЕКСАНДР ВЕНИАМИНОВИЧ, МАЛЮГИН ВЛАДИМИР ДМИТРИЕВИЧ, ЖУКОВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, ЛЕВЕРТОВ ЯКОВ АНАТОЛЬЕВИЧ, ДЯТЧИНА ИРИНА ФЕДОРОВНА, СПЕРАНСКАЯ ИРИНА ВЛАДИМИРОВНА

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 30.01.1990

Код ссылки

<a href="https://patents.su/12-1539776-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для комбинационно-логического управления сложными системами

Следующий патент: Устройство переменного приоритета

Случайный патент: Би5л; -(оггка