Устройство для вычисления нормированных статистических моментов случайных процессов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1385131

Авторы: Гусев, Козловский, Хмельник, Штеренберг

Текст

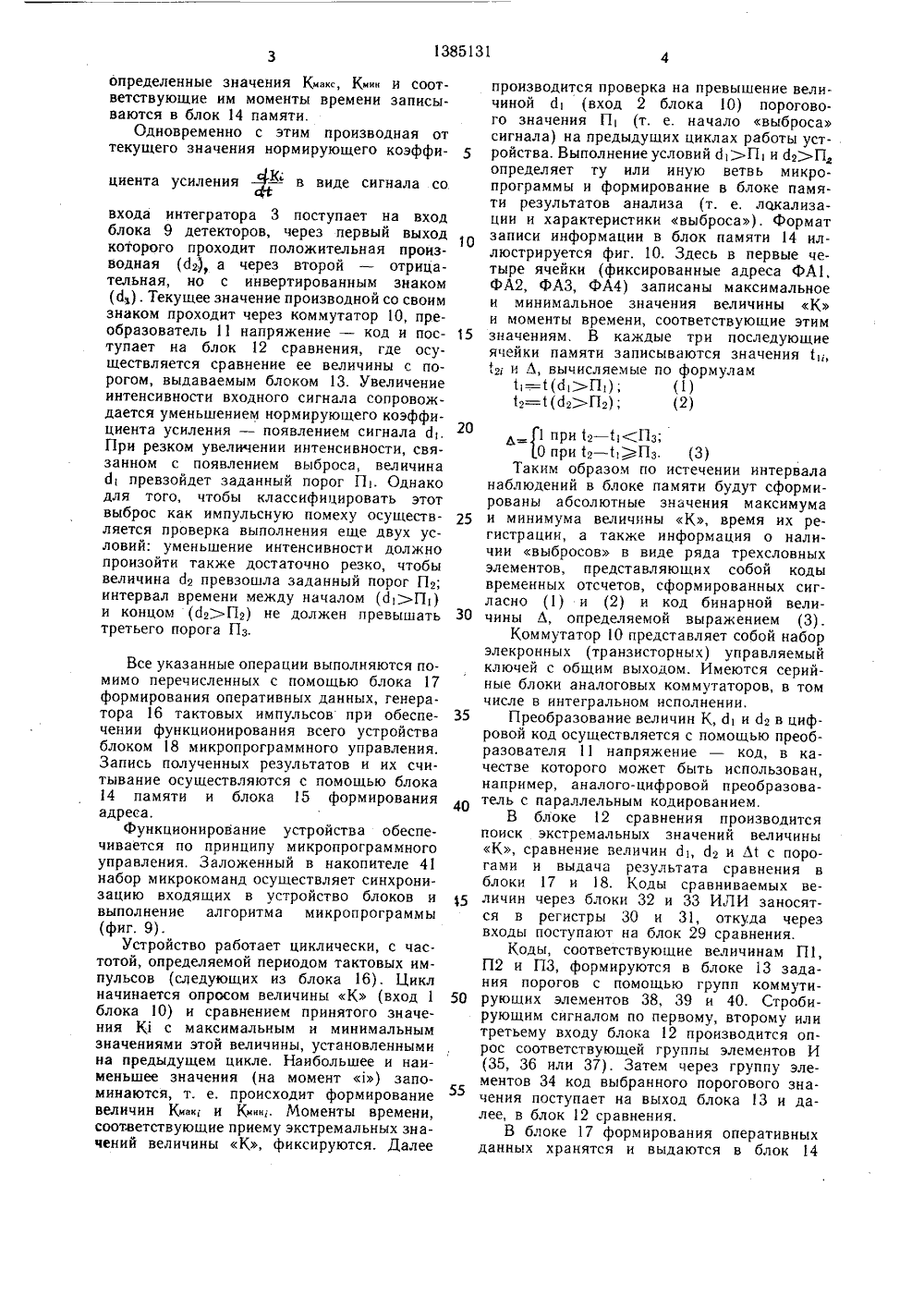

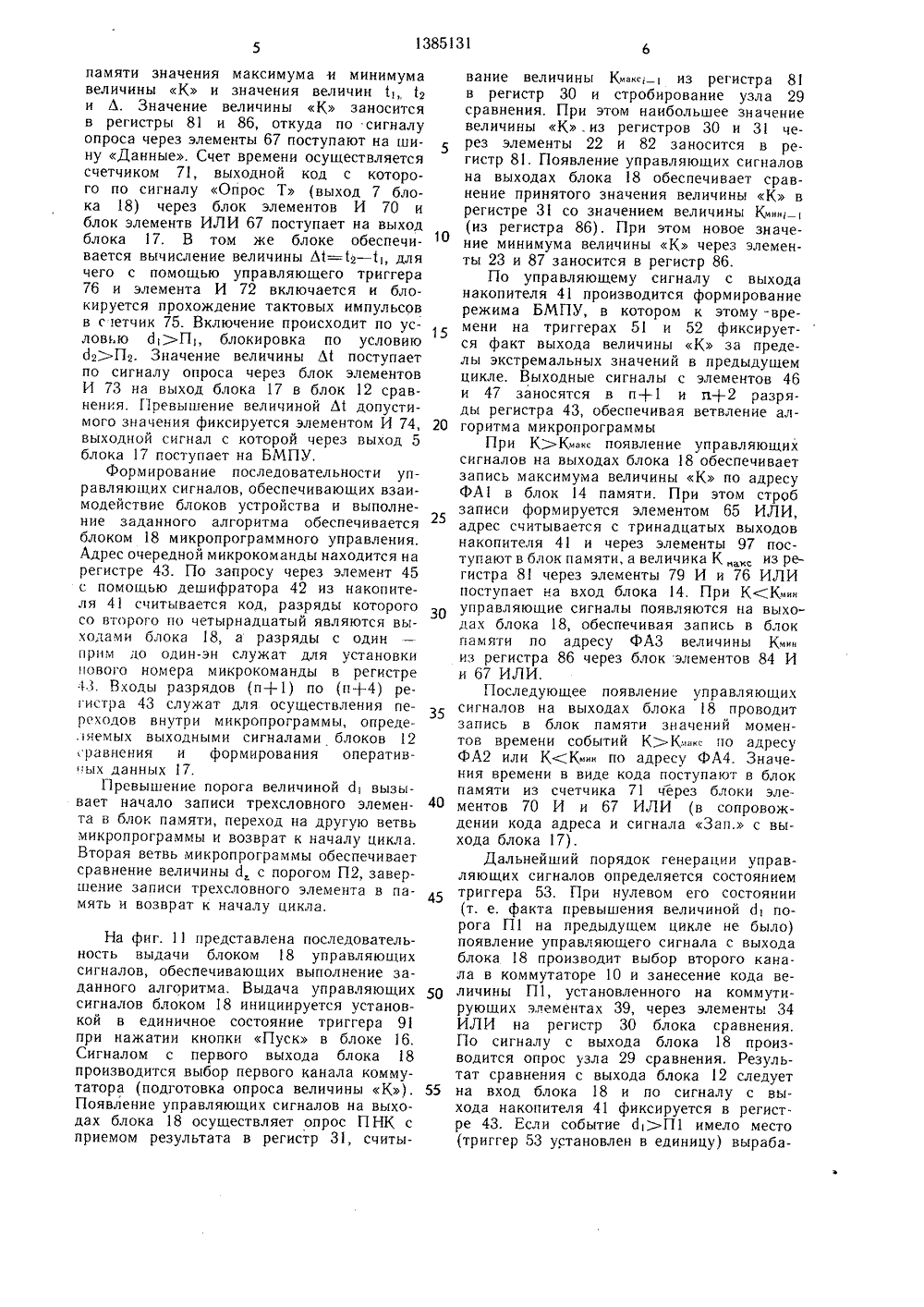

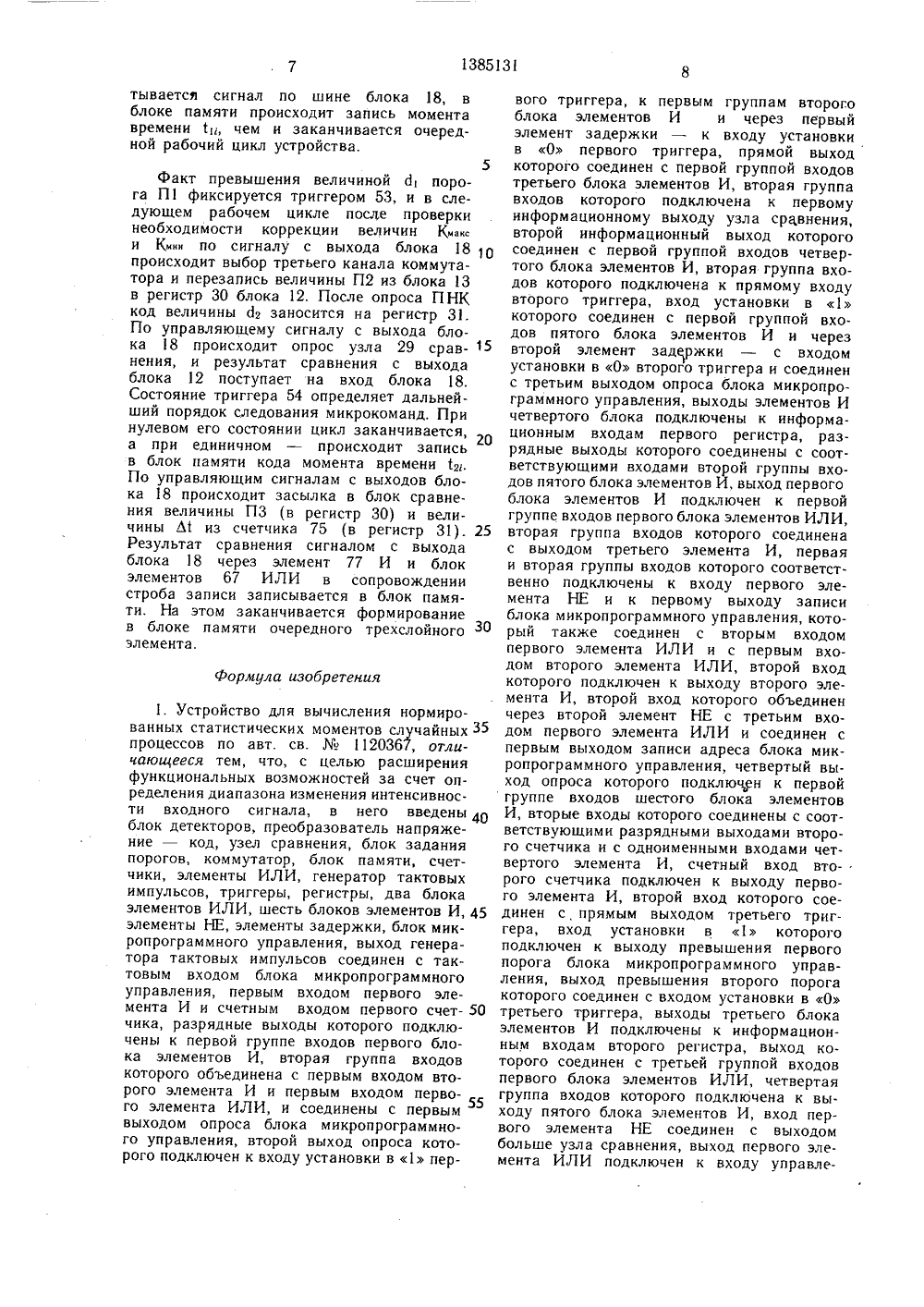

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК сю 4 б 06 6 7 52 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НОРМИРОВА ННЫХ СТАТИСТИЧЕСКИХ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ (57) Изобретение может быть использовано при исследовании и классификации случайных процессов, в том числе нестационарных, зашумленных импульсными помехами. Целью изобретения является расширение функциональных возможностей уст 801385131 А 2 ройства за счет определения диапазона изменения интенсивности входного сигнала и фиксирования импульсных помех. Цель достигается благодаря тому, что одновременно с процессами нормирования и вычисления с помощью блока 9 детекторов, коммутатора 10, преобразователя 11 напряжение - код, блока 12 сравнения, блока 13 задания порогов, блока 14 памяти, блока 15 формирования адреса, генератора 16 тактовых импульсов, блока 17 формирования оперативных данных и блока 18 микропрограммного управления в результате обработки сигналов со входа и выхода интегратора 3 производится определение диапазона изменения интенсивности входного сигнала на всем интервале обработки, выявление и фиксирование импульсных по- э мех. 1 з.п. ф-лы, 11 ил.138513 7 Фиа 10 ол Тг У=да ыюор пер ога папа бпаю Ю Останоб Ппрос пик4 Ьтись кора Ю ЮПроС Кмис из Рг 81 км нва(пг/ Юкмо КпфО= йОпрос уооп сра нЗапись ;ос б Строб.Запись щроб Лыись Вьи 7 аиа Фп Виооца Фрг и Опрос к ;.1 ио Рг ВбОПРОС Кмиос В Опрос 4 максЮпросуда сро н. 20 Зались Кта б Рг 6 б ц Слроб,ооо Ьпуоб .ЗаписьО 2 Вюдоио Ю Иаиа ФП 4 1 г опись Тип бч 71 7 глана о рмгогтоПу В Ргз 7 Запись Тио С днцкньбрх дпприргщп 4= ыпор оаюого аиа- Опрос щоееьего кцо Йоа ш2 нала Иоо 10Оарос п 1 оо борко 1 б Опрос П 2 ио Юшка О Юапись Тоо С орос Ш иобп, 1 б б Опрос пик Опрос ПИКЗапись коуп и Я.У 4 Запись обо урга Опрос аТипйо 7 Х Опрос уопп сра 1.гу б Опрос уопасро 3. Л б Опрпсутсрабп гс Ю Усщоно ка рвяипабИПУ б Рг 45 Упппно и ренпнабг 1 ПУ о Рг О йапись Вепиицны Ргнф д РЩф 43=1 данегп опись Тцо Си 71 7 Уиг. 11Соста вител ь И. М ухи нТехред И. ВересТираж 704комитета СССР по делам иа, Ж - 35, Раушская набическое предприятие, г. Уж40 45 50 55 Изобретение относится к вычислительной технике и может быть использовано при исследовании и классификации случайных процессов,Целью изобретения является расширение функциональных возможностей за счет определения диапазона измерения интенсивности входного сигнала и фиксирование наличия импульсных помех.На фиг. 1 приведена структурная схема устройства, на фиг. 2 - 8 - примеры схемной реализации блока детекторов, блока сравнения, блока задания порогов, блока микропрограммного управления, блока. формирования оперативнь 1 х данных, генератора тактовых импульсов и блока формирования адреса соответственно; на фиг. 9 укрупненная блок-схема алгоритма определения динамического диапазона и наличия импульсной помехи; на фиг. 10 - формат записи информации в блоке памяти; на фиг. 11 - блок-схема алгоритма работы блока микропрограммного управления.Устройство содержит центр ирующий фильтр 1, блок 2 определения моментов, интегратор 3, блок 4 умножения, квадратор 5, блок 6 усреднения, коммутатор 7, блок 8 переключения постоянной времени интегрирования, блок 9 детекторов, коммутатор 10, преобразователь 11 напряжение - код, узел 12 сравнения, блок 13 задания порогов, блок 14 памяти, блок 15 формирования адреса, генератор 16 тактовых импульсов, блок 17 формирования оперативных данных, блок 18 микропрограммного управления.Блок 9 детекторов содержит инвертор 19, детекторы 20 и 21. Узел 12 сравнения содержит группы элементов ИЛИ 22 и 23, группы элементов И 24 - 27, элемент НЕ 28, блок 29 сравнения, регистры 30 и 31, группы элементов ИЛИ 32 и ЗЗ. Блок 13 задания порогов содержит группу элементов ИЛИ 34, группы элементов И 35 - 37, группы коммутирующих элементов 38 - 40. Блок 18 микропрограммного управления содержит накопитель 41, дешифратор 42, регистр 43, элемент 44 задержки, элемент ИЛИ 45, элементы И 46 - 49, элемент 50 задержки, триггеры 51 - 54, элементы И 55 - 58, элемент НЕ 59, триггеры 60 - 63, элемент ИЛИ 64. Блок 17 формирования оперативных данных содержит элементы ИЛИ 65, 66, блок элементов ИЛИ 67, элемент И 68, элемент НЕ 69, блок элементов И 70, счетчик 7, элемент И 72, блоки элементов И 73 и 74, счетчик 75, триггер 76, элемент И 77, элемент 8 задержки, блок элементов И 79, триггер 80, регистр 81, блок элементов И 82, элемент 83 задержки, блок элементов И 84, триггер 85, регистр 86, блок элементов И 87, элемент НЕ 88. Генератор 16 тактовых импульсов содержит задающий гене 5 10 15 20 25 30 35 ратор 89, элемент И 90, триггер 91, одновибраторы 92 и 93, коммутирующие элементы 94 и 95.Блок 15 формирования адреса содержит счетчик 96 блок элементов ИЛИ 97,Устройство работает следующим образом.Сигнал, поступающий на вход устройства, проходит через центрирующий фильтр 1 и перемножается в блоке 4 умножения с нормирующим коэффициентом усиления, вырабатываемым на выходе интегратора 3. Нормированный сигнал и его квадрированное значение, получаемое на выходе квадратора 5, поступают в блок 2 определения моментов, где вычисляются необходимые статистические моменты случайного процесса. Одновременно с этим сигнал с выхода квадратора 5 усредняется в блоке 6, Полученный сигнал (2) поступает на первый вход коммутатора 7, на второй вход которого поступает сигнал опорного напряжения (2 ю) . Эти сигналы сравниваются по величине и при 2(2 ю на выходе коммутатора проходит прямой сигнал с выхода интегратора 3, а при 2)2 ю - инверсный. С выхода коммутатора 7 сигнал поступает на первый вход блока 8 переключения постоянной времени интегрирования, в то время как на второй и третий входы блока 8 поступают соответственно сигналы 2 и 2 ю. Проходя через блок 8, сигнал интегрируется на интеграторе 3 с постоянной времени, величина которой автоматически устанавливается в соответствии с выбранной зависимостью от текущей интенсивности нормируемого сигнала.Одновременно с процессами нормирования и вычисления статистических моментов нормированного сигнала происходит определение диапазона изменения интенсивности входного сигнала на всем анализируемом участке (интервале) обработки, выявление и фиксирование выбросов интенсивности входного сигнала, которые можно классифицировать в качестве импульсных помех. С этой целью текущее значение нормирующего коэффициента усиления Кс в виде сигнала с выхода интегратора 3 через коммутатор 10 и преобразователь 11 напряжение - код после преобразования подается на блок 12 сравнения, где осуществляется сравнение его величины с наибольшим Кмакс; 1 и наименьшим Кмнн - 1 за предыдущий цикл обработки его значениями, хранящимися в блоке 17 формирований оперативных данных. В тех случаях, когда К;)Кмакс;или К,(Кмнн;происходит изменение хранящегося наибольшего или наименьшего значения К с одновременной фиксацией с помощью генератора тактовых импульсов соответствующего им времени отсчета 1. В противном случае оперативная информация не изменяется. По окончании процесса обработкиопределенные значения Кмакс, Кмис и соответствующие им моменты времени записываются в блок 14 памяти.Одновременно с этим производная от текущего значения нормирующего коэффициента усиления- в виде сигнала соЫК;входа интегратора 3 поступает на вход блока 9 детекторов, через первый выход которого проходит положительная производная (дг), а через второй - отрицательная, но с инвертированным знаком (6), Текущее значение производной со своим знаком проходит через коммутатор 10, преобразователь 11 напряжение - код и поступает на блок 12 сравнения, где осуществляется сравнение ее величины с порогом, выдаваемым блоком 13. Увеличение интенсивности входного сигнала сопровождается уменьшением нормирующего коэффициента усиления - появлением сигнала д. При резком увеличении интенсивности, связанном с появлением выброса, величина д превзойдет заданный порог П. Однако для того, чтобы классифицировать этот выброс как импульсную помеху осуществляется проверка выполнения еще двух условий: уменьшение интенсивности должно произойти также достаточно резко, чтобы величина дг превзошла заданный порог Пг; интервал времени между началом (д)П) и концом (дг)Пг) не должен превышать третьего порога Пз 35 40 5 50 55 Все указанные операции выполняются помимо перечисленных с помощью блока 17 формирования оперативных данных, генератора 16 тактовых импульсов при обеспечении функционирования всего устройства блоком 18 микропрограммного управления, Запись полученных результатов и их считывание осуществляются с помощью блока 14 памяти и блока5 формирования адрееа.Функционирование устройства обеспечивается по принципу микропрограммного управления, Заложенный в накопителе 41 набор микрокоманд осуществляет синхронизацию входящих в устройство блоков и выполнение алгоритма микропрограммы (фиг. 9).Устройство работает циклически, с частотой, определяемой периодом тактовых импульсов (следующих из блока 16) . Цикл начинается опросом величины К (вход 1 блока 10) и сравнением принятого значения К с максимальным и минимальным значениями этой величины, установленными на предыдущем цикле. Наибольшее и наименьшее значения (на момент Ь) запоминаются, т. е. происходит формирование величин Кмак; и Кмкн;. Моменты времени, соответствующие приему экстремальных значений величины К, фиксируются. Далее 10 15 20 25 30 производится проверка на превышение величиной д (вход 2 блока 10) порогового значения П, (т. е. начало выброса сигнала) на предыдущих циклах работы устройства. Выполнение условий с 1)П и дг)П определяет ту или иную ветвь микропрограммы и формирование в блоке памяти результатов анализа (т. е. локализации и характеристики выброса). Формат записи информации в блок памяти 14 иллюстрируется фиг. 10. Здесь в первые четыре ячейки (фиксированные адреса ФА 1, ФА 2, ФАЗ, ФА 4) записаны максимальное и минимальное значения величины К и моменты времени, соответствующие этим значениям. В каждые три последующие ячейки памяти записываются значения г и Л, вычисляемые по формулам=(а)п );1 г=1(дг)Пг) (2) 1 при 1 г 11(Пз0 при 1 г - 1)Пз. (3)Таким образом по истечении интервала наблюдений в блоке памяти будут сформированы абсолютные значения максимума и минимума величины К, время их регистрации, а также информация о наличии выбросов в виде ряда трехсловных элементов, представляющих собой коды временных отсчетов, сформированных сигласно (1) и (2) и код бинарной величины Л, определяемой выражением (3) .Коммутатор0 представляет собой набор элекронных (транзисторных) управляемый ключей с общим выходом. Имеются серийные блоки аналоговых коммутаторов, в том числе в интегральном исполнении.Преобразование величин К, д и сг в цифровой код осуществляется с помощью преобразователя 11 напряжение - код, в качестве которого может быть использован, например, аналого-цифровой преобразователь с параллельным кодированием,В блоке 12 сравнения производится поиск экстремальных значений величины К, сравнение величин дь дг и Л с порогами и выдача результата сравнения в блоки 17 и 18. Коды сравниваемых величин через блоки 32 и 33 ИЛИ заносятся в регистры 30 и 31, откуда через входы поступают на блок 29 сравнения.Коды, соответствующие величинам П 1, П 2 и ПЗ, формируются в блоке 13 задания порогов с помощью групп коммутирующих элементов 38, 39 и 40. Стробирующим сигналом по первому, второму или третьему входу блока 12 производится опрос соответствующей группы элементов И (35, 36 или 37). Затем через группу элементов 34 код выбранного порогового значения поступает на выход блока 13 и далее, в блок 12 сравнения.В блоке 17 формирования оперативных данных хранятся и выдаются в блок45055 памяти значения максимума и минимума величины К и значения величин и Л. Значение величины К заносится в регистры 81 и 86, откуда по сигналу опроса через элементы 67 поступают на шину Данные. Счет времени осуществляется счетчиком 71, выходной код с которого по сигналу Опрос Т (выход 7 блока 18) через блок элементов И 70 и блок элементв ИЛИ 67 поступает на выход блока 17, В том же блоке обеспечивается вычисление величины Л 1=2 - 1 ь для чего с помощью управляющего триггера 76 и элемента И 72 включается и блокируется прохождение тактовых импульсов в с етчик 75. Включение происходит по условию д)ПВ блокировка по условию д 2)П. Значение величины М поступает по сигналу опроса через блок элементов И 73 на выход блока 17 в блок 12 сравнения. Превышение величиной Л допустимого значения фиксируется элементом И 74, выходной сигнал с которой через выход 5 блока 17 поступает на БМПУ.Формирование последовательности управляющих сигналов, обеспечивающих взаимодействие блоков устройства и выполнение заданного алгоритма обеспечивается блоком 18 микропрограммного управления, Адрес очередной микрокоманды находится на регистре 43. По запросу через элемент 45 с помощью дешифратора 42 из накопителя 41 считывается код, разряды которого со второго по четырнадцатый являются выходами блока 18, а разряды с один прим до один-эн служат для установки нового номера микрокоманды в регистре 4.3. Входы разрядов (п+1) по (п+4) регистра 43 служат для осуществления переходов внутри микропрограммы, опреде- .немых выходными сигналами блоков 12 равнения и формирования оператив ы х да нных 17.Превышение порога величиной д 1 вызывает начало записи трехсловного элемента в блок памяти, переход на другую ветвь микропрограммы и возврат к началу цикла. Вторая ветвь микропрограммы обеспечивает сравнение величины д, с порогом П 2, завершение записи трехсловного элемента в память и возврат к началу цикла. На фиг. 11 представлена последовательность выдачи блоком 18 управляющих сигналов, обеспечивающих выполнение заданного алгоритма. Выдача управляющих сигналов блоком 18 инициируется установкой в единичное состояние триггера 91 при нажатии кнопки Пуск в блоке 16. Сигналом с первого выхода блока 18 производится выбор первого канала коммутатора (подготовка опроса величины К), Появление управляющих сигналов на выходах блока 18 осуществляет опрос ПНК с приемом результата в регистр 31, считы 5 10 15 20 25 30 35 40 45 ВВНИЕ ВЕЛИЧИНЫ Кмакс; 1 ИЗ рЕГИСтра 81 в регистр 30 и стробирование узла 29 сравнения. При этом наибольшее значение величины К . из регистров 30 и 31 через элементы 22 и 82 заносится в регистр 81. Появление управляющих сигналов на выходах блока 8 обеспечивает сравкение принятого значения величины К в регистре 3 со значением величины К "; (из регистра 86). При этом новое значение минимума величины К через элементы 23 и 87 заносится в регистр 86,По управляющему сигналу с выхода накопителя 41 производится формирование режима БМПУ, в котором к этому -времени на триггерах 51 и 52 фиксируется факт выхода величины К за пределы экстремальных значений в предыдущем цикле. Выходные сигналы с элементов 46 и 47 заносятся в п+1 и и+2 разряды регистра 43, обеспечивая ветвление алгоритма микропрограммыПРИ К)Кмакс ПОЯВЛЕНИЕ уПраВЛЯЮЩИХ сигналов на выходах блока 18 обеспечивает запись максимума величины К по адресу ФА 1 в блок 14 памяти. При этом строб записи формируется элементом 65 ИЛИ, адрес считывается с тринадцатых выходов накопителя 41 и через элементы 97 поступают в блок памяти, а величика К из регистра 8 через элементы 9 И и 76 ИЛИ поступает на вход блока 14, При К(К управляющие сигналы появляются на выходах блока 18, обеспечивая запись в блок памяти по адресу ФАЗ величины К.", из регистра 86 через блок элементов 84 И и 67 ИЛИ.Последующее появление управляющих сигналов на выходах блока 18 проводит запись в блок памяти значений моменВремени событий К) Кмакс по адресу ФА 2 или К(К-. по адресу ФА 4. Значения времени в виде кода поступают в блок памяти из счетчика 71 через блоки элементов 70 И и 67 ИЛИ (в сопровождении кода адреса и сигнала Зап, с выхода блока 17).Дальнейший порядок генерации управляющих сигналов определяется состоянием триггера 53. При нулевом его состоянии (т. е. факта превышения величиной д 1 порога П 1 на предыдущем цикле не было) появление управляющего сигнала с выхода блока 18 производит Выбор второго канала в коммутаторе 10 и занесение кода величины П 1, установленного на коммутирующих элементах 39, через элементы 34 ИЛИ на регистр 30 блока сравнения. По сигналу с выхода блока 18 производится опрос узла 29 сравнения. Результат сравнения с выхода блока 12 следует на вход блока 18 и по сигналу с выхода накопителя 41 фиксируется в регистре 43. Если событие д 1)П 1 имело место (триггер 53 установлен в единицу) выраба 1385131тывается сигнал по шине блока 18, в блоке памяти происходит запись момента времени 1 и, чем и заканчивается очередной рабочий цикл устройства.5факт превышения величиной дпорога П 1 фиксируется триггером 53, и в следующем рабочем цикле после проверки необходимости коррекции величин Кмакс и Км.н по сигналу с выхода блока 18 10 происходит выбор третьего канала коммутатора и перезапись величины П 2 из блока 13 в регистр 30 блока 12. После опроса ПНК код величины д заносится на регистр 31. По управляющему сигналу с выхода блока 18 происходит опрос узла 29 срав нения, и результат сравнения с выхода блока 12 поступает на вход блока 18, Состояние триггера 54 определяет дальнейший порядок следования микрокоманд. При нулевом его состоянии цикл заканчивается, а при единичном - происходит запись в блок памяти кода момента времени 1 и. По управляющим сигналам с выходов блока 18 происходит засылка в блок сравнения величины ПЗ (в регистр 30) и величины Л 1 из счетчика 75 (в регистр 31). 25 Результат сравнения сигналом с выхода блока 18 через элемент 77 И и блок элементов 67 ИЛИ в сопровождении строба записи записывается в блок памяти. На этом заканчивается формирование в блоке памяти очередного трехслойного З 0 элемента.Формула изобретения1. Устройство для вычисления нормированных статистических моментов случайных 5 процессов по авт. св. Мо 1120367, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения диапазона изменения интенсивности входного сигнала, в него введены 40 блок детекторов, преобразователь напряжение - код, узел сравнения, блок задания порогов, коммутатор, блок памяти, счетчики, элементы ИЛИ, генератор тактовых импульсов, триггеры, регистры, два блока элементов ИЛИ, шесть блоков элементов И, 45 элементы НЕ, элементы задержки, блок микропрограммного управления, выход генератора тактовых импульсов соединен с тактовым входом блока микропрограммного управления, первым входом первого элемента И и счетным входом первого счет чика, разрядные выходы которого подключены к первой группе входов первого блока элементов И, вторая группа входов которого объединена с первым входом второго элемента И и первым входом первого элемента ИЛИ, и соединены с первым выходом опроса блока микропрограммного управления, второй выход опроса которого подключен к входу установки в 1 первого триггера, к первым группам второго блока элементов И и через первый элемент задержки - к входу установки в О первого триггера, прямой выход которого соединен с первой группой входов третьего блока элементов И, вторая группа входов которого подключена к первому информационному выходу узла сравнения, второй информационный выход которого соединен с первой группой входов четвертого блока элементов И, вторая группа входов которого подключена к прямому входу второго триггера, вход установки в 1 которого соединен с первой группой входов пятого блока элементов И и через второй элемент задержки - с входом установки в О второго триггера и соединен с третьим выходом опроса блока микропрограммного управления, выходы элементов И четвертого блока подключены к информационным входам первого регистра, разрядные выходы которого соединены с соответствующими входами второй группы входов пятого блока элементов И, выход первого блока элементов И подключен к первой группе входов первого блока элементов ИЛИ, вторая группа входов которого соединена с выходом третьего элемента И, первая и вторая группы входов которого соответственно подключены к входу первого элемента НЕ и к первому выходу записи блока микропрограммного управления, который также соединен с вторым входом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, второй вход которого объединен через второй элемент НЕ с третьим входом первого элемента ИЛИ и соединен с первым выходом записи адреса блока микропрограммного управления, четвертый выход опроса которого подключен к первойгруппе входов шестого блока элементов И, вторые входы которого соединены с соответствующими разрядными выходами второго счетчика и с одноименными входами четвертого элемента И, счетный вход второго счетчика подключен к выходу первого элемента И, второй вход которого соединен с прямым выходом третьего триггера, вход установки в 1 которого подключен к выходу превышения первого порога блока микропрограммного управления, выход превышения второго порога которого соединен с входом установки в О третьего триггера, выходы третьего блока элементов И подключены к информационным входам второго регистра, выход которого соединен с третьей группой входов первого блока элементов ИЛИ, четвертая группа входов которого подключена к выходу пятого блока элементов И, вход первого элемента НЕ соединен с выходом больше узла сравнения, выход первого элемента ИЛИ подключен к входу управле 1385131ния записью блока памяти, выход второго элемента ИЛИ соединен со счетным входом третьего счетчика, выход шестого блока элементов И подключен к первому информационному входу узла сравнения, первый информационный вход блока микропрограммного управления соединен с выходом четвертого элемента И, выход первого блока элементов ИЛИ соединен с информационным входом блока памяти и вторым информационным входом узла сравнения, адресный выход блока микропрограммного управления подключен к первой группе входов второго блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти, выход которого является выходом устройства, пятый и шестой выходы опроса блока микропрограммного управления подключены к первому и второму входам считывания блока задания порогов и к первому и второму управляющим входам коммутатора, третий управляющий вход которого соединен с выходом Выбор канала блока микропрограммного управления, седьмой выход опроса которого подключен к третьему входу считывания блока задания порогов, выход которого соединен с вторым информационным входом блока сравнения, тактовый вход которого подключен к восьмому выходу опроса блока микропрограммного управления, девятый выход опроса которого соединен с тактовым входом преобразователя напряжение - код, выход которого подключен к третьему информационному входу блока сравнения, вход преобразователя напряжение - код соединен с выходом коммутатора, первый, второй и третий информационные входы которого подключены соответственно к выходу интегратора и к прямому и инверсному выходам блока детекторов, вход которого соединен с выходом блока переключения постоянной времени интегрирования, выход третьего счетчика подключен к второй группе входов второго блока элементов ИЛИ, третьи входы которых подключены к входу задания адресной константы устройства,5 1 О 15 20 25 30 35 40 тактовый вход устройства соединен с входом управления записью блока памяти.2. Устройство по п. 1, отличающееся тем, что блок сравнения содержит четыре группы элементов ИЛИ, два регистра, узел сравнения, группу элементов НЕ, четыре группы элементов И, первые входы элементов ИЛИ первой группы являются первой группой информационных входов блока сравнения, вторая группа информа. ционных входов которого соединена с вторыми входами элементов ИЛИ первой группы,. выходы которых подключены к разрядным входам первого регистра, выход которого соединен с первым информационным входом узла сравнения и первыми входами элементов И первой и второй групп, вторые входы которых объединены с первыми входами элементов И третьей и четвертой групп и с тактовым входом узла сравнения и подключены к тактовым входом блока сравнения, второй информационный вход узла сравнения объединен с вторыми входами элементов И четвертой группы и вторыми входами элементов И третьей группы и соединен с разрядными выходами второго регистра, разрядные входы которого подключены к выходам элементов ИЛИ второй группы, первые и вторые входы элементов ИЛИ которой являются третьей и четвертой информационными группами входов блока, третьи входы элементов И второй и третьей групп соединены с выходом группы элементов НЕ, входы которой объединены с третьими входами элементов И первой и четвертой групп и подключены к выходу узла сравнения, который является выходом Больше блока, выходы элементов И первой и третьей групп соединены с первыми и вторыми входами элементов ИЛИ третьей группы соответственно, выходы которого являются первыми информационными выходами блока, выходы элементов И второй и четвертой групп подключены к первым и вторым входам элементов ИЛИ четвертой группы, выходы которой являются вторыми выходами блока.

СмотретьЗаявка

4035077, 11.03.1986

ПРЕДПРИЯТИЕ ПЯ Г-4152

ГУСЕВ АНДРЕЙ ВАДИМОВИЧ, КОЗЛОВСКИЙ БОЛЕСЛАВ ВЛАДИСЛАВОВИЧ, ХМЕЛЬНИК ИЛЬЯ БОРИСОВИЧ, ШТЕРЕНБЕРГ ЮРИЙ ОВСЕЕВИЧ

МПК / Метки

МПК: G06G 7/52

Метки: вычисления, моментов, нормированных, процессов, случайных, статистических

Опубликовано: 30.03.1988

Код ссылки

<a href="https://patents.su/12-1385131-ustrojjstvo-dlya-vychisleniya-normirovannykh-statisticheskikh-momentov-sluchajjnykh-processov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления нормированных статистических моментов случайных процессов</a>

Предыдущий патент: Устройство для определения канала с экстремальным напряжением

Следующий патент: Светодиодный матричный плоский экран

Случайный патент: Сталь