Регенератор двоичных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1185630

Авторы: Красковский, Семенов

Текст

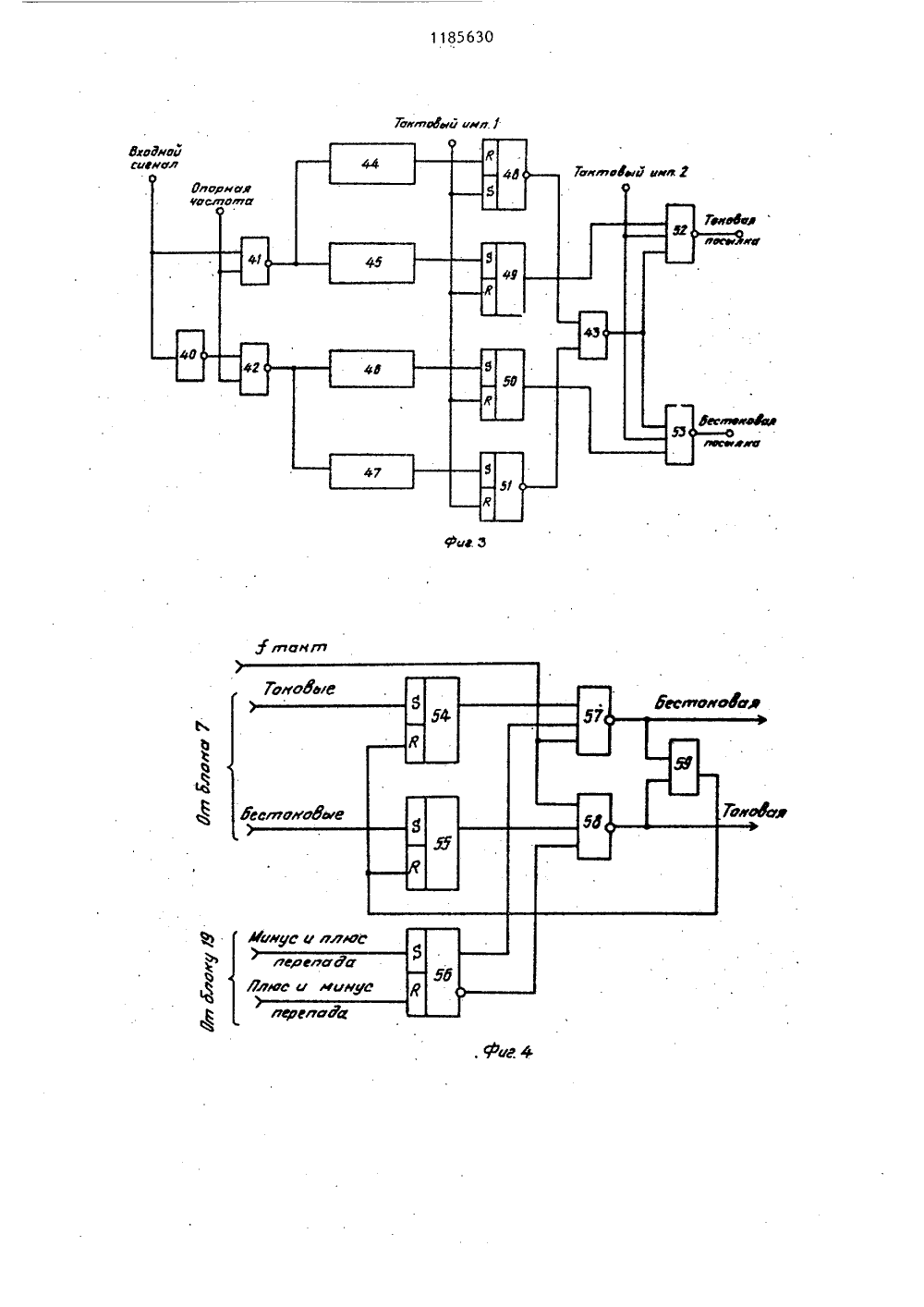

(72) А.Е. Красковский и А.А. Семенов (7 1) Ленинградский ордена Ленина институт инженеров железнодорожного транспорта им. акад, В,Н. Образцова (53) 621.394.662(088.8)(56) Авторское свидетельство СССР У 743211, кл. Н 04 1. 7/02, 1977.Авторское свидетельство СССР 9 995346, кл. Н 04 Е 7/02, 198 1. (54)(57) РЕГЕНЕРАТОР ДВОИЧНЫХ СИГНАЛОВ, содержащий последовательно соединенные блок регистрации, первый блок задержки, первый блок коммутации и выходной блок, выход которого является выходом регенератора, последовательно соединенные первый анализирующий блок, первый блок памяти, первый блок сравнения и первый решающий блок, к третьему и четвертому входам которого подключены выходы второго блока задержки, последовательно соединенные блок выделения тактовых интервалов без дроблений, блок оченки и формирователь зоны анализа, а также анализатор дроблений, выделитель фронтов сигнала, второй анализирующий блок, первый вход которого объединен с первыми входами блока регистрации, первого анализирующего блока, блока определения знака перепада, вьщелителя фронтов сигнала и блока фазирования, выход которого через формирователь сигнала опорных частот подключен к первому входу блока выделения тактовых интервалов без дроблений, вторым входам выделителя фронтов сигнала блока регистрации, первого и второго аналиэи рующих блоков и четвертому входу фор мирователя зоны анализа, выход которого подключен к первому входу анализатора дроблений и второму входу блока определения знака перепада, выходы которого через последовательносоединенные второй блок памяти и второй блок сравнения подключены к входам второго блока задержки, при этомвыходы первого анализирующего блокачерез второй блок коммутации подключены к третьему и четвертому входампервого блока сравнения, а к третьему и четвертому входам второго блокасравнения подключены через третийкоммутатор выходы блока определения знака перепада, к третьему входу ко торого, а также к вторым входам бл ка формирования, блока выделения та товых интервалов без дроблений и ан лизатора дроблений подключен выход выделителя фронтов сигнала, причем выход анализатора дроблений подключен к третьему входу второго блока памяти, а выход второго анализирующего блока подключен к третьим входам второго и третьего блоков коммутации, четвертые входы которых объединены, о т л и ч а ю щ и й с я тем,что, с целью повышения точности регенерации двоичных сигналов, введеныпоследовательно соединенные третийблок сравнения, третий блок задержки,второй решающий блок и элемент ИЛИ,последовательно соединенные блок регистрации знакоперемен,третий блок памяти;четвертый блок сравнения, четвертыйблок задержки и третий решающий блок,атакжеделитель, четвертый блок комму 11856301185630 Авенир Составитель Г, Лерантовичедактор М. Митейко Техред .Мигунова Корректор М.Максимишинец Заказ 644 иал ППП "Патент", г. Ужгород, ул. Проектная 0 ТиВНИИПИ Госупо делам и 113035, Москва,аж 668арственного комобретений и откЖ, Раушская Подписитета СССРытийаб., д. 4/1185630 тации и пятый блок сравнения, к входам которого подключены выходы второго блока коммутации и первого блокапамяти, а выходы пятого блока сравнения подключены к третьему и четвертому входам второго решающего блока,при этом выходы первого и третьегорешающих блоков подключены к входамэлемента ИЛИ, первый выход которогоподключен к четвертым входам второгои третьего блоков коммутации, а второй, третий и четвертый, выходы элемента ИЛИ подключены к третьему, четвертому и пятому входам первого блока коммутации, выходы второго блокапамяти подключены к первому и второму входам третьего блока сравнения,к третьему входу которого и второмувходу четвертого блока сравнения подключен;. выход четвертого блока коммутации, первый и второй входы которого объединены с третьим;и четвертымвходами третьего блока коммутации, ак третьему входу четвертого блокакоммутации подключен выход блока регистрации знакоперемен, к первому ивторому входам которого подключенысоответственно выход выделителя Фрон. Изобретение относится к области радиотехники и предназначено для использования в аппаратуре передачи данных и в качестве автономного устройства в системах связи.Цель изобретения - повышение точности регенерации двоичных сигналов,Ба Фиг. 1 представлена структурпая электрическая схема регенератора двоичных сигналов; на фиг. 2 - схема блока регистрации; на фиг, 3 -схема первого анализирующего блока; на фиг, 4 - схема первого решающего блока; на фиг, 5 - схема второго анализирующего блока; на Фиг. 6 - схема блока выделения тактовых интерваловбез дроблений; на фиг, 7 - схема блока оценки; на фиг. 8 - схема формиро вателя зоны анализа; на фиг. 9 - схема выделителя фронтов сигнала; на фиг. 10 - схема анализатора дроблений; на фиг. 11 - схема блока опреде 5 10 15 20тов сигнала и первый выход формирователя зоны анализа, второй, третий ичетвертый выходы которого подключенык второму, третьему и четвертому входам блока оценки, а выход формирователя сигнала опорных частот подключен к входу делителя, первый выходкоторого подключен к третьему входупервого анализирующего блока, к четвертому входу которого, а также ктретьим входам блока регистрации,блока фазирования, первого блока задержки, первого блока памяти, второго анализирующего блока, второго блока памяти, второго и третьего блоковзадержки, выходного блока, анализатора дроблений, блока выделения тактовых интервалов без дроблений, блокарегистрации знакоперемен, вторым входам третьего блока памяти, четвертого блока задержки и третьего решающего блока и пятым входам первого и второго решающих блоков, пятого бло -ка сравнения, Формирователя зоныанализа подключен второй выход делителя, а выходы блока сравнения подключены к третьему и четвертому входам третьего решающего блока,гления знака перепада; на Фиг. 12схема решающего блока; на Фиг. 13схема третьего решающего, блока; нафиг. 14 - схема блока регистрациизнакоперемен,Регенератор двоичных сигналов содержит блок 1 регистрации, первыйблок 2 задержки, первый блок 3 коммутации, первый анализирующий блок 4,первый блок 5 памяти, второй блок 6коммутации, первый блок 7 сравнения,первый решающий блок 8, второй анализирующий блок 9, блок 10 выделениятактовых интервалов без дроблений,блок 11 оценки, формирователь 12 зоны анализа, выделитель 13 фронтовсигнала, блок 14 определения знакаперепада, третий блок 15 коммутации,анализатор 16 дроблений, второйблок 17 памяти, второй блок 18 сравнения, второй блок 19 задержки, выходной блок 20, блок 21 фазирования,формирователь 22 сигнала опорных частот, пятый блок 23 сравнения, второй решающий блок 24, элемент ИЛИ 25, третий решающий блок 26, третий блок 27 сравнения, третий блок 28 5 задержки, четвертый блок 29 коммутации, четвертый блок 30 задержки, блок 31 регистрации знакоперемен, четвертый блок 32 сравнения, третий блок 33 памяти, делитель 34, при этом блок 1 регистрации состоит из трех двухвходовых элементов И-НЕ 35, 36 и 37, счетчика 38 и 0-триггера 39, первый анализирующий блок 4 состоит из инвертора 40, трех двухвходовых элементов И 41, 42 и 43, четырех счетчиков 44 - 47, четырех КБ - триггеров 48 - 5 1, двух трехвходовых элементов И 52 и 53, первый решающий блок 8 состоит из трех КБ - триггеров 54, 55 и 56, двух трехвходовых элементов И-НЕ 57 и 58 и элемент ИЛИ 59, второй анализирующий блок 9 содержит инвертор 60, два трехвходовых элемента И 61 и 62, три счетчика 63,64 и 65, два КБ - триггера 66 и 67 и элемент ИЛИ 68, блок 10 выделения .тактовых интервалов без дроблений содержит 0-триггер 69, три счетчика 70., 71 и 72, два двухвходовых элемен та И 73 и 74, элемент ИЛИ 75, блок 11 оценки состоит из трех двухвходовых элементов И-НЕ 76, 77 и 78, четырех счетчиков 79 - 82, трех КБ - триггеров 83, 84 и 85, двухвходового элемента И 86, трехвходового элемента И 87, четырехвходового элемента И 88, формирователь 12 зоны анализа содержит счетчик 89, три коммутатора 90, 91 и 92, три элемента И-НЕ 93, 94 и 40 95, три двухвходовых элемента ИЛИ 96, 97 и 98, трехвходовой элемент И 99, три КБ - триггера 100, 101 и 102, выделитель 13 фронтов сигнала состоит из инвертора 103, двух трехвходовых 15 элементов И 104 и 105, элемента ИЛИ106, 0-триггера 107, анализатор 16 дроблений состоит из двух двухвходовых элементов И-НЕ 108 и 109, 0-триггера 110, блок 14 определения знака 50 перепада состоит из трех двухвходовых элементов И-НЕ 111, 112 и 113, инвертора 114, КБ - триггера 115,двухвходового элемента ИЛИ 116, второй решающий блок 24 состоит из четырех КБ - триггеров 117- 120, двух трехвходовых элементов И 12 1 и 122 и элемент ИЛИ 123, третий решающий блок 22 состоит из трех КБ - триггеров 124, 125 и 126, двух трехвходовыхэлементов И 127 и 128 и элемент ИЛИ 129, блок 31 регистрации знакоперемен состоит из двух двухвходовыхэлементов И-НЕ 130 и 131, КБ -триггера 132.Регенератор двоичных сигналов работает следующим образом.С помощью блока 21 фаэирования, формирователя 22 сигнала опорных частот и делителя 34 осуществлено фазирование тактовых импульсов по отношению к входному сигналу. Формирование зоны анализа производится следующим образом. В вьщелителе 13 фронтов сигнала создаются узкие импульсы в моментсмены знака посылок. Эти импульсы поступают на вход блока 10 выделения тактовых интервалов без дроблений, в котором они задерживаются на один тактовый период с помощью счетчиков 1 или 2. На выходе блока 10 выделениятактовых интервалов без дробленийформируются узкие импульсы (фронты),которые поступают на первый вход блока 11 оценки. На остальные входы этого блока поступают зоны с различной длительностью. Поэтому в зависи- мости от дисперсии флуктуации фронтовна одном из выходов блока 11 оценки появляется сигнал, который поступает на вход формирователя 12 зоны анализа и устанавливает один из КБ - триггеров 100, 101 и 102 в единичное состояние. С помощью этих триггеров осуществляется выбор соответствующегоимпульса (зоны), который появляется на выходе трехвходового элемента И 99.При поступлении сигнала на вход блока 1 регистрации, работа которого основана по принципу интегральной регистрации,. в нем производится определение знаков приходящих посыпок.Сигнал о знаке посылок, задержанный на два тактовых периода в первом блоке 2 задержки, подается на вход блока 3 коммутации.Одновременно с регистрацией знака всех поступающих на вход посылок в блоке 1 регистрации, осуществляется определение знака малоискаженных посыпок в первом анализирующем блоке 4.При этом считается, что посылка малоискажена, если в тактовом периоде втечение 0,7имеет место однополярная часть посылки. В этом случае отработает только один счетчик 44 илий 1, и запрета на формирования сигналов о знаке посылки не будет. Таккак рассматривается случай, когдапервоначально приходит малоискаженная посылка, то с помощью счетчика 45или 46 определяется знак посылки, исигнал о знаке посылки с выхода трехвходовых элементов И 52 или 53 поступает на вход первого блока 5 памяти и хранится в памяти блока в течение двух тактовых интервалов и затем подается на входы первого 7 ипятого 23 блоков сравнения.Допустим, что в следующем тактовом 15периоде поступает сильнодробленнаяпосылка, Тогда на выходе второго ана-.лизирующего блока 9 формируется сигнал, который показывает, что в данном тактовом интервале присутствовали дробления посылки с суммарной длительностью более 307. от всей длительности посылки. При этом запомнилисьсчетчики 63 и 64. Сигнал с выходавторого анализирующего блока 9 пере -ключает второй, третий и четвертыйблоки 6,15 и 29 коммутации в положение, разрешающее прохождение сигналов через эти блоки.С помощью блока 14 определения 30знака перепада производится определение знака перепада в зоне анализа,сформированной с помощью блоков 10и 11 и формирователя 12 зоны анализа,причем временное положение последней 35зоны соответствует началу сильнодробленной посылки. Сигнал о знаке перепада с выхода блока 14 определениязнака перепада поступает на вход второго блока 17 памяти, в котором храиится в течение одного тактового периода,Если в зоне анализа, следующей засильнодробленной посылкой, отсутствует знакоперепад, то на выходе блока 3145регистрации знакоперемен формируетсясигнал, который через четвертый блок29 коммутации поступает на третийвход третьего блока 27 сравнения. Кмоменту поступления этого сигнала на 50втором входе блока 27 присутствуетсигнал о знаке перепада переднегофронта сильнодробленной посылки. Врезультате логической обработки входных сигналов на выходе третьего блока 5527 сравнения формируется сигнал ознаке сильнодробленной посылки. Этотсигнал задерживается в третьем блоке 28 задержки на один такт, в течение которого регистрируется знак малоискаженной посылки в первом анализирующем блоке 4. Сигнал о результате регистрации с выхода первого анализирующего блока 4 через второй блок 6 коммутации поступает на третий и четвертый входы первого блока 7 сравнения и третий и четвертый входы пятого блока 23 сравнения. Так как рассматривается случай поступления разнополярных малоискаженных посылок, сигнал на выходе первого блока 7 сравнения отсутствует, а на выходе пятого блока 23 сравнения появляется сигнал о знаке малоискаженной посылки следующей за сильнодробленной, который поступает на третий и четвертый входы второго решающего блока 24. Поэтому в конце тактового интервала, следующего эа сильнодробленной посылкой, на входах второго решающего блока 24 присутствуют сигналы о знаке перепада первого фронта сильнодробленной посылки и о знаке малоискаженной посылки, которая следует за сильнодробленной. Если знак перепада соответствует знаку малоискаженной посылки, то во втором решающем блоке 24 принимается решение о знаке сильнодробленной посылки и вырабатывается сигнал, который через элемент ИЛИ 25 поступает на соответствующий вход первого блока 3 коммутации, четвертые входы второго и третьего блоков 6 и 15 коммутации и первый вход четвертого блока 29 коммутации. Сигнал с выхода элемента ИЛИ 25 переключает блоки 6 и 15 и 29 коммутации в положение, запрещающее прохождение сигнала через эти блоки, Кроме того, сигнал с выхода элемента ИЛИ 25, выполненного на основе тактируемого триггера, поступает через первый блок 3 коммутации в выходной блок 20, При этом в первом блоке 3 коммутации производится запрет на прохождение сигнала от первого блока 2 задержки.Во втором случае сильнодробленная посылканаходится между слабоискаженньми или вообще неискаженными однополярными посылками, однако в зонах анализа, перед и после сильнодробленной посылки отсутствуют перепады от информационных фронтов. В такой ситуации можно предположить, что поступают три подряд однополярныепосылки и знак сильноискаженной посылки соответствует знаку неискаженных.В этом случае устройство работает следующим образом.При поступлении малоискаженной посылки в первом анализирующем блоке ч определяется ее знак, который запоминается в первом блоке 5 памяти в те О чение двух тактовых периодов. При отсутствии знакоперемены в концетактового периода в блоке 31 регистрации знакоперемен формируется сигнал, который поступает в третий 15 блок 33 памяти, В следующем тактовом . периоде поступает сильнодробленная посылка, поэтому во втором анализирую. щем блоке 9 формируется сигнал, который переключает первый, второй и 2 О четвертый блоки 3, 6 и 29 коммутации в положение, разрешающее прохождение сигналов через эти блоки. По оконча нии поступления сильнодробленной посылки при условии, что в зоне анализа отсутствует знакоперемена, в блоке 31 регистрации знакоперемен создается сигнал, который через четвертый блок 29 коммутации посылается в четвертый блок 32 сравнения. Таким об- ЗО разом, в конце второго тактового периода на входах четвертого блока 32сравнения появляются сигналы об отсутствии знакоперемен.В результате логической обработки З 5 сигналов в четвертом блоке 32 сравнения формируется импульс, который поступает на вход четвертого блока 30. задержки. В четвертом блоке 30 задержки импульс задерживается на один так О товый период, Если в этом тактовом периоде поступает малоискаженная посылка, сигнал о ее знаке подается с выхода первого анализирующего блока 4 через второй блок 6 коммутации на 45 третий и четвертый входы первого блока 7 сравнения, Первый блок 7 сравнения выносит решение о том, что знаки Малоискаженных посылок совпадают. Поэтому в первом блоке 7 сравнения вырабатывается сигнал, который поступает на первый и второй входы третье-. го решающего блока 26.Таким образом, к моменту оконча-, ния малоискаженной посылки в первом блоке 7 сравнения оказывается сформированным сигнал о знаках малоискаженных посылок. Кроме того, на выходе четвертого блока 30 задержки появляется сигнал об отсутствии энакоперемен в зоне анализа. Сигналы о знаках малоискаженных посылок и об отсутствии знакоперемен в зонах анализа поступают на соответствующие входы третьего решающего блока 26. На основании логической обработки этих сигналов в третьем решающем блоке 26 определяется знак сильнодроблен,ной посылки, причем этот знак соответствует знаку малоискаженных посылок. Сигнал с выхода третьего решающего блока 26 через элемент ИЛИ 25 подается на входы второго и третьего блоков 6 и 15 коммутации и первый вход четвертого блока 29 коммутации, которые переключаются в положение, запрещающее прохождение сигналов через эти блоки. Кроме того, сигнал с выхода элемента ИЛИ 25 через первый блок 3 коммутации поступает на вход выходЪного блока 20, в котором формируется регенерированная посылка. При этом в первом блоке 3 коммутации производится запрет на прохождение сигнала с выхода первого блока 2 задержки,Наличие двух фронтов в зоне анализа, что соответствует дроблению посылки, фиксируется в анализатор 16 дроблений.

СмотретьЗаявка

3776183, 19.07.1984

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА ИМ. АКАД. В. Н. ОБРАЗЦОВА

КРАСКОВСКИЙ АЛЕКСАНДР ЕВГЕНЬЕВИЧ, СЕМЕНОВ АНАТОЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H04L 7/02

Метки: двоичных, регенератор, сигналов

Опубликовано: 15.10.1985

Код ссылки

<a href="https://patents.su/12-1185630-regenerator-dvoichnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Регенератор двоичных сигналов</a>

Предыдущий патент: Пороговый декодер сверточного кода

Следующий патент: Устройство для синхронизации опорного колебания широкополосного демодулятора

Случайный патент: Устройство для рентгенографии