Устройство для моделирования сетевых графов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

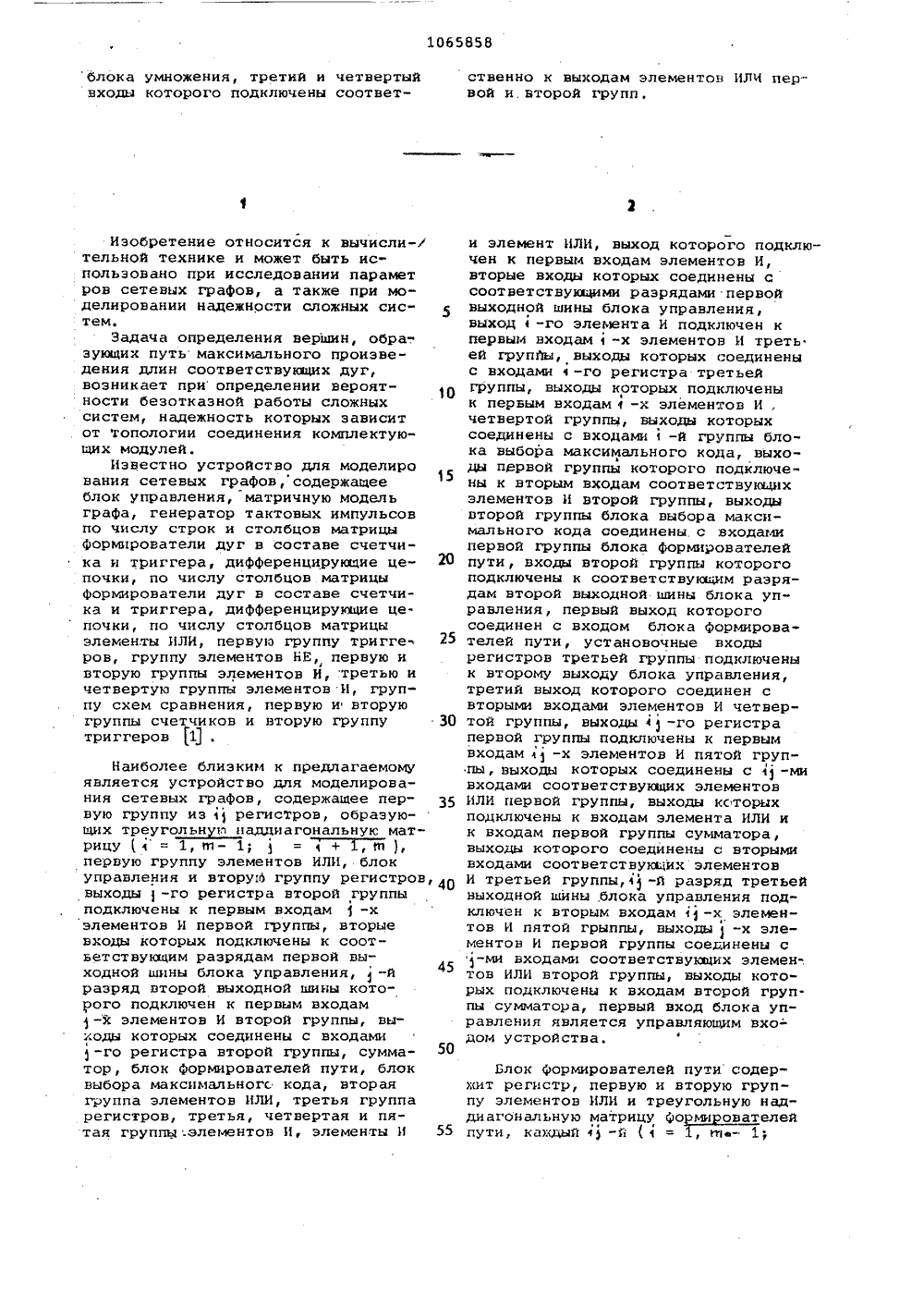

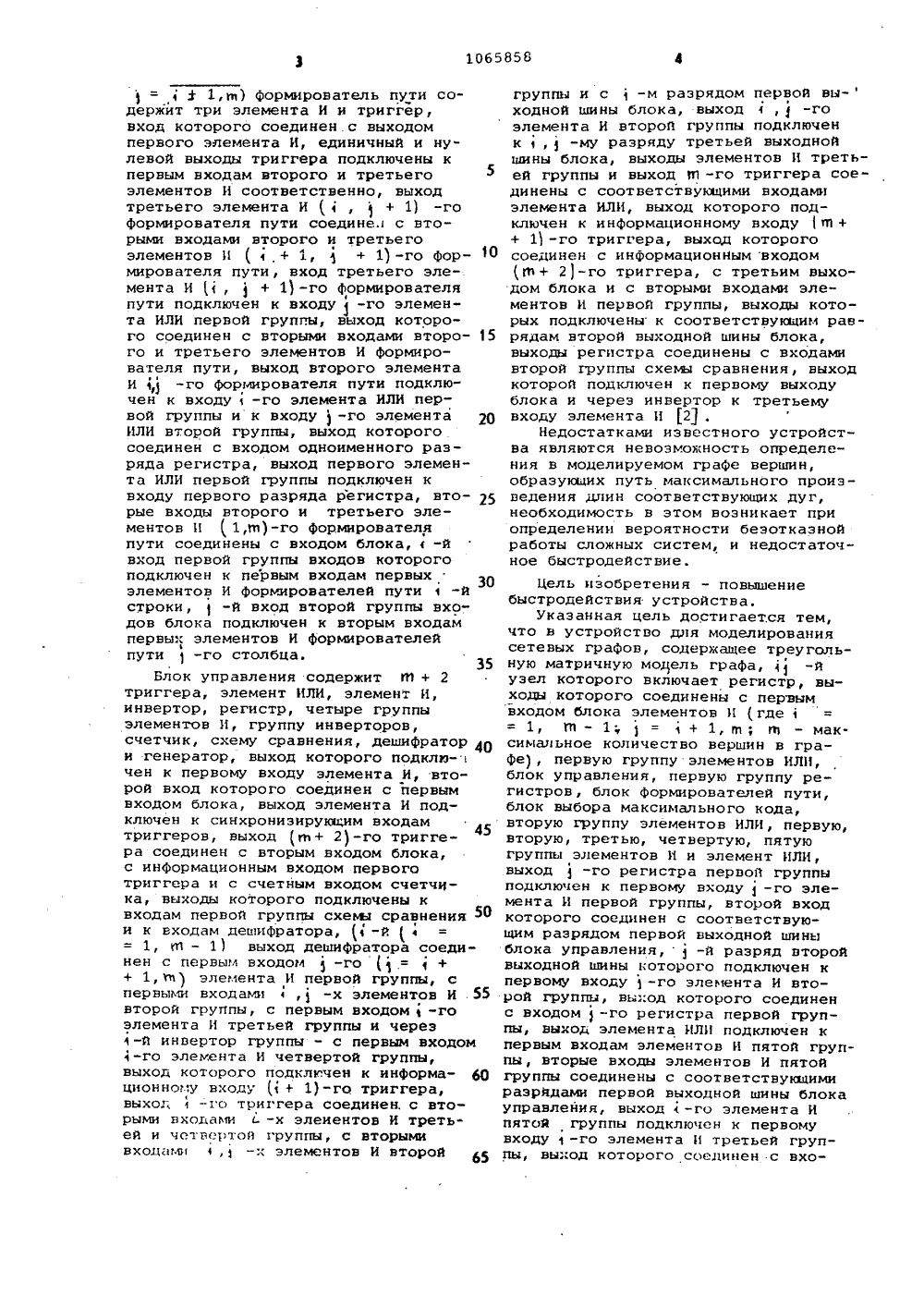

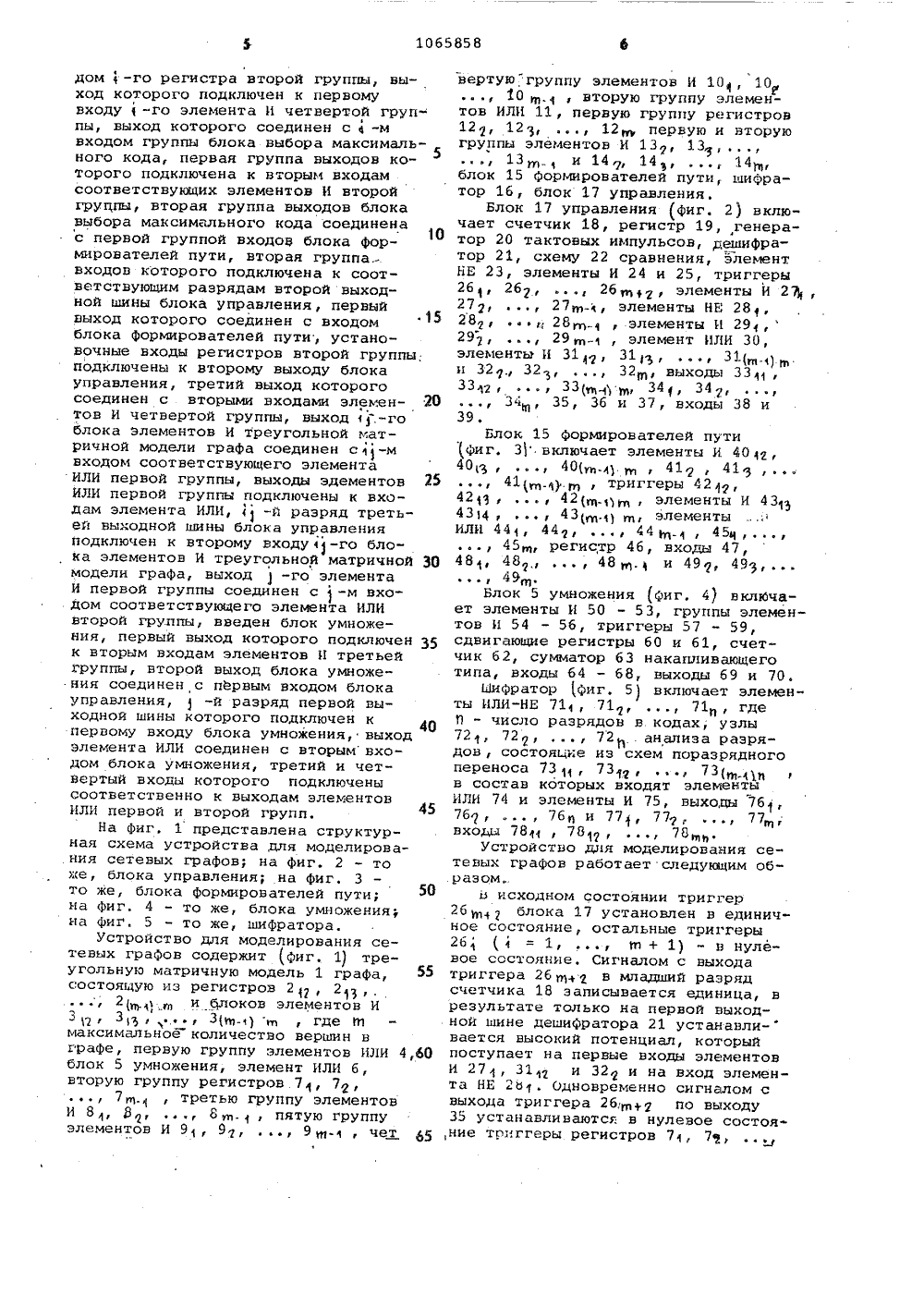

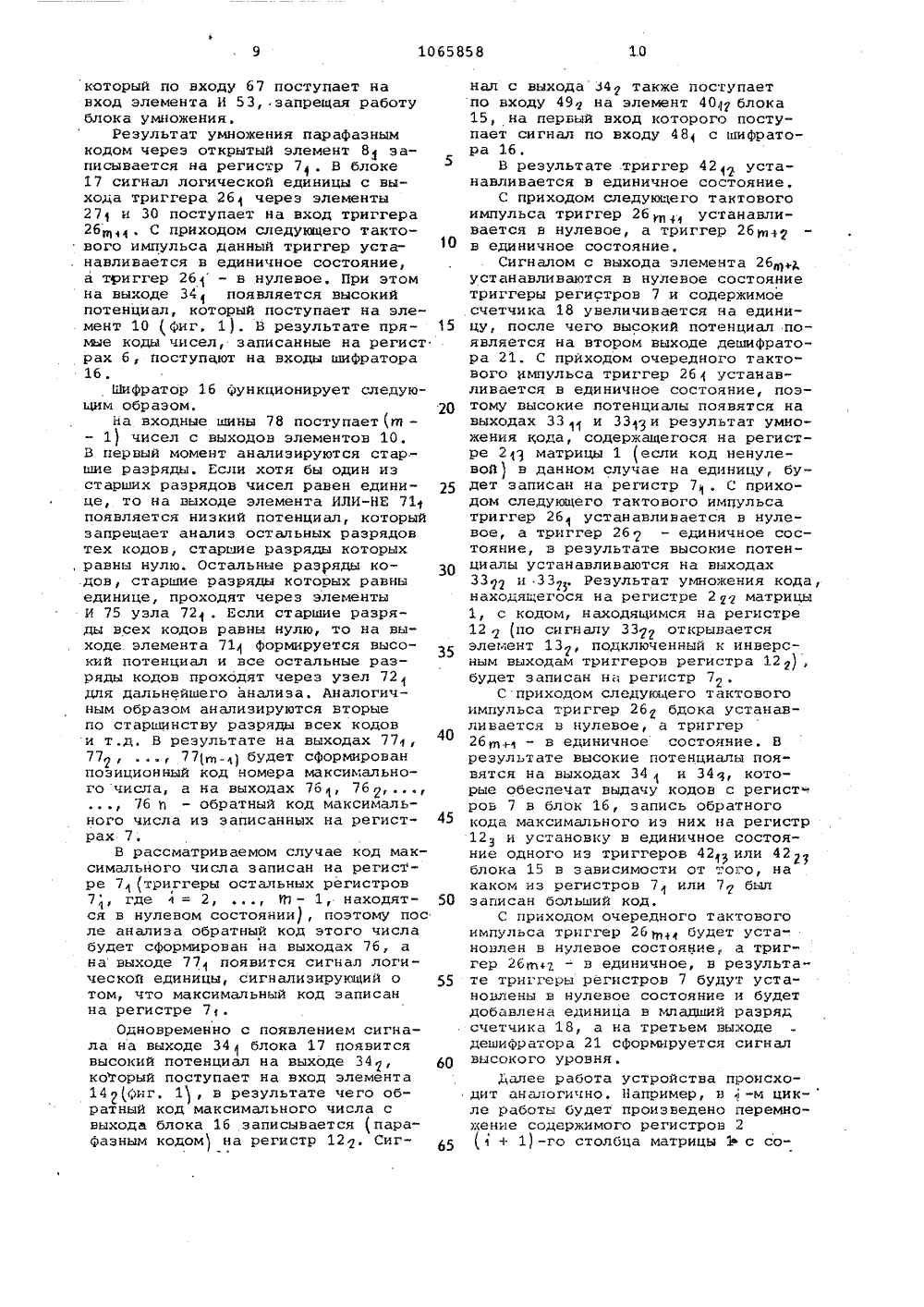

(1% Ш) 315 В С 06 Р 15/20 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТМЙ 21 ) 3411698/18-2422 ) 24.03. 82(56) 1. Авторское свидетельство СССРР 842842, кл, 0 06 0 7/122, 1981.2, Авторское свидетельство СССРпо заявке Р 3341571/24,кл. а 06 г 15/20, 1981 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВА-:НИЯ СЕТЕВЫХ ГРАФОВ, содержащеетреугольную матричную модель графа,1 -и Узел которой включает регистр,выходы которого соединены с первымвходом блока элементов И 1,гдеа - 1, 1 = +,Г,максимальное количество вершин вграФе), первую группу элементовИЛИ, блок управления, первую группурегистров, блок Формирователей пути, блок выбора максимального кода,вторую группу элементов ИЛИ, первую,вторую, третью, четвертую, пятуюгруппы элементов И и .элемент ИЛИ,выход 1 -го регистра первой группыподключен к первому входу 1-го элемента И первой группы, второй входкоторого соединен с соответствующим разрядом первой выходной шиныблока управления,-й разряд второйвыходной шины которого подключен кпервому входу 1 -го элемента И второй группы, выход которого соединенс входом 1-го регистра первой группы, выход элемента ИЛИ подключен кпервым входам элементов И пятойгруппы, вторые входы элементов Ипятой группы соединены с соответствукщими разрядами первой выходнойшины блока управления, выход-гоэлемента И пятой группы подключенк первому входу-го элемента Итретьей группы, выход которого соединен с входом 1 -го регистра второй группы, выход которого подключен к первому входу 1 -го элемента И четвертой группы, выход которого соединен с 1 -м входом группы блока выбора максимального кода, первая группа выходов которого подключена к нторым входам соотнетстнующих элементов И второй группы, вторая группа выходов блока выбора максимального кода соединена с первой группой вхоДов блока Формирователей пути, вторая группа входоь которого подключена к соответствующим разря. - .: дам второй выходной шины блока управления, первый выход которого соединен с входом блока формирователей пути, .устаноночные входы регист ров второй группы подключены к второму выходу блока управления, третий выход которого соединен с вторымй входами элементов И четвертой группы, выход 1) -го блока элементов И треугольной матричной модели граФа соединен с 11 -и входом соответствующего элемента ИЛИ первой группы, выходы элементов ИЛИ первой группы подключены к входам элемента ИЛИ,11 -и разряд третьей выходной шины блока управления подключен к второму входу 11 -го блока элементов И треугольной матричной модели графа, выход 1 -го элемента И первой группы ;соединен с 1 -м входом соответствующего элемента ИЛИ второй группы, отличающееся тем, что, с целью повышения быстродействия, в него введен блок умножения, первый выход которого подключен к вторым входам элементов И третьей группы, второй выход блока умножения соединен с первым входом блока управления, 1 -й разряд первой выходной шины которого подключен к первому входу блока умножения, выход элемента ИЛИ соединен с вторым входом1065858Составитель И.ДубининаРедактор СКвятковская Техред Т. Маточка Корректор А.ТяскоЭакаэ 11047/50 Тираж Об Подписное ЭНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, 11 осква, У:.-35, Раушская наб., д. 4/5 филиал ППП "Патент", г, Ужгород, ул. Проектная, 410 б 5858 55 блока умножения, третий и четвертыйвходы которого подключены соответИзобретение относится к вычисли-Гтельной технике и может быть использовано при исследовании параметров сетевых графов, а также при моделировании надежности сложных систем.Задача определения вершин, обра-.зующих путь максимального произведения длин соответствукщих дуг,возникает при определении вероятности безотказной работы сложныхсистем, надежность которых зависитот топологии соединения комплектующих модулей,Известно устройство для моделирования сетевых графов, содержащееблок управления, матричную модельграфа, генератор тактовых импульсовпо числу строк и столбцов матрицыФормирователи дуг в составе счетчика и триггера, дифференцирующие цепочки, по числу столбцов матрицыФорьиронатели дуг в составе счетчика и триггера, дифференцирующие це.почки, по числу столбцов матрицыэлементы ИЛИ, первую группу триггерон, группу элементов НЕ, первую ивторую группы элементов И, третью ичетвертую группы элементов И, группу схем сравнения, первую и вторуюгруппы счетчиков и вторую группутриггеров 1 . Наиболее близким к предлагаемому является устройство для моделирования сетевых графов, содержащее пер" вую группу из 1 регистров, образуюанх треугольнуо надднагональнуе матраца ) ) = 1,- 1; 1 =ье ), первую группу элементов ИЛИ, блок управления и втору)б группу регистров, выходы-го регистра второй группы подключены к первым входам 1 -х элементов И первой группы, вторые входы которых подключены к соотьетстнующим разрядам первой выходной шины блока управления,-й разряд второй выходной шины которого подключен к первым входам-х элементон И второй группы, выходы которых соединены с входами-го регистра второй группы, сумматор, блок Формирователей пути, блок выбора максимальногс кода, вторая группа элементон ИЛИ, третья группа регистров, третья, четвертая и пятая групп .элементов И, элементы И 10 15 20 25 30 35 40 45 50 ственно к выходам элементов ИЛЧ первой и. второй групп. и элемент ИЛИ, выход которого подключен к первым входам элементов И,вторые входи которых соединены ссоответствуи)цими разрядами первойвыходной шины блока управления,выход-го элемента И подключен кпервым входам-х элементов И третьей групйы, выходы которых соединеныс входами-го регистра третьейгруппы, выходы которых подключенык первым входам-х элементов И,четвертой группы, выходы которыхсоединены с входами-й группы блока выбора максимального кода, выходы первой группы которого подключены к вторым входам соответстнуюцихэлементов и второй группы, выходывторой группы блока выбора максимального кода соединены с входамипервой группы блока формирователейпути, входы второй группы которогоподключены к соответствующим разрядам второй выходной шины блока управления, первый выход которогосоединен с входом блока Формирователей пути, установочные входырегистров третьей группы подключенык второму выходу блока управления,третий выход которого соединен свторыми входами элементов И четвертой группы, выходы 4 -го регистрапервой группы подключены к первымвходам-х элементов И пятой группы, выходы которых соединены с-мивходами соответствующих элементовИЛИ первой группы, выходы кс торыхподключены к нходам элемента ИЛИ ик входам первой группы сумматора,выходы которого соединены с вторымивходами соответствующих элементонИ третьей группы, -й разряд третьейвыходной шины, блока управления подключен к вторым входам-х элементов И пятой грыппы, выходы-х элементов И первой группы соединены с-ми входами соответствуицих элементов ИЛИ второй группы, выходы которых подключены к входам второй группы сумматора, первый вход блока управления является управляющим вхо-дом устройства,Блок Формирователей пути содержит регистр, перную и вторую группу элементов ИЛИ и треугольную наддиагональную матрицу Фо ми ователей ПУТИ, Ка 1 дьДЫй Э -й (=, )а1,э) Формирователь пути содержит три элемента И и триггер,вход которого соединен.с выходомпервого элемента И, единичный и нулевой выходы триггера подключены кпервым входам второго и третьего5элементов И соответственно, выходтретьего элемента И (,+ 1) -гоформирователя пути соедине. с вторыми входами второго и третьегоэлементов И,+ 1, ) + 1) -го Формирователя пути, вход третьего элемента И ,+ 1) -го Формирователяпути подключен к входу 1 -го элемента ИЛИ первой группы, выход которого соединен с вторыми входами второго и третьего элементов И Формирователя пути, выход второго элементаИ 1,) -го формирователя пути подключей к входу 1 -го элемента ИЛИ первой группы и к входу 1 -го элемента 2 ОИЛИ второй группы, выход которогосоединен с входом одноименного разряда регистра, выход первого элемента ИЛИ первой группы подключен квходу первого разряда регистра, вторые входы второго и третьего элементов И1,е)-го Формирователяпути соединены с входом блока,-йвход первой группы входов которогоподключен к первым входам первыхэлементов И форьирователей пути 1 -йстроки, ) -й вход второй группы входов блока подключен к вторым входампервых элементов И формирователейпути ) -го столбца.Блок управления содержит й 1 + 2триггера, элемент ИЛИ, элемент И,инвертор, регистр, четыре группыэлементов И, группу инверторов,счетчик, схему сравнения, дешифратор 4 Ои генератор, выход которого подключен к первому входу элемента И, вто"рой вход которого соединен с первымвходом блока, выход элемента И подключен к синхронизируюцим входамтриггеров, выход е + 2)-го триггера соединен с вторым входом блока,с информационным входом первоготриггера и с счетным входом счетчнка, выходы которого подключены квходам первой группы схемы сравнения 5 Ои к входам дешифратора, 1 -й1, Ф - 1) выход дешифратора соединен с первым входом 1 -го 1 = 1 +-го элемента И четвертой группы,выход которого подключен к информационному входу1)-го триггера,выход-го триггера соединен. с вторыми входами-х элеиентов И третьей и четвертой группы, с вторымивходами , -х элементов И второй 65 группы и с 1 -м разрядом первой выходной шины блока, выход (,-го элемента И второй группы подключен к 1,-му разряду третьей выходной шины блока, выхоцы элементов И третьей группы и выход П -го триггера соединены с соответствующими входами элемента ИЛИ, выход которого подключен к информационному входу (п 3 + + 1) -го триггера, выход которого соединен с информационным входом Ф+ 2-го триггера, с третьим выходом блока и с вторыми входами элементов И первой группы, выходы которых подключены к соответствуюцим раврядам второй выходной шины блока, выходы регистра соединены с входами второй группы схемы сравнения, выход которой подключен к первому выходу блока и через инвертор к третьему входу элемента И 2) .Недостатками известного устройства являются невозможность определения в моделируемом графе вершин, образующих путь максимального произведения длин соответствующих дуг, необходимость в этом возникает при определении вероятности безотказной работы сложных систем, и недостаточное быстродействие.Цель изобретения - повышение быстродействия устройства.Указанная цель достигается тем, что в устройство для моделирования сетевых графов, содержащее треугольную матричную моЕ)ель графа,-й узел которого включает регистр, выходы которого соединены с первым входом блока элементов И (где 11, п 1 - 1 1 = 1 + 1, в; в - максимальное количество вершин в граФе), первую группу элементов ИЛИ, блок управления, первую группу регистров, блок формирователей пути, блок выбора максимального кода, вторую группу элементов ИЛИ, первую, вторую, третью, четвертую, пятую группы элементов И н элемент ИЛИ, выход-го регистра первой группы подключен к первому входу 1 -го элемента И первой группы, второй вход которого соединен с соответствующим разрядом первой выходной шины блока управления,-й разряд второй выходной шины которого подключен к первому входу 1 -го элемента И второй группы, выод которого соединен с входом-го регистра первой группы, выход элемента ИЛИ подключен к первым входам элементов И пятой группы, вторые входы элементов И пятой группы соединены с соответствукицими разрядами первой выходной шины блока управления, выход-го элемента И пятой группы подключен к первому входу 1 -го элемента И третьей группы, выод которого соединен с вхо 1065858дом -го регистра второй группы, выход которого подключен к первомувходу-го элемента И четвертой группы, выход которого соединен с-мвходом группы блока выбора максимального кода, первая группа выходов которого подключена к вторым входамсоответствующих элементов И второйгруцпы, вторая группа выходов блокавыбора максимального кода соединенас первой группой входоц блока формирователей пути, вторая группа.входов которого подключена к соответствующим разрядам второй выходной шины блока управления, первыйвыход которого соединен с входомблока формирователей пути, установочные входы регистров второй группы,подключены к второму выходу блокауправления, третий выход которогосоединен с вторыми входами злементов И четвертой группы, выход ,-гоблока элементов И треугольной матричной модели графа соединен с-мвходом соответствующего элементаИЛИ первой группы, выходы эдементов 25ИЛИ первой группы подключены к входам элемента ИЛИ, 1 -и разряд третьей выходной шины блока управленияподключен к второму входу -го блока элементов И треугольной матричной 30модели графа, выход-го элементаИ первой группы соединен с-и входом соответствующего элемента ИЛИвторой группы, введен блок умножения, первый выход которого подключен 35к вторым входам элементов И третьейгруппы, второй выход блока умножения соединен с первым входом блокауправления,-й разряд первой выходной шины которого подключен кпервому входу блока умножения, выходэлемента ИЛИ соединен с вторым входом блока умножения, третий и четвертый входы которого подключенысоответственно к выходам элементовИЛИ первой и второй групп,На фиг, 1 представлена структурная схема устройства для моделирования сетевых графов; на фиг. 2 - тоже, блока управления; на Фиг, 3то же, блока формирователей пути;на фиг. 4 - то же, блока умножения;на фиг. 5 - то же, шифратора,Устройство для моделирования сетевых графов содержит ,Фиг. Ц треугольную матричную модель 1 графа,состоящую из регистров 2, 22 п,1и волоков элементов И3, 3 п 11гдемаксимальное количество вершин вграфе, первую группу элементов ИЛИ 4,60блок 5 умножения, элемент ИЛИ б,вторую группу регистров 7, 7,7 щ. , третью группу элементовИ 8, д.8., пятую группуэлементов И 9, 9, , 9 щ-, чет 65 вертую группу элементов И 10, 10,10 п 1 вторую группу элементов ИЛИ 11, первую группу регистров12, 123.12 п первую и вторуюгруппы элементов И 13, 13.13 р и 14 , 14 , , 14 п,блок 15 Формирователей пути, шифратор 16, блок 17 управления,Блок 17 управления фиг. 2) включает счетчик 18, регистр 19, генератор 20 тактовых импульсов, дешифратор 21, схему 22 сравнения, элементНЕ 23, элементы И 24 и 25, триггеры26, 262, , 26 щ, элементы И 27,272, , 27 п 1 , элементы НЕ 28,28 р е ц 28 тэлементы И 29,297. , 29 п , элемент ИЛИ 30,элементы и 31 , 3131и 32 р 323, , 32 п, выходы 33,33 у33 п 1 пр 3434 234, 35, Зб и 37, входы 38 и39.Блок 15 Формирователей пути,Фиг. З включает элементы И 40,40 д, , 40 д,.1 , 41 д, 4141 п п, триггеры 42 А,42342 о,.п, элементы И 43431443 щ.,1 т, элементыИЛИ 44, 44 , , 44 п , 4545 и, регистр 46, входы 47,48, 48 48 п.и 49, 49,ау 49 п,Блок 5 умножения Фиг. 4 включает элементы И 50 - 53, группы элементов И 54 - 56, триггеры 57 - 59,сдвигающие регистры 60 и 61, счетчик 62, сумматор 63 накапливающеготипа, входы 64 - 68, выходы 69 и 70.шифратор ,Фиг. 5) включает элементы ИЛИ-НЕ 71, 71, , 71 п, гдеП - число разрядов в кодах, узлы72, 72, , 72 анализа разрядов, состоящие из схем поразрядногопереноса 73 , 73, , 73в состав которых входят элементыИЛИ 74 и элементы И 75, выходы 76,7 бф 7 с .ю 7 бп и 77 77 у г фвходы 78, 78 .70.Устройство для моделирования сетевых графов работает следующим об.разомо исходном состоянии триггер26блока 17 установлен в единичное состояние, остальные триггеры26= 1, , в + 1) - в нулевое состояние. Сигналом с выходатриггера 26 п+в младший разрядсчетчика 18 записывается единица, врезультате только на первой выходной шине дешифратора 21 устанавли-вается высокий потенциал, которыйпоступает на первые входы элементовИ 27, 31 и 322 и на вход элемента НЕ 28. Одновременно сигналом свыхода триггера 26,п,+у по выходу35 устанавливаются в нулевое состояние триггеры регистров 7, 7, 73 1065858хода триггера 57 высокий потенциал по выходу 70 подается на вход 38 45 блока 17 фиг. 2) и на вход тригге" ра 58, который находится в единичном состоянии. С выхода триггера 58 высокий потенциал подается на тре-, тий вход элемента 53 и на группы 50 .элементов И 54 и 56.Высокий потенциал с выхода 33 блока 17 поступает по входу 68, в результате чего записывается единица в старший разряд регистра 61 и . 55 высокий потенциал поступает также на второй вход элемента И 53. По .сигналу с выхода 33,ц код, записанный на регистре 242 (если он нулевой, поступает по входу 64 и через откры 60 тый элемент И 56 записывается на регистр 60. С выхода элемента 6 вы" сокий потенциал поступает на вход67 и через элемент И 53 устанаалива- ется в единичное состояние триггер 65 7, . На регистр 19 блока 17 записывается код числа вершин в моделируемом графе, на регистры 2,ц, 2 й2 л.111 л матрицы 1 записываются коды весов" соответствующих дуг графа, Если дуги между какими-либо верыинамю графа отсутствуют, то на соответствующих регистрах записаны коды нуля. Триггеры регистра 46 блока 15 установлены в нулевое состояние,Устройство начинает работу после подачи входного сигнала по шине 39 блока 17. Этот сигнал через элемент И 25 поступает навторой вход элемента И 24, и тактовые импульсы с выхода генератора 20 поступают на входы триггеров 26. С приходом первого импульса триггер 26 устанавливается в единичное состояние, при этом на выходе 33 4 появляется высокий потенциал, который поступает на вход элемента И 91, а с выхода 332 высокий потенциал поступает на входы группы 3, В результате код с регистра 2 через открытую группу Зц, группу элементов ИЛИ 4 пос-. тупает на вход блока 5 и подается также на вход элемента 6, В зависимости от содержимого регистра 2 у нана выходе элемента 6 формируетсявысокий или низкий потенциал, запрещакиций или разрешающий работу блокаумножения н запись на регистры 7 результатов умножения, Если код нарегистре 2 у ненулевой, то на выходе элемента б формируется высокий потенциал, и наоборот.Блок 5 умножения функционирует следующим образом,В исходном состоянии триггер 57 находится в нулевом состоянии. С прямого выхода этого триггера низкий потенциал подается на второйвход элемента И 52. С инверсного вы 153540 57, С инверсного выхода этого триггера низкий потенциал подается навход триггера 58 и по выходу 70поступает на вход 38 блока 17, а спрямого выхода высокий потенциал подается на первый вход элемента И 52.Следукщий тактовый импульс с генератора 20 по выходу 37 блока 17 посту"пает на вход 66 и через открытый элемент И 52 записывает единицу в счетчик 62, устанавливаеттриггер сосчетным входом 59 в единичное состояние, а триггер 58 - в нулевое состояние, с выхода которого нулевой потенциал подается на третий вход элемента И 53. С прямого выхода триггера 59 высокий потенциал подается навход элементов И 50 н 51,На второй вход элемента И 50 подается высокий потенциал с триггерастаршего разряда регистра множителя61. На выходе элемента И 50 появля"ется. высокий потенциал, поступакщийна элемент И 55, Иножнмое, находящееся на регистре 60, через открытыйэлемент И 55 поступает на вход сумматора 63, где происходит сложениекодов. На первый и второй входыэлемента И 51 поступают сигналы свторого по старшинству триггерарегистра 61 и нулевого триггерарегистра 60. Если эти триггерыбудут находиться в единичном состоянии, то с выхода элемента И 51 вдополнительный разряд сумматоразаписывается единица. С приходомследующего тактового импульса к со;держимому счетчика 62 приставляетсяединица и триггер 59 устанавливается в нулевое состояние. С инверсного выхода этого триггера высокийпотенциал поступает в цепи сдвигагеристров 60 и 61, причем содержимое регистра 60 сдвигается на одинразряд в сторону младших разрядов,а содержимое регистра 61 - в сторону старших разрядов. Умножение продолжается до приходал+ 1)-готактового импульса, при этом навыходе счетчика 62 появляется едини-ца переполнения. Данный сигнал устанавливается в нулевое состояниетриггер 57 и подается в дополнительный разряд сумматора 63 для округления результата умножения. С прямого выхода триггера 57 низкий потенциал подается на второй входэлемента И 52, а с инверсного выходаэтого элемента высокий потенциалподается на вход триггера 58 и повыходу 70 поступает на вход 38 блока 17, тем саьым разрешая тактовымимпульсам через элемент 24 проходитьв блок 17 управления.Если код, считываемый с регистра2 ц 2 нулевой, то на выходе элемента6 формируется сигнал низкого уровня, 1065858который по входу 67 поступает на вход элемента И 53, запрещая работу блока умножения.Результат умножения парафазным кодом через открытый элемент 8 записывается на регистр 7 . В блохе 17 сигнал логической едйницы с выхода триггера 261 через элементы 27 и 30 поступает на вход триггера 26 щ,. С приходом следующего тактового импульса данный триггер устанавливается в единичное состояние, а триггер 26 - в нулевое. При этомна выходе 341 появляется высокий потенциал, который поступает на элемент 10 фиг, 1). В результате пря мые коды чисел, записанные на регист рах 6, поступают на входы шифратора 16.шифратор 16 Функционирует следуюцим образом. 20На входные шины 78 поступает(я -1) чисел с выходов элементов 10, В первый момент анализируются старшие разряды. Если хотя бы один из старших разрядов чисел равен едини це, то на выходе элемента ИЛИ-НЕ 711 появляется низкий потенциал, который запрещает анализ остальных разрядов тех кодов, старшие разряды которых , равны нулю. Остальные разряды ко О дов, старшие разряды которых равны единице, проходят через элементы И 75 узла 72, Если старшие разряды всех кодов равны нулю, то на выходе. элемента 71 формируется высокий потенциал и все остальные разряды кодов проходят через узел 72 для дальнейшего анализа, Аналогичным образом анализируются вторые по старшинству разряды всех кодов и т.д. В результате на выходах 77, 4 О77 в-) будет сформирован позиционный код номера максимального числа, а на выходах 76, 76 76 п - обратный код максимального числа из записанных на регист рах 7.В рассматриваемом случае код максимального числа записан на регист- ре 7(триггеры остальных регистров 7, где= 2, , В - 1, находят ся в нулевом состоянии, поэтому пос ле анализа обратный код этого числа будет сформирован на выходах 76, а на выходе 774 появится сигнал логической единицы, сигнализирующий о 55 том, что максимальный код записанна регистре 7.Одновременно с появлением сигнала на выходе 34 блока 17 появитсявысокий потенциал на выходе 34, 60 который поступает на вход элемента 14 фиг, 1, в результате чего обратный код максимального числа с выхода блока 16 записывается параФазным кодом) на регистр 122, Сигнал с выхода 34 также поступаетпо входу 49 на элемент 40, блока15, на первый вход которого поступает сигнал по входу 48 с шифратора 16.В результате триггер 42 12 устанавливается в единичное состояние.С приходом следующего тактовогоимпульса триггер 26устанавливается в нулевое, а триггер 26.в единичное состояние.Сигналом с выхода элемента 26,п+устанавливаются в нулевое состояниетриггеры регистров 7 и содержимоесчетчика 18 увеличивается на единицу, после чего высокий потенциал появляется на втором выходе дешифратора 21. С приходом очередного тактового импульса триггер 26 устанавливается в единичное состояние, поэтому высокие потенциалы появятся навыходах 331 и 3343 и результат умножения кода, содержащегося на регистре 2 матрицы 1 (если код ненулевой) в данном случае на единицу, будет записан на регистр 7 . С приходом следующего тактового импульсатриггер 261 устанавливается в нулевое, а триггер 267 - единичное состояние, в результате высокие потенциалы устанавливаются на выходах332 и 33. Результат умножения кода,находящегося на регистре 2матрицы1, с кодом, находяцимся на регистре12 2 по сигналу 3322 открываетсяэлемент 13, подключенный к инверсным выходам триггеров регистра 12),будет записан н регистр 72,С приходом следующего тактовогоимпульса триггер 26 бдока устанавливается в нулевое, а триггер26 р,+ - в единичное состоячие. Врезультате высокие потенциалы появятся на выходах 34и 34, которые обеспечат выдачу кодов с регистров 7 в блок 16, запись обратногокода максимального из них на регистр12 и установку в единичное состояние одного из триггеров 421 или 422блока 15 в зависимости от того, накаком из регистров 71 или 7 былзаписан больший код,С приходом очередного тактовогоимпульса триггер 26 л будет уста"новлен в нулевое состояние а триггер 26 е 2 - в единичное, в результате триггеры регистров 7 будут уста"новлены в нулевое состояние и будетдобавлена единица в младший разрядсчетчика 18, а на третьем выходедешифратора 21 сформируется сигналвысокого уровня.Далее работа устройства происходит аналогично. Например, в-м цик-ле работы будет произведено перемно"жение содержимого регистров 2держиьым регистров 12 у, 123 12 (содержимое регистра 2 ( 1 м) умножается на единицу), далее будет определено максимальное произведение и обратный код его будет записан на регистр 12;.ц, а один из триггеров 42, 422 , 42блока 15 будет установлен в единич-с ное состояние.Работа устройства продолжается аналогичным образом.до тех пор, пока содержимое счетчика 18 не станет равным коду, записанному на регистре 19. В этом случае на выходе схемы 22 появляется высокий потенциал, а на выходе элемента НЕ 23 - низкий, поэтому импульсы с генератора 20 перестанут поступать на входы триггеров 26. Сигнал с выхода схемы 22 является сигналом опроса блока 15 для определения максимального пути. Этот сигнал с выхода 36 поступает по входу 47 блока 15 (фиг. 3) на входы элементов 41 щ н 43. Единичные выходы триггеров 42 соединены с, первыми входами элементов И 41, а нулевые выходы " с первыми входами элементов И 43. Таким образом, если триггер 42 установлен в единичное состояние, то соответствукюдий ему элемент 41 открыт, а элемент 43 закрыт, и наоборот. Сигнал опроса с входа 47 проходит через открытые элементы 4343 д, 43 , т.е, сначала опрашиваются триггеры щ-го столбца блока 15, пока не будет найден триггер 42 ш, установленный вединичное состояние, у котОрогозакрыт элемент 43 и открыт элемент 41 . Высоким потенциалом свыхода элемента 41 через элементИЛИ 45 будет установлен в единичноесостоянием-й триггер регистра 46.Это означает, что 3 Ъ-я вершина моделируемого графа входит в максимальный путь, и через элемент 44(1 -1) -йсигнал опроса пройдет на опрос ( -- 1 -го столбца блока 15, т.е. поступит на вторые входы элементов41( - 1) и 43- 1). Если же вВ-м столбце матрицы 15 ни один иэ 15 триггеров 42 не будет находиться вединичном состоянии, то высокийпотенциал с выхода элемента 43(н-цчерез элемент 44 е.1) поступит наопрос (ю - 1 -го столбца, т.е. пос тупит на вторые входы элементов41 , и 43( . Аналогичнымобразом опрос будет продолжаться дотех пор, пока не будет найден триггер 42 , установленный в единичное 25 состояйие. Это означает, что-йвершин в первую вершину сформированмаксимальный путь. В этом случае будут установлены в единичное состоя"ние-й и первый триггеры регистра46, что свидетельствует об окончании работы устройства. Предлагаемая совокупность блоков и связей между ними позволила повысить точность моделирования.

СмотретьЗаявка

3411698, 24.03.1982

ВОЕННАЯ ОРДЕНА ЛЕНИНА, ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОРДЕНА СУВОРОВА АКАДЕМИЯ ИМ. Ф. Э. ДЗЕРЖИНСКОГО

ТИТОВ ВИКТОР АЛЕКСЕЕВИЧ, БАЖЕНОВ СЕРГЕЙ МИХАЙЛОВИЧ, ЛЕВАШОВ ВЛАДИМИР КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06F 15/173

Метки: графов, моделирования, сетевых

Опубликовано: 07.01.1984

Код ссылки

<a href="https://patents.su/12-1065858-ustrojjstvo-dlya-modelirovaniya-setevykh-grafov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования сетевых графов</a>

Предыдущий патент: Сигнатурный анализатор

Следующий патент: Устройство для определения технологических параметров периода доводки в мартеновской печи

Случайный патент: Сборная станция метрополитена колонного типа