Устройство для дифференцирова-ния частоты следования импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 798881

Автор: Чистяков

Текст

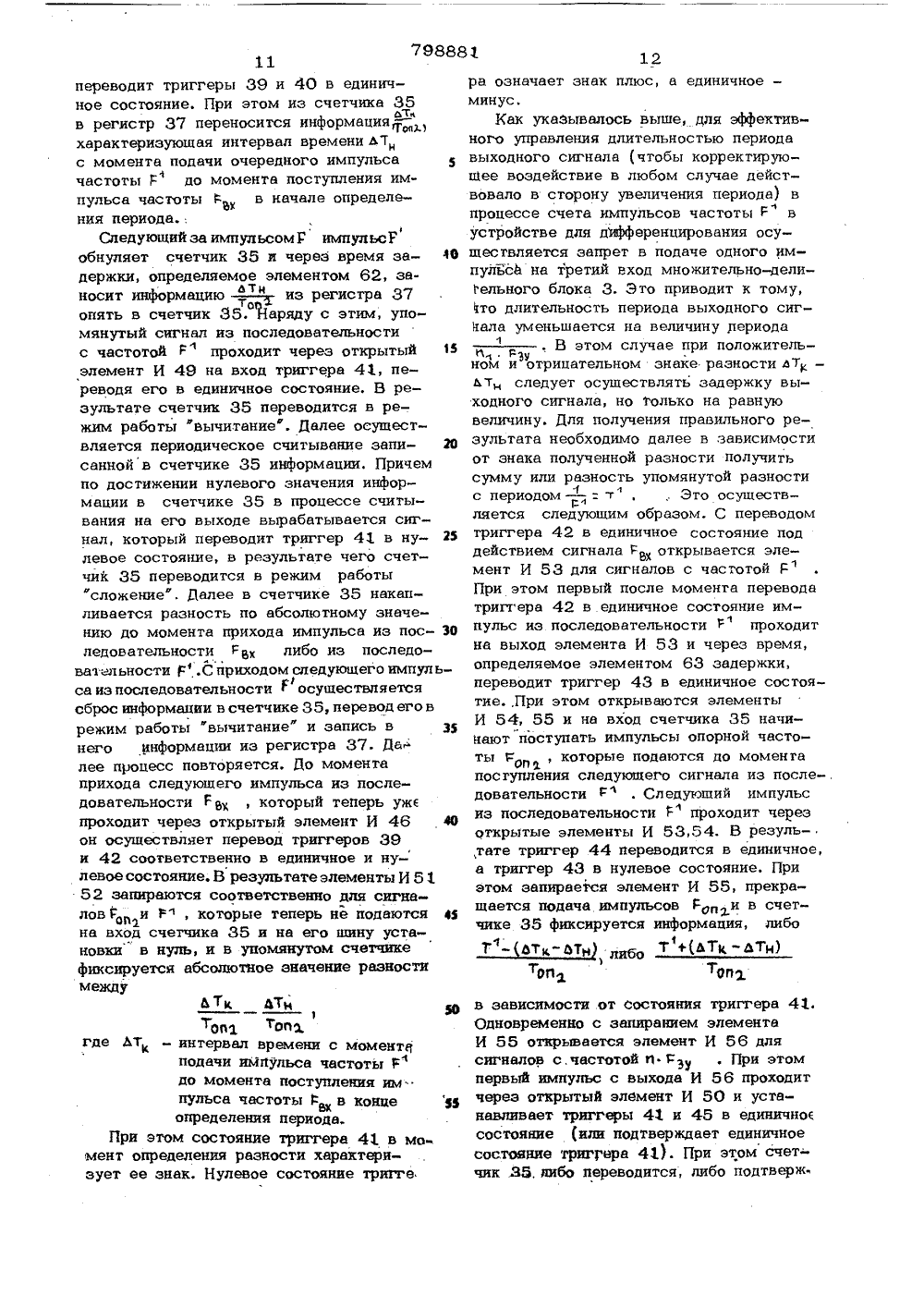

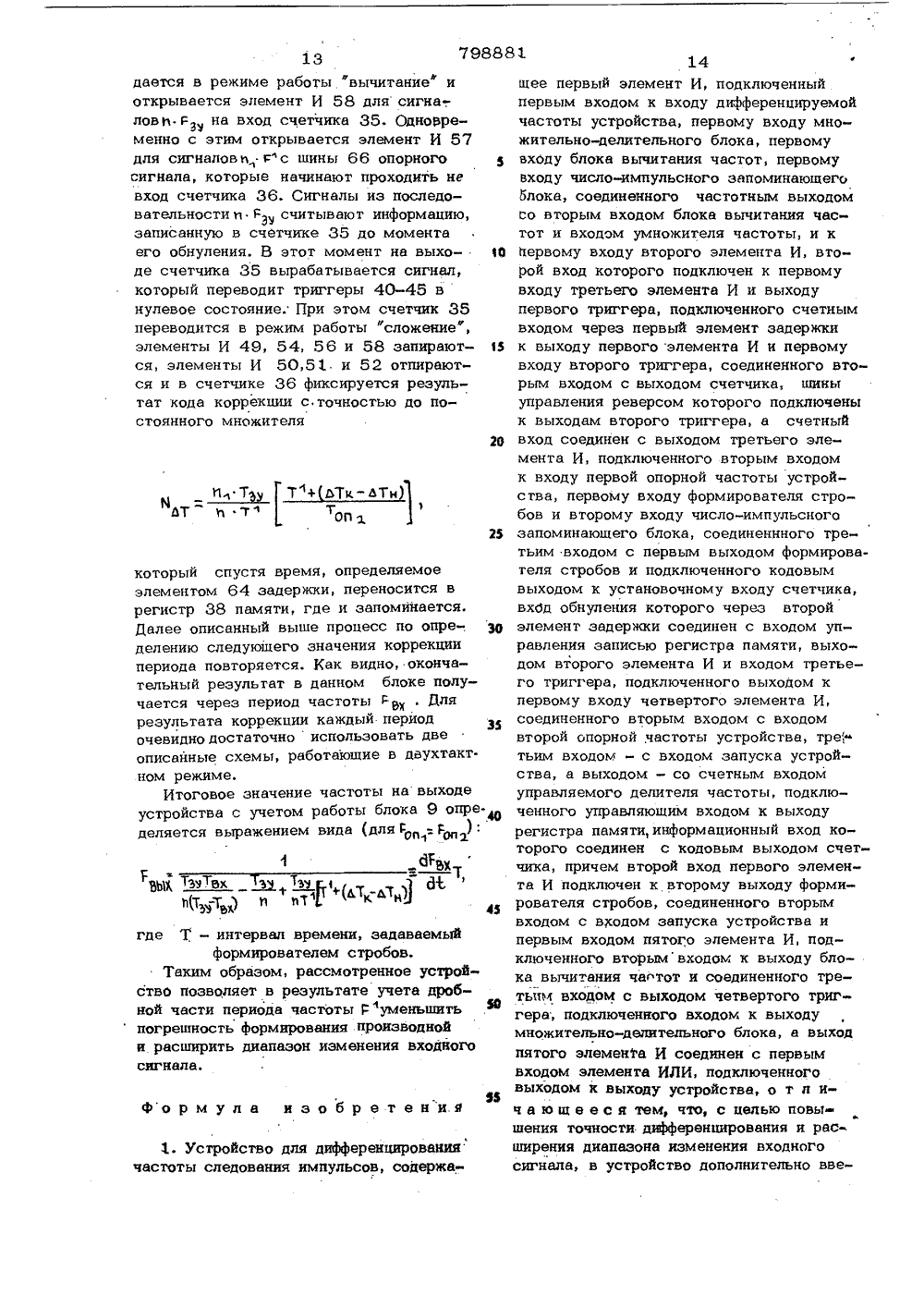

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциалистически кРеспублик(51) М. Кл. С 06 6 7/18 Государственный комитет СССР .до делам изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ДИффЕРЕНЦИРОВАНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВИзобретение относится к автоматике и:вычислительной технике, в частности к устройствам обработки информации, представленной в частотно-импульсной форме.Известно дифференцирующее устройство,5 содержащее блок выделения разности периодов, блок возведения в куб, элемент И и счетчик импульсов 13.Известно также двференцирующеео устройство, содержащее генератор импульсов, счетчик, блок управления, блок вычитания, группы элементов И и управляемые делители частоты 21.Недостатками известных устройств являются пониженная, точность и ограниченный диапазон изменения входного сигнала.Наиболее близким по технической сущности является устройство для дифференцирования частоты следования импульсов, содержащее первый элемент И, подключенный первым входом к входу дифференцируемой частоты, первому входу множительно 2целительного блока, первому входу блока вычитания частот, первому входу число-импульсного запоминающего блока, соединенного частотным выходом со вто- . рым входом блока вычитания частот и входом умножителя частоты, и к первому входу второго элемента И, второй вход которого подключен к первому входу тре,тьего элемента И и выходу первого триггера, подключенного счетным входом через первый элемент задержки к выходу первого элемента И и первому входу второго триггера, соединенного вторым входом с выходом счетчика, шины управления реверсом которого подключены к выходам второго триггера, а счетный вход соединен с выходом третьего элемента И, подключенного вторым входом к входу первой опорной частоты, первому входуформирователя стробов и второму входу число-импульсного .запоминающего блока, соединенного третьим входом с первым выходом формирователя стробов и подключенного кодовым выходом к уста 798883.3 7988новочному входу счетчика, вход обнуления которого через второй элемент задержки соединен с входом управления за.писью регистра памяти, выходом второгоэлемента И и входом третьего триггера,Подключенного выходом к первому входучетвертого элемента И, соединенногоруорым входом с входом второй опорнойчастоты, третьим входом - с входом запуска устройства, а выходом .- со счетным входом. управляемого делителя частоты, подключенного управляющим входом к выходу регистра, памяти, информационный вход которого соединен с кодовым выходом счетчика, причем второй Ивход первого элемента И подключен квторому выходу формирователя стробов,соединенного вторым входом с входомзапуска устройства и первым входом пятяго элемента И, подключенного вторым 26входом к выходу блока вычитания частоти соединенного третьим входом с выходомчетвертого триггера, подключенного входом к выходу множительно-делительногоблока, а выход пятого элемента И сое Юдинен с первым входом элемента ИЛИ,подключенного выходом к выходу устройства и соединенного вторым входом с выходом множительно-делительного блока,второй вход которого подключен к выходу умножителя частоты, а третий входсоединен с выходом управляемого делителя частоты 3,Недостатками известного устройства являются низкая точность и ограниченный диа- Зназон изменения входного сигнала, Это обусловлено тем, что при увеличении значенияпроизводной увеличивается разность периодов, фиксируемая за один цикл вычисления в счетчике, что приводит к уменьше анию частоты. следования импульсов натретьем входе множительно-делительногоблока и повышению погрешности дискретности.Целью изобретения является повышение 4точности дифференцирования и расширениедиапазона изменения входного сигнала.Цель достигается тем, что в устройство для дифференцирования частотыследования импульсов, содержащее первыйэлемент И, подключенный первым входомк входу дифференцируемой частоты устройства, , первому входу множительно-делительного блока, первому входу блокавычитания частот, первому входу числоимпульсного запоминающего блока, .соединенного частотным выходом со вторымвходом блока вычитания частот и входомумножителя частоты, и к первому входу 8 4второго элемента И, второй вход которого подключен к первому входу третьегоэлемента И и выходу первого триггера,подключенного счетным входом черезпервый элемент задержки к выходу первого элемента И и первому входу второго триггера, соединенного вторым входомс выходом счетчика, шины управления реверсом которого подключены к выходамвторого триггера, а счетный вход соеди- .нен с выходом третьего элемента И, подКлюченного вторым входом к входу первой опорной частоты устройства, первомувходу формирователя стробов и второмувходу число-импульсного запоминаюш егоблока, соединенного третьим входом спервым выходом формирователя стробови подключенного кодовым выходом к установочному входу счетчика, вход обнуления которого через второй элементзадержки соединен с входом управлениязаписью регистра памяти, выходом второгоэлемента И и входом третьего триггера,подключенного выходом к первому входучетвертого элемента И, соединенноговторым входом с входом второй опорнойчастоты устройства, третьим входом - свходом запуска устройства, а выходомсо счетным входом управляемого делителя частоты, подключенного управляюшимвходом к выходу регистра памяти, информационный вход которого соединен скодовым выходом счетчика, причем второйвход первого элемента И подключен квторому выходу формирователя стробов,соединенного вторым входом с входомзапуска устройства и первым входом пятого элемента И, подключенного вторымвходом к выходу блока вычитания частоти соединенного третьим входом с выходом четвертого триггера, подключенноговходом к выходу множительно-делительного блока, а выход пятого элемента Исоединен с первым входом элемента ИЛИ,подключенного выходом к выходу устройства, дополнительно введены блок задержки, блок сдвига фазы, элемент запрета и блок управления коррекцией, подключенный первым входом к входу дифференцируемой частоты устройства, вторымвходом - к выходу умножителя частоты ипервому входу блока сдвига фазы, третьим входом - к входу второй опорнойчас готы усФройства, четвертым входам - квыходу управляемого делителя частотыи первому входу элемента запрета, авыходом - к первому входу блока задеожки, соединенного вторым входомс выходом множительно-делительногоблока и подключенного выходом к второму входу элемента ИЛИ и второму входу блока сдвига фазы, вьиод которого соединен со вторым входом множительно-делительного блока, подключенного третьим входом к выходу элемента. запрета, соединенного вторым входом с входом ди-, ференцируемой частоты.Кроме этого, блок управления коррекцией содержит первый и второй элемен-, ты И, соединенные первыми входами с первым входом блока управления коррекцией и подключенные вторыми входами к выходу первого триггера, соединенного первым входом с выходом второго элемента И, входом второго триггера и с первыми входами элементов И первой группы, подключенных вторыми входами к выходам разрядов первого счетчика и соединенных выходами с входами первого регистра памяти, выходы которого подключены к первым входам элементов.И второй группы, соединенных вторыми . входами с выходом первого элементазадержки и подключенных выходами к. входам разрядов первого счетчика, соединенного счетным входом с выходом элемента ИЛИ и подключенного входами управления реверсом к выходам третьего триггера, первый вход которого соединен с выходом первого счетчика и с первым входом третьего элемента И, а вторые входы третьего .триггера подключены к выходам четвертого и пятого элементов И, причем первый вход четвертого элемента И, соединенного вторым входом с выходом второго триггера, подключен к входу обнуленияпервого счетчика, входу первого элемента задержки и выходу шестого элемента И, соединенного первым входом с первым выходом четвертого. триггера и с первым входом седьмого элемента И и подключенного вторым входом к четвертому входу блока управления коррекцией и к первымвходам восьмого и девятого элементов И, а выход восьмого элемента И, соединенного вторым входом с вторым выходом четвертого триггера, подключен черезвторой элемент задержки к счетному входу пятого триггера, соединенного первым выходом с первым входом десятого и вторым входом девятого элементов И иподключенного вторым выходом к первым входам одиннадцатого и, двенадцатого элементов И причем второй вход один иадцатого элемента И, соединенного третьим входом со вторым входом блока управления коррекцией, подключен к цер вому выходу шестого триггера и к вторым входам третьего и двенадцатого элементов И, а выход третьего элемента И соединен с первыми входами четвертого, шестого и седьмого триггеров и с входом третьего элемента задержки, подключенного выходом к первым входам элементов И третьейгруппы, соединенных вторыми входами с выходами разрядов ( второго счетчика и подключенных выходами к входам второго регистра памяти, выходы которого соединены с выходом блока управления коррекцией, а вход второго счетчика подключен к выходу и двенадцатого элемента И, соединенноготретьим входом с шиной опорного сигнала, причем выход первого элемента И подключен к вторым входам первого и четвертого триггеров, выход девятого р элемента И соединен со вторым входом.шестого триггера, подключенного вторым выходом к третьему входу восьмого элемента И, а выход седьмого элемента И, соединенного вторым входом с третьим входом блока управления коррекцией и со в-орым входом десятого элемента И подключен к первому входу элемента ИЛИ, соединенного вторым входом с выходом цедятого элемента И и подключенног трещ тьим входом к выходу тринадцатого элемента И,1 первый вход.которого соединен с выхоДом одиннадцатого элемента И и с первым входом пятого элемента И, а второй вход тринадцатого элемента И подключен к первому выходу седьмого триггера, 35соединенного вторым выходом со вторымвходом пятого элемента И, подключенного выходом к второму входу седьмоготриггера.40На фиг. 1 изображена блок хема устройства для дифференцирования частоты следования импульсов, на фиг. 2 - блоксхема блока управления коррекцией.Устройство содержит счетчик 1, управляемый делитель 2 частоты,множительноделительный блок 3, умножитель 4 частоты, регистр 5 памяти, блок 6 вычитаниячастот, число-имцульсный запоминающийблок 7, формирователь 8 стробоа, блок 9управления коррекцией, блок 10 задержки,блок 11 сдвига фазы, элемент 12 запрета, первый, второ, третий и четвертыйтриггеры 13-3,6, с первого по пятый эле- менты И 17-23.; элемент ИЛИ 22, первыйи второй элементы 23, 24 задержки,вход 25 подачи диференцируемых частотно-импульсных сигналов, входы 26 и 2первой и второй опорных частот, вход 287 79888запуска устройства, выход 29 устройстваи первый, второй, третий и четвертыйвходы 30-33 и выход 34 блока 9 управления коррекцией, Возможный вариантреализации блока 9 управления коррекцией(фиг,2) содержит первый и второй счетчики 35, 36, первый и второй регистры37 38, с первого по седьмой триггеры39-45, с первого по тринадцатый элементы И 46-58, первую, вторую и третью группы элементов И 59-61, первый,второй и третий элементы 62-64 задержки, элемент ИЛИ 65 и шину 66 опорногосигнала.Устроиство для дифференцирования работает следующим образом,В исходном состоянии счетчики, регистр и триггеры обнулены. Работа устройства начинается с подачи сигнала запуска на вход 28 устройства. При этом 20формирователь 8 стробов начинает периодическую выработку сигналов на своихвыходах с периодом Т, которые подаютсяна вход элемента И 17 и на третий входчисло-импульсного запоминающего блока 7. 2Причем первый сигнал после запуска с выхода формирователя стробов 8 подаетсятолько на вход блока 7. С подачей указанного импульса на вход блока 7 поддействием первого же сигнала входной щдифференцнруемой последовательностичастотыв нем осуществляется записьи запоминание информации о периоде входной частоты в данный момент времени,а также преобразование запомненной ин- цформации в частоту следования импульсов,которые непрерывно подаются на входы,блока 6 вычитания частот и умножителя4 частоты, с выхода которого сигналыподаются на второй вход 31 блока 9управления коррекцией и на вход блока 11сдвига фазы. Следует отметить, что поскольку после подачи сигнала запускарезультирующая последовательность навыходе множительно-делительного: блока 3появляется с некоторой задержкой, то допоявления этой последовательности навход выходного элемента ИЛИ 22 подается через элемент И 2 З с выхода блока 6 вычитания частот последовательностьнеравномерной разностной частоты междувходной частотой Ги запомненной вблоке 7. При этом знак разности (производной) фиксируется на дополнительномвыходе блока 6. ,Управление подачейуказанной последовательности навыход устройства осуществляется сигналами с входа 28 и с выхода триггера 16,котовый запрещает прохождение сигналов 1 8с выхода блока 6 вычитания при появлении первого же сигнала на выходе множительно-делительного блока 3,Работа основного тракта дифференцирования осуществляется следующим образом. При подаче следующе о второгосигнала с выхода формирователя 8 стробов он подается на вход блока 7, а также на вход элемента И 17. При этомосуществляется выдача запомненной вблоке 7 информации в параллельном кодена счетчик 1 и запись в запоминающийблок 7 текущего значения периода частоты входных сигналов. В счетчике 1 осуществляется вычитание информации опериоде запомненной частоты и периодетекущего значения частоты.Это производится. следующим образом.Первый после момента подачи сигнала свыхода формирователя 8 стробов импульсвходной частоты, подаваемый на вход 25,проходит через элемент И 17 и черезэлемент 23 задержки на счетный входтриггера 13, переводя его из нулевогов единичное состояние. Очевидно, что приэтом сигнал не проходит на выход элемента И 18, так как отпирающий сигналтриггера 13 подается на его вход с задержкой за счет элемента 23 задержки.Одновременно сигнал с выхода элемента И 17 подается на вход триггера 14,переводя его в нулевое состояние, в результате чего счетчик 1 устанавливается в режим работы "вычитание, С переводом триггера 13 в единичное состояние отпирающий сигнал с его выхода подается на элемент И 18 и элемент И 19,При этом через элемент И 19 на входсчетчика 1 начинают подаваться сигналыопорной частоты Г пс входа 26, которые вычитаются из информации, записанной в счетчике 1. Поступление сигналов на вход счетчика 1 осуществляетсядо момента поступления следующего сигнала на вход 25. Этот сигнал проходитна выход элемента:И 18, переводя триггер 15 в единичное состояние, и черезвремя, определяемое элементом 23 задержки, переводит триггер 3.3 в нулевоесостояние. В результате прекращаетсяподача отпирающего напряжения на входэлемента И 4,9 и прекращается подачасигналов опорной частоты на вход счетчика 1. При этом в нем фиксируется информация, соответствующая разности периодов Твходной частоты Р и Гзапомненной частоты С . Одновременнов результате перевода трщтера 15 вединичное состояние .отпирается эле8881 10 где 9 79 мент И 20 для сигналов второй опорной частоты Р , которые начинают проходить на вход управляемого делителя 2 и на четвертый вход 33 блока 9.Следует отметить, что в счетчике всегда фиксируется абсолютное значение разности (по модулю). Если в процессе вычитания счетчик обнуляется, на его выходе вырабатывается сигнал, который подается на второй вход триггера 14, переводя его из нулевого в единичное состояние. В результате .счетчик 1 пе реводится из режима вычитания в режим сложения и накапливается разность по абсолютному значению.Число импульсов, зафиксированное в счетчике 1, определяется как где Т - период сигналов первой опорОПной частоты Со,После фиксирования информации о разности периодов в счетчике 1 под действием второго сигнала из последовательности входных сигналов (сигнвла с выходаэлемента И 18) информация, накопленнаяв счетчике 1 переписывается в регистр 5памяти, а счетчик 1 обнуляется.Процесс получения информации о разности двух периодов повторяется при периодической (с периодом Т) подаче сигналов с формирователя 8 стробов,Выходной код регистра 5 памятиуправляет коэффициентом деления дели-теля 2 частота следования импульсов на.выходе которого соответственно равнаОП 2ОИ р 1Ъ ьхДалее в множительно-делительном блоке 3 .осуществляется операция перемножения входной частоты Г нв предварительно умноженную на коэффициент б в умножителе 4 запомненную частоту Гзу (с выхода запоминающего блока 7) и де 1 ления этого произведения на частотуС этой целью на третий вход множи:-. тельно-делительного блока 3 через схему 1.2 запрета импульса и вход 33 блока 9 подаются сигналы с выхода делите; ля 2 (сигналы, характеризующие К" ). нв первый вход блока 3 и на вход ЗО блока 9 подаются сигналы входной чу ,.готы Гииа второй вход блока 3 подают ЗО 35 43 0 Я ся сигналы частоты Р , сдвинутыепо фазе в блоке 11. При этом сигналыс выхода умножителя 4 частоты подают-ся на вход 31 блока 9. Следует отметить, что подача одного из импульсовпоследовательности сигналов с выходаделителя 2 на третий вход множительноделительного блока 3 запрещается с помощью схемы запрета импульса, чтонеобходимо для осуществления коррекции периода выходного сигнала. Схема элемента запрета при этом может быть реализована на основе триггера и элемента задержки.Результирующая частота на выходе множительно-делительного блока 3 равнаОП Вх ЗИГ "Р Г2Сигналы с выхода блока 3 подаются нв второй вход блока 10 задержки на первый вход которого подаются сигналы с выхода 34 блока 9 управления коррекцией периода выходной частоты, которые определяют необходимую величину звдержки. Ьа выходе блока 10 формируются сигналы, характеризующие окончательный результат, которые через элемент ИЛИ 22 поступают нв выход 29 устройства, На выходе блока 11 сдвига фазы по сигналам с выхода блока 10 вырабатываются сдвинутые по фазе сигналы с частотойи Е Таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блоха 10 задержки, на выходе блока 10 имеют место сигналы, период которых изменен на величину, вырабатываемую в блоке 9 управления коррекцией.Работа блока 9 осуществляется сле. дующим образом.. Первый импульс частоты Р, подаваеВхМый на вход 30, проходит через элемент И 47 на первые входы группы элементов И 59. Сигналы опорной частоты Ропопчерез открытый элемент И 52 и элемент ИЛИ 65 проходят на вход счетчика 35, считающего в прямом направлении. С приходом каждого импульса частоты Р" с входа 33 он проходит через .открытый элемент И 51 на вход установки в нуль счетчика 35 и через элемент 62 задержки - на вторые входы группы элементов И 60. При этом. информация в счетчике 35 сбрасывается и затем подсчет импульсов осуществляется снова. Такой счет производится до момента прихода сигнала частотыкоторый через открытый элемент И 47 поступает ца первые входы гочты элементов И 59 и12 ра означает знак плюс, а единичное -минус,Как указывалось выше, для эффективного управления длительностью периодавыходного сигнала (чтобы корректируюШее воздействие в любом случае действовало в сторону увеличения периоде) в1процессе счета импульсов частоты Е вустройстве для дифференцирования осуществляется запрет в подаче одного импульса на третий вход множительно-делиельного блока 3, Это приводит к тому,1 то длительность периода выходного сигнала уменьшается на величину периода, В этом случае при положитель 1 3 уном и отрицательном знаке разности дТ -ЬТ, следует осуществлять задержку выходного сигнала, но только на равнуювеличину. Для получения правильного результата необходимо далее в зависимостиот знака полученной разности получитьсумму или разность упомянутой разностис периодом - : т", , Это осуществр 1ляется следующим образом. С переводомтриггера 42 в единичное состояние поддействием сигнала Готкрывается элемент И 53 для сигналов с частотой Г 1При этом первый после момента переводатриггера 42 в единичное состояние импульс из последовательностипроходитна выход элемента И 53 и через время,определяемое элементом 63 задержки,переводит триггер 43 в единичное состоятие.,При этом открываются элементыИ 54, 55 и на вход счетчика 35 начийают поступать импульсы опорной частоты Г которые подаются до моментаОПУ. "поступления следующего сигнала из после- .довательности " . Следующий импульсиз последовательности " проходит черезоткрытые элементы И 53,54. В резуль,тате триггер 44 переводится в единичное,а триггер 43 в нулевое состояние. Приэтом запирается элемент И 55, прекращается подача импульсов Го и в счетчике 35 фиксируется информация, либо7"- Атк- Атн либ т(АГК - Атн))1 ООЯ.времени с моментпульса частоты Р а поступления им тоты 1 в конце я периода.е триггера 41 в зности характерие состояние тркт в зависимости от состояния триггера 41.Одновременно с запиранием элементаИ 55 открывается элемент И 56 длясигналов с.частотой У 1 у . При этомпервый импульс с выхода И 56 проходитчерез открытый элемент И 50 и устанавливает триггеры 41 и 45 в единичносостояние (или подтверждает единичноесостояние триггера 43,). При этом счетчик Зб, либо переводится, либо подтверж. 1 опинтервалподачи имдо моментпульса часопределени где ЬТ При этом состояни мент определения ра зует ее знак. Нулево ма 11798881 переводит триггеры 39 и 40 в единичное состояние. При этом из счетчика 35ьт в регистр 37 переносится информация - характеризующая интервал времени ьТ с момента подачи очередного импульса частоты Г до момента поступления импульса частоты 1 в начале определеак ния периода.,Следующий за импульсом Г импудьсГ обнудяет счетчик 35 и через время за держки, определяемое элементом 62, заносит информацию - -+ из регистра 371 ОО, опять в счетчик 35. Наряду с этим, упомянутый сигнал из последовательности с частотой Р" проходит через открытый И элемент И 49 на вход триггера 41., переводя его в единичное состояние. В результате счетчик 35 переводится в ре-. жим работы "вычитание. Далее осуществляется периодическое считывание эапи санной в счетчике 35 информации. Причем по достижении нулевого значения информации в счетчике 35 в процессе считывания на его выходе вырабатывается сигнал, который переводит триггер 41 в ну левое состояние, в результате чего счетчик 35 переводится в режим работы сложение". Далее в счетчике 35 накапливается разность по абсолютному значению до момента прихода импульса из пос ледовательности Г к либо из последоват ел ьности Е . С приходом следующего импул ье 1 са из последовательности г осуществляется сброс информации в счетчике 35, перевод его в режим работы "вычитание" и запись в него информации из регистра 37. Да лее процесс повторяется, До момента прихода следующего импульса из последовательности Гк, который теперь уж проходит через открытый элемент И 46 40 он осуществляет перевод триггеров 39 и 42 соответственно в единичное и нулевое состояние, В результате элементы И 5 1 52 запираются соответственно ддя сигналов Гои Р", которые теперь не подаются Ноптна вход счетчика 35 и на его шину установки в нудь, и в упомянутом счетчике фиксируется абсолютное значение разности между13 798881 дается в режиме работы "вычитание и открывается элемент И 58 для сигна-.ловь г на вход счетчика 35. Одновременно с этим открывается элемент И 57 для сигналовьг" с шины 66 опорногосигнала, которые начинают проходить не вход счетчика 36. Сигналы из последо- б вательности п Сз считывают информацию,с записанную в счетчике 35 до момента т его обнуления. В этот момент на выхо О Н де счетчика 35 вырабатывается сигнал, р который переводит триггеры 40-45 в в нулевое состояние. При этом счетчик 35 и переводится в режим работы фсложение", в элементы И 49, 54, 56 и 58 запирают к ся, элементы И 50,51. и 52 отпирают- в ся и в счетчике 36 фиксируется резуль- р тат кода коррекции с точностью до постоянного множителя к даваемый бов.ное устройета дробеньшить ф изводной ия входного погреши расширсигнал изобретению ор который спустя время, определяемое элементом 64 задержки, переносится в регистр 38 памяти, где и запоминается. Далее описанный выше процесс по определению следующего значения коррекции периода повторяется. Как видно, окончательный результат в данном блоке получается через период частоты. Для результата коррекции каждый период очевидно достаточноиспользовать две описанные схемы, работающие в двухтакт. ном режиме.Итоговое значение частоты на выходе устройства с учетом работы блока 9 определяется выражением вида (для 1 - Г ):"-,где Т - интервал времени, заформирователем строТаким образом, рассмотренство позволяет в результате учной части периода частоты Р "умность формирования проить диапазон изменен 1. Устройство для дифференцированиястоты следования импульсов, содержа 14юшее первый элемент И, подключенныйпервым входом к входу дифференцируемойчастоты устройства, первому входу множительно-делительного блока, первомувходу блока вычитания частот, первомувходу число-импульсного запоминающеголока, соединенного частотным выходомо вторым входом блока вычитания часот и входом умножителя частоты, и кервому входу второго элемента И, втоой вход которого подключен к первомуходу третьего элемента И и выходуервого триггера, подключенного счетнымходом через первый элемент задержкивыходу первого элемента И и первомуходу второго триггера, соединенного втоым входом с выходом счетчика, шиныуправления реверсом которого подключенывыходам второго триггера, а счетный 20 вход соединен с выходом третьего элемента И, подключенного вторым входомк входу первой опорной частоты устройства, первому входу формирователя стробов и второму входу число-импульсного 2 запоминающего блока, соединеннного третьим входом с первым выходом формирователя стробов и подключенного кодовымвыходом к установочному входу счетчика,вход обнуления которого через второй ф элемент задержки соединен с входом управления записью регистра памяти, выходом второго элемента И и входом третьего триггера, подключенного выходом кпервому входу четвертого элемента И,соединенного вторым входом с входомвторой опорной, частоты устройства, тре 1- тьим входом - с входом запуска устройства, а выходом - со счетным входомуправляемого делителя частоты, подключенного управляющим входом к выходурегистра памяти, информационный вход которого соединен с кодовым выходом счетчиха, причем второй вход первого элемента И подключен к второму выходу формирователя стробов, соединенного вторымвходом с входом запуска устройства ипервым входом пятого элемента И, подключенного вторымвходом к выходу блока вычитания частот и соединенного третьим входом с выходом четвертого триггера, подключенного входом к выходумножительно-делитедьного блока, а выходпятого элемента И соединен с первымвходом элемента ИЛИ, подключенноговыходом к выходу устройства, о т л ич а ю щ е е с я тем, что, с целью повышения точности дифференцирования и расширения диапазона изменения входногосигнала, в устройство дополнительно вве15 79888 дены блок задержки, блок сдвига фазы, элемент запрета и блок управления коррекцией, подключенный первым входом к входу дифференцируемой частоты устройства, вторым входом к выходу умножи теля частоты и первому входу блока сдвига фазы, третьим входом- к входу второй опорной частоты устройства, четвертым входом - к выходу управляемого делителя частоты и первому входу эле О мента запрета, а выходом к первому входу блока задержки, соединенного вторым входом с выходом множительно-делительного блока и подключенного выходом к второму входу элемента ИЛИ и второму И входу блока сдвига фазы, выход которого соединен со вторым входом множительно- делительного блока, подключенного третьим входом к выходу элемента запрета соединенного вторым входом с входом 26 дифференцируемой частоты устройства.2. Устройство по и, 1, о т л и ч а юш е е с я тем, что блок управления коррекцией содержит первый и второй элементы И, соединенные первыми входами с 25 первым входом блока управления коррекцией и подключенные вторыми входами к выходу первого триггера, соединенного первым входом с выходом второго элемента И, входом второго триггера и с ЗО первыми входами элементов И первой группы, подключенных вторыми входами к выходам разрядов первого счетчика и соединенных выходами с входами первого регисира памяти, выходы которого подключены к первым входам элементов И второй группы, соединенных вторыми входами г выходом первого элемента задержки и подключенных выходами к входам разрядов первого счетчика, соеди п немного счетным входом с выходом элемента ИЛИ и подключенного входами управд"агния реверсом к выходам третьего триггера, первый вход которого соединен с выходом первого счетчика и с первым 4 входом третьего элемента И, а вторые входы третьего триггера подключены к выходам четвертого и пятого элементов И, причем первый вход четвертого элемента И, соединенного вторым вхо- ув, дом с выходом второго триггера, подключен к входу обнуления первого счетчика, входу первого элемента задержки и выходу шестого элемента И, соединейного пера вым входом с первым выходом четвертого триггера и с первым входом Седьмого элемента И и подключенного вторым входом к четвертому входу блока управления коррекцией и к первым входам 16восьмого и девятого элементов И, при этом второй вход восьмого элемента И подключен ко второму выходу. четвертого триггера, а выход через второй элемент задержки - к счетному входу пятого триггера, соединенного первым выходом с первым входом десятого и вторым входом. девятого элементов И и подключенного вторым выходом к первым входам одиннадцатого и двенадцатого элементов И, причем второй вход одиннадцатого элемента И,соединенного третьим входом со вторым входом блока управления коррекцией подключей к первому выходу шестого триггера и к вторым входам третьего и двенадцатого элементов И, а выход третьего элемента И соединен с первыми входами четвертого, шестого и седьмого триггеров и с входом третьего элемента задержки, подключенного выходом к первым входам элементов И третьей группы, соединенных вторыми входами с выходами разрядов второго счетчика и подключенных выходами к входам второго регистра памяти, выходы которого соединены с выходом блока управления коррекцией, а вход второго счетчика подключен к выходу двенадцатого элемента И, соединенного третьим входом с шиной опорного сигнала, причем вьход первого элемента И подключен к вторым входам первого и четвертого триггеров, выход девятого элемента И соединен со вторым входом шестого тригге ра, подключенного вторым выходом к третьему входу восьмого элемента И, а выход седьмого элемента И, соединенного вторым входом с третьим входом блока управления коррекцией и со вторым входоь десятого элемента И, подключен к первому входу элемента ИЛИ, соединенного вторым входом с выходом десятого элемента И и подключенного третьим входом к вьход тринадцатого элемента И, первый вход которого соединен с выходом одиннадцатого элемента И и с первым входом пятого элемента И, а второй вход тринадцатого элемента И подключен к первому выходу седьмого триггера, соединенного вторым выходом со вторым входом пятого элемента И, подключенного выходом к второму входу седьмого триггера. Источники информации,примятые во внимание при. экспертизе1. Сергеев Н, П. и др. Двференцируюшие устройства для обработки частотной информации, Изв. ВУЗов "Приборостроение, % 7, 1975, с. 13-17.172. Авторское свидетельство СССР % 604008, кл. С 06 С 7/18, 1976, 798881 183. Авторское свидетельство СССРМ 525117, кл. 6 06 С 7/18, 1974

СмотретьЗаявка

2594184, 24.03.1978

ПРЕДПРИЯТИЕ ПЯ А-1923

ЧИСТЯКОВ БОРИС ВИКТОРОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: дифференцирова-ния, импульсов, следования, частоты

Опубликовано: 23.01.1981

Код ссылки

<a href="https://patents.su/11-798881-ustrojjstvo-dlya-differencirova-niya-chastoty-sledovaniya-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для дифференцирова-ния частоты следования импульсов</a>

Предыдущий патент: Четырехквадратное множительноеустройство

Следующий патент: Устройство для дифференцирова-ния частотно модулированногосигнала

Случайный патент: Фильтр токов нулевой последовательности