Формирователь квазиоптимальных дискретно-частотных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1578836

Авторы: Головко, Гриненко, Лысаковский

Текст

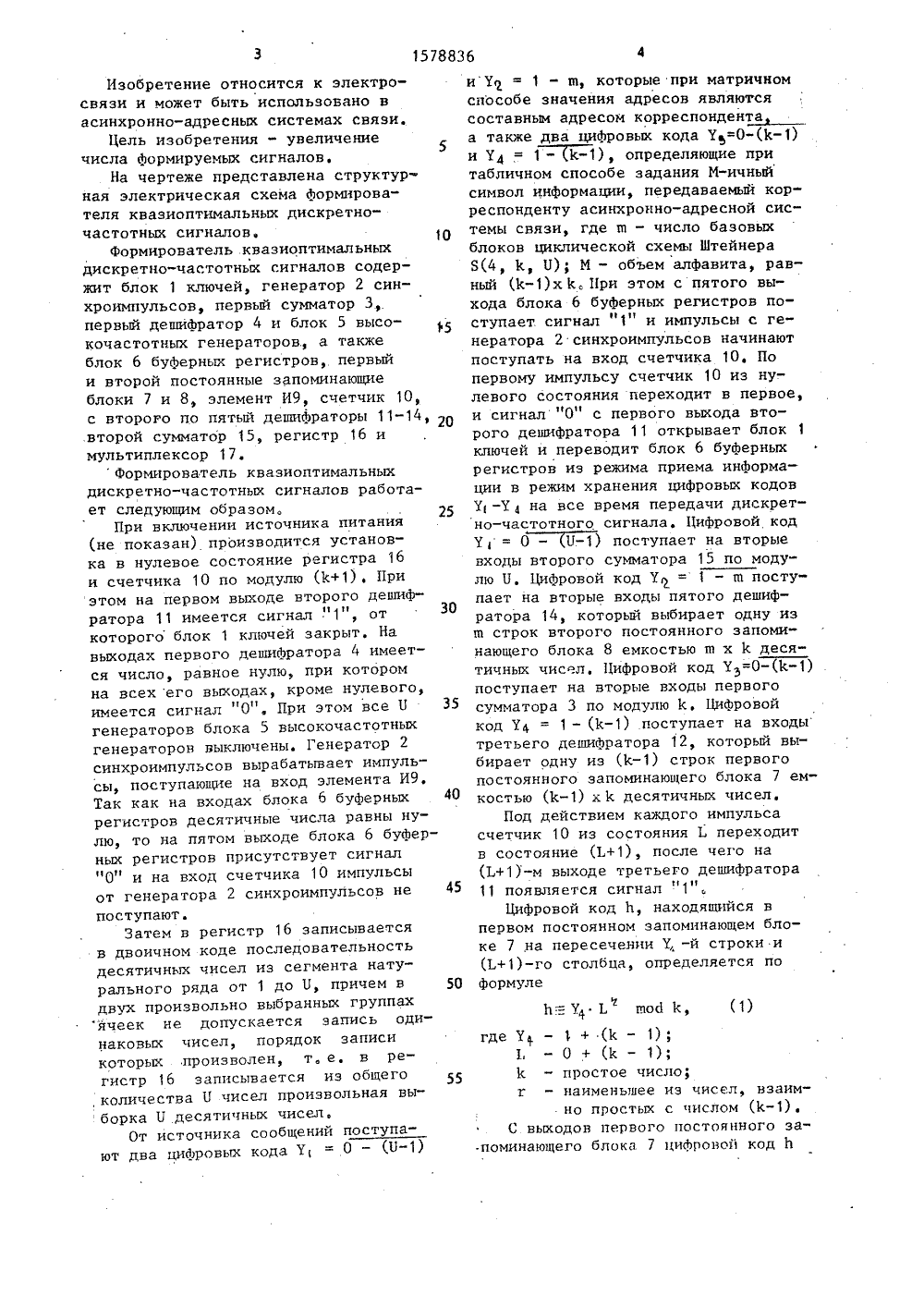

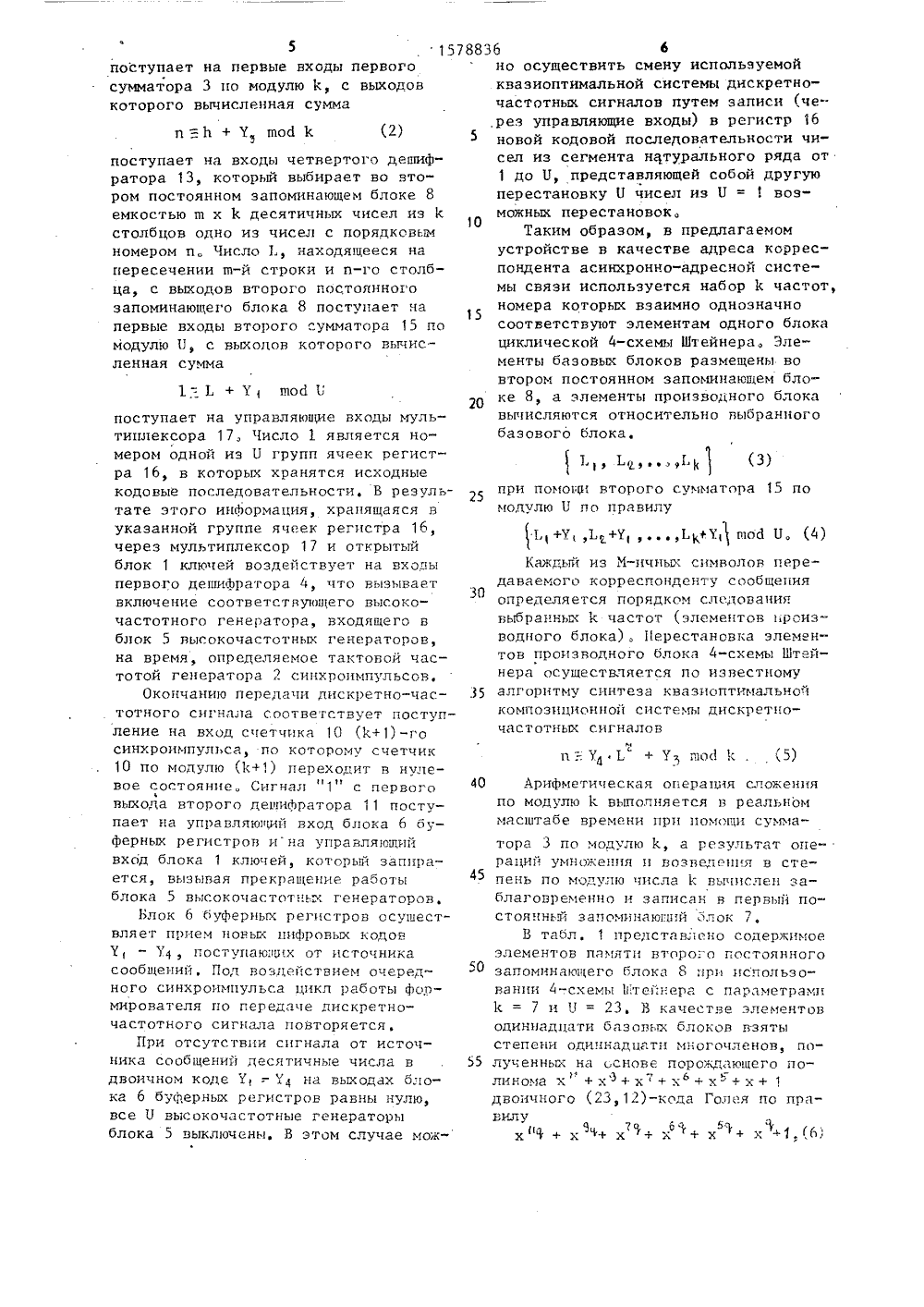

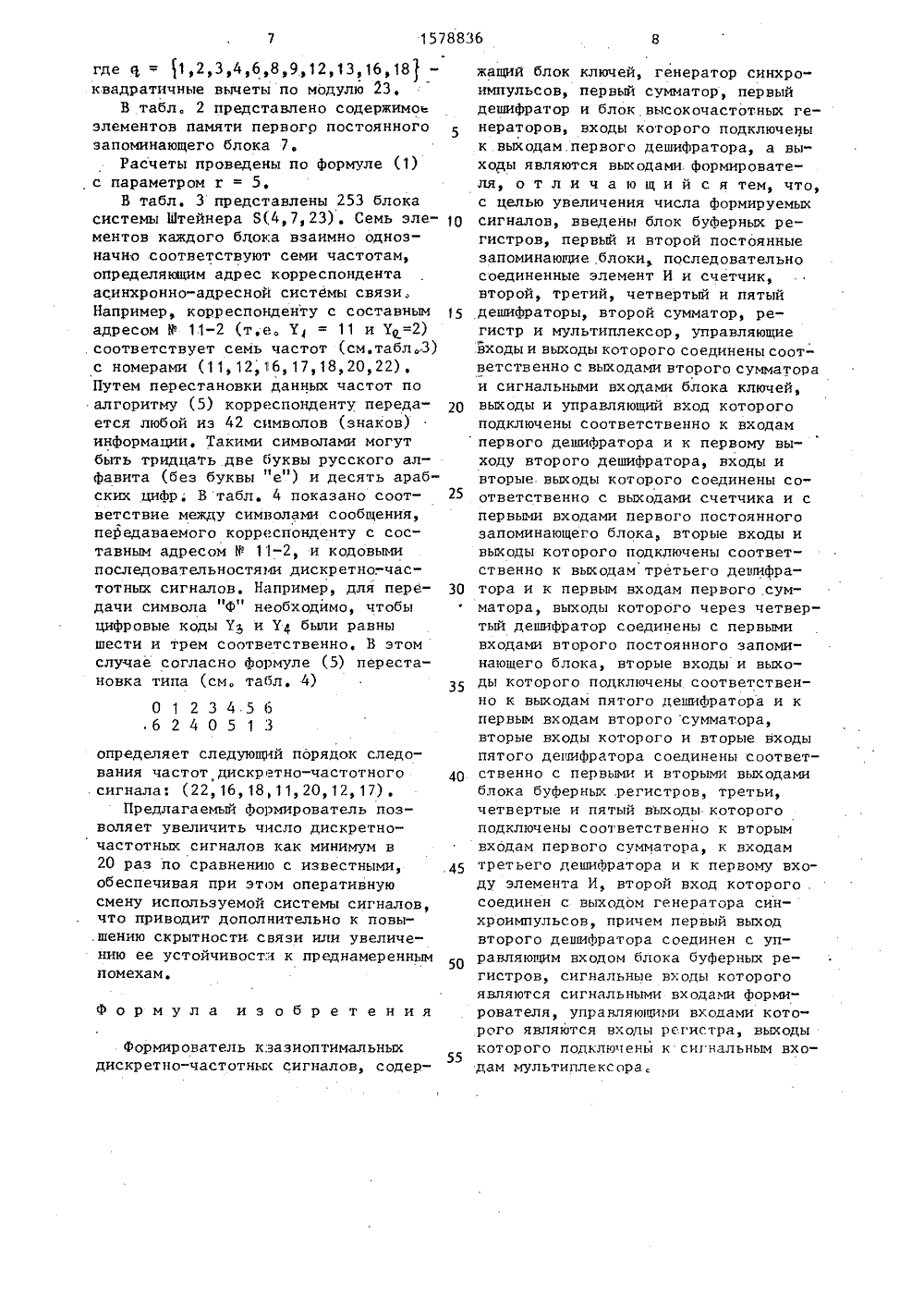

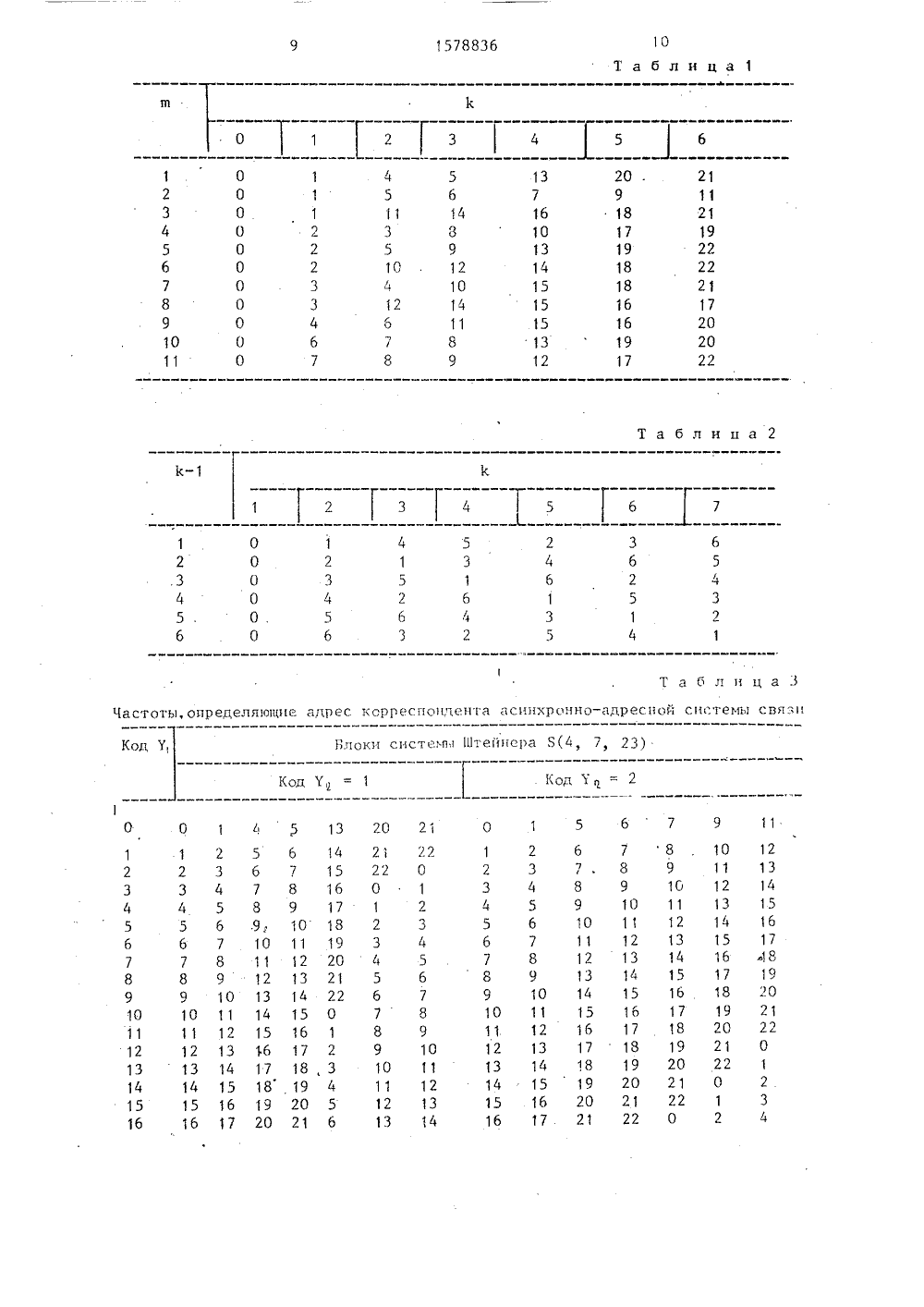

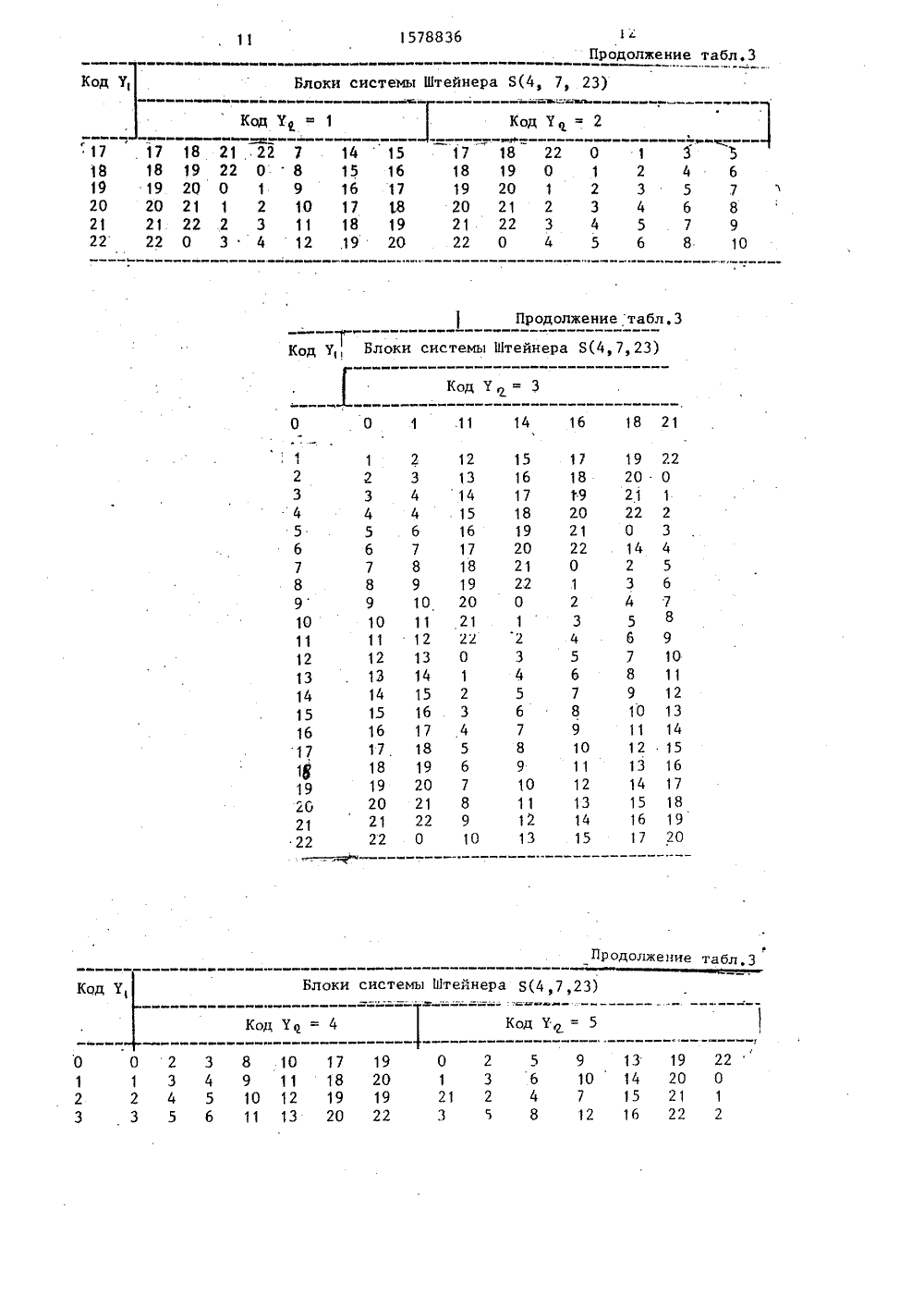

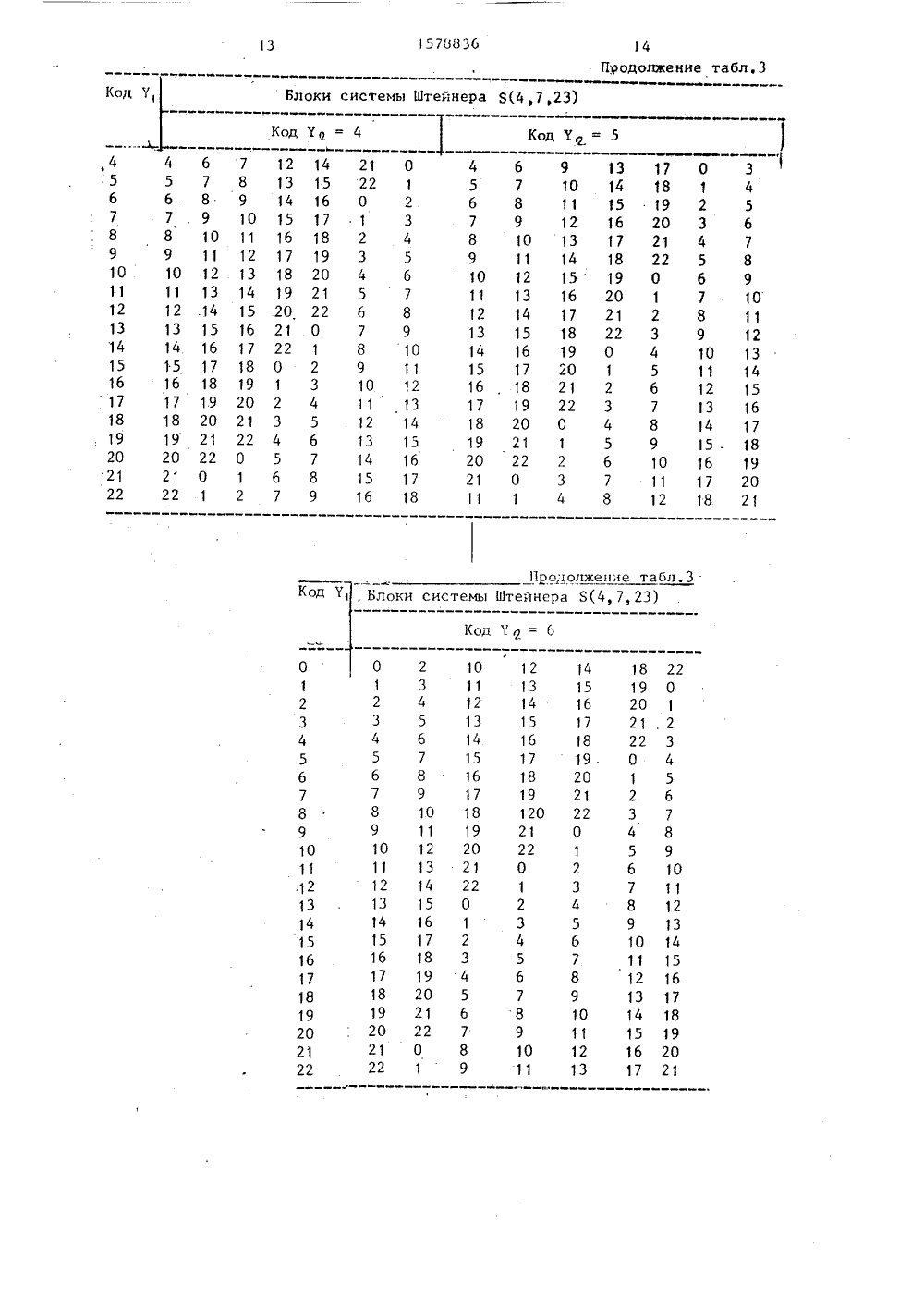

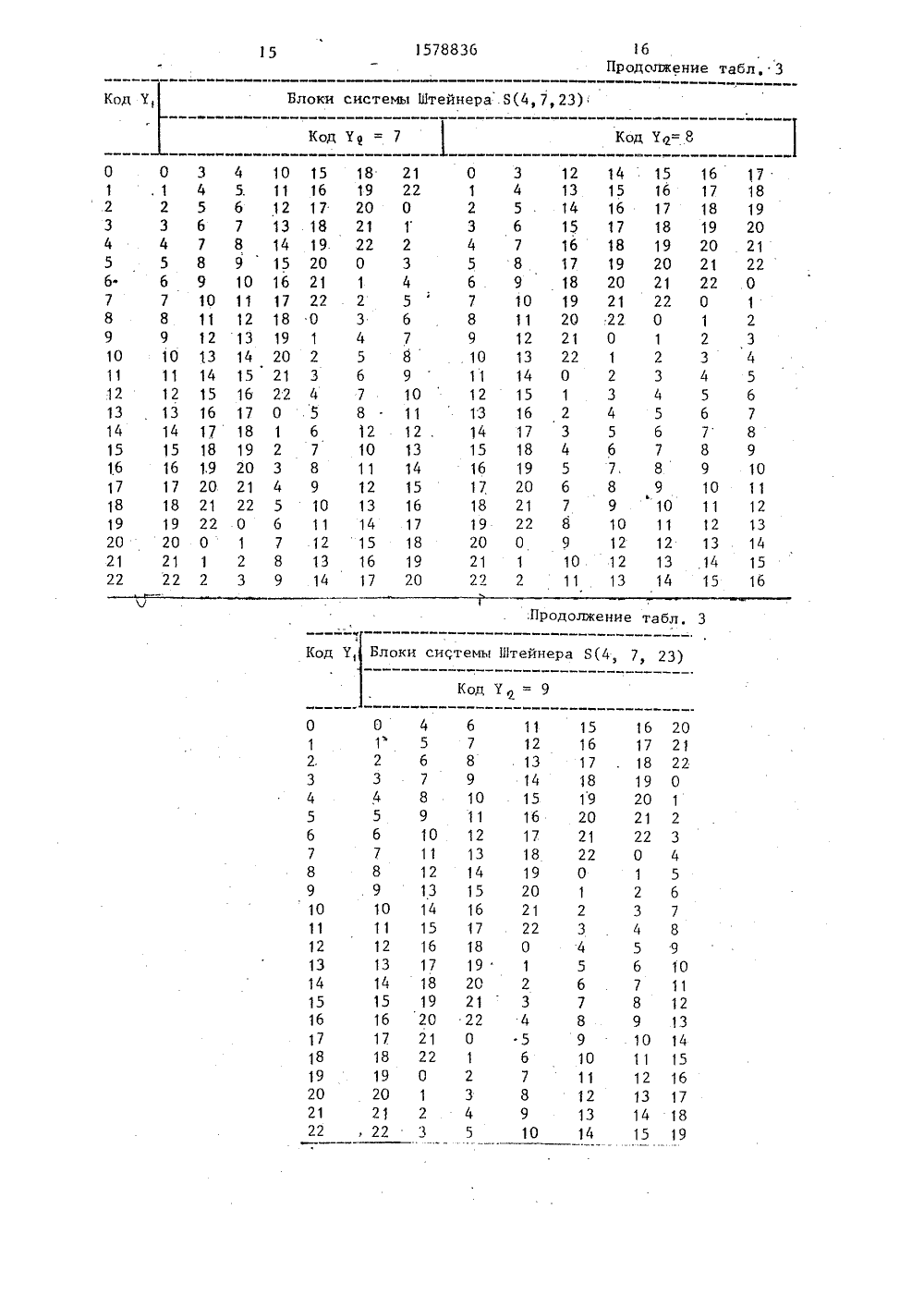

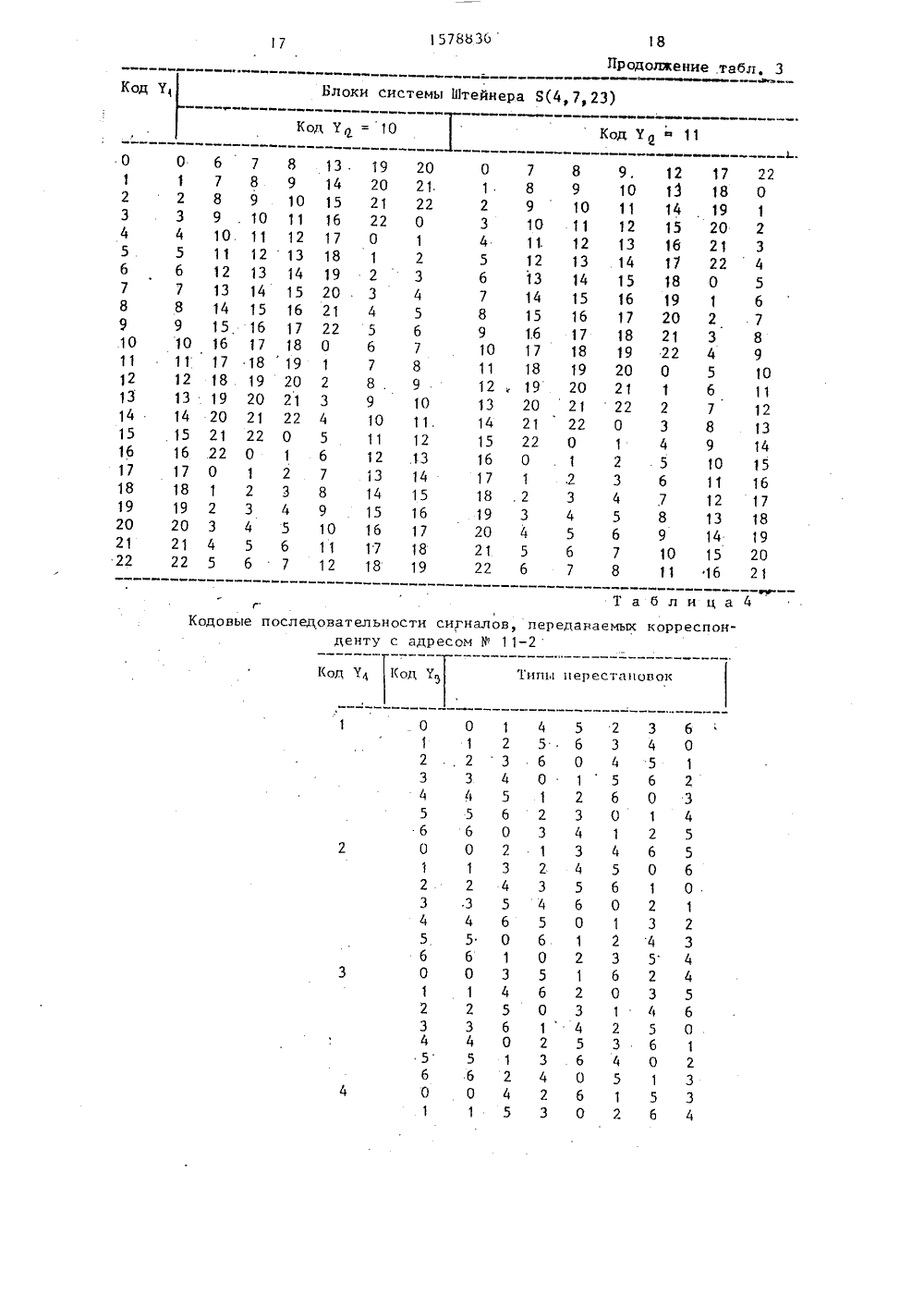

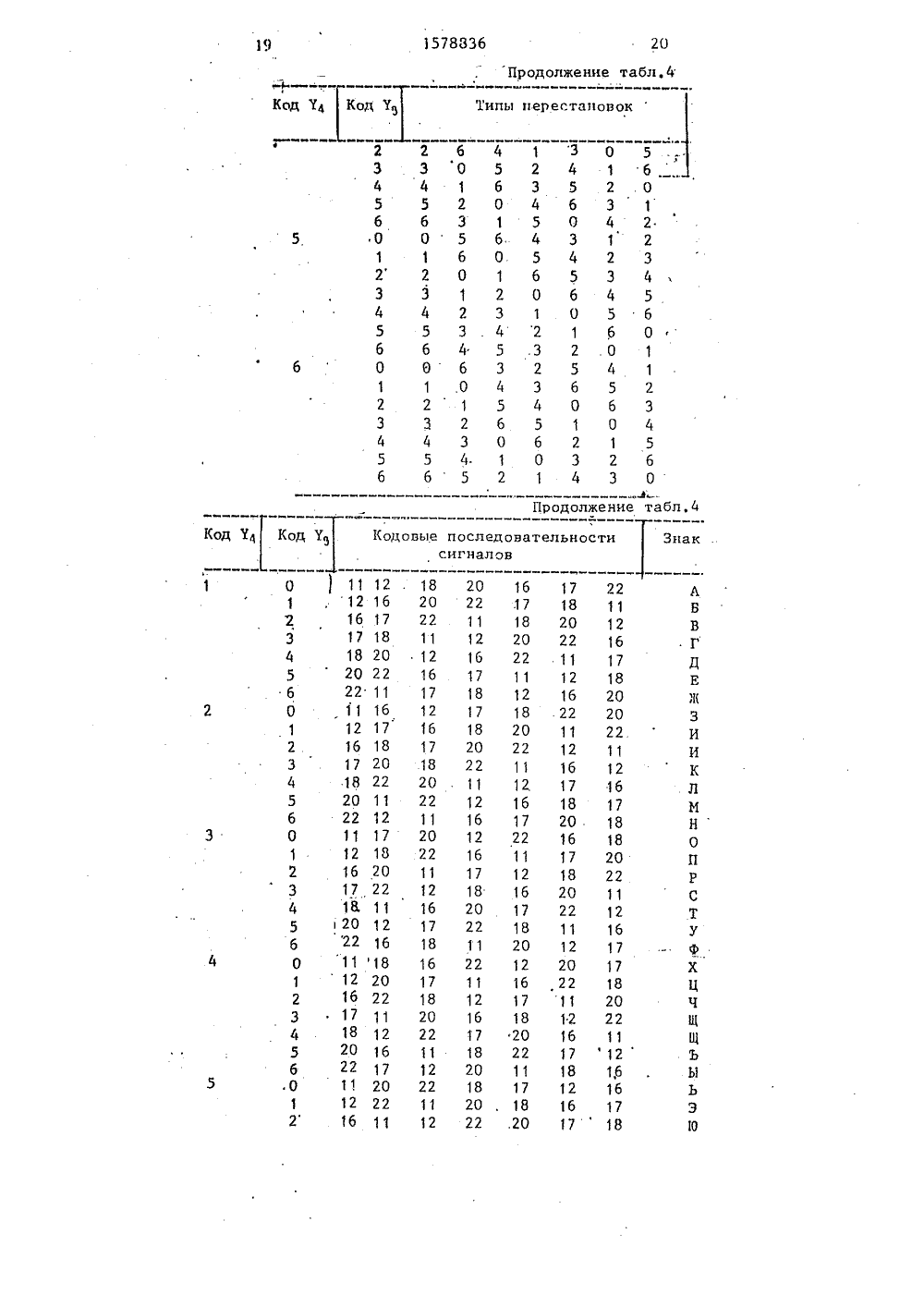

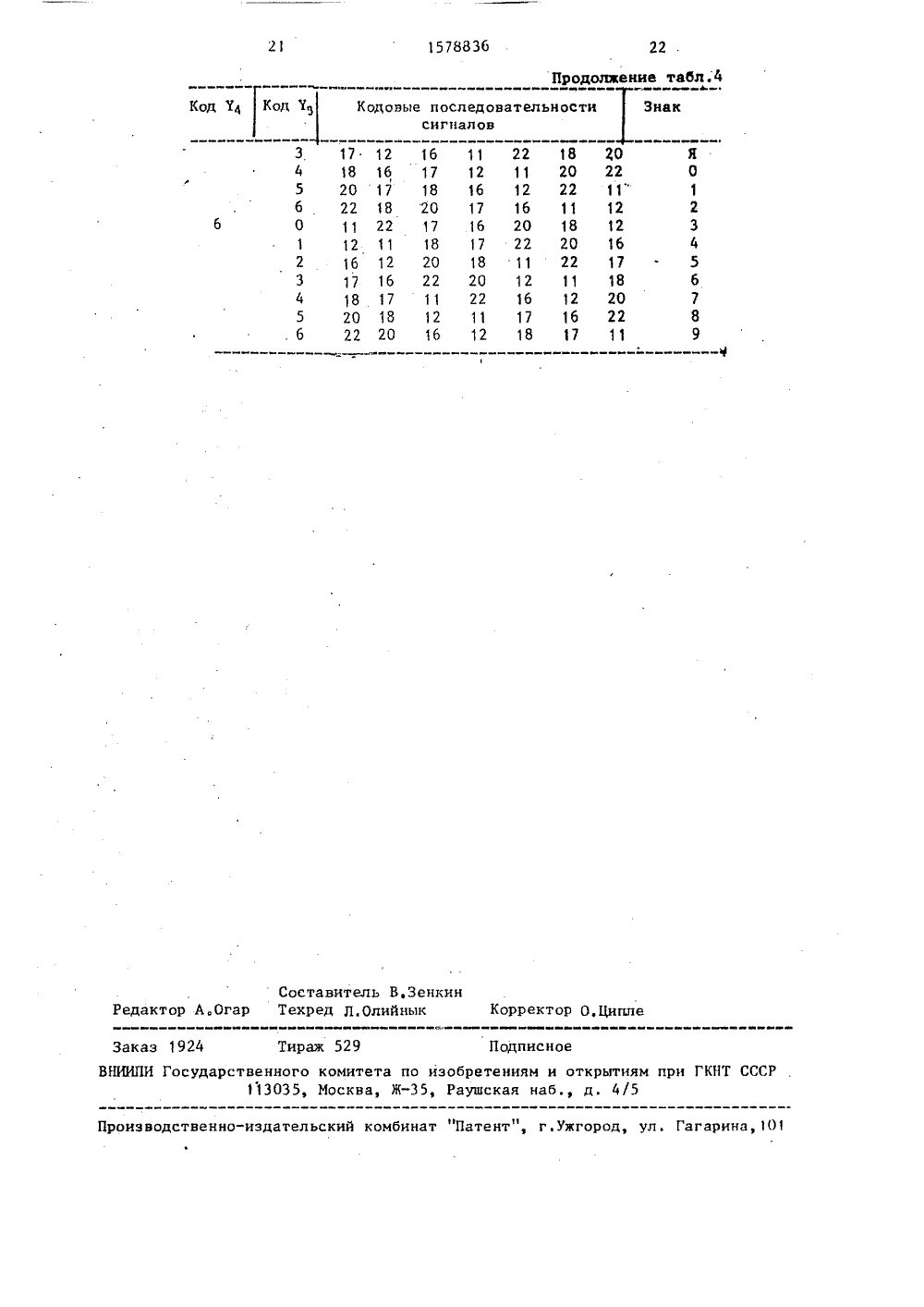

.801578836 А 1 Д 1)5 Н 04 Ь 27/26 ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР 1(56) Авторское свидетельство СССРР 362437, кл. Н 03 К 3/80, 1971.(57) Изобретение относится к электросвязи и может быть использовано васинхронно-адресных системах связи,Цель изобретения - увеличение числаформируемых сигналов. Для достиженияцели в формирователь введены блок 6.буферных регистров, первый и второйпостоянные запоминающие блоки 7 и 8,элемент И 9, счетчик 10, второй - пя 2 тый дешифраторы 11-14, второй сумматор 15, регистр 16 и мультиплексор 17. Блок 6 буферных регистров осуществляет прием цифровых кодов от ис" точника сообщения. В качестве адреса корреспондента используется набор частот, элементы базовых блоков размещены во втором постоянном запоминающем блоке 8, а элементы производ-. ного блока вычисляются во втором сумматоре 15. Арифметическая операция сложения по модулю 1 выполняется в реальном масштабе времени в первом сумматоре 3, а результат арифметических вычислений записи - в первом постоянном запоминающем блоке 7, Обеспечивается оперативная смена системы сигналов при значительном увеличении числа дискретно-частотных сигналов. 1 ил.,4 табл. С:1578336 20 Продолжение табл,4 Типы пеРестановок Код 7 Код 5 60 1 6 4 0 5 1 6 2 0 3 1 5 б б О.0 1 1 2 2 3 2 2 3 . Э 4 4 5 5 6 б О О 1 2 2 3 Э 4 4 4 3 . 4 4 5 0 5 5 6 60 9 6 3 1 1,0 4 2 2 Э 3 1 5 2 6 3 0 б 0Э 6 6 Продолжение табл,4 Кодовые последовательности сигналов Код У Код У Знак О 11 12 16 20 16 22 .17 11 18 12 20 16 22 17 11 18 12 17 18 18 20 20 22 22 11 11 12 12 16 16 17 12 22 16 11 17 1218 16 20 17 22 18 11 20 22 12 11 16 12 17 16 18 17 18 20 22 11 12 16 22 11 12 16 17 18 20 22 11 12 16 17 18 20 16 17 18 20 22 11 12 16 17 18 18 20 22 20 22 11 12 20 ,22 11 11 12 16 17 17 18 20 22 12 22 17 2011 18 22 16 11 1712 18 16 12 22 11 20 11 18 17 20 . 18 16 17 18 12 16 17 12 22,20 1, 12 2 16 17 Э 17 18 4 18 20 5 20 22 6 22 11 О 11 16 1 12 17 2 16 18 3 17 20 4 18 22 5 20 11 6 22 12 0 11 17 1 12 18 2 16 20 3 17 22 4 1 В 11 520 12 б 22 16 0 1 1 18 112 20 2 16 22 3 17 11 4 18 12 5 20 16 б 22 17 ,0 11 201 12 22 2 16 11 18 20 22 11 12 16 17 12 16 17 18 20 22 11 20 22 11 12 16 17 18 16 17 18 20 1 2 3 4 5 5 б 0 1 2 Э 2 Э 4 5 6 0 1 Э 4 б 0 3 4 5 б 0 1 2 5 б 0 1 2 Э 4 А Б В Г Д Е 1( 3 И И К Л М Н0 П Р С Т У Ф Х Ц Ч Ш Щ Ь Ы Ь Э 1 ОЗаказ 1924 Тираж 529 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д. 4/5 изводственно-издательский комбинат "Патент", г.ужгород, ул, Гагарина,10 2 3 4 5 18 16 17 20 17 18 22 18 20 11 22 17 12 11 18 16 12 20 7 16 2 8 17 1 0 18 1 2 20 1 11 22 18 12 11 20 16 12 22 17 16 1 1 16 20 18 17 22 20 18 11 22 20 12 11 22 16 12 11 17 16 12 18 17 Я 0 1 230 Изобретение относится к электросвязи и может быть использовано васинхронно-адресных системах связи,Цель изобретения - увеличение5числа формируемых сигналов.На чертеже представлена структурная электрическая схема Формирователя квазиоптимальных дискретночастотных сигналов.10Формирователь квазиоптимальныхдискретно-частотных сигналов содержит блок 1 ключей, генератор 2 синхроимпульсов, первый сумматор 3,первый дешифратор 4 и блок 5 высокочастотных генераторов, а такжеблок 6 буферных регистров, первыйи второй постоянные запоминающиеблоки 7 и 8, элемент И 9, счетчик 10,с второго по пятый дешифраторы 11-14, 20второй сумматор 15, регистр 16 имультиплексор 17.Формирователь квазиоптимальныхдискретно-частотных сигналов работает следующим образом.25При включении источника питания(не показан) производится установка в нулевое состояние регистра 16и счетчика 10 по модулю Ь+1), Приэтом на первом выходе второго дешиф 11 11ратора 1 1 имеется сигнал . 1 , откоторого блок 1 ключей закрыт, Навыходах первого дешифр ат ор а 4 имеется число , равное нулю, при которомна всех ег о выходах, кроме нулевого,имеется сигнал " 0" . При этом вс е Б 3 5генераторов блока 5 высокочастотныхгенераторов выключены . Генератор 2синхроимпуль со в вырабатывает импульсы, поступающие на вход элемента И 9 .Так как на входах блока 6 буфер ных 40регистров десятичные числа равны нулю, то на пятом выходе блока 6 буферных регистров присутствует сигнал" 0" и на вход счетчика 1 О импульсыо т генератора 2 синхроимпуль сов н е 45поступают ,Затем в регистр 1 6 записываетсяв двоичном коде последовательностьдесятичных чисел из сегмента натуР ального РЯда о т 1 до Б р пРичем в 50двух произвольно выбранных группахячеек не допускается запись одинаковых чисел , порядок записикоторых произволен, т, е, в р егис тр 1 6 записывается из общего, количества Б чисел произвольная выб ор ка Б десятичных чисел ,От источника сообщений поступают два цид)ровых кода У= 0 - О) - 1 ) иУ = 1 " ш, которые при матричном способе значения адресов являются составным адресом корреспондента а также два цифровых кода уащО-Й) и уа сх ) - Г 1), определяющие при табличном способе задания М-ичный символ информации, передаваемый корреспонденту асинхронно-адресной системы связи, где ш - число базовых блоков циклической схемы Штейнера Б(4, К, У); М - объем алфавита, равный (1 с)х К. При этом с пятого выхода блока 6 буферных регистров поступает. сигнал "1" и импульсы с генератора 2 синхроимпульсов начинают поступать на вход счетчика 10, По первому импульсу счетчик 10 из нулевого состояния переходит в первое, и сигнал "0" с первого выхода второго дешифратора 11 открывает блок 1 ключей и переводит блок 6 буферных регистров из режима приема информации в режим хранения цифровых кодов У, -Уна все время передачи дискретно-частотного сигнала, Цифровой код у, = О - Г- поступает на вторые входы второго сумматора 15 по модулю Б, Цифровой код У) = 1 - ш поступает на вторые входы пятого дешифратора 14, который выбирает одну из ш строк второго постоянного запоминающего блока 8 емкостью ш х с десятичных чисел, Цифровой код 7=0-Й) поступает на вторые входы первого сумматора 3 по модулю К, Цифровой код У 4 = 1 - Ь) поступает на входы третьего дешифратора 12, который выбирает одну из -1) строк первого постоянного запоминающего блока 7 емкостью (К) хдесятичных чисел,Под действием каждого импульса счетчик 10 из состояния Ь переходит в состояние (Ь+1), после чего на (Ь+1)-м выходе третьего дешифратора 11 появляется сигнал оЦифровой код Ь, находящийся в первом постоянном запоминающем блоке 7 на пересечении У,. -й строки и (Ь+1)-го столбца, определяется по формулеЬ:= У Ь шос ср (1) где У - 1 + Ос - 1);Ь -О+ Ь);к - простое число;г - наименьшее из чисел, взаимно простых с числом (с),С выходов первого постоянного запоминающего блока 7 цифровой код Ьпоступает на первые входы первогосумматора 3 по модулю К, с выходовкоторого вычисленная сумма(2) п=Ь+У шойК поступает на входы четвертого дешифратора 13, которыи выбирает во втором постоянном запоминающем блоке 8емкостью ш х 1 с десятичных чисел изстолбцов одно из чисел с порядковымномером и. Число 1., находящееся напересечении ш-й строки и и-го столбца, с выходов второго постоянногозапоминающего блока 8 поступает напервые входы второго сумматора 15 помодулю 11, с выходов которого вычисленная сумма 1= Е + Ушос 1 (1 поступает на управляющие входы мультиплексора 17. Число 1 является номером одной из 0 групп ячеек регистра 16, в которых хранятся исходные кодовые последовательности, В результате этого информация, хранящаяся в указанной группе ячеек регистра 16, через мультиплексор 17 и открытый блок 1 ключей воздействует на входы первого дешифратора 4, что вызывает включение соответствующего высокочастотного генератора, входящего в блок 5 высокочастотных генераторов, на время, определяемое тактовой частотой генератора 2 синхроимпульсов,Окончанию передачи дискретно-частотного сигнала с.оответствует поступление на вход счетчика 10 %+1) -го синхроимпульса, по которому счетчик 10 по модулю (1 с+1) переходит в нулевое состояние, Сигнал "1" с первоговыхода второго дешифратора 11 поступает на управляющий вход блока 6 бу - ферных регистров ина управляющий вход блока 1 ключей, который запирается, вызывая прекращение работы блока 5 высокочастотных генераторов,Блок 6 буферных регистров осушествляет прием новых цифровых кодов У, - У, поступаюпПх от источника сообщений, Под воздействием очередного синхроимпульса цикл работы формирователя по передаче дискретно- частотного сигнала повторяется.При отсутствии сигнала от источника сообщений десятичные числа в двоичном коде У, . - 7 на выходах блока 6 буферных регистров равны нулю, все У высокочастотные генераторы блока 5 выключены. В этом случае мож 8 8366но осуществить смену используемойквазиоптимальной системы дискретночастотных сигналов путем записи (че,рез управляющие входы) в регистр 16новой кодовой последовательности чисел из сегмента натурального ряда от1 до У, представляющей собой другуюперестановку Б чисел из У =возможных перестановок.Таким образом, в предлагаемомустройстве в качестве адреса корреспондента асинхронно-адресной системы связи используется набор К частот,номера которых взаимно однозначносоответствуют элементам одного блокациклической 4-схемы Штейнера, Элементы базовых блоков размещены вовтором постоянном запоминающем блоке 8, а элементы производного блокавычисляются относительно выбранногобазового блока.1, , "Сзпри помощи второго сумматора 15 помодулю П по правилу1, +у,у,еФ 1,1 пмд О, (4)Каждый из М-ичных символов передаваемого корреспонденту сообщенияопределяется порядком следованиявыбранных 1 с частот (элементовроизводного блока). Перестановка элементов производного блока 4-схемы Штайнера осуществляется ло известному 35 алгоритму синтеза квазиоптимальнойкомпозиционной системы дискретночастотных сигналовми.-. У1, + У шо(1 1, (5)10 Арифметическая операция сложенияпо модулю 1: выполняется в реальном масштабе времени при помощи сумматора 3 по модулю Е, а результат операций умножения и возведения в сте пень по модулю числа к вычислен заблаговременно и записан в первый постоянный зацсминающий блок 7,В табл, 1 представлено содержимоеэлементов памяти второго гостоянного (О запоминающего блока 8 при использовании 4-.схемы 1,тайлера с параметрамп 1 с = 7 и У = 23, В качестве элементов одиннадцати базовых блоков взяты степени одиннадцати многочленов, по лученных на основе порождающего полинома х +х" +х+х +х-+х+ 1 двоичного (23,12)-када Голая по правилухи + х + х 1+ х + х + х +1. (6,9 7 о 5 Ъгде е = 11,2,3,4,б,8,9,12,13,18,181квадратичные вычеты по модулю 23,В табл. 2 представлено содержимоьэлементов памяти первого постоянногозапоминающего блокаРасчеты проведены по формуле (1)с параметром г = 5,В табл. 3 представлены 253 блокасистемы Штейнера Я(4,7,23). Семь элементов каждого блока взаимно однозначно соответствуют семи частотам,определяющим адрес корреспондентаасинхронно-адресной системы связи.Например, корреспонденту с составным 15адресом У 1.1-2 (т,е. У 2 = 11 и У=2). соответствует семь частот (см,табл 3)с номерами (1 1, 12,16, 17, 18, 20, 22) .Путем перестановки данных частот поалгоритму (5) корреспонденту передается любой из 42 символов (знаков)информации, Такими символами могутбыть тридцать две буквы русского алФавита (без буквы "е") и десять араб"ских цифр; В табл. 4 показано соответствие между символами сообщения,передаваемого корреспонденту с составным адресом У 11-2, и кодовымипоследовательностями дискретно;частотных сигналов. Например, для передачи символа "ф" необходимо, чтобыцифровые коды У и У 4 были равнышести и трем соответственно. В этомслучае согласно Формуле (5) перестановка типа (см. табл, 4)3501 234566240513определяет следующий порядок следования частот дискретно-частотного 40сигнала: (22, 16, 18, 11, 20, 12, 17),Предлагаемый формирователь позволяет увеличить число дискретночастотных сигналов как минимум в20 раз по сравнению с известными, 45обеспечивая при этом оперативнуюсмену используемой системы сигналов,что приводит дополнительно к повы,шению скрытности. связи или увеличению ее устойчивости к преднамереннымпомехам.Формула из обретенияФормирователь квазиоптимальных дискретно-частотных сигналов, содер жащий блок ключей, генератор синхроимпульсов, первый сумматор, первыйдешифратор и блок высокочастотных генераторов, входы которого подключенык.выходам. первого дешифратора, а выходы являются выходами. Формирователя, о т л и ч а ю щ и й с я тем, что,с целью увеличения числа формируемыхсигналов, введены блок буферных регистров, первый и второй постоянныезапоминающие, блоки, последовательносоединенные элемент И и счетчик,второй, третий, четвертый и пятыйдешифраторы, второй сумматор, регистр и мультиплексор, управляющиевходы и выходы которого соединены соответственно с выходами второго сумматораи сигнальными входами блока ключей,выходы и управляющий вход которогоподключены соответственно к входампервого дешифратора и к первому выходу второго дешифратора, входы ивторые выходы которого соединены соответственно с выходами счетчика и спервыми входами первого постоянногозапоминающего блока, вторые входы ивыходы которого подключены соответственно к выходам третьего дешифратора и к первым входам первого сумматора, выходы которого через четвертый дешифратор соединены с первымивходами второго постоянного запоминающего блока, вторые входы и выходы которого подключены соответственно к выходам пятого дешифратора и кпервым входам второго сумматора,вторые входы которого и вторые входыпятого депифратора соединены соответственно с первыми и вторыми выходамиблока буферных .регистров, третьи,четвертые и пятый выходы которогоподключены соответственно к вторымвходам первого сумматора, к входамтретьего дешифратора и к первому входу элемента И, второй вход которого .соединен с выходом генератора синхроимпульсов, причем первый выходвторого дешифратора соединен с управляющим входом блока буферных регистров, сигнальные входы которогоявляются сигнальными входами Формирователя, управляющими входами кото.рого являются входы регистра, выходыкоторого подключены к сигнальным входам мультиплексора,1578836 Т а б л и ц а 1 0 1 2 3 4 5 6ее щ4 5 135 6 711 14 163 8 105 910 12 144 10 1512 14 156 11 158 138 9 12 21 11 21 19 2 22 21 17 20 20 22 Таблица 2 3 4 5 6 7 1 2 .3 4 5 б 0 0 о О.0 Т а блица 3 Час Готы, 011 Р еделя 101 ц 11 е апРес коРР еспондента ас 11 нхР 011 но-с 1 ДРес 110 Й системы сВя В 1 Блоки снсте,п 1 Штей 11 ера 8(4, 7, 23) Код У Код 1 = 2 КОДУ = 1о о 0 1 5 67 9 11 1 г 3 4 5 6 7 8 9 10 11 1 1 22 2 33 3 44 4 55 5 б6 6 77 7 88 8 99 9 1010 10 1 111 11 1212 12 131313 1414 14 1515 15 1616 16 17 0 0 о 0 0 о 0 0 о о 0 4 5 13 5 6 14 6 7 15 7 8 16 8 9 17 9;. 10 18 10 11 19 1 1 12 20 12 13 21 13 14 22 14 15 015 16 1 16 17 2 17 18, 3 18 19 19 20 5 20 21 б 20 21 21 22 22 0 0 1 1 2 2 3 3 4 5 5 6 6 7 8 8 9 9 10 10 11 11 12 12 13 13 141578836 Продолжение табл,З Блоки системы Штейнера 8(4, 7, 23) Код У Код У= 2 Код У - 1% 1 3 5 2 4 6 3 5 .7 4 б 8 5 7 9 6 8 10 17 . 17 18 18 19 19 20 20 21 21 22 22 17 18 19 20 21 22 18 22 19 0 20 1 21 2 22 3 0 4 18 21. 22 7 19 22 О 8 20 0 1 9 21 1 2 10 22 2 3 11 0 3 4 12 14 15 15 16 16 17 17 8 18 19 19 20 0 1 2 3 4 5 Продолжение табл,З Код У, Блоки системы Штейнера 8(4,7,23) Г Код У= 3 14 1 1 1 22 15 11 19 16 18 20 17 19 21 18 20 22 19 21 О 20 22 14 21 0 2 22 1 3 0 2 А 1 3 5 2 4 б 2 2 3 13 3 3 4 14 4 4 4 15 5 5 б 16 6 6 7 17 7 7 8 18 8 8 9 19 9 9 10 20 10 10 11,21 11 11 12 22 12 12 13 0 13 . 13 14 1 14 14 15 2 15 15 16 3 16 16 17 417, 18 5 18 19 6 19 20 720 21 8 21 22 9 22 О 10 2 3 4 91011 34 6 8 5 7 9 6 8 10 7 9 11 8 10 12 9 11 13 10 12 14 1 1 13 15 12 14 16 13 15 17 14 15 16 17 1 ф 19 20 21 22 1 2 олжецие табл,3 4,7,23) Блоки системы Штейнер еыююмм одУ =51578836 8(4,7,23) системы Штейнера Код У,Блоки Код 7,2 = 5 Код 7 12 8 13 9 14 1 О 15 11 16 12 17 13 18 14 19 15 20 14 15 16 17 18 19 20 21 22 21 0 22 1 0 2 1 3 2 4 3 5 4 6 5 7 б 8 16 21 17 22 18 0 19 1 20 2 21 3 22 4 0 5 1 б 2 7 7 9 8 10 9 11 10 12 11 13 12 14 13 15 14 16 15 17 16 18 У, Блоки Код исте од 14 15 16 17 18 19 120 21 22 0 2 31578836 18 17 Продолжение табл. 3 Блоки системы Штейнера 8(4,7,23) Код У Код У = 10 Код Уд 0 0 1 1 2 2 Э 3 5 0 5 11 1 6 12 2 7 13 3 8 14 4 9 15 5 10 16 б 11 17 7 12 18 7 8 ца 4 б л 1 а 7 налов, пеом У 11-2 корреспон а емых одовые послецовательности денту с адсие ипы перестало од У Ко 1 4 2 53 б 4 О 3 4 5 б 0 1 2 6 0 1 б Э 0 4 15 1 2 6 2 3 0 Э 4 1 1 3 2 4 5 Э 5 60 6 0 1 2 5 4 б 6 5 0 0 б 1 1 0 2 3 5б 2 1 3 2 4 Э 5 б 2 О 3 1 4 2 5 3 б 4 О 5 15 2 6 5 0 3 б 14 0 2 5 1 3 б 2 4 О 4 2 6 5 3 0 5б 7 7 8 8 9 9 10 10 11 11: 2 12 13 13 14 14 15 15 16 16 17 17 18 18 19 19 20 20 21 21 22 22 6 7 7 8 8 9 9 .10 10 11 11 12 12 13 13 14 14 15 15 16 16 17 17 18 18 19 19 20 20 21 21 22 22 0 0 1 1 2 2 3 8 13 19 20 9 14 20 21 10 15 2 22 11 16 22 0 12 17 0 1 13 18 1 2 14 19 2 3 15 20 3 4 16 21 4 5 17 22 5 б 18 019 120 221 322 4 б 7 7 8 8 . 9 9 10 10 1112

СмотретьЗаявка

4487397, 28.09.1988

РОСТОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

ГРИНЕНКО НИКОЛАЙ ИВАНОВИЧ, ЛЫСАКОВСКИЙ АНДРЕЙ ФРАНЦЕВИЧ, ГОЛОВКО ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/26

Метки: дискретно-частотных, квазиоптимальных, сигналов, формирователь

Опубликовано: 15.07.1990

Код ссылки

<a href="https://patents.su/11-1578836-formirovatel-kvazioptimalnykh-diskretno-chastotnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь квазиоптимальных дискретно-частотных сигналов</a>

Предыдущий патент: Устройство для передачи и приема многочастотных многопозиционных сигналов

Следующий патент: Многоканальное устройство информационно-диспетчерской службы

Случайный патент: Устройство для измерения линейных перемещений