Микропрограммный процессор с самоконтролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

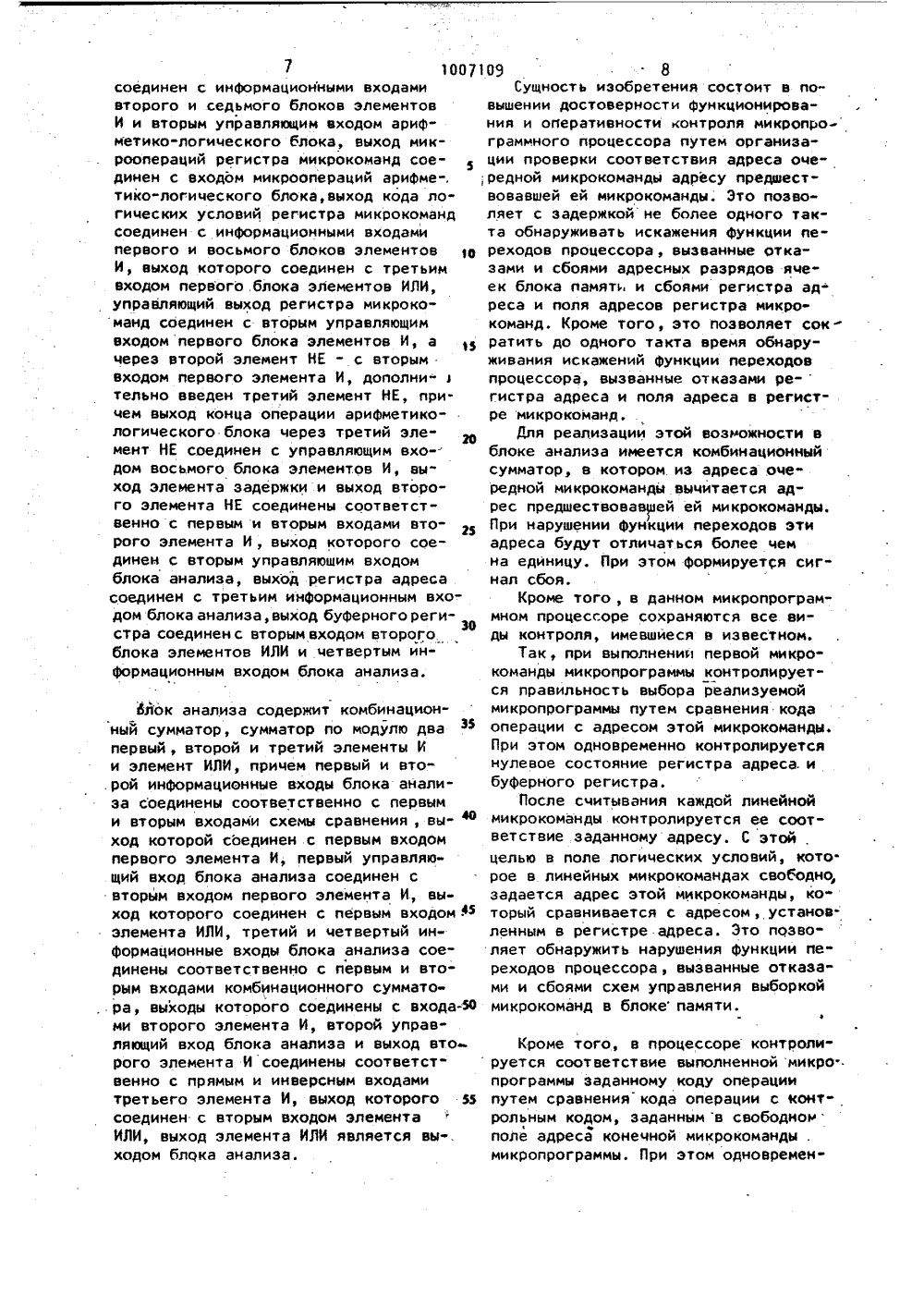

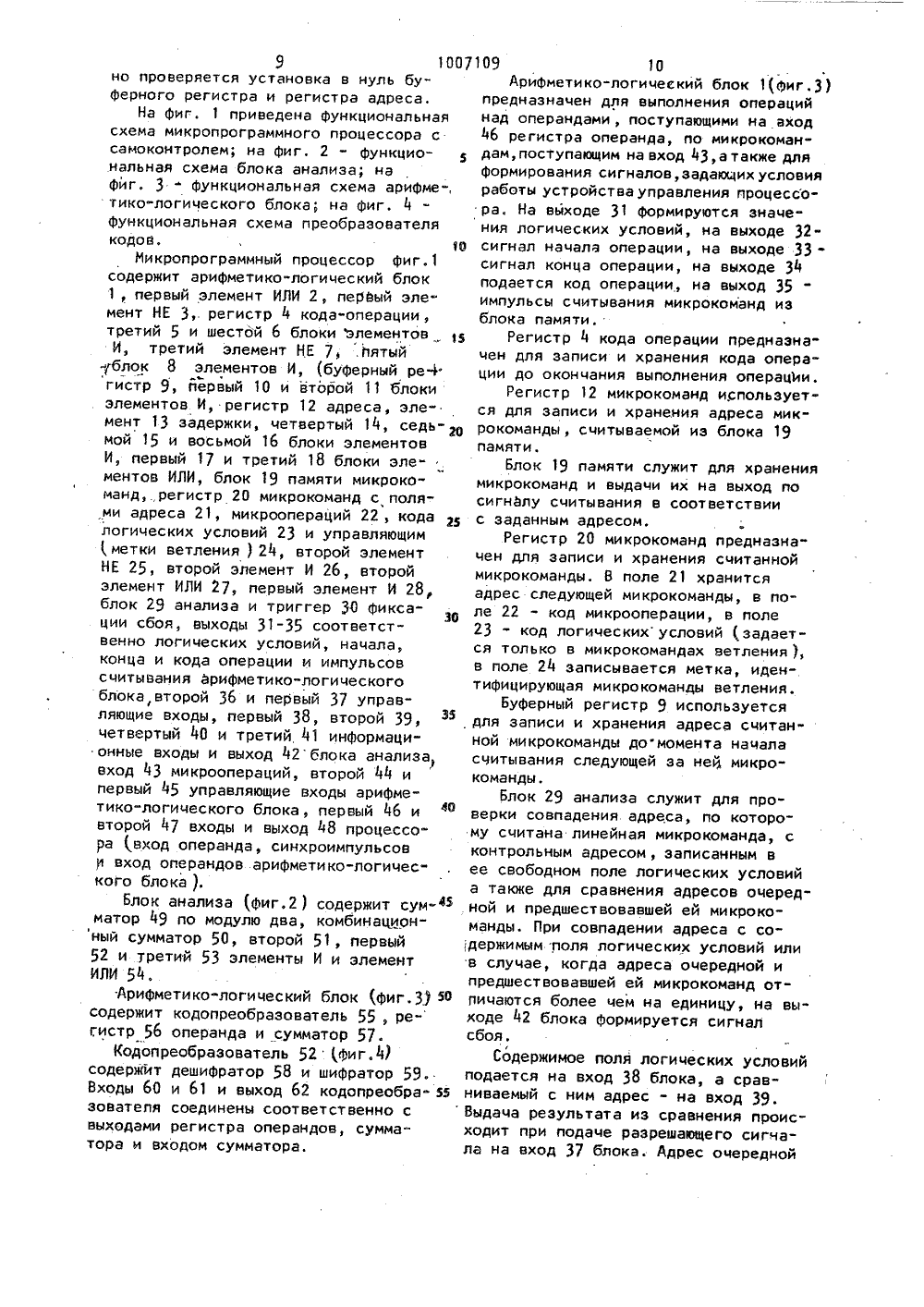

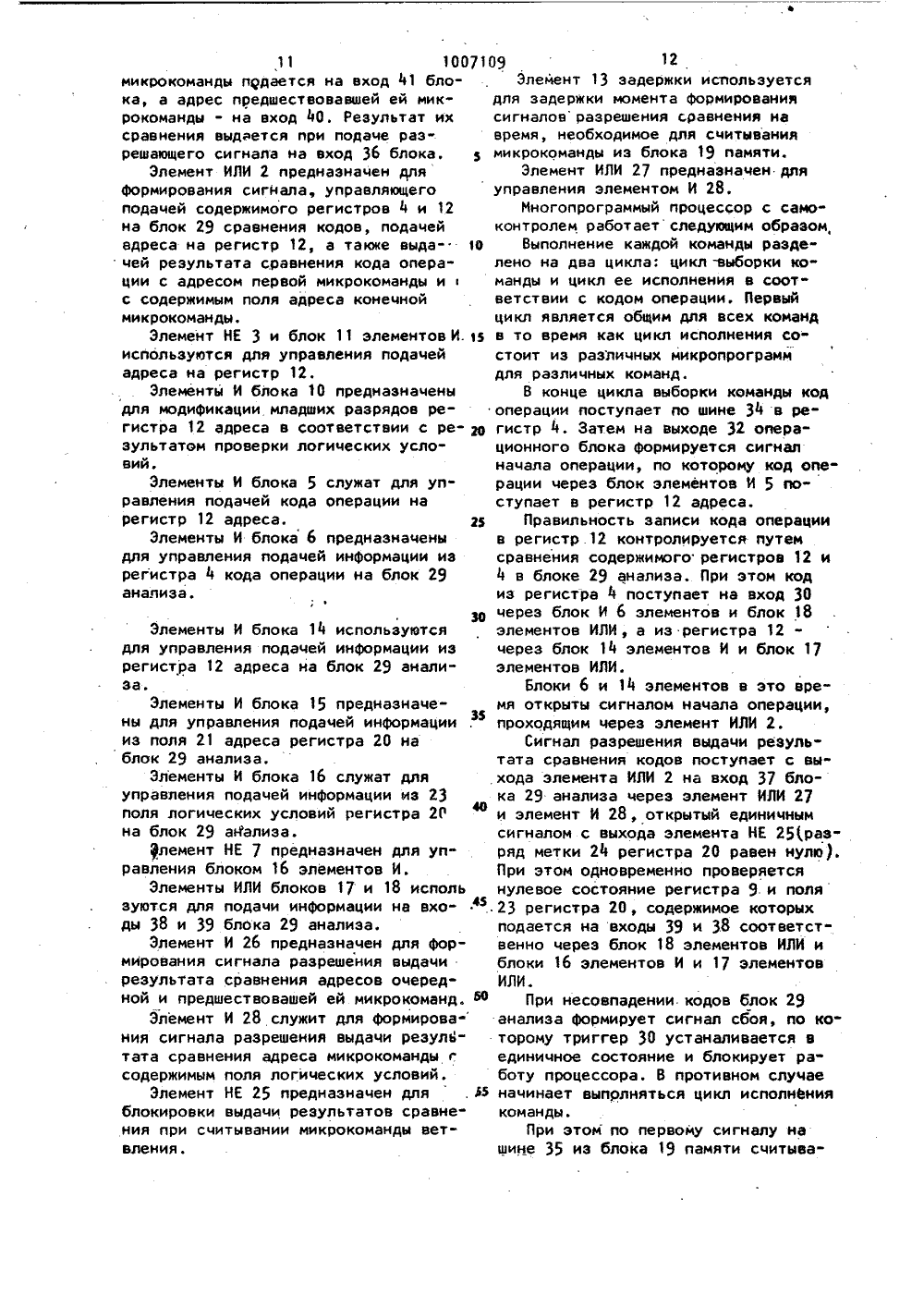

071 СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ РЕСПУБЛИК 19) 0ИЗОБРЕТЕН И К АВТОРСК ВИДЕТЕЛЬСТВ У тов Ис дом буф вертогосоедине дом пер хот хо ер м ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) 1. Авторское свидетельствоСССР И 181036, кл.С 86 Г 9/1,19752. Авторское свидетельство СССР й 512"71, кл. С 06 Г 15/00, 1976.3. Авторское свидетельство СССР . по заявке к". 275670 М,18-2 Ькл. С 06 Г 15/ОО, 1979 (прототип),(54) (57) 1. МИКРОПРОГРАММНЫЙ ПРОЦЕССОР С САМОКОНТРОЛЕМ, содержащий арифметико-логический блок, блок памяти микрокоманд, регистр кода операции, регистр микрокоманд, регистр адреса, буферный регистр, блок анализа, триггер фиксации сбоя, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки элементов И, первый и второй элементы И, первый и второй блоки элементов ИЛИ, первый и второй элементы ИЛИ, первый и второй элементы НЕ и элемент задержки, причем первый и второй входы процессора соединены соответственно с входами операндов и синхро" импульсов арифметико"логического блока, выход операндов которого является выходом процессора, выход логических условий арифжетико"логического блока соединен с первым управляющим входом первого блока элементов Й, выход которого соединен с первым информационным входом регистра адреса, выходы второго и третьего блоков элементов Исоединены соответственно с вторым а) С 06 Г 15/00; С 06 Г 11/ и третьим информационными входами регистра адреса, выход которого соеди"нен с адресным входом блока памятимикрокоманд и информационными входами четвертого и пятого блоков элементов И, выход начала операции арифметико-логического блока соединен с управляющим входом третьего блока элементов И и первым входом первого элемента ИЛИ, выход которого соединен спервым входом второго элемента ИЛИ,управляющими входами четвертого и шестого блоков элементов И, а через первый элемент НЕ - с управляющим входомвторого блока элементов И, выход конца операцииарифметико-логического блоблока соединен с вторым входом перво го элемента ИЛИ, установочными входами регистра адреса, буферного регист-. ра и управляющим входом седьмого .бло" С ка элементов И, выход которого соединен с первым входом первого блока эле Я ментов ИЛИ, выход кода операции ариФ" метико-логического блока соединен с входом регистра кода операции, выход ,которого соединен с информационными входами третьего и шестого блоков эле ментов И, выход управляющих сигналов считывания арифметико-логического бло ка соединен с управляющим входом блока памяти микрокоманд, управляющим входом пятого блока элементов И и через элемент задержки - с вторым вхо" дом второго элемента ИЛИ, выход кото" рого соединен с первым входом первого элемента И, .выход пятого блока элемен оединен с информационны ерного регистра, выходы . и шестого. блоков элемен ны соответственно с вто вого блока элементов ИЛ1007109 Составитель И. Сигаловедактор Т.Кугрцшева Техред О,Неце Корректор,Ю, Макаренко сное иал ППП "Патент",жгород, ул. Проектная Заказ 21 М/72 Тираж 704 ВНИИПИ Государственного к ло делам изобретений и 113035, Москва, Ж, РаувПодитета СССРткрнтийкая наб., 100 вым входом второго блока элементов ИЛИ, выходы которых соединены соот" Ьетственно с первым и вторым информационньЪи входами блока анализа, выход первого элемента И соединен с пер. вым управляющим входом блока анализа, выход которого соединен с входом триггера фиксации сбоя, выход которого соединен с первым управляющим входом арифметико-логического блока, выход блока памяти микрокоманд соединен с входом регистра микрокоманд, выход адреса которого соединен с информационными входами второго и седьмого блоков элементов И и вторым управляющим.входом арифметико-логического блока, выход микроопераций регистра микрокоманд соединен с входом микро" операций арифметико-логического блока, выход кода логических условий . регистра микрокоманд соединен с информационными входами первого и восьмого блоков элементов И, выход которого соединен с третьим входом пер" вого блока элементов ИЛИ, управляющий выход регистра микрокоманд соединен с вторым управлядщим входом первого бло ка элементов И, а через второй элемент НЕ - с вторым входом первого элемента И, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности Функционирования и оперативности контроля, введен третий элемент НЕ причем выход конца операции ариф метико-логического баока через третий элемент НЕ соединен с управляющим входом восьмого блока элементов И, выл ход элемента задержки и выход второго 7109элемента НЕ соединен с первым и вторым входами второго элемента И, выход которого соединен с вторым управляющим входом блока анализа, выход ре гистра адреса соединен с третьим информационным входом блока анализа,выход буферного регистра соединен с вторым входом второго блока элементов ИЛИ и четвертым управляющим входом блока анализа. 2. Процессор по и,1, о т л ич а ю щ и й с я тем, что блок анализа содержит комбинационыый сумматорсхему сравнения, первый, второй итретий элементы И, и элемент ИЛИ,причем первый и второй информационные входы блока анализа соединенысоответственно с первым и вторым входами схемы сравнения, выход которойсоединен с первым входом первогоэлемента И, первый управляющий входблока анализа соединен с вторым входом первого элемента И,выход которого соединен с первым вхадом элемента ИЛИ, третий и четвертый информациоиные входы блока анализа соединены соответственно с первым и вторымвходами комбинационного сумматора,выходы которого соединены с входамивторого элемента И; второй управляющий вход блока анализа и выход второго элемента И соединены соответственно с прямым и инверсным входамитретьего элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход элемента ИЛИ являетсявыходом блока анализа, 1Изобретение относится к цифровой вычислительной технике и может быть использовано при построении самоконтролируемых процессоров ЭВИ с микропрограммным управлением.%Известны микропрограммные процессоры с контролем, содержащие операционный блок, блок памяти микрокоманд, регистры адреса и микрокоманд, блок сравнения, триггер фиксации 1 сбоя, логические элементы И, ИЛИ,НЕ Г 11, 2. 2Недостатками этих устройств являются низкие достоверность функционирования и оперативность контроля.Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому является микропрограммный процессор с самоконтролем, содержащий блок памяти микрокоманд, арифметико-логический блок, регистр кода операции микрокоманд, регистр адреса, буферный регистр, блок анализа, триггер фикса3 007 ции сбоя, элементы И, ИЛИ, ЙЕ и.элемент задержки причем первый выход арифметико-логического блока через первый элемент И соединен с первым входом регистра адреса, выход которого соединен с первыми входами второго и третьего элементов И и блока памяти, выход которого соединен с входом регистра микрокоманд, первый выход которого соед 1 нен с первым входом 10 арифметико-логического блока, а также. через четвертый элемент И и первый элемент ИЛИ с первым входом блока ана-. лиза, а через пятый элемент И с вторым входом регистра адреса, третий 15 вход которого соединен с вторыми выходами арифметико-логического блока и четвертого элемента И, с первым входом буферного регистра, а также через второй элемент ИЛИ и первый элемент НБ с вторым входом пятого элемента И, второй выход регистра микрокоманд сое динен с вторым входом арифметико-логи. ческого блока, третий выход которого соединен с входом регистра кода операций, выход которого соединен через шестой элемент И с четвертым входом регистра адреса, а через седьмой элемент И и третий элемент ИЛИ - с вторым входом блока анализа, выход которого соединен с единичным входом триггера сбоя, единичный выход которого соединен с третьим входом арифметикологического блока, четвертый выход которого соединен с вторыми входами второго элемента ИЛИ и шестого элемента И, третий выход регистра микро- команд соединен с вторым входом пер" вого элемента И,. а через восьмой элемент И, с вторым входом первого элемента ИЛИ, пятый выход арифметико-логического блока соединен с вторыми входами блока памяти и второго.элемента И, выход которого соединен с вторым входом буферного регистра, а через элемент задержки, четвертый элемент ИЛИ и девятый элемент И пятый выход операционного блока соединен с третьим входом блока анализа четвертый выход регистра микрокоманд соединен стретьеим входомпервого эле-:.5 О мента И, а через второй элемент НЕ " с вторым входом девятого элемента И, выход второго элемента ИЛИ соединен с вторыми входами четвертого элемента ИЛИ, седьмого и третьего элемен та И, выход которого соединенс третьим входом первого элемента ИЛИ. 309 ЛВ указанном процессоре с целью повышения достоверности функционирования и оперативности контроля осуществляется контроль правильности выбора реализуемой микропрограммы пу" тем сравнения кода операции и адреса первой считываемой микрокоманды, а также осуществляется контроль соответствия каждой считанной, линейной микрокоманды ее адресу путем сравнения этого адреса с контрольным адре" сом, задаваемым в свободном поле логических условий линейных микроко" манд, Кроме того, в процессоре контролируется соответствие выполненной микропрограммы заданному коду операции путем сравнения кода операции с контрольным кодом, задаваемым в свободном поле адреса конечной микрокоманды микропрограммы 3,Недостатками известного процессора являются низкие достоверность Функционирования и оперативностьконтроля,Низкая достоверность функционирования обусловлена тем, что средствами контроля процессора не обнаруживаются искажения адресов микрокоманд, вызванные отказами и сбоямиадресных разрядов ячеек блока памяти, а также сбоями регистра адресаили поля адреса регистра микрокоманд. Исключение составляют лишь теискажения, которые приводят к переходу в зону адресов микрокоманд,принадлежащих микропрограмме с другим кодом операции, и которые в про"цессоре могут быть обнаружены присравнении кода операции с содержимым поля адреса конечной микрокоманды микропрограммы.Вследствие этого в процессоре возможен пропуск микрокоманд, нарушениепорядка их выполнения, а также переход к реализации микрокоманд, не принадлежащих реализуемой микропрограмме, т.е, возможно нарушение функциипереходов. Контроль правильности считывания микрокоманд, реализуемый впроцессоре путем сравнения адреса, покоторому считана микрокоманда, с адресом, которыи записан в свободномполе логических условий, позволяетобнаружить лишь те нарушения функциипереходов, которые вызваны отказамии сбоями схем управления выборки вблоке памяти.Нарушения Функции переходов, выз"ванные отказами регистра адреса или5поля адреса, регистра микрокоманд, впроцессоре могут быть косвенно об"наружены при сравнении кода операции с содержимым поля адреса конечной микрокоманды микропрограммы, Этовозможно благодаря тому, что отказыполя адреса регистра микрокоманд приводят к искажению содержимого поляадреса конечной микрокоманды, а отказы регистра адреса искажают нулевсе состояние этого регистра при установке его в нуль, вследствие чего его содержимое, складываясь с содержимым поля адреса регистра микрокоманд, искажает записанный в этом 13поле код.Таким образом, отказы регистра адреса и поля адреса регистра микро"команд, а также некоторые отказы исбои адресных разрядов ячеек памяти щобнаруживаются лишь в конце выполнения, микропрограммы, а не в момент их, возникновения, чем обуславливаетсянизкая оперативность контроля.,Низкая оперативность контроля обу-Иславливает также и низкую глубинудиагностирования указанного микропрограммного,. процессора, так как вмомент обнаружения отказа отсутствует информация о моменте его возникно-Зрвения и состоянии аппаратуры. Это ограничивает применение известного процессора в системах, работающих в режиме реального времени.Целью изобретения является повышение достоверности функционирования иоперативности контроля микропрограммного процессора.Поставленная цель достигается тем,что в микропрограммный процессор ссамоконтролем, содержащий арифметикологический блок, блок памяти микрокоманд, регистр кода операции, регистр микрокоманд, регистр адреса, буферный регистр, блок анализа, триггерфиксации сбоя, первый, второй, третийчетвертый, пятый, шестой, седьмой ивосьмой блоки элементов И, первый ивторой элементы И, первый и второйблоки элементов ИЛИ, первый и второйэлементы ИЛИ, первый и второй элементы НЕ и элемент задержки, причемпервый и второй входы процессора соединены соответственно с входами операндов и синхроимпульсов арифметикологического блока, выход операндовкоторого является выходом процессора,выход логических условий арифметикологического блока соединен с первым 09 6управляющим входом первого блока элементов И, выход которого соединен спервым информационным входом регистра адреса, выходы второго и третьегоблоков элементов И соединены соответственно с вторым и третьим информационными входами регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд и информационными входами четвертого и пятого блоков элементов И, выход началаопераций арифметико-логического блока соединен с управляющим входом третьего блока элементов И и первым,вхо"дом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, управляющими входами четвертого и шестого блоков элементов И, а через первый элемент НЕс управляющим входом второго блокаэлементов И, выход конца операцииарифметико-логического блока соединенс вторым входом первого элемента ИЛИ,установочными входами регистра адресабуферного регистра и управляющим входом седьмого блока элементов И, выходкоторого соединен с первым входомпервого блока элементов ИЛИ, выходкода операции арифметико-логическогоблока соединен с входом регистра кода операции, выход которого соединенс информационными входами третьегои шестого блоков элементов И, выходуправляющих сигналов считывания арифметико логического блока соединен суправляющим входом блока памяти микрокоманд, управляоиим входом пятогоблока элементов И и через элемент задержки - с вторым входом второго элемента ИЛИ, выход которого соединен спервым входом первого элемента И, выход пятого блока элементов И соединенс информационным входом буферного регистра, выходы четвертого и шестогоблоков элементов И соединены соответственно с вторым входом первого блока элементов ИЛИ и первым входом вто"рого блока элементов ИДИ, выходы которых соединены соответственно с первым и вторым информационными входами блока анализа, выход первого элемента И соединен с первым управляющимвходом блока анализа, выход которогосоединен с входом триггера фиксациисбоя, выход которого соединен с первым управляющим входом арифметико-логического блока, выход блока памятимикрокоманд соединен с входом регист-,ра микрокоманд, выход адреса которого1007103 соединен с информационными входамивторого и седьмого блоков элементовИ и вторым управляющим входом арифметико-логического блока, выход микроопераций регистра микрокоманд соединен с входом микроопераций арифме-,тико-логического блока, выход кода логических условий регистра микрокомандсоединен с информационными входамипервого и восьмого блоков элементовИ, выход которого соединен с третьимвходом первого .блока элементов ИЛИ,управляющий выход регистра микрокоманд соединен с вторым управляющимвходомпервого блока элементов И, ачерез второй элемент НЕ - с вторымвходом первого элемента И, дополнительно введен третий элемент НЕ, причем выход конца операции арифметикологического блока через третий элемент НЕ соединен с управляющим вхо-дом восьмого блока элементов И, выход элемента задержки и выход второго элемента НЕ соединены соответственно с первым и вторым входами второго элемента И, выход которого соединен с вторым управляющим входомблока анализа, выход регистра адресасоединен с третьим информационным входом блока анализа, выход буферного регистра соединенс вторым входом второго.блока элементов ИЛИ и четвертым инФормационным входом блока анализа. Блок анализа содержит комбинационный сумматор, сумматор по модулю два зф первый, второй и третий элементы К и элемент ИЛИ, причем первый и вто.рой информационные входы блока анализа соединены соответственно с первым и вторым входами схемы сравнения, вы в ход которой соединен с первым входом первого элемента И, первый управляющий вход блока анализа соединен с вторым входом первого элемента И, выход которого соединен с первым входом фф элемента ИЛИ, третий и четвертый информационные входы блока анализа соединены соответственно с первым и вторым входами комбинационного сумматора, выходы которого соединены с входами второго элемента И, второй управляющий вход блока анализа и выход второго элемента И соединены соответственно с прямым и инверсным входами третьего элемента И, выход которого м соединен с вторым входом элемента ИЛИ, выход элемента ИЛИ является вы-, ходом блока анализа. ВСущность изобретения состоит в повышении достоверности Функционирования и оперативности контроля микропрограммного процессора путем организации проверки соответствия адреса оче,редной микрокоманды адресу предшествовавшей ей микрокоманды, Это позволяет с задержкой не более одного такта обнаруживать искажения функции переходов процессора, вызванные отказами и сбоями адресных разрядов ячеек блока память и сбоями регистра ад- реса и поля адресов регистра микро- команд. Кроме того, это позволяет сократить до одного такта время обнаруживания искажений функции переходов процессора, вызванные отказами регистра адреса и поля адреса в регистре микрокоманд.Для реализации этой воэможности в блоке анализа имеется комбинационный сумматор, в котором. из адреса оче" редной микрокоманды вычитается адрес предшествовавшей ей микрокоманды, При нарушении функции переходов эти адреса будут отличаться более чем на единицу. При этом Формируется сиг" нал сбоя.Кроме того, в данном микропрограммном процессоре сохраняются все виды контроля, имевшиеся в известном.Так, при выполнении первой микро- команды микропрограммы контролирует" ся правильность выбора реализуемой микропрограммы путем сравнения кода операции с адресом этой микрокоманды. При этом одновременно контролируется нулевое состояние регистра адреса. и буферного регистра.После считывания каждой линейной микрокоманды контролируется ее соответствие заданному адресу. С этой, целью в поле логических условий, которое в линейных микрокомандах свободно, задается адрес этой микрокоманды, ко" торый сравнивается с адресом, установленным в регистре адреса. Это поэво" ляет обнаружить нарушения Функции пе" реходов процессора, вызванные отказа" ми и сбоями схем управления выборкой микрокоманд в блоке памяти.е Кроме того, в процессоре контролируется соответствие выполненной микро . программы заданному коду операции путем сравнения кода операции с монт" рольным кодом, заданным в свободномФполе адреса конечной микрокоманды . микропрограммы. При этом одновремен1007109 но проверяется установка в нуль бу" ферного регистра и регистра адреса.На фиг. 1 приведена функциональная схема микропрограммного процессора с самоконтролем; на фиг. 2 - функциональная схема блока анализа; нафиг. 3 " функциональная схема арифме-, тико-логического блока; на фиг.функциональная схема преобразователя кодов, ОИикропрограммный процессор фиг.1 содержит арифметико-логический блок 1, первый элемент ИЛИ 2, первый элемент НЕ 3, регистр 4 кода-операции, третий 5 и шестой 6 блоки ,элементовИ, третий элемент НЕ 7, .пятый -блок 8 элементов И, (буферный ре+ гистр 9 йервый 10 и второй 11 блоки элементов И, регистр 12 адреса, элемент 13 задержки, четвертый 14, седь-мой 15 и восьмой 16 блоки элементов И, первый 17 и третий 18 блоки эле" ментов ИЛИ, блок 19 памяти микрокоманд,. регистр 20 микрокоманд с полями адреса 21, микроопераций 22, кода логических условий 23 и управляющимметки ветления ) 24, второй элемент НЕ 25, второй элемент И 26, второй элемент ИЛИ 27, первый элемент И 28, блок 29 анализа и триггер 30 фиксации сбоя, выходы 31-35 соответственно логических условий, начала, конца и кода операции и импульсов считывания арифметико-логического блока, второй 36 и первый 37 управляющие входы, первый 38, второй 39, четвертцй 40 и третий 41 информационные входы и выход 42 блока анализа, вход 43 микроопераций, второй 44 и первцй 45 управляющие входы арифметико-логического блока, первый 46 и ф второй 47 входы и выход 48 процессора вход операнда, синхроимпульсоввход операндов.арифметико-логического блока ).Блок анализа фиг,2 ) содержит сумматор 49 по модулю два, комбинационный сумматор 50, второй 51, первый 52 и третий 53 элементы И и элемент ИЛИ 54.Арифметико-логический блок фиг3) о содержит кодопреобразователь 55, регистр 56 операнда и сумматор 57.Кодопреобразователь 52 фиг.4) содержит дешифратор 58 и шифратор 59. Входц 60 и 61 и выход 62 кодопреобра зоватепя соединены соответственно с выходами регистра операндов, сумматора и входом сумматора. 1 ОРрифметико-логический блок 1(фиг3)предназнацен для выполнения операцийнад операндами, поступающими на вход46 регистра операнда, по микрокоман"дам,поступающим на вход 43,атакже дляформирования сигналов,задаюцих условияработы устройствауправления процессора. На выходе 3 Формируются значения логических условий, на выходе 32 сигнал начала операции, на выходе 33 сигнал конца операции, на выходе 34подается код операции, на выход 35 импульсы считывания микрокоманд изблока памяти.Регистр 4 кода операции предназначен для записи и хранения кода операции до окончания выполнения операции.Регистр 12 микрокоманд используется для записи и хранения адреса микрокоманды, считываемой из блока 19памяти.Блок 19 памяти служит для хранениямикрокоманд и выдачи их на выход посигналу считывания в соответствиис заданным адресом.Регистр 20 микрокоманд предназначен для записи и хранения считанноймикрокоманды. В поле 21 хранитсяадрес следующей микрокоманды, в поле 22 - код микрооперации, в поле23 - код логических условийзадается только в микрокомандах ветления ),в поле 24 записывается метка, идентифицирующая микрокоманды ветления.Буферный регистр 9 используетсядля записи и хранения адреса считанной микрокаманды до"момента началасчитывания следующей за ней микрокоманды,Блок 29 анализа служит для проверки совпадения адреса, по которому считана линейная микрокоманда, сконтрольным адресом, записанным вее свободном поле логических условийа также для сравиения адресов очередной и предшествовавшей ей микрокоманды. При совпадении адреса с со;держимым поля логических условий илив случае, когда адреса очередной ипредшествовавшей ей микрокоманд отпичаются более чем на единицу, на выходе 42 блока Формируется сигналсбоя,РСодержимое поля логических условийподается на вход 38 блока, а сравниваемый с ним адрес - на вход 39.Выдача результата из сравнения происходит при подаче разрешающего сигнала на вход 37 блока. Адрес оцередной30Элементы И блока 14 используется для управления подачей информации из регистра 12 адреса на блок 29 анали" за.Элементы И блока 15 предназначе" ны для управления подачей информации из поля 21 адреса регистра 20 на блок 29 анализа.Элементы И блока 16 служат для управления подачей информации из 23 поля логических условий регистра 2 Р на блок 29 анализа.лемент НЕ 7 предназначен для управления блоком 16 элементов И.Элементы ИЛИ блоков 17 и 18 исполь зуются для подачи информации на вхо- ф ды 38 и 39 блока 29 анализа.Элемент И 26 предназначен для формирования сигнала разрешения выдачи результата сравнения адресов очередной и предшествовашей ей микрокоманд. 9Элемент И 28 служит для формирова- ния сигнала разрешения выдачи резуль- тата сравнения адреса микрокоманды г содержимым поля логических условий.Элемент НЕ 25 предназначен для.И блокировки выдачи результатов сравнения при считывании микрокоманды ветвления. 11 10071 микрокоманды пддается на вход 41 блока, а адрес предшествовавшей ей микрокоманды - на вход 40. Результат их сравнения выдается при подаче разрешающего сигнала на вход 36 блока.Элемент ИЛИ 2 предназначен для формирования сигнала, управляющего подачей содержимого регистров 4 и 12 на блок 29 сравнения кодов, подачей вдреса на регистр 12, а также выда е чей результата сравнения кода операции с адресом первой микрокоманды ис содержимым поля адреса конечной микрокоманды.Элемент НЕ 3 и блок 11 элементов И. 1 з используются для управления подачей адреса на регистр 12.Элементы И блока 10 предназначены дпя модификации младших разрядов регистра 12 адреса в соответствии с ре- щ зультатом проверки логических условий.Элементы И блока 5 служат для управления подачей кода операции на регистр 12 адреса. 2Элементы И блока 6 предназначены для управления подачей информации из регистра 4 кода операции на блок 29 анализа. 09Элемент 13 задержки используетсядля задержки момента формированиясигналов разрешения сравнения навремя, необходимое для считываниямикрокоманды из блока 19 памяти,Элемент ИЛИ 27 предназначен дляуправления элементом И 28,Многопрограммый процессор с самоконтролем работает следующим образом,Выполнение каждой команды разде"лено на два цикла: цикл .выборки ко"манды и цикл ее исполнения в соот"ветствии с кодом операции, Первыйцикл является общим для всех командв то время как цикл исполнения состоит из различных микропрограммдля различных команд.В конце цикла выборки команды кодоперации поступает по шине 34 в регистр 4. Затем на выходе 32 операционного блока формируется сигналначала операции, по которому код операции через блок элементов И 5 поступает в регистр 12 адреса.Правильность записи кода операциив регистр 12 контролируется путемсравнения содержимого регистров 12 и4 в блоке 29 анализа. При этом кодиз регистра 4 поступает на вход 30через блок И 6 элементов и блок 18элементов ИЛИ, а из регистра 12через блок 14 элементов И и блок 17элементов ИЛИ.блоки 6 и 14 элементов в это время открыты сигналом начала операции,проходящим через элемент ИЛИ 2.Сигнал разрешения выдачи результата сравнения кодов поступает с вы",хода элемента ИЛИ 2 на вход 37 блока 29 анализа через элемент ИЛИ 27и элемент И 28, открытый единичнымсигналом с выхода элемента НЕ 25 разряд метки 24 регистра 20 равен нулю).При этом одновременно проверяетсянулевое состояние регистра 9 и поля.23 регистра 20, содержимое которыхподается на входы 39 и 38 соответст"венно через блок 18 элементов ИЛИ иблоки 16 элементов И и 17 элементовИЛИ.При несовпадении кодов блок 29анализа формирует сигнал сбоя, по которому триггер 30 устаналивается вединичное состояние и блокирует ра"боту процессора, В противном случаеначинает выпрлняться цикл исполнениякоманды.При этом по первому сигналу нашине 35 из блока 19 памяти считыва13 10071 ется первая микрокоманда, которая записывается в регистр 20 микрокоманд, Так как в ходе выполнения микропрограммы сигнала начала и конца операции на шинах 32 и 33 отсутствуют, то на выходе элемента НЕ 3 сохраняется единичный сигнал, открывающий блок 11 элементов И. Через этот блок в регистр12 с поля 21 регистра 20 поступает адрес А 1.1+ очередной микрокоманды, 0При считывании микрокоманды прове.ряется соответствие ее тому адресу .А который был задан в регистре 12, Для осуществления проверки этот адрес в начале такта считывания по сигналу 15 на шине 35 записывается в регистр 9 и подается с него на вход 39 блока 29 анализа. 8 поле логических условий 23 регистра 20 при правильном считывании линейной микрокоманды дол жен быть записан ее адрес А , а в поле 24 метки должен быть нуль. Содержимое поля логических условий 23 пода ется на вход 38 блока 29 анализа через открытый блок 16 элементов И и блок 17 элементов ИЛИ и сравнивается с содержимым регистра 9 . Сигнал, разрешающий сравнение, подается на вход 37 блока 29 анализа через элемент ИЛИ 27 и открытый элемент И 28 с выхода элемента 3 задержки, Результат сравнения фиксируется триггером 30. Таким образом контролируется работа регистра 12, схем управления выборкой микрокоманд и поля логических условий блока 19 памяти, а также поля 23 регистра 20. Одновременнно контролируется работа блока элементов И 8 регистра 9, блоков 16 элементов И и 17 элементов ИЛИ, относящихся к. контрольному оборудованию.46Кроме того, при считывании микрокоманды контролируется функция переходов процессора путем проверки соответствия адреса А очередной микрокоманды адресы А считанной микро- команды. 8 качестве контрольного признака используется величина разности адресов А; и А . Так как проверка осушествляется только для линейных микрокоманд, адреса которых зако- О дированы последовательно, то для соседних микрокоманд величина этой разности не может превышать единицу,Адрес А подается на вход 40 блока 29 анализа из регистра 9, а адрес А;+ - на вход 41 этого блока с выхода регистра 12. Сигнал., разрещающий сравнение, подается на вход 09 1436 блока 29 анализа с,выхода эле"мента 13 задержки через элемент И 26.Если сравниваемые адреса отличаютсяболее чем на единицу, на выходе 42блока 29 анализа формируется сигнал сбоя.Таким образом контролируется ра-"бота поля адреса блока 19 памяти,по-ля 22 регистра 20, а также регистра12,При отсутствии сбоев на шине 35появляется следующий сигнал считывания, по которому аналогично вышеопи-.всанному из блока 12 памяти по адресу,установленному в регистре 12, считывается следующая микрокоманда и осуществляется сравнение ее адреса с со-держимым поля 23 логических. условийи с адресом следующей микрокоманды,считанным из блока 9 памяти в регистр 12.Если считаннная микрокоманда является условной микрокомандой ветвления, то в поле 24 метки записываетсяединица, По сигналу с поля 24-меткизапираются элементы И 26 и 28, запрещая сравнение адресов в блоке 29 анализа. а также отпиоается блок 1 Оэлементов И,который в соответствии созначениями логическихусловий на шине31 модифицирует младшие разряды регистра 12, заданные в поле 23 логических условий.После считывания конечной микрокоманды реализуемой микропрограммы иосуществления вышеописанных проверокна шине 33 формируется сигнал концаоперации по которому регистры 12 и 9обнуляется, а блок 29 анализа сравнивает код операции, установленный нарегистре 4, с содержимым поля 21 адреса регистра 20. В этом поле записан код выполненной операции.Содержимое регистра 4 подается навход 39 блока 29 анализа через блок18 элементов ИЛИ и блок 6 элементов И, открытый сигналом с выхода2 элемента ИЛИ.Содержимое поля 21 адреса подается на вход 38 блока 29 анализа черезблок 17 элементов ИЛИ и блок 15 элементов И, открытый сигналом с шины 33 Кроме того, через блок 1 о элементов ИЛИ на вход 39 блока подается содержимое регистра 9а на вход 38 через блок 17 элементов ИЛИ и открытый блок 14 элементов И подается содержимое регистра 12.15 10071Если суммарный код регистра 4 кода операции и регистра 9 равен суммарному коду, установленному в поле 21 адреса, регистра 20 и в регистре 12 адреса, то это означает, чтл микропрограмма выполнена в соо-ветствии с заданным кодом операции, а регистры 9 и 12, работоспособны и установлены в нуль. В этом случае процессор переходит к выполнению цикла 1 ф выборки следующей команды.Если же сравниваемые коды не равны, то это означает или сбой какого- либо из регистров 4,9,12 или поля 21 регистра 20, либо несоответствие вы з полненной микропрограммы заданному коду операции. В этом случае блок 29 анализа формирует сигнал сбоя, по которому процессор переходит к пов 09 16торению участка микропрограммы или к поиску места отказа.Таким образом, в предлагаемом микропрограммном процессоре наряда с контролем правильности начала и конца выйолнения микропрограммы и работы схем управления выборкой микро" команд из блока памяти, имеввим место в известном, осуществляется контроль правильности задания адреса каждой очередной микрокоманды.Исключение составляют адреса лищь тех микрокоманд, которые следуют за микрокомандами ветвления.екроме того, полностью сохраняется свойство самопроверяемости элементов процессора, входящих в состав контрольного оборудования.

СмотретьЗаявка

3236793, 08.12.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор, самоконтролем

Опубликовано: 23.03.1983

Код ссылки

<a href="https://patents.su/11-1007109-mikroprogrammnyjj-processor-s-samokontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор с самоконтролем</a>

Предыдущий патент: Реконфигурируемое устройство с программным управлением

Следующий патент: Устройство для оперативного контроля готовности слитков к освобождению от изложниц

Случайный патент: Дренажное устройство