Программируемый управляющий модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

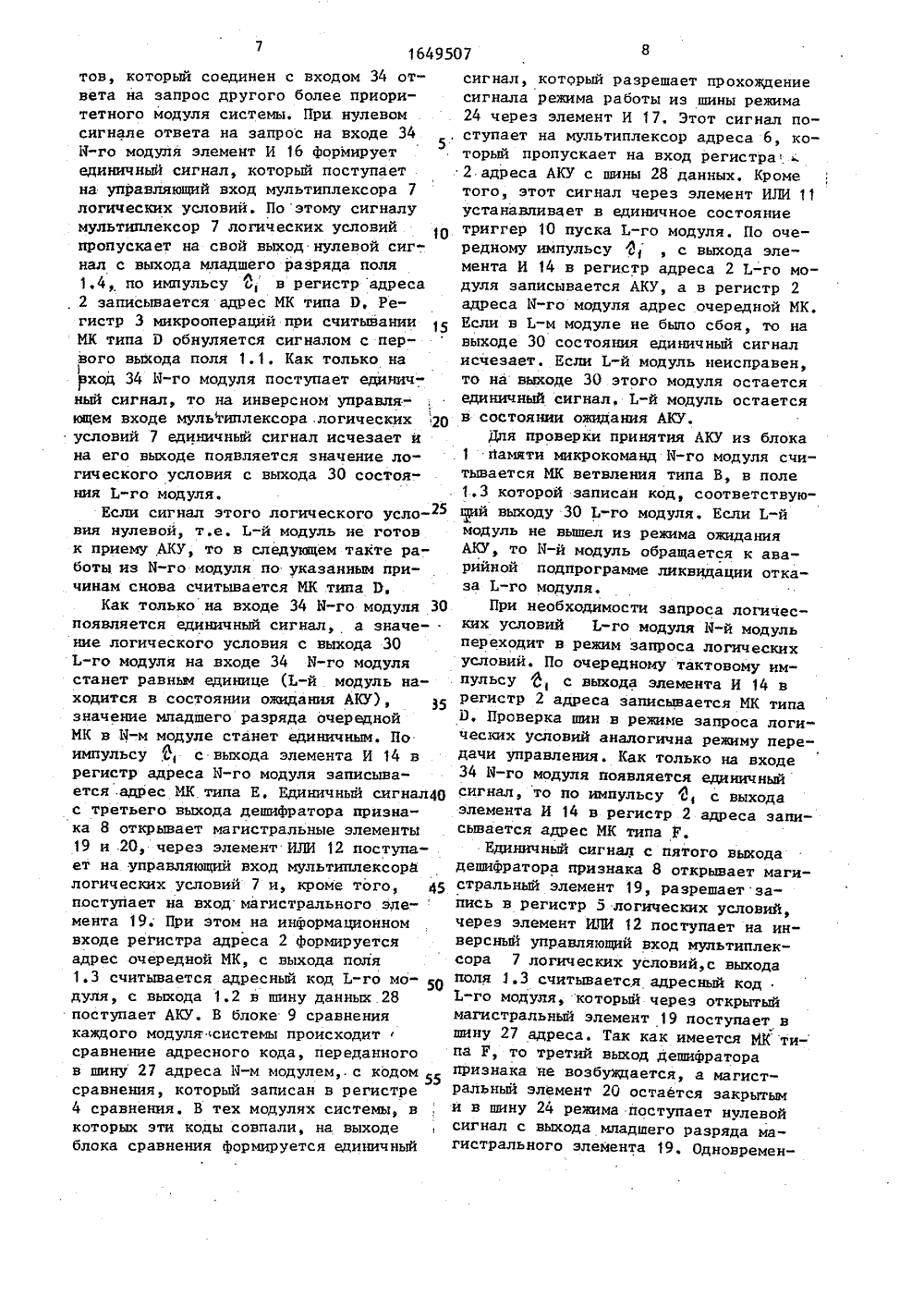

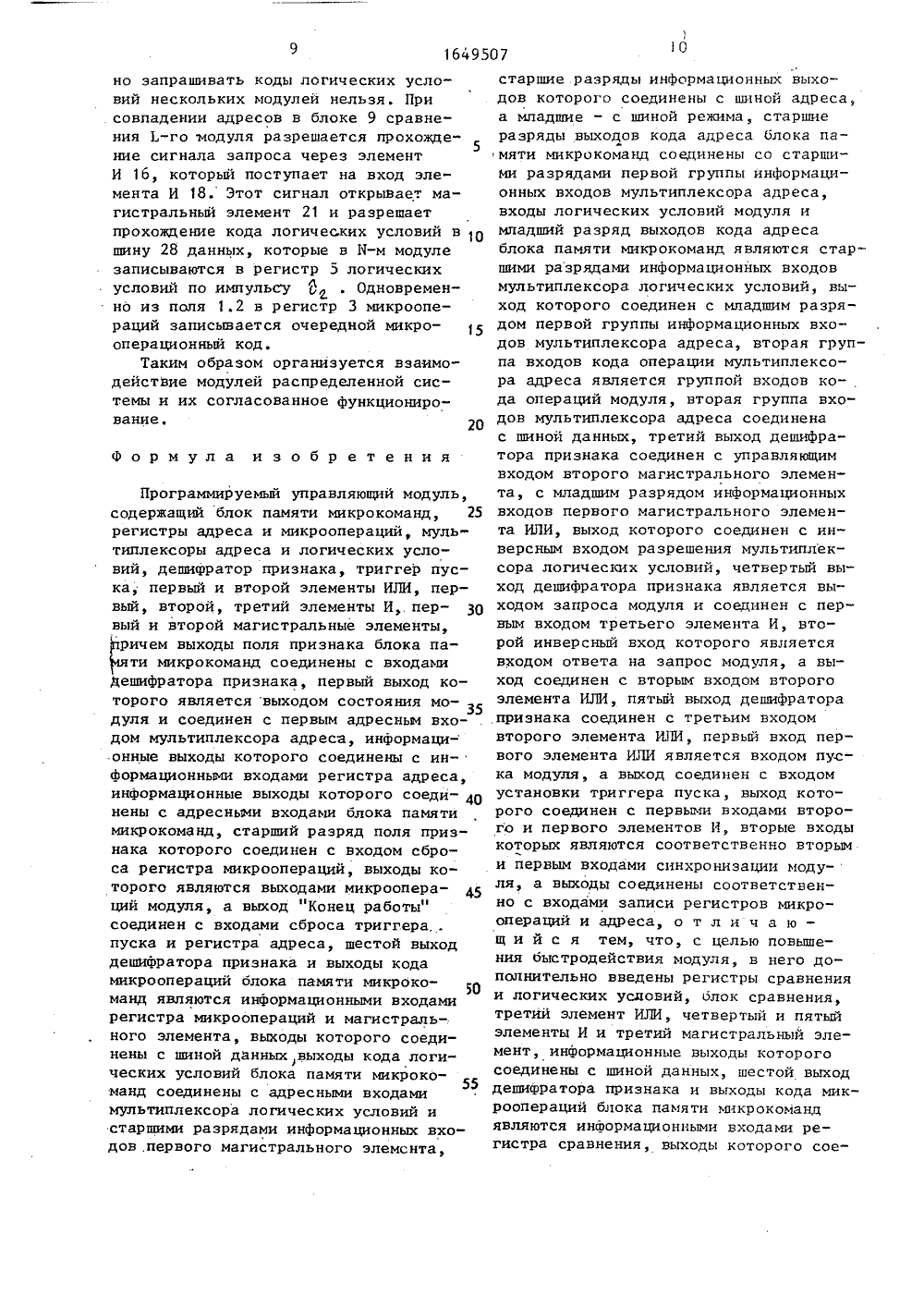

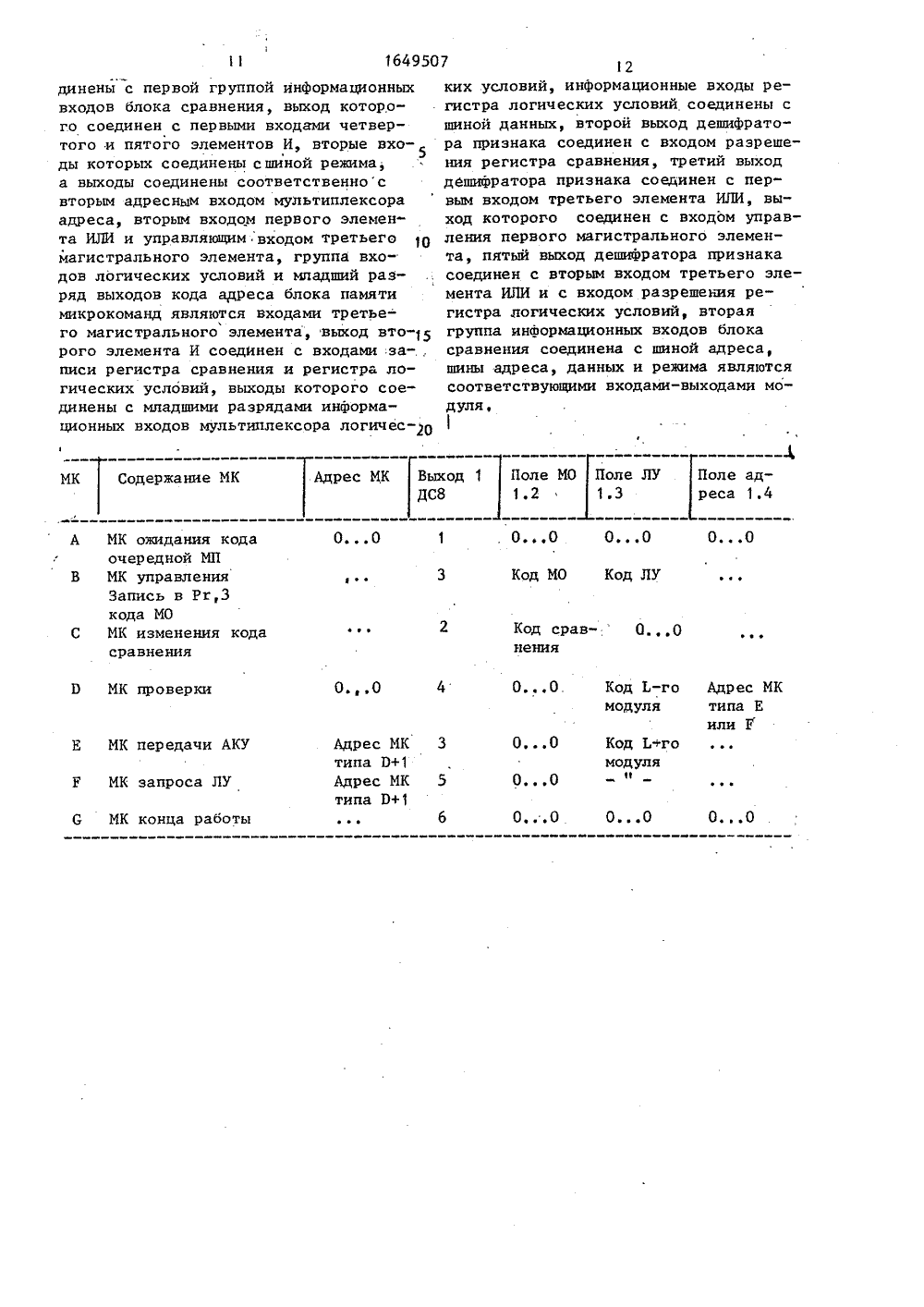

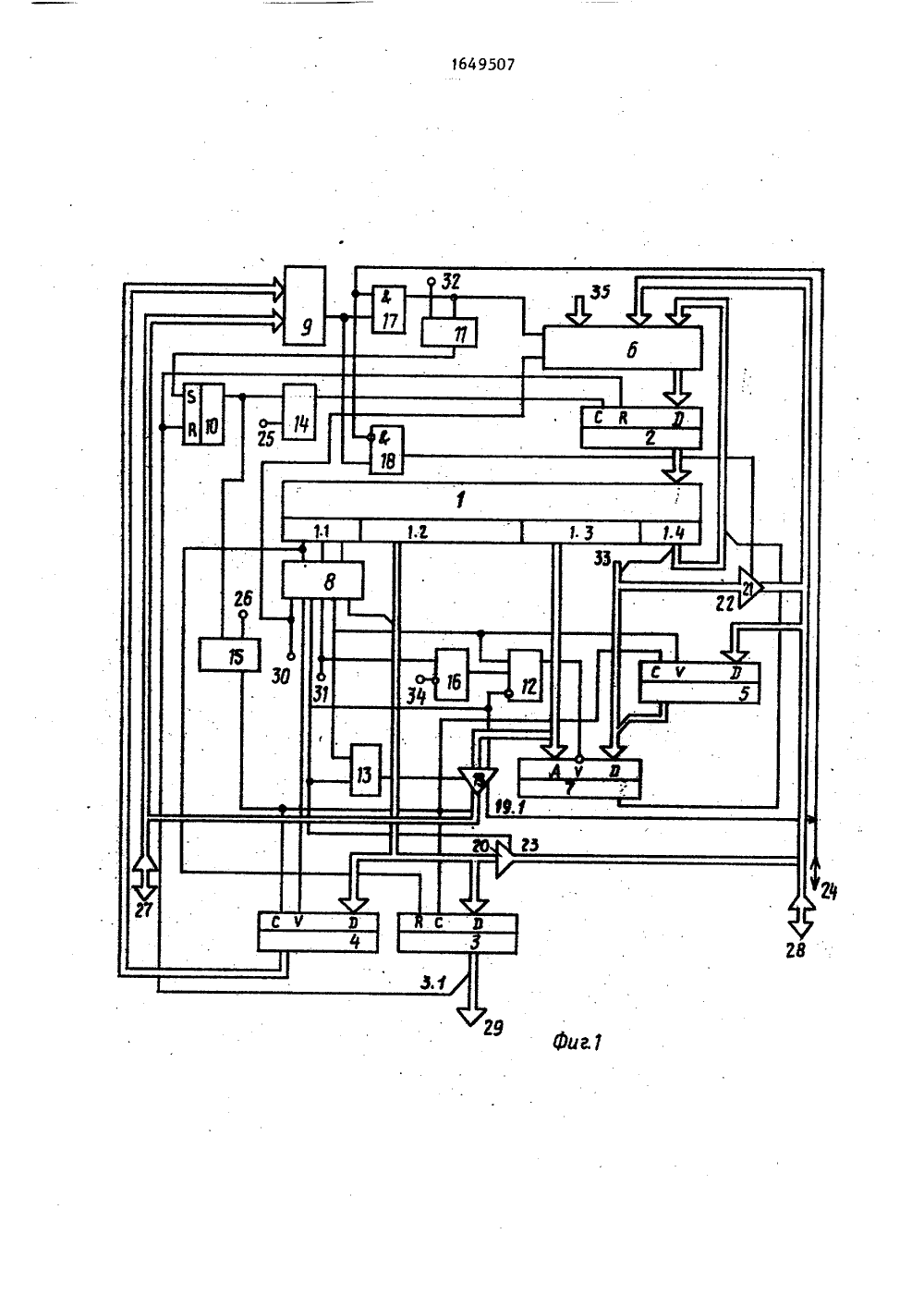

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 5 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР ЫОЕ 383 ЦБИ - Е( "1 ЕООПИСАНИЕ ИЗОБРЕТ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ тры адресаексоры адредешифраторпервый и вто(21 (22 46.55(088,8)ое свидетельство СССРС 05 В 19/18, 1981.свидетельство СССР4370638/24,9/08, 1988, - третий эл истрал введен ческих усл ии элемен ементы И,по кл АММИРУЕМЫИ УПРАВЛЯЫЩИ Изобретение вычислительн использованостойчивых упр П,.использую управления и д е при расшире функций. Цель е быстродейст ая цель дости ное устройств шениленвес зобрет ики относится к оьласт ислительной техни пользовано в распр тойчивых управляющи использующйх про равления и допускаоматики и выч ед и может ьыть ис ленных отказоуссистемах АСУ ТП мный принцип уп наращивание при чолняемых функциЦель изобрет родействия модул грам ющих вырасширении числг ия - повьппение быстза счет сокращения(57)ке ибытьказоуАСУ Тцип тносится к автомати- й технике и может в распределенных отавляющих системах щих программный прин- опускающих наращиии числа выполняеизобретения - повыия модуля. Поставается тем, что в изсодержащее блок памяти микрокоманд, регисмикроонераций, мультипл са и логических условий, признака, триггер пуска, рой элементы ИЛИ, первый менты И, первый и второй ные элементы, дополнитель регистры сравнения и логи вий, блок сравнения, трет ИЛИ, четвертый и пятый эл третий магистральный элемент, Введение новых элементов позволяет обеспечить в зависимости от программы функционирования измерение кода сравнения, с помощью которого осуществляется идентификация адресного кода, устанавливающего управляющий модуль, павы- Е сить производительность системы, реализуемой на модулях, путем параллельной работы модулей, каждый из которых имеет свой алгоритм функциониро 4 % вания, повысить отказоустойчивость системы за счет перераспределения функций отказавшего модуля между исп-равными модулями системы. 4 ил., р времени выполнения программы при от казе одного из управляющих модулей .и замене его на резервный.На Фиг. 1 представлена функциональная схема программируемого упра ляющего модуля (ПУМ), на Фиг. 2 - Функциональная схема системы, реали зованной на модулях; на Фиг. 3 - вр менные диаграммы работы двух модуле распределенной системы, на фиг. 41649507 оставитель О, Фомичевехред Л.Сердюкова Корр 1. Цчолинская акт М. Самборская каз 15 аж одписное ГКНТ СС оизводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 10 идаевсяУи щца/редююодры ВНИИПИ Государственного коми 113035, Мосблок-схема алгоритма функционированиямодуля.Модуль содержит блок 1 памяти микрокоманд с полями признака 1.1, кодамикроопераций (МО) 1.2, кода логических условий (ЛУ) 1.3 и адреса 1.4,регистры адреса 2, микроопераций 3,сравнения 4 и логических условий 5,мультиплексоры адреса 6 и логическихусловий 7, дешифратор 8 признака,блок 9 сравнения, триггер 10 пуска,первый 11, второй 12 и третий 13 элементы ИЛИ, первый 14, второй 15, третий 16, четвертый 17 и пятый 18 элементы.И, а также первый 19, второй20 и третий 21 магистральные элементыи имеет информационный вход 22 магистрального элемента 21, выход 23 магистрального элемента 20, вход-выход 24 20шины режима, первый 25 и второй 26 входы синхронизации, вход-выход 27 шиныадреса, вход-выход шины данных 28,выходы микроопераций 29, выход 30 состояния, выход 31 запроса, вход 32 пус 5ка, вход 33 логических условий, вход34 ответа на запрос и вход 35 кодаопераций.Систему образуют генератор 36 тактовых импульсов и определитель 37 при оритета,Программируемый управляющий модульв рамках распределенной системы работает следующим образом.В исходном состоянии генератор 36тактовых импульсов вырабатывает на .своих выходах последовательности сдвинутых относительно друг друга тактовых импульсов, все модули находятсяв исходном состоянии ожидания. Все 40элементы памяти, кроме регистра 4сравнения, установлены в нулевое состояние. Регистр 4 сравнения установлен в. единичное состояние, т,е. в немзаписан единичный код, Из блока 1 па-;45мяти микрокоманд считьвается содержимое ячейки по нулевому адресу.В таблице это макрокоманда (МК)типа А. В ее поле 1.1. записан нулевой код, который декодируется дешифратором признака 8 как сигнал ожидания кода очередной МП. Этот единичный.сигнал поступает на выход 30 состоя;ния модуля.Ф55Кроме того, сигнал ожидания кода очередной МП с первого выхода дешифратора признака 8 поступает на второй управляющий вход мультиплексора 6 адреса, который пропускает на информандонные входы регистра 2 адреса код операции с входа 35 модуля, Единичный код с выхода регистра сравнения 4 поступает на соответствующие информационные входы блока 9 сравнения, на другие: входы которого с шины 27 адреса поступает нулевой код.Таким образом, блок9 сравнения формирует на выходе нулевой сигнал, который запрещает прохождение через элементы И 12 и 1 сигналов режима работы шины 24 режима, Установка регистра 4 сравнения в единичное состояние приводит к тому, чтомодуль воспринймает нулевой код в шине 27 адреса как чужой, В таком состоянии управляющая система находится допоступления сигнала "Пуск" на вход 32пуска хотя бы одного модуля системы.Каждый модуль может работать в следующих режимах: режим ожидания кодаочередной МП, режим управления; режимизменения кода сравнения; режим передачи управления; режим запроса логических условий; режим ожидания АКУ.Исходное состояние модуля равнозначно состоянию модуля в режиме ожидания АКУ,Переход модуля в режим ожидания кода МП из исходного состояния осуществляется по сигналу "Пуск", поступающему с входа 32 через элемент ИЛИ 11 наустановочный вход триггера 10 пуска.Сигнал с выхода триггера 10 пуска открьвает элементы И 14 и 15, разрешаяпрохождение тактовых импульсов с выходов генератора 36 тактовых импульсовпо соответствующим входам модуля.Если к моменту появления на синхро"входе регистра адреса 2 модуля заднего фронта первого тактового импульсаФ ) с выхода элемента И 14 на выходе35 кода операций еще не появилось, тов регистре 2 адреса меняется нулевойадрес и из блока 1 памяти микрокомандснова считывается МК типа А. Так какв ее поле 1.2 записан нулевой код,то по заднему фронту тактового импульса с выхода второго элемента И 15 регистр 3 микроопераций своего состояния не изменяет,После появления кода МП на входе35 модуля этот код через мультиплексор адреса 6 записывается в регистр 2адреса и модуль переходит в режим управления,По заднему фронту тактового импульсас выхода элемента И 15 в ре- п5 16495 гистр 3 микроопераций записывается мик рооперационный код первой МК микропрограммы. Кроме того, в режиме управения возбуждается седьмой выход де 5фратора 8 признака и пропадает единичный сигнал на первом выходе дешифратора 8 признака.По заднему фронту очередного такто-. вого импульса с выхода элемента И 14 в регистр 2 адреса с выхбдов мультиплексора б адреса записывается адрес очередной МК. Этот адрес поступает на третий информационный вход мультиплексора адреса б со старших разрядов выходов 1.4 поля адреса блока 1 памяти микрокоманд (немодифицируемая часть) и выхода мультиплексора логических условий 7 (модифицируемая часть), В линейных МК значения млад .щего разряда адреса очередной МК определяется значением младшего разряда поля адреса 1,4, В поле 1,3 логических условий в линейных МК записан нулевой код. По этому коду мультиплексор 25 7 логических условий пропускает на выход значение сигнала с мпадшего разряда поля 1.4. В МК ветвления в поле 1.3 записан код логического условия, значение которого анализируется при 3 Формировании адреса очереднои МК. По этому коду мультиплексор 7 логических условий пропускает с входа 33 логических условий на свой выход значения нужного логического условия. Таким образом, в режиме управления младший разряд адреса очередной МК полностью определяется значением сигнала на выходе мультиплексора 7 логических условий. По записанному в регистр 2 ад О реса адресу из блока 1 памяти микро- команд считывается очередная МК линейная или ветвления.Из режима управления модуль может перейти в любой другой режим. 45При переходе в.режим ожидания кода очередной МП в полях 1.3 и 1.4 формата последней МК выполняются нулевые коды и в следующем такте из блока памяти микрокоманд считывается нулевой МК типа А, т.е. модуль переходит в состояние ожидания.При переходе в режим ожидания АКУ или окончания работы модуля в поле 1.1 формата последней МК записывается код, по которому дешифратор признака 8 формирует на шестом выходе сигнал микрооперации конца работы. В полях 1.3 и 1.4 этои МК (МК типа С) за 07 6писаны нулевые коды, Сигнал "Кбнец работы" по заднему фронту очередного "тактового импульса о записывается влрегистр 3 микроопераций. Затем с соот- .ветствующего выхода 3,1 регистра 3микроопераций единичный сигнал микрооперации "Конец работы". обнуляет триггер 10 пуска и регистр 2 адреса. Изблока памяти микрокоманд считываетсяМК типа С,При необходимости изменения кодасравнения, записанного в регистре 4сравнения, модуль из режима управления переходит в режим изменения кодасравнения. По заднему фронту очередного импульса 6, с выхода элементаИ 14 в регистр 2 адреса записываетсяадрес МК тина С. На втором выходе дешифратора признака 8 формируется единичный сигнал, который разрешает запись в регистр 4 сравнения нового кода сравнения с выхода поля 1,2 блокапамяти микрокоманд.По заднему фронту очередного тактового импульса Ф с выхода элементаИ 15 в регистр 4 сравнения записывается новый код сравнения. В режиме изменения кода сравнения регистр 3 микроопераций устанавливается в нулевоесостояние сигналом со старшего разряда выхода поля 1.1.В регистр сравнения может быть записан любой новый код., кроме нулевого.При необходимости передать инфор-мацию другому модулю системы рассматриваемый модуль переходит в режим передачи управления.По заднему фронту очередного тактового импульса Я, с выхода элементаИ 20 (фиг. 3) в регистр 2 адреса записывается адрес МК типа О. Эта МК проверяет готовность системы к передачеот 11-го модуля Е-му модулю (группе модулей) АКУ,На четвертом выходе дешифраторапризнака 8 формируется сигнал запросасостояния шины данных, адреса и режима. Этот сигнал поступает на соответствующий Б-й вход определителя приоритета 37. Если в этом такте работы системы на определитель 3 приоритетасигналов запроса от других модулей непоступило, то он формирует на своем11-м выходе сигнал разрешения пользования общесистемными шинами в следующемтакте работы системы. В противном случае такой сигнал формируется на другом выходе определителя 37 приорите 1649507тов, который соединен с входом 34 ответа на запрос другого более приори" тетного модуля системы, При нулевом . сигнале ответа на запрос на входе 34 14-го модуля элемент И 16 формирует единичный сигнал, который поступает на управляющий вход мультиплексора 7 логических условий, Поэтому сигналу мультиплексор 7 логических условийпропускает на свой выход нулевой сигнал с выхода младшего разряда поля 1.4, по импульсу о, в регистр адресал:2 записывается адрес МК типа О, Регистр 3 микроопераций при считыванииМК типа 0 обнуляется сигналом с первого выхода поля 1. 1. Как только на рход 34 11-го модуля поступает единичный сигнал, то на инверсном управляющем входе мультиплексора .логических 5 101520 условий 7 единичный сигнал исчезает и на его выходе появляется значение логического условия с выхода 30 состоя-. ния Ь-го модуля.Если сигнал этого логического условия нулевой, т.е. Ь-й модуль не готов к приему АКУ, то в следующем такте работы из И-го модуля по указанным причинам снова считывается МК типа О,Как только на входе 34 14-го модуля 30 появляется единичный сигнал, а значение логического условия с выхода 30 Ь-го модуля на входе 34 В-го модуля станет равньм единице (Ь-й модуль находится в состоянии ожидания АКУ), ц значение младшего разряда очередной МК в И-м модуле станет единичным. По импульсу 9, с выхода элемента И 14 в регистр адреса 14-го модуля записывается адрес МХ. типа Е, Единичный сигнал 40с третьего выхода дешифратора признака 8 открывает магистральные элементы 19 и 20, через элемент ИЛИ 12 поступает на управляющий вход мультиплексора логических условий 7 и, кроме того, поступает на вход магистрального эле-мента 19. При этом на информационном входе регистра адреса 2 формируется адрес очередной МК, с выхода поля 1.3 считывается адресный код Ь-го мо дуля, с выхода 1.2 в шину данных.28 поступает АКУ. В блоке 9 сравнения каждого модуля системы происходитсравнение адресного кода, переданногов шину 27 адреса 11-м модулем с кодом 55сравнения, который записан в регистре4 сравнения, В тех модулях системы, вкоторых эти коды совпали, на выходеблока сравнения формируется единичный сигнал, который разрешает прохождение сигнала режима работы из шины режима 24 через элемент И 17. Этот сигнал поступает на мультиплексор адреса 6, который пропускает на вход регистра .2 адреса АКУ с шины 28 данных. Кроме того, этот сигнал через элемент ИЛИ 11 устанавливает в единичное состояние триггер 10 пуска Ь-го модуля. По очередному импульсу 3 , с выхода элемента И 14 в регистр адреса 2 Ь-го модуля записывается АКУ, а в регистр 2 адреса 14-го модуля адрес очередной МК, Если в Ь-м модуле не было сбоя, то на выходе 30 состояния единичный сигнал исчезает. Если Ь-й модуль неисправен, то на выходе 30 этого модуля остается единичный сигнал. Ь-й модуль остается в состоянии ожидания АКУ.Для проверки принятия АКУ из блока 1 памяти микрокоманд 1%-го модуля считывается МК ветвления типа В, в поле 1,3 которой записан код, соответствуюрй выходу 30 Ь-го модуля, Если Ь-й модуль не вышел из режима ожидания АКУ, то Н-й модуль обращается к аварийной подпрограмме ликвидации отказа Ь-го модуля.При необходимости запроса логических условий Ь-го модуля Н-й модуль переходит в режим запроса логических условий. По очередному тактовому импульсу ф, с выхода элемента И 14 в регистр 2 адреса записывается МК типа П, Проверка шин в режиме запроса логических условий аналогична режиму передачи управления. Как только на входе 34 1 Ф-го модуля появляется единичныйсигнал, то по импульсу , с выхода элемента И 14 в регистр 2 адреса записывается адрес МК типа Р.Единичный сигны с пятого выхода дешифратора признака 8 открывает магистральный элемент 19, разрешает запись в регистр 5 логических условий, через элемент ИЛИ 12 поступает на инверсный управляющий вход мультиплексора 7 логических условий,с выхода поля 1.3 считывается адресный код Ь-го модуля, который через открытый магистральный элемент 19 поступает в шину 27 адреса. Так как имеется МК типа Р, то третий выход дешифратора признака не возбуждается, а магистральный элемент 20 остается закрытым и в шину 24 режима поступает нулевой сигнал с выхода младшего разряда магистрального элемента 19. Одновремен 16 ч 9507но запрашивать коды логических условий нескольких модулей нельзя. При совпадении адресов в блоке 9 сравнения Е-го модуля разрешается прохожде"5 ние сигнала запроса через элемент И 16, который поступает на вход элемента И 18. Этот сигнал открывает магистральный элемент 21 и разрешает прохождение кода логических условий в 1 О шину 28 данных, которые в 11-м модуле записываются в регистр 5 логических условий по импульсу 8 . Одновременно из поля 1.2 в регистр 3 микроопераций записывается очередной микро- операционный код.Таким образом организуется взаимодействие модулей распределенной системы и их согласованное функционирование, 20Формула изобретенияПрограммируемый управляющий модуль, содержащий блок памяти микрокоманд, 25 регистры адреса и микроопераций, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый, второй, третий элементы И, пер- ЗО вый и второй магистральные элементы, ричем выходы поля признака блока пати микрокоманд соединены с входами дешифратора признака, первый выход которого является выходом состояния модуля и соединен с первым адресным входом мультиплексора адреса, информаци- .онные выходы которого соединены с инФормационными входами регистра адреса, информационные выходы котоРого соеди иены с адресными входами блока памяти микрокоманд, старший разряд поля признака которого соединен с входом сброса регистра микроопераций, выходы которого являются выходами микроопераций модуля, а выход "Конец работы" соединен с входами сброса триггера,. пуска и регистра адреса, шестой выход дешифратора признака и выходы кода микроопераций блока памяти микрокоманд являются информационными входами регистра микроопераций и магистрального элемента, выходы которого соединены с шиной данных выходы кода логи)ческих условий блока памяти микрокоманд соединены с адресными входами55 мультиплексора логических условий и старшими разрядами информационных входов первого магистрального элемента,старшие разряды информационных выходов которого соединены с шиной адреса, а младшие - с шиной режима, старшие разряды выходов кода адреса блока памяти микрокоманд соединены со старшиМи разрядами первой группы информационных входов мультиплексора адреса, входы логических условий модуля и младший разряд выходов кода адреса блока памяти микрокоманд являются старшими разрядами информационных входов мультиплексора логических условий, выход которого соединен с младшим разрядом первой группы информационных входов мультиплексора адреса, вторая группа входов кода операции мультиплексора адреса является группой входов кода операций модуля, вторая группа входов мультиплексора адреса соединена с шиной данных, третий выход дешифратора признака соединен с управляющим входом второго магистрального элемента, с младшим разрядом информационных входов первого магистрального элемента ИЛИ, выход которого соединен с инверсным входом разрешения мультиплексора логических условий, четвертый выход дешифратора признака является выходом запроса модуля и соединен с первым входом третьего элемента И, второй инверсный вход которого является входом ответа на запрос модуля, а выход соединен с вторым входом второго элемента ИЛИ, пятый выход дешифратора признака соединен с третьим входом второго элемента ИЛИ, первый вход первого элемента ИЛИ является входом пуска модуля, а выход соединен с входом установки триггера пуска, выход которого соединен с первыми входами второго и первого элементов И, вторые входы которых являются соответственно вторым и первым входами синхронизации модуля, а выходы соединены соответственно с входами записи регистров микро- операций и адреса, о т л и ч а ю - щ и й с я тем, что, с целью повышения быстродействия модуля, в него дополнительно введены регистры сравнения и логических условий, олок сравнения, третий элемент ИЛИ, четвертый и пятый элементы И и третий магистральный элемент, информационные выходы которого соединены с шиной данных, шестой выход дешифратора признака и выходы кода микроопераций блока памяти микрокоманд являются информационными входами регистра сравнения, выходы которого сое164950 Адрес МК Выход 1 Поле МО Поле ЛУ Поле адДС 8 1.2 1.3 реса 1.4 МК Содержание МК 00. 00 00 00 МК ожидания кодаочередной МПМК управленияЗапись в Рг,Зкода МОМК изменения кодасравнения А Код МО Код ЛУ В у2 Код срав0нения 00 00 Код Ь-гомодуля Адрес МКтипа Еили Г 0 МК проверки 00 Код Ь+гомодуля Адрес МК типа П+1 Адрес МК типа 0+1 Е МК передачи АКУР МК запроса ЛУС МК конца работы 00 00 О..0 00 динены с первой группой информационныхвходов блока сравнения, выход которого соединен с первыми входами четвертого и пятого элементов И, вторые вхо- эды которых соединены сшиной режима,а выходы соединены соответственносвторым адресным входом мультиплексораадреса, вторым входом первого элемента ИЛИ и управляющим входом третьего 10магистрального элемента, группа входов логических условий и мпадший разряд выходов кода адреса блока памятимикрокоманд являются входами третье-го магистрального элемента, выход вто рого элемента И соединен с входами за-,.писи регистра сравнения и регистра логических условий, выходы которого соединены с младшими разрядами информационных входов мультиплексора логичес712ких условий, информационные входы регистра логических условий соединены сшиной данных, второй выход дешифратора признака соединен с входом разрешения регистра сравнения, третий выходдешифратора признака соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом управления первого магистрального элемента, пятый выход дешифратора признакасоединен с вторым входом третьего элемента ИЛИ и с входом разрешения регистра логических условий, втораягруппа информационных входов блокасравнения соединена с шиной адреса,шины адреса, данных и режима являютсясоответствующими входами-выходами модуля, 1649507

СмотретьЗаявка

4685730, 03.05.1989

ПРЕДПРИЯТИЕ ПЯ Г-4651

СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ВАЛОВ ОЛЕГ ГЕННАДЬЕВИЧ, АГЕЕНКО ВИКТОР ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G05B 19/08

Метки: модуль, программируемый, управляющий

Опубликовано: 15.05.1991

Код ссылки

<a href="https://patents.su/10-1649507-programmiruemyjj-upravlyayushhijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый управляющий модуль</a>

Предыдущий патент: Программируемый управляющий модуль

Следующий патент: Устройство для управления разгоном и торможением двигателя

Случайный патент: Манипулятор