Устройство для отладки микропроцессорных систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

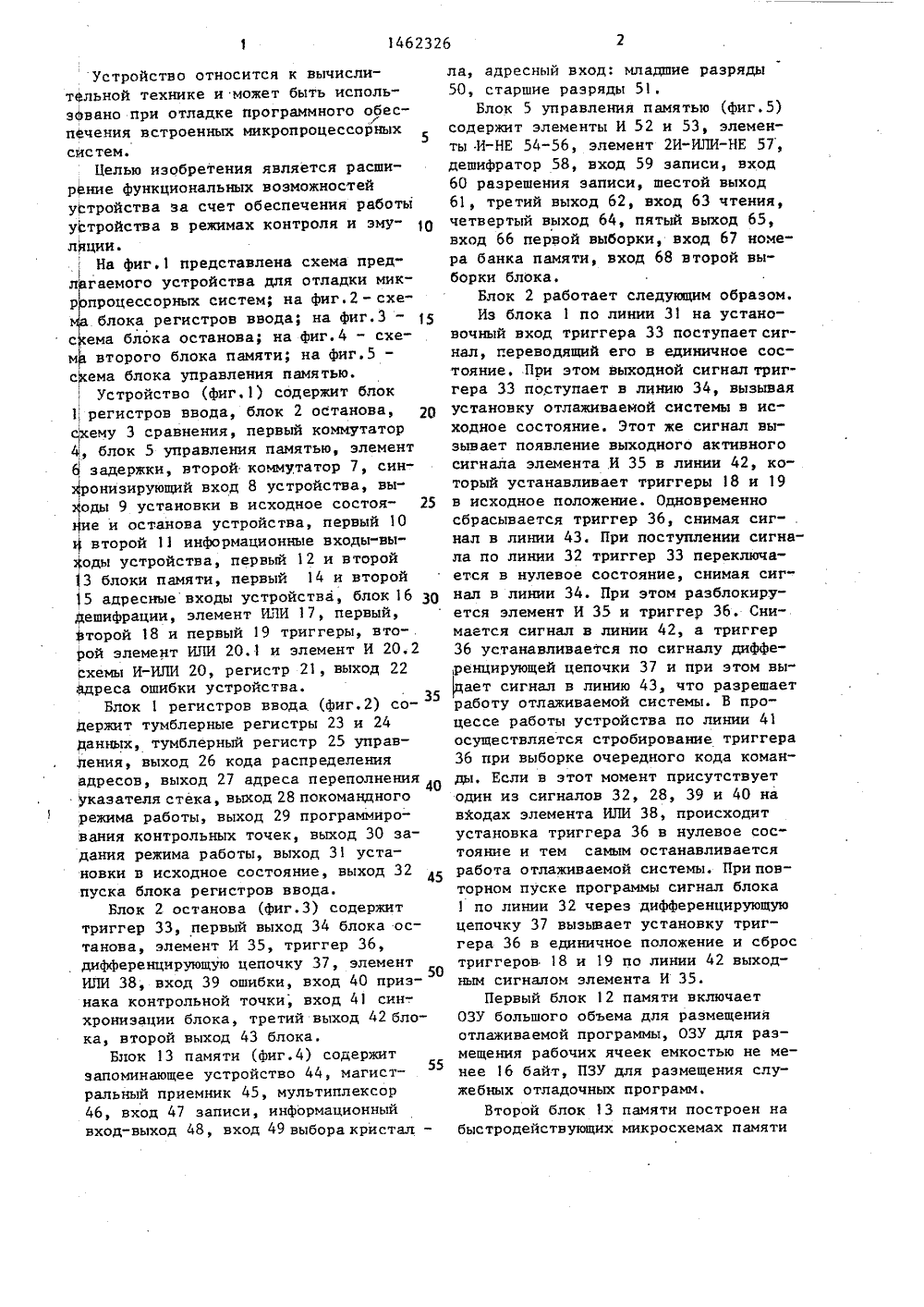

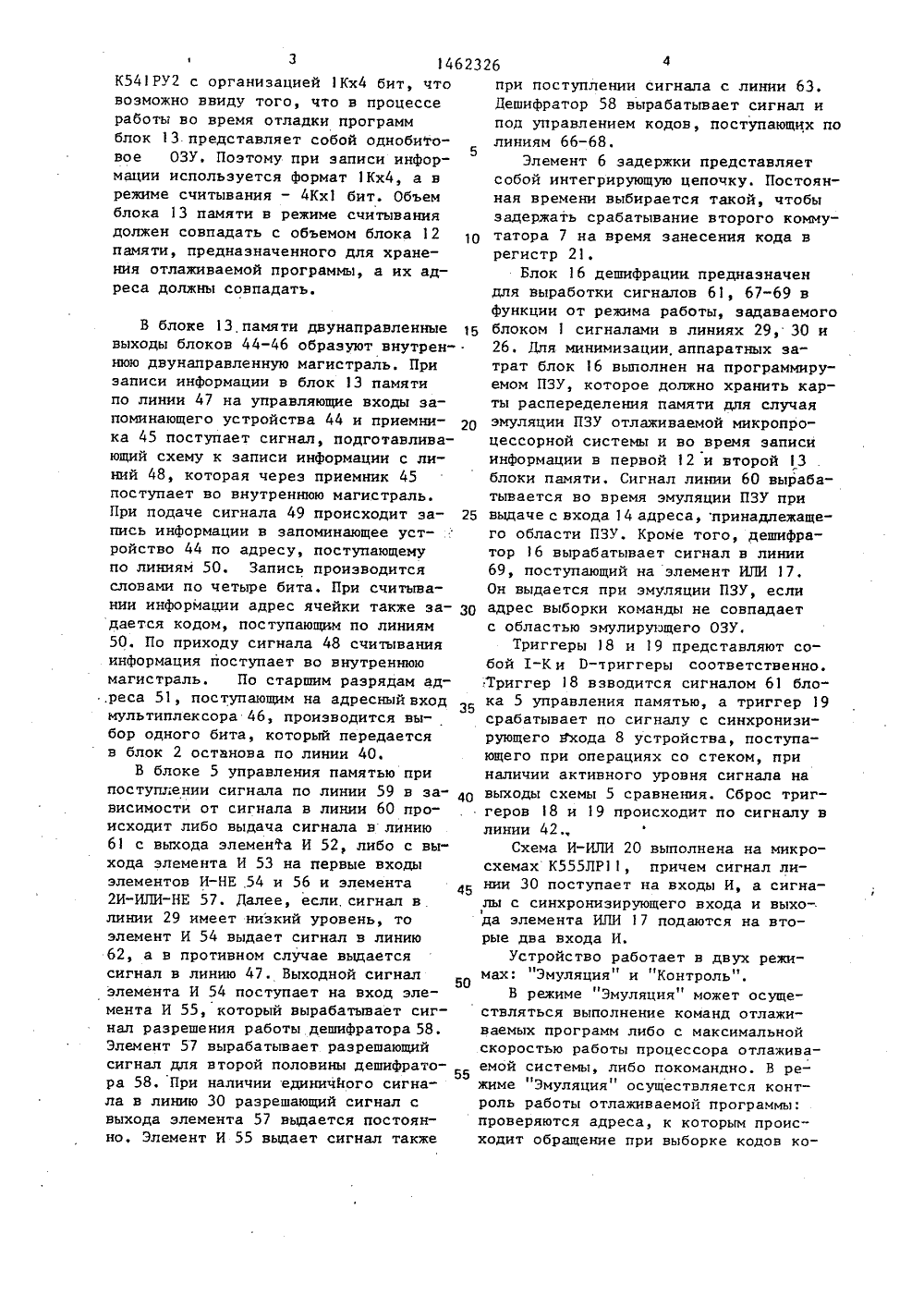

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 19) (11 А С 06 Р 11/ ИЕ ИЗОБРЕТЕН ПИС ь"беВ 8 ети.И.Головен тельство СССР Р 11/28, 1984 льство СССР Р 1/28, 1983 блокерж 12,(54) УСТРОЙСТВО ДЦЕССОРНЫХ СИСТЕМ(57) Изобретение ОТ ЛАДКИ МИК а л носится к вычислиГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидВ 1171799, кл, С 06Авторское свидетВ 1104521, кл. С 06 тельной технике и может быть исползовано при отладке программногоспечения встроенных микропроцессосистем. Целью изобретения являетсрасширение функциональных возможнтей за счет обеспечения, работы усройства в режимах контроля н эмулции. В устройство для отладки микпроцессорных систем, содержащее брегистров ввода 1, блок остановасхему сравнения 3, коммутатор 4,5 управления памятью, элемент задки 6, коммутатор 7, блоки памяти13, введены блок дешифрации 16, элмент ИЛИ 17, триггеры 18, 19, схемИ-ИЛИ 20 и регистр 21. 5 ил.,1 таб1462326 дактор Ю.Середа 8 Тираж 667 Подписноеарственного комитета по изобретениям и открытиям113035, Москва, Ж, Раушская наб д. 4/5 и ГКНТ ССС Производственно-издательский комбинат "Патент", г. Ужгород, улГагарина,10 Заказ 714 ВБИИПИ Го СоставителЛ.ОлийныкУстройство относится к вычислительной технике и может быть использовано при отладке программного обеспечения встроенных микропроцессорных систем.Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения работы устройства в режимах контроля и эму ляции.На фиг.1 представлена схема предлргаемого устройства для отладки микропроцессорных систем; на фиг,2 - схема блока регистров ввода; на фиг.З " 15 схема блока останова; на фиг.4 - схема второго блока памяти; на фиг.5 - схема блока управления памятью.Устройство (фиг.1) содержит блок 1, :регистров ввода, блок 2 останова, 20 схему 3 сравнения, первый коммутатор 4, блок 5 управления памятью, элемент 6 задержки, второй коммутатор 7, синМронизирующий вход 8 устройства, выходы 9 установки в исходное состоя ие и останова устройства, первый 10второй 11 информационные входы-выХоды устройства, первый 12 и второй 13 блоки памяти, первый 14 и второй 15 адресные входы устройства, блок 16 30 Дешифрации, элемент ИЛИ 17, первый, торой 18 и первый 19 триггеры, второй элемент ИЛИ 20.1 и элемент И 20.2 схемы И-ИЛИ 20, регистр 21, выход 22 Эдреса ошибки устройства.Блок 1 регистров ввода, (фиг.2) со 35 Держит тумблерные регистры 23 и 24 данных, тумблерный регистр 25 управления, выход 26 кода распределения адресов, выход 27 адреса переполнения указателя стека, выход 28 покомандного режима работы, выход 29 программирования контрольных точек, выход 30 задания режима работы, выход 31 установки в исходное состояние, выход 32 пуска блока регистров ввода.Блок 2 останова (фиг.З) содержит триггер 33, первый выход 34 блока останова, элемент И 35, триггер 36, дифференцирующую цепочку 37, элемент ИЛИ 38, вход 39 ошибки, вход 40 признака контрольной точки, вход 41 син-. хронизации блока, третий выход 42 блока, второй выход 43 блока.Блок 13 памяти (фиг.4) содержит запоминающее устройство 44, магистральный приемник 45, мультиплексор 46, вход 47 записи, информационныйвход-выход 48, вход 49 выбора кристал -ла, адресный вход: младшие разряды50, старшие разряды 51,Блок 5 управления памятью (фиг.5)содержит элементы И 52 и 53, элементы И-НЕ 54-56, элемент 2 И-ИЛИ-НЕ 57,дешифратор 58, вход 59 записи, вход60 разрешения записи, шестой выход61, третий выход 62, вход 63 чтения,четвертый выход 64, пятый выход 65,вход 66 первой выборки, вход 67 номера банка памяти, вход 68 второй выборки блока.Блок 2 работает следующим образом.Из блока 1 по линии 31 на установочный вход триггера 33 поступает сигнал, гереводящий его в единичное состояние. При этом выходной сигнал триггера 33 поступает в линию 34, вызываяустановку отлаживаемой системы в исходное состояние. Этот же сигнал вызывает появление выходного активногосигнала элемента,И 35 в линии 42, который устанавливает триггеры 18 и 19в исходное положение. Одновременносбрасывается триггер 36, снимая сиг- .нал в линии 43. При поступлении сигнала по линии 32 триггер 33 переключается в нулевое состояние, снимая сиг"нал в линии 34. При этом разблокируется элемент И 35 и триггер Зб. Снимается сигнал в линии 42, а триггер36 устанавливается по сигналу дифференцирующей цепочки 37 и при этом вы"ает сигнал в линию 43, что разрешаетработу отлаживаемой системы. В процессе работы устройства по линии 41осуществляется стробирование триггера36 при выборке очередного кода команды, Если в этот момент присутствуетодин из сигналов 32, 28, 39 и 40 навходах элемента ИЛИ 38, происходитустановка триггера 36 в нулевое состояние и тем самым останавливаетсяработа отлаживаемой системы. Приповторном пуске программы сигнал блока1 по линии 32 через дифференцирующуюцепочку 37 вызывает установку триггера 36 в единичное положение и сбростриггеров 18 и 19 по линии 42 выходным сигналом элемента И 35.Первый блок 12 памяти включаетОЗУ большого объема для размещенияотлаживаемой программы, ОЗУ для размещения рабочих ячеек емкостью не менее 16 байт, ПЗУ для размещения служебных отладочных программ,Второй блок 13 памяти построен набыстродействующих микросхемах памяти1 3 14623 К 541 РУ 2 с организацией 1 Кх 4 бит, что возможно ввиду того, что в процессе работы во время отладки программ блок 13 представляет собой однобитовое ОЗУ, Поэтому при записи инфор 5 мации используется формат 1 Кх 4, а в режиме считывания - 4 Кх бит. Объем блока 13 памяти в режиме считывания должен совпадать с объемом блока 12 памяти, предназначенного для хранения отлаживаемой программы, а их адреса должны совпадать. В блоке 13 памяти двунаправленные выходы блоков 44-46 образуют внутрен- . нюю двунаправленную магистраль. При записи информации в блок 13 памяти по линии 47 на управляющие входы запоминающего устройства 44 и приемни ка 45 поступает сигнал, подготавливающий схему к записи информации с линий 48, которая через приемник 45 поступает во внутреннюю магистраль. При подаче сигнала 49 происходит за пись информации в запоминающее уст- .:. ройство 44 по адресу, поступающему по линиям 50. Запись производится словами по четыре бита. При считывании информации адрес ячейки также за- З 0 дается кодом, поступающим по линиям 50. По приходу сигнала 48 считывания информация поступает во внутреннюю магистраль. По старшим разрядам ад,реса 51, поступающим на адресный вход мультиплексора 46, производится выбор одного бита, который передается в блок 2 останова по линии 40.В блоке 5 управления памятью при поступлении сигнала по линии 59 в за О висимости от сигнала в линии 60 происходит либо выдача сигнала в линию 61 с выхода элемента И 52, либо с выхода элемента И 53 на первые входы элементов И-НЕ 54 и 56 и элемента 2 И-ИЛИ-НЕ 57. Далее, если, сигнал в линии 29 имеет низкий уровень, то элемент И 54 выдает сигнал в линию 62, а в противном случае выдается сигнал в линию 47. Выходной сигнал элемента И 54 поступает на вход элемента И 55, который вырабатывает сигнал разрешения работы дешифратора 58, Элемент 57 вырабатывает разрешающий сигнал для второй половины дешифрато 55 ра 58, При наличии единичйого сигнала в линию 30 разрешающий сигнал с выхода элемента 57 выдается постоянно, Элемент И 55 выдает сигнал также 264при поступлении сигнала с линии 63. Дешифратор 58 вырабатывает сигнал и под управлением кодов, поступающих по линиям 66-68.Элемент 6 задержки представляет собой интегрирующую цепочку. Постоянная времени выбирается такой, чтобы задержать срабатывание второго коммутатора 7 на время занесения кода в регистр 21Блок 16 дешифрации предназначен для выработки сигналов 61, 67-69 в функции от режима работы, задаваемого блоком 1 сигналами в линиях 29, 30 и 26. Для минимизации аппаратных затрат блок 16 выполнен на программируемом ПЗУ, которое должно хранить карты распеределения памяти для случая эмуляции ПЗУ отлаживаемой микропроцессорной системы и во время записи информации в первой 12 и второй 13 блоки памяти. Сигнал линии 60 вырабатывается во время эмуляции ПЗУ при выдаче с входа 14 адреса, принадлежащего области ПЗУ. Кроме того, дешифратор 16 вырабатывает сигнал в линии 69, поступающий на элемент ИЛИ 17, Он выдается при эмуляции ПЗУ, если адрес выборки команды не совпадает с областью эмулирующего ОЗУ.Триггеры 18 и 19 представляют со" бой 1-К и П-триггеры соответственно, .Триггер 18 взводится сигналом 61 блока 5 управления памятью, а триггер 19 срабатывает по сигналу с синхронизирующего нхода 8 устройства, поступающего при операциях со стеком, при наличии активного уровня сигнала на выходы схемы 5 сравнения. Сброс триггеров 8 и 19 происходит по сигналу в линии 42.Схема И-ИЛИ 20 выполнена на микросхемах К 555 ЛР 11, причем сигнал линии 30 поступает на входы И, а сигналы с синхронизирующего входа и выхода элемента ИЛИ 17 подаются на вторые два входа И.Устройство работает в двух режимах: "Эмуляция" и "Контроль".В режиме "Эмуляция может осуществляться выполнение команд отлаживаемых программ либо с максимальной скоростью работы процессора отлаживаемой системы, либо покомандно. В режимеЭмуляция" осуществляется контроль работы отлаживаемой программы: проверяются адреса, к которым происходит обращение при выборке кодов ко 1462326манд; контролируются выполняемыециклы записи данных и блокируются поПытки записи в область эмулирующегоОЗУ; контролируется глубина стека впроцессе работы программ; в случаедостижения программой одного из заданных адресов (контрольная точка)выдается сигнал останова,В случае возникновения ошибок илири достижении контрольной точки вегистр 21 заносится адрес команды,ри выполнении которой возникла ошиба. В режиме "Контроль" осуществляется доступ к блоку 12 памяти для запи;си/считывания, запись контрольных тоЧек в блок 13 памяти. Доступ к реги.,:стру 21 может осуществляться в обоихрежимах.Устройство работает следующим образом.В регистре 26 управления блока 1вначале набирается нулевая комбинация, переводящая сигнал линий 29-32 всостояние логического нуля, При поступлении сигнала 29 в блок 5 запре;,щается работа логических схем 56 и57 иразрешается работа схемы 54.Низкий уровень сигнала линии 30 блокирует работу схемы 57 по вторым входам и переключает первый и второйкоммутаторы 4 и 7 на передачу сигналовс входов 11 и 15 соответственно. Низкий уровень сигнала в линии 31 переводит триггер 33 блока 2 останова вединичное состояние. Выходной сигналтриггера 33 вызывает формированиенизкого уровня сигнала схемой И 35 влинии 42, который переводит в нуле"вое состояние триггеры 18 и 19, атакже устанавливает в нулевое состояние триггер 36, который снимает сигнал в линии 43. Наличие соответствующих уровней сигналов в линиях 34 и 43вызывает переход отлаживаемой системы в исходное состояние и блокирование ее работы в этом состоянии. Далее может быть произведена загрузкаотлаживаемой программы в эмулирующееОЗУ блока 12 памяти, При этом с ин-формационного входа 11 через первыйкоммутатор 4 на информационный входпервого блока 12 памяти передаютсякоды отлаживаемой программы, а с ад"ресного входа 15 передаются соответствующие адреса. Через второй коммутатор 7 коды адресов передаются наадресные входы блока 12 памяти и блока 16, который по старшим разрядам адреса с учетом состояния сигналовлиний 29 и 30 вырабатывает сигналы66-68, причем в линиях бб и 67 уровни сигналов активны, а сигнал в линии 68 пассивен. Уровень сигнала линии 60 имеет значение "1, так как врежиме"Контроль может производитьсязапись в область эмулирующего ОЗУ 10 блока 12 памяти. При поступлении скоммутатора 7 активного сигнала линии 59 схема И 53 вырабатывает сигнал, который вызывает формированиесхемой И-НЕ 54 активного уровня сигнала в линии 62, который переводитОЗУ блока 12 в режим записи информации. Одновременно сигнал схемы И-НЕ54 поступает на вход схемы И-НЕ 55,которая вырабатывает стробирующий 20 сигнал, поступающий на дешифратор 58,разрешая выдачу одного из сигналоввыборки в линиях 64. При поступленииэтих сигналов в блок 12 памяти происходит запись информации, В случае 25 считывания информации из блока 12 памяти с коммутатора 7 по линии 63 поступает на схему 55 сигнал для выработки строба, разрешающего работу дешифратора 58, который формирует сиг- ЗО нал в одной из линий 64. При поступлении этих сигналов в блок 12 памятипроисходит считывание информации извыбранного банка. При программировании контрольных точек производится заЗ 5 лись информации в блок 12 памяти.При этом коды адресов и данных поступают с входов устройства 11 и 15 через коммутаторы 4 и 7, а запись происходит по приходу сигнала линии 59, 40 выдаваемого коммутатором 7.Кроме того, должен быть переведенв единичное состояние сигнал линии29 регистра 25 блока 1Этот сигналпоступает в блоки 6 и 16, которые по 45 старшим разрядам адреса, поступающимс коммутатора 7, вырабатывает сигналыв линиях 60, 66-68, причем сигнал линии имеет единичное значение, разрешая работу схемы И 53, сигнал линии 50 бб пассивен, запрещая работу дешифратора 58 на линии 64 и 65, а сигналылиний 67 и 68 разрешают выработку сигналов в линиях 49 дешифратором 58.При поступлении сигнала линии 59 с 5 б коммутатора 7 схема И 53 вырабатываетсигнал, поступающий на второй входсхемы И-НЕ 56 и вход схемы 2 И-ИЛИ-НЕ57При наличии единичного значениясигнала линии 29 схема И-НЕ 56 выра1714623 батывает сигнал в линии 47, переводящий запоминающее устройство 44 и приемник 45 блока 13 памяти в режим записи,. Схема 57 по конъюнкции сигна 5 лов линий 29 и выходного сигнала схемы И 53 вырабатывает сигнал стробирования дешифратора 58 для выдачи сигналов линий 49. Они поступают на . вход 44 выборки запоминающего устрой ства 44 блока 13 памяти и происходит запись информации с линий 48 по адресу, задаваемому кодом с линий 50. По окончании записи контрольных точек сигнал линии 29 должен быть переведен 15 в пассивное состояние. Для перевода устройства в режим "Эмуляция" сигнал линии 30 блока. 1 переводится в единичное состояние. Запуск отлаживаемой программы происходит в два этапа: 20 вначале сигнал с линии 31 регистра 25 блока 1 переводится в единичное состояние, При этом снимается сигнал с установочного входа триггера 33 блока 2 останова. Затем сигнал линии 25 32 также перводится в единичное состояние. При этом происходит переключение триггера 36 в нулевое состояние, и снимается сигнал в линии 34. Одновременно сигнал линии 32 через 30 дифференцирующую цепочку 37 устанавливает триггер 36, который выдает сигнал в лийию 43, что разрешает работу отлаживаемой системы с нулевого адреса. Схема И 35 при переключении сигнала линии 34 снимает сигнал линии 42 с триггеров 18 и 19, разрешая их работу, так как сигнал линии 30 принял единичное значение и произошло ,переключение коммутаторов 4 и 7 на 40 прием сигналов с информационного и адресного входов 1 О и 14 устройства соответственно. ПоЪ воздействием сигнала линии 30 схема 2 И-ИЛИ-НЕ 57 блока 5 выдает постоянный разрешающий сигнал 45 на вход дешифратора 58. Этим же сигналом блок 16 настраивается на работу в режиме эмуляции.При выполнении отлаживаемой про-. граммы происходит считывание команд 5 О из области эмулирующего ОЗУ блока 12 памяти по сигналу линии 63 аналогично описанному. Отличие заключается в том, что дешифратор 58 блока 5 выдает активные сигналы по всем линиям 66-68 55 и считывание происходит одновременно из блоков 12 и 13 памяти под управлением сигналов линий 49, 64 и 65, Сиг- нал линии 47 пассивен. Поэтому запо- . 26 8минающее устройство 44 блока 13 памяти находится э режиме считывания, а приемник 45 отключен от информационных линий 48. По сигналам линий 50 из запоминающего устройства 44 с приходом сигнала 49 происходит считывание информации, которая по внутренней магистрали блока 13 памяти поступает на информационные входы мультиплексора 46, который управляется сигналами старших разрядов адреса линий 51. С выхода мультиплексора 46 выбранный бит по линии 40 поступает на вход схемы ИЛИ 38 блока останова. При выдаче с коммутатора 7 кода адреса, принадлежащего эмулирующему ОЗУ блока 12 памяти, блок 16 выдает нулевой сигнал в линию 60 и если поступает сигнал записи по линии 59, та происходит блокирование его распространения через схему И 53. Срабатывает схема И 52, выдавая сигнал в линйю 61. Этот сигнал устанавливает триггер 18, фиксируя попытку записи в область эмулирующего ОЗУ. При выдаче с коммутатора 7 адреса, не совпадающего с картой памяти, заданной сигналами линий 27 регистра 23 блока 1, блок 16 выдает сигнал в линию 69, которыйпоступает на схему ИЛИ 17. Схема 3 сравнения постоянна анализирует коды, ,поступающие с выхода коммутатора 7, сравнивая их с кодами линий 27 регистра 24 блока 1. При совпадении этих кодов схема 3 выдает сигнал на триггер 19. В процессе отработки программы отлаживаемой системой на синхронизирующий вход 8 устройства поступают сигналы выборки кода команды и выдачи содержащего указателя стека. Код указателя стека подается на вход 14 устройства, При наличии на входе триггера 19 сигнала са схемы Э сравнения в момент поступления с входа 9 устройства сигнала выдачи содержимого указателя стека происходит срабатывание триггера 19. Сигналы блока 1, блока 13 памяти и выходной сигнал схемы ИЛИ 17 опрашиваются блоком 2 астанава по приходу с синхранизирующега входа 8 сигнала выборки кода команды. При наличии хотя бы одного активного сигнала на входе схемы ИЛИ 38 она вырабатывает сигнал, поступающий на информационный вход триггера 36, и по приходу сигнала линии 41 с синхронизирующего входа 8 о выборке кода команды триггер 36 взвадится, снимая9 14623сигнал в линии 43, который вызываетостанов выполняемой программы. Сигналом 41 при отсутствии сигнала схемыИЛИ 17 постоянно стробируется регистр21 через схему И-ИЛИ 29. В этот ребгистр заносится код адреса, выдавве"мый коммутатором 7. В случае возникновения ошибочной ситуации в процес-.се выполнения отлаживаемой программывыходной сигнал схемы ИЛИ 17 блокирует занесение очередного адреса выборки кода команды по приходу сигна:.ла линии 41 и регистра 21 сохраняетсяадрес кода команды, в которой произошла,15.ошибка. Это обеспечивает получениепрограммистом адреса ошибочной команды без дополнительных действий.При переводе устройства в режимКонтроль сигналом линии 30 блока 1 20производится занесение в регистр 21кода адреса останова отлаживаемойсистемы, так как на управляющий входкоммутатора 7 сигнал линии 30 поступает через элемент б задержки. Нели-.; 25чие в регистре 21 адреса остановапозволяет управлять переходами протцессора, выполняющего отлаживаемуюпрограмму, на адресе блока 13 памяти,хранящие служебные отладочные программы и осуществлять таким образомисследование результатов прогона отлаживвемой программы.Таким образом, предлагаемое устройство обеспечивает доступ к блокам памяти как для загрузки информации, необходимой для проведения отладки программы,так и для контроля содержимого с цельюуправления процессором отладки. Такая,организация устройства позволяет осуществлять отладку программ в диалоговом режиме, в также существенно ускорить этот процесс,Формула иэ обретения 45Устройство для отладки микропро:цессорных систем, содержащее блок регистров ввода, блок останова, схему сравнения, два коммутатора, блок уп 50 равления памятью, элемент задержки, два блока памяти, причем выход адреса переполнения указателя стека блока регистров ввода соединен с первым информационным входом схемы сравнения, выходы покомандного режима работы, установки в исходное состояние и пуска блока регистров ввода подключены к одноименным входам блока останова,2 б 10вход синхронизации блока останова подключен к входу синхронизации устройства, первый и второй выходы блокаостанова являются соответственно выходами установки в исходное состояниеи останова устройства для подключенияк управляющей шине отлаживаемой системы, выход задания режима работыблока регистров ввода соединен непо-.средственно с первым управляющим входом первого коммутатора и через элемент задержки с управляющим входоМвторого коммутатора и с входом задания режима работы блока управленияпамятью, выход программирования контрольных точек блока регистров вводасоединен,с одноименным входом блокауправления памятью, первый и второйинформационные входы-выходы первогокоммутатора являются соответственнопервым информационным входом-выходомустройства для подключения к информационной шине отлаживания системы ивторым информационным входом-выходомустройства для подключения к информа"ционной шине отлаживаемой системы,информационные входы-выходы первогои второго блоков памяти соединены стретьим информационным входом-выходомпервого коммутатора, выход признакаконтрольной точки второго блока памяти соединен с одноименным входом бло-ка останова, первый выход блока управления памятью сОединен с вторымуправляющим входом первого коммутатора и с входом записи второго блокапамяти, вход выбора кристалла котора"го соединен свторым выходом блокауправления памятью третий выход которого соединен с третьим управляющим входом первого коммутатора и свходом записи первого блока памяти,первый и второй входы выбора кристал".ла которого соединены с четвертым ипятым выходами блока управления памятью первый и второй информационные входы второго коммутатора являют-,ся соответственно первым адреснымвходом устройства для подключения кшине адреса отлаживающей системы ивторым адресным входом устройства дляподключения к шине адреса отлаживаемой системы, группа выходов второгокоммутатора соединена с адреснымивходами первого и второго блоков па"мяти, с вторым информационным входомсхемы сравнения и входами записи ичтения блока управления памятью, о т14623 Код адр ти Код нен аспределенияов банков памоков 2 и 13дреса переполуказателя стекаСигналрежимСигнал 28 а управления блока покомандногоработыпрограммироонтрольных 29 ни точек 3 5 Сигнал задания режи ма работы устройств Установка в исходно остояни 2 3 3 Сигнал пускаСигнал установки висходное состояниеотлаживаемого устростваСигнал ошибкиСигнал контрольнойточки 17 13 4 2 8 инхрони Входная шин ции устройс о ки Сигнал выб р кодакомандыУстановка трйггеров в исходное состояни Сигнал останова Сигнал записи контрольных точек 8 9 2 2 43 47 л и ч а ю щ е е с я тем, что, с целью расширения функциональных возмо,"ностей за счет обеспечения работы устройства в режимах контроля и эмуляции, оно содержит блок дешифрации,5 два элемента ИЛИ, два триггера, элемент И и регистр, причем группа выходов второго коммутатора соединена с информационными входами регистра, вы О ходы кода распределения адресов, программирования контрольных точек и задания режима работы блока регистров ввода и группа выходов второго коммутатора подключены к информационному входу блока дешифрации, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с входами разрешения записи, первой выборки, номера банка памяти, второй выборки блока управления памятью и с первым входом первого элемента ИЛИ, выход которого соединен с входом ошибки блока останова и с пер 26 12вым входом элемента И, вход синхронизации устройства подключен к синхровходу первого триггера и к второмувходу элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединенс выходом задания режима работы блокарегистров ввода, выход второго элемента ИЛИ соединен с входом записирегистра, выход которого является выходом адреса ошибки устройства, третий выход блока останова соединен свходами сброса первого и второготриггеров, шестой выход блока управления памятью соединен с установоч"ным входом второго триггера, информационный вход первого триггера соединен с выходом схемы сравнения, выходвторого триггера соединен с вторымвходом первого элемента ИЛИ, третийвход которого соединенс выходом первого триггера,Первая информационнаяшина блока 1 торая информационнаяшина блока 1 ходная шина устроиств Выходная шина устройст48 12 13 1 Э 12 13 12 13 5 5 50 51 716 59 60 61 62 18 13 63 64 512 65 5 12 16 16 16 16 67 68 69 5517ИнформационныесигналыПервый сигнал выборакристаллаСигналы младшихразрядов адресаСигналы старшихразрядов адресаСигналы записиСигналы разрешениязаписиСигнал ошибки записиСигнал записи,в эмулирующее ОЗУСигнал чтенияВторой сигнал выборакристаллаТретий сигнал выбора кристаллаСигнал "Выборка 1" Сигнал "Номер банка"Сигнал "Выборка 2"Сигнал ошибки адреса Шина данных коммутатора 4 Выхорная шина коммутатора 7Шина управления блока 16 Шина управления блока 16

СмотретьЗаявка

4179129, 24.11.1986

ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

СОБКЕВИЧ НИКОЛАЙ ОЛЕГОВИЧ, ГОЛОВЕНЬ ТАМАРА ИВАНОВНА, ШЕЛЕСТОВ СЕРГЕЙ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: микропроцессорных, отладки, систем

Опубликовано: 28.02.1989

Код ссылки

<a href="https://patents.su/10-1462326-ustrojjstvo-dlya-otladki-mikroprocessornykh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для отладки микропроцессорных систем</a>

Предыдущий патент: Устройство для контроля последовательности выполнения модулей программ

Следующий патент: Устройство для отладки программ

Случайный патент: Способ стабилизации метилбнхлорида