Кодер двоичного кода 3в4в-3

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1444964

Автор: Котиков

Текст

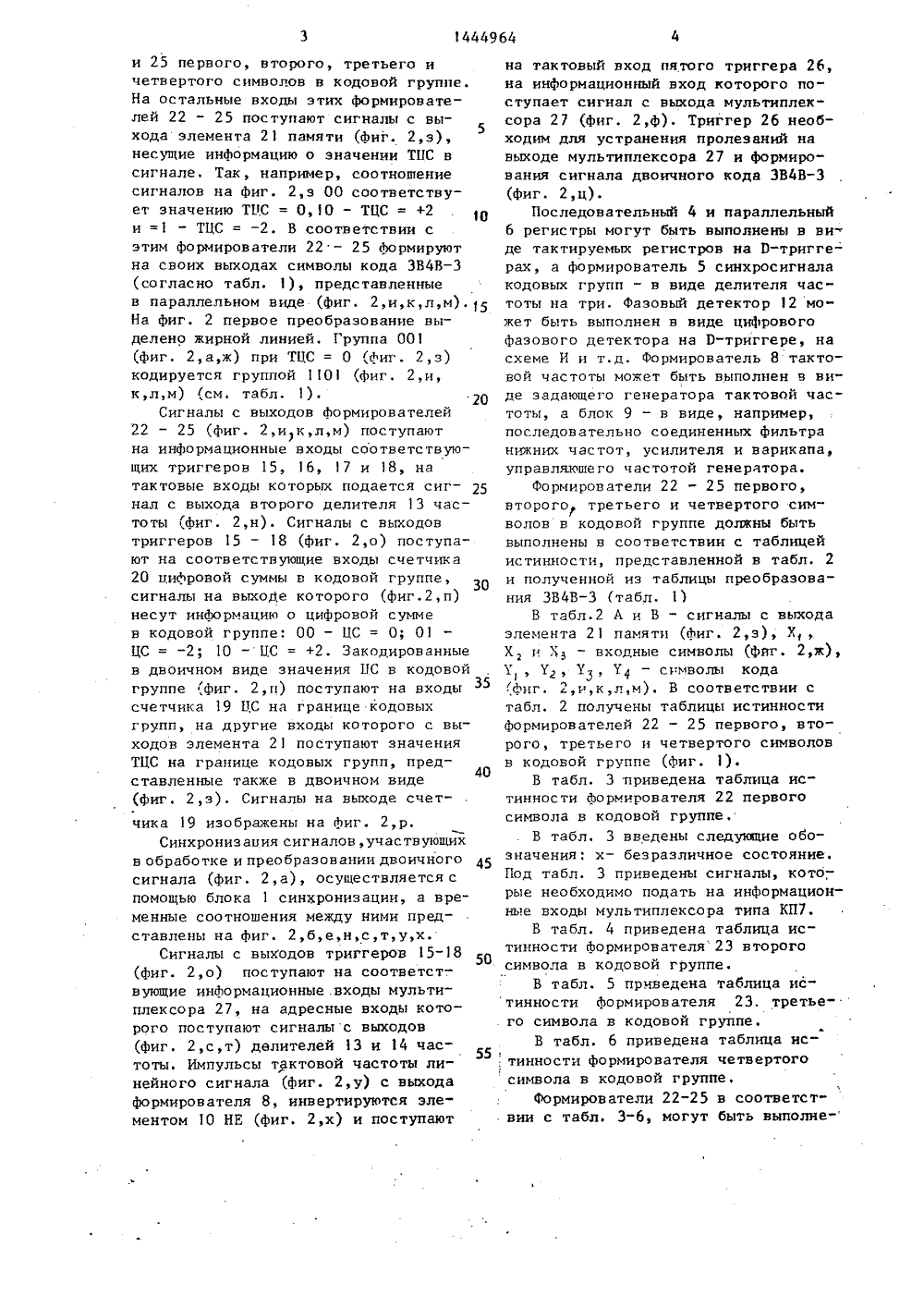

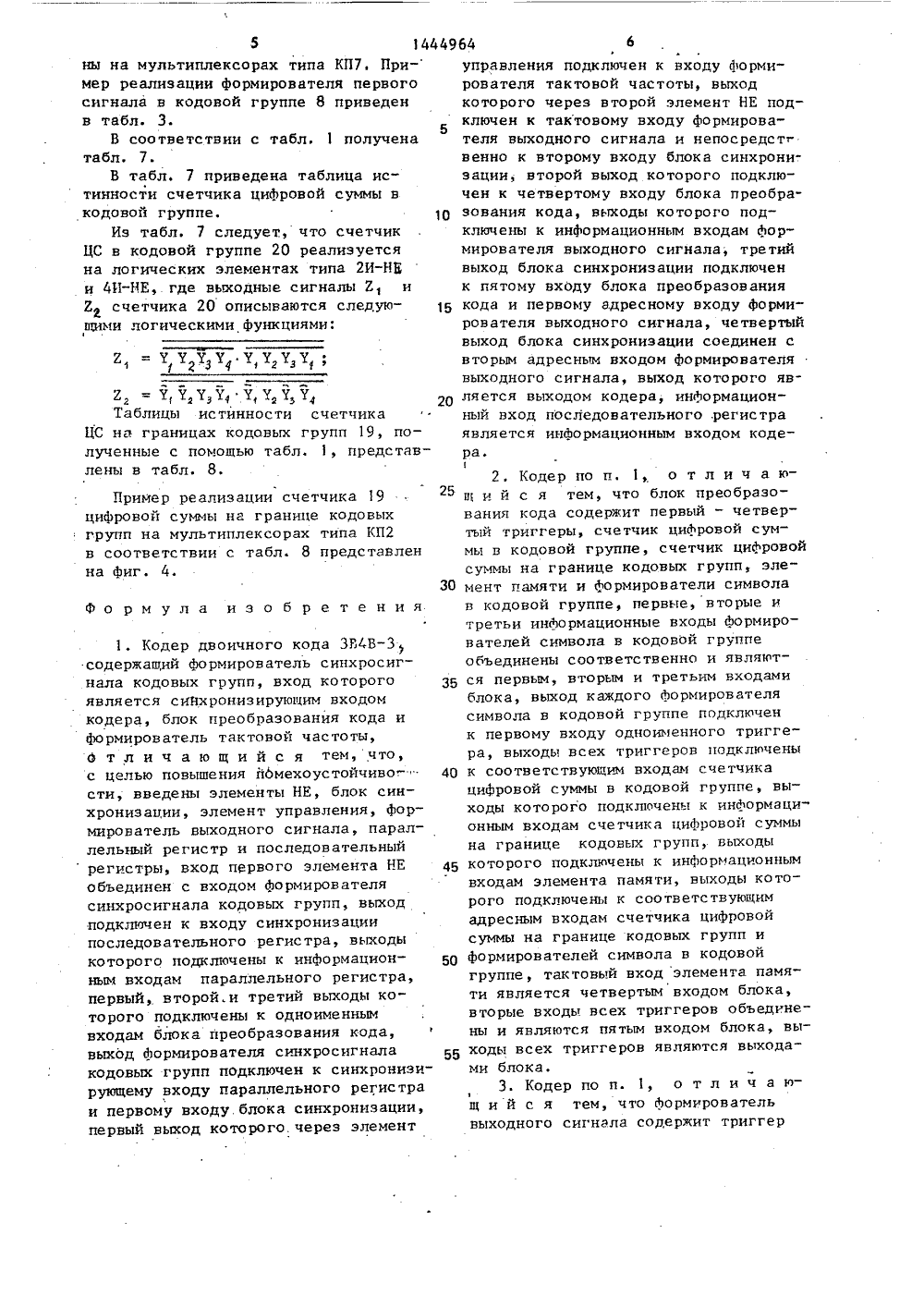

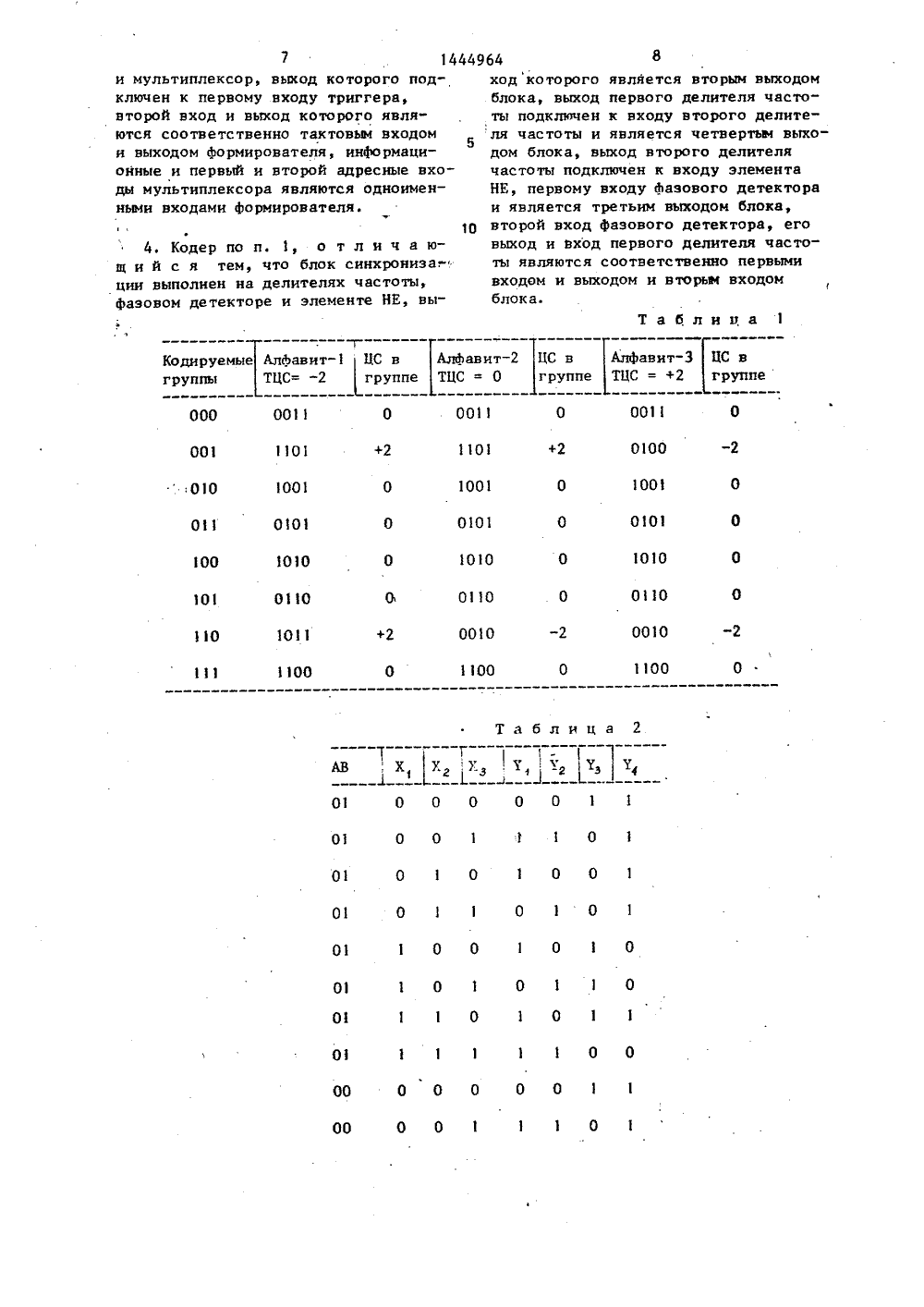

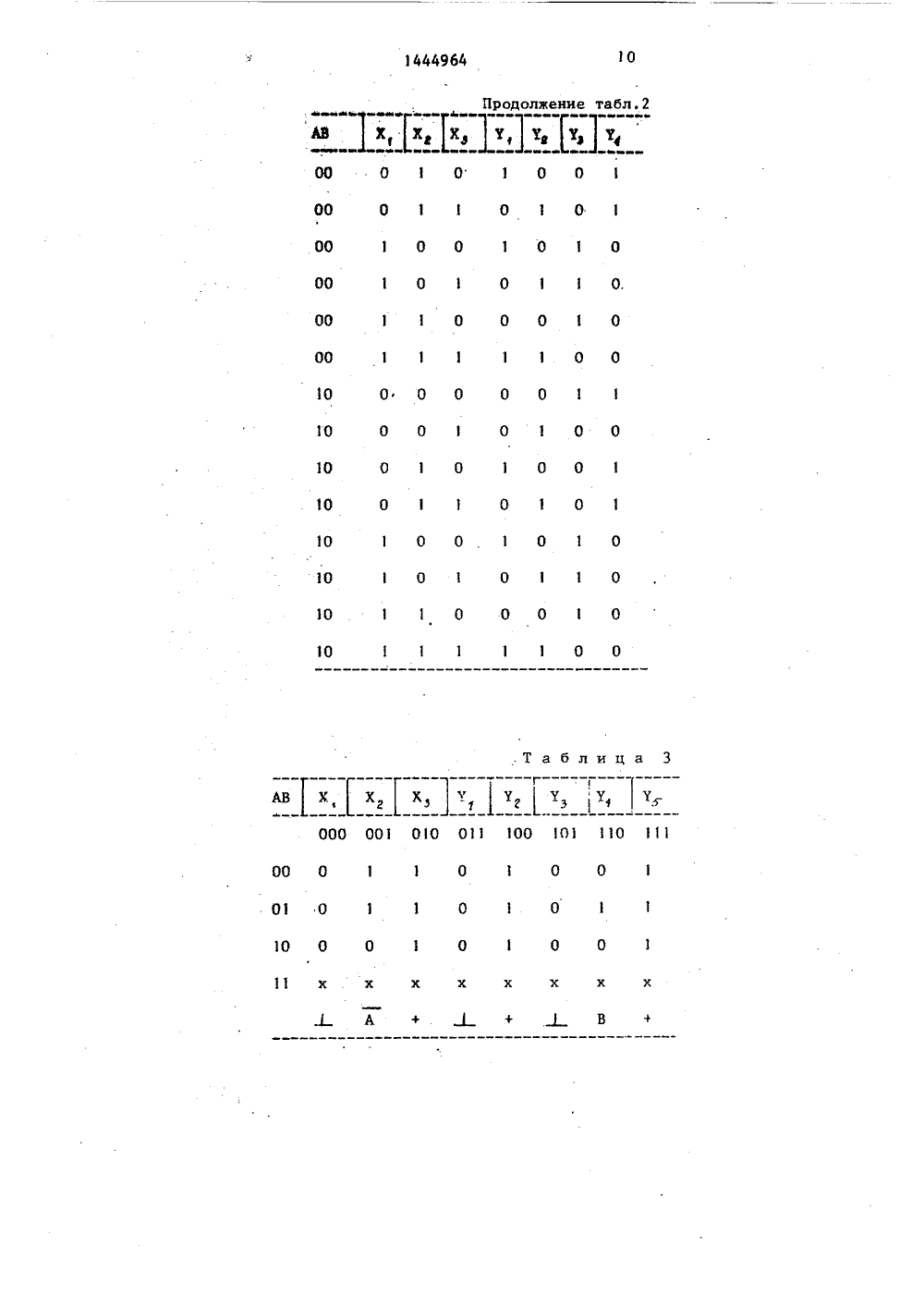

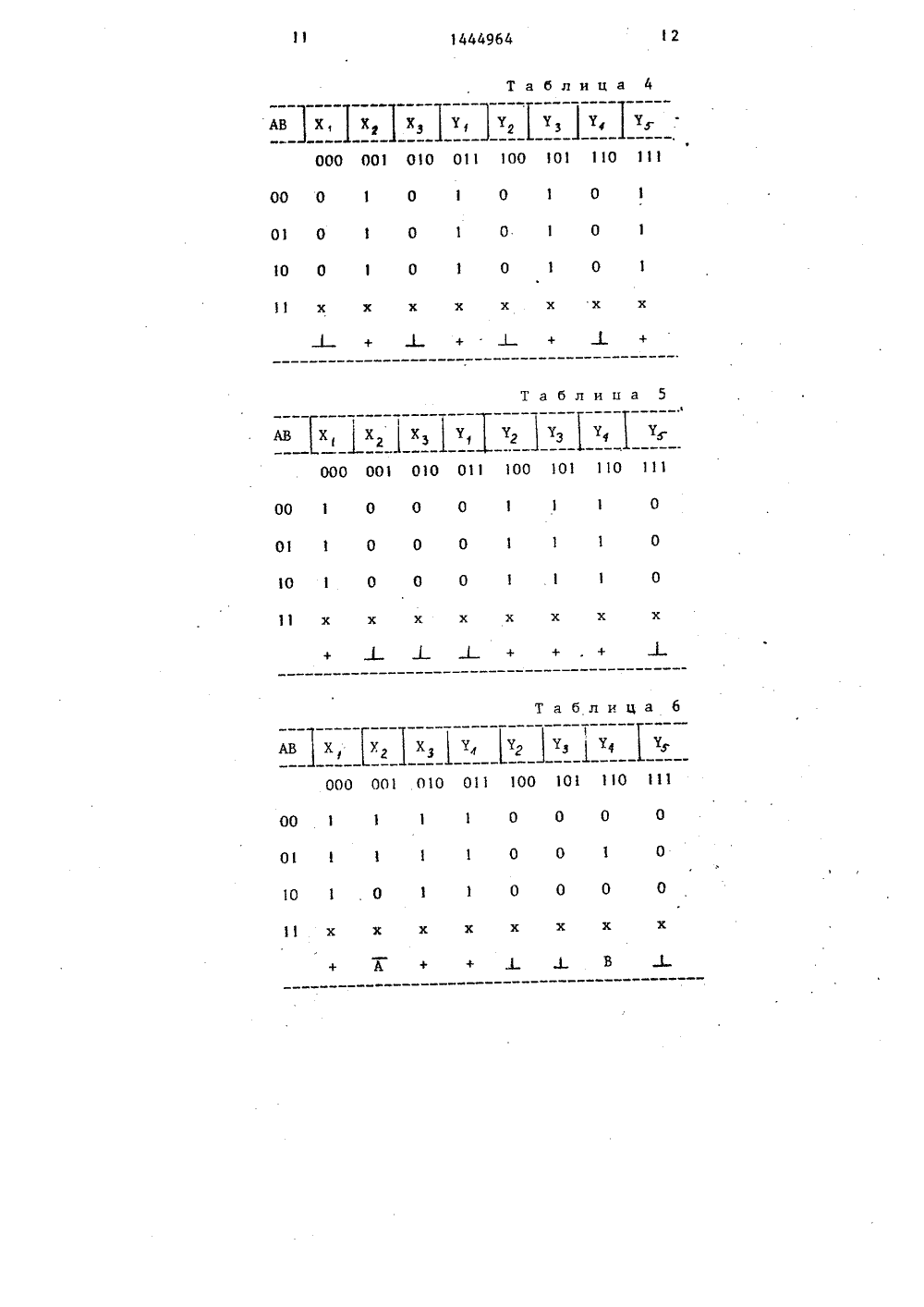

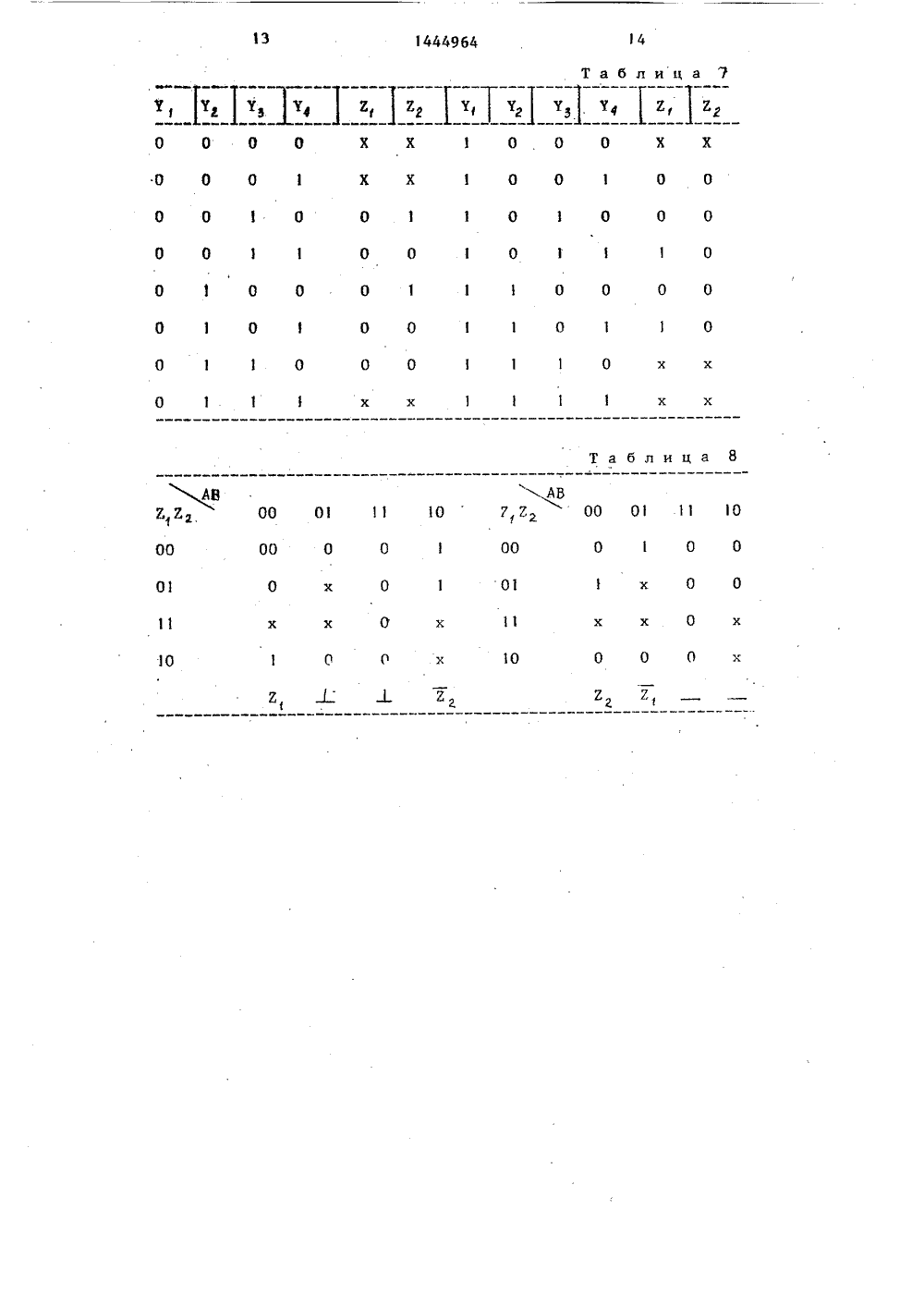

СОЮЗ СОВЕТСКИХСОЩ 4 АЛИСТИЧЕСКИКРЕСПУБЛИК Ц 9 Ог. 0 54 Н 0 ОПИСАНИЕ ИЗОБРЕТК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ-3,Е:.,-1 Чмщ ьЪ тПГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРпо делАм изоБРетений и ОткРытий(56) Мурадян А,Г. и Гинзбург С.А. Системы передачи инФормации по оптическому кабелю, М.: Связь, 1980, с. 137.Авторское свидетельство СССР Р 815953, кл. Н 04 1, 5/00, 1981, (54) КОДЕР ДВОИЧНОГО КОДА ЗВ 4 В(57) Изобретение относится к электро связи.и может найти применение в пиФ ровых с ис темах переда ванных по оптико-воло релейным линиям связи тения является повыше тойчивости кодера. УС держит блоксинхрон рователь 2 выходного мент НГ 3, последоват 4, Формирователь 5 син довых групп, параллел блок 7 преобразования ватель 8 тактовой час 9 управления и элемен ф-лы, 4 ил табл. и, организоонным и радио- Целью изобреие помехоусройство созации, Формиигнала, злельный регистр хросигнала коный регистр 6, кода, Формирооты, злемен НЕ 1 О, 3 з1444964 ставитель О.хред Л, Олийн СРедактор И. Сегляник Т Корректор М. 1 емчи Заказ 6516 Тираж одписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж, Раушская наб д. 4 одствеино рафическое предприятие, г. Ужгород, ул. ПроектИзобретение относится к электросвязи и может быть использовано дляпередачи цифровой информации по волоконно-оптическим и радиорелейным5линиям связиаЦель изобретения - повышение помехоустойчивости кодера.На Фиг. 1 приведена структурнаясхема кодера двоичного кода ЗВ 4 В; 1 Она Фиг. 2 - временные диаграммы работы устройства; на Фиг. 3 - практическая реализация Формирователя первого символа в кодовой группе; нафиг. 4 - счетчик цифровой суммы на 15границе кодовых групп.Кодер содержит блок 1 синхронизации, формирователь 2 выходного сигнала, элемент НЕ 3, последовательныйрегистр 4, формирователь 5 синхросигнала кодовых групп, параллельный регистр 6, блок 7 преобразования кода,формирователь 8 тактовой частоты,блок 9 Фазовой автоподстройки часто -ты и элемент НЕ 10. 25Блок 1 синхронизации содержит зле -мент НЕ 11, фазовый детектор 12, делители 13 и 14 частоты.Блок 7 преобразования кода содер -жит триггеры 15-18, счетчик 19 цифровой суммы на границе кодовых групп,счетчик 20 цифровои суммы в кодовойгруппе, элемент 21 памяти, Формирователи 22-25 символа в кодовой группе.Формирователь 2 выходного сигналасодержит триггер 26 и мультиплек-.сор 27,На фиг, 2 показаны следующие сиг -налы: а - исходный двоичный сигнал;б - тактовый сигнал на выходе первого 40элемента НЕ 3; в,г и д - сигналы навыходах последовательного регистра4;, е - сигнал на выходе формирователя 5 синхросигнала кодовых групп;ж - сигналы на выходах параллельного д 5регистра 6; з - сигналы на выходахэлемента памяти 21; и, к, л, мсигналы на выходах формирователейпервого 22, второго 23, третьего 24и четвертого 25 символов в кодовойгруппе соответственно; н - сигнална выходе делителя 13 частоты; осигналы на выходах первого, второго,третьего и четвертого триггеров 15,16, 17 и 1.8; и - сигналы на выходахсчетчика 20 цифровой суммы в кодовойгруппе;,. р - сигналы на выходах счетчика 19 цифровой суммы на границахкодовых групп; с - сигнал на выходе элемента НЕ 11; т - сигнал на выходепервого делителя частоты на два 23;у - сигнал на выходе Формирователя 8тактовой частоты; ф - сигнал на выходе мультиплексора 27; х - сигнал навыходе элемента НЕ 10; ц - сигнална выходе устройства.Устройство работает следующим образом.Преобразование по закону кодирова"ния ЗВ 4 Восуществляется в соответствии с табл. 1,В табл 1 рядом с каждой кодовойгруппой указано значение цифровойсуммы, определяемое как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам0 и 1 кода поставлено в соответствиенормированное напряжение -1 и +1.В табл 1 имеется три алфавита,каждый из которых используется присоответствующем значении текущей цифровой суммы (ТЦС) на границах кодо -вых групп к моменту поступления кодируемой группы. ТЦС определяется какалгебраическая сумма амплитуд импульсов в переданном сигнале от начала передачи до настоящего момента.Например, если к моменту передачикодируемой группы 001 (табл. 1)ТЦС = -2, то эта группа передаетсякодовой группой 1101 в ЦС в группе,равной +2. При этом, ТЦС к моментупоступления следующей кодируемойгруппы будет равна (-2)+(+2)= (О)и следуюшая группа будет кодироваться группой из алфавита -2 с ТЦС = О.Как следует из алгоритма кодирования тактовая частота линейногосигнала повышается в 1,33 раза. Приэтом, в устройстве количество уровнейвпередаваемом линейном сигнале равно двум, что позволяет, при равенстве тактовых частот линейного сигнала,повысить помехоустойчивость передаваемого сигнала примерно в два раза,Двоичный сигнал (фиг. 2,а) запи -сывается в последовательный регистр(Фиг, 1, фиг. 2, в,г,д) тактовымсигналом с выхода элемента НЕ 3(Фиг. 2,б) и переписывается синхро -сигналом кодовых групп (Фиг. 2,е),поступающим с выхода формирователя 5синхросигнала кодовых групп, в параллельный регистр 6 (Фиг, 2,ж). Сигналы с выходов параллельного регистра6 (фиг. 2,ж) поступают на соответствующие входы формирователей 22, 23, 24и 25 первого, второго, третьего ичетвертого символов в кодовой группе.На остальные входы этих формировате -лей 22 - 25 поступают сигналы с выхода элемента 21 памяти (фиг. 2,з),5несущие информацию о значении ТБС всигнале. Так, например, соотношениесигналов на Фиг. 2,з 00 соответству -ет значению ТЦС = О,О - ТЦС = +2и =1 - ТЦС = - 2. В соответствии сэтим формирователи 22 - 25 Формируютна своих выходах символы кода ЗВ 4 В(согласно табл. 1), представленныев параллельном виде (Фиг. 2,и,к,л,м).5На Фиг. 2 первое преобразование выделено жирной линией. Группа 001(фиг. 2,а,ж) при ТЦС = 0 (фиг. 2,з)кодируется группой 1101 (Фиг. 2,и,к,л,м) (см. табл. 1),20Сигналы с выходов формирователей22 - 25 (Фиг. 2,и к,л,м) поступаютна информационные входы соответствующих триггеров 15, 16, 17 и 18, натактовые входы которых подается сигнал с выхода второго делителя 13 частоты (Фиг. 2,н). Сигналы с выходовтриггеров 15 - 18 (Фиг. 2,о) поступают на соответствующие входьг счетчика20 цифровой суммы в кодовой группе,сигналы на выходе которого (фиг.2,п)несут информацию о цифровой суммев кодовой группе: 00 - ЦС = 0; 01ЦС = -2; 10 - ЦС = +2. Закодированныев двоичном виде значения ЦС в кодовойгруппе ,фиг. 2,п) поступают на входысчетчика 19 ЦС на границе кодовыхгрупп, на другие входы которого с выходов элемента 2 поступают значенияТЦС на границе кодовых групп, пред 40ставленные также в двоичном виде(Фиг. 2,з). Сигналы на выходе счетчика 19 изображены на Фиг. 2,р,Синхрониз апия сигналов, участвующихв обработке и преобразовании двоичного 45сигнала (фиг. 2,а), осуществляется спомощью блока 1 синхронизации, а временные соотношения между ними представлены на Фиг. 2,б,е,н,с,т,у,х.Сигналы с выходов триггеров 5-18(Фиг. 2,о) поступают на соответст-.вующие информационные. входы мультиплексора 27, на адресные входы которого поступают сигналы с выходов(фиг. 2,с,т) делителей 13 и 14 частоты. Импульсы тактовой частоты линейного сигнала (фиг. 2,у) с выходаформирователя 8, инвертируются элементом 1 О НЕ (фиг. 2,х) и поступают на тактовый вход пятого триггера 26,на информационный вход которого поступает сигнал с выхода мультиплексора 27 (фиг. 2,Ф). Триггер 26 необходим для устранения пролезаний навыходе мультиплексора 27 и формирования сигнала двоичного кода ЗВ 4 В(Фиг. 2,ц).Последовательный 4 и параллельный6 регистры могут быть выполнены в виде тактируемых регистров на 0-триггерах, а формирователь 5 синхросигналакодовых групп - в виде делителя частоты на три. Фазовый детектор 12 может быть выполнен в виде цифровогофазового детектора на Ю-триггере, насхеме И и т.д, Формирователь 8 тактовой частоты может быть выполнен в виде задающего генератора тактовой частоты, а блок 9 - в виде, например,последовательно соединенных фильтранижних частот, усилителя и варикапа,управляюпгего частотой генератора.Формирователи 22 - 25 первого,второго третьего и четвертого симРволов в кодовой группе должны бытьвыполнены в соответствии с таблицейистинности, представленной в табл. 2и полученной из таблицы преобразования ЗВ 4 В(табл. 1)В табл,2 А и В - сигналы с выходаэлемента 21 памяти (Фиг. 2,з), ХХ и Х - входные символы (Фиг. 2,ж),11, гг, 3, г 4 - спг 1 волы кодаФиг. 2,р,к,л,м). В соответствии стабл, 2 получены таблицы истинностиформирователей 22 - 25 первого, второго, третьего и четвертого символовв кодовой группе (Фиг. 1).В табл. 3 приведена таблица истинности формирователя 22 первогосимвола в кодовой группе.В табл. 3 введены следующие обозначения: х- безразличное состояние.Под табл, 3 приведены сигналы, кото-,рые необходимо подать на информационные входы мультиплексора типа КП 7.В табл. 4 приведена таблица истинности формирователя 23 второгосимвола в кодовой группе,В табл. 5 прчведена таблица ис"тинности Формирователя 23. третьего символа в кодовой группе,В табл. 6 приведена таблица истинности формирователя четвертогосимвола в кодовой группе,Формирователи 22-25 в соответствии с табл. 3-6, могут быть выполне5 14449 ны на мультиплексорах типа КП 7, При- мер реализации формирователя первого сигнала в кодовой группе 8 приведен в табл. 3.5В соо тве тс твин с табл. 1 получена табл. 7.В табл. 7 приведена таблица истинности счетчика цифровой суммы в кодовой группе. 10Из табл. 7 следует, что счетчик ЦС в кодовой группе 20 реализуется на логических элементах типа 2 И-НЕ и 4 И-НЕ, где выходные сигналы Е, и Е счетчика 20 описываются следую йщими логическими функциями: Е= У Т Т У У, Уг Уз У 1 2г1г з гТаблицы истинности счетчика ЦС на границах кодовых групп 19, полученные с помощью табл. 1, представлены в табл. 8. 20 25 Пример реализации счетчика 19 цифровой суммы на границе кодовых групп на мультиплексорах типа КП 2 в соответствии с табл. 8 представлен на фиг. 4. 30 Формула изобретения 50 1. Кодер двоичного кода 384 В содержащий формирователь синхросигнала кодовых групп, вход которогоявляется сийхронизирующим входомкодера, блок преобразования кода иформирователь тактовой частоты,отличающийся тем, что,с целью повышения йЬмехоустойчиво" 40сти, введены элементы НЕ, блок синхронизации, элемент управления, формирователь выходного сигнала, параллельный регистр и последовательныйрегистры, вход пЕрвого элемента НЕ 45объединен с входом формирователясинхросигнала кодовых групп, выходподключен к входу синхронизациипоследовательного регистра, выходыкоторого подключены к информационным входам параллельного регистра,первый, второй.и третий выходы которого подключены к одноименнымвходам блока преобразования кода,выход формирователя синхросигналакодовых групп подключен к синхронизирующему входу параллельного регистраи первому входу блока синхронизации,первый выход которого. через элемент б 4 управления подключен к входу формирователя тактовой частоты, выход которого через второй элемент НЕ подключен к тактовому входу формирователя выходного сигнала и непосредстг венно к второму входу блока синхронизации, второй выход которого подключен к четвертому входу блока преобразования кода, выходы которого подключены к информационным входам формирователя выходного сигнала; третий выход блока синхронизации подключен к пятому входу блока преобразования кода и первому адресному входу формирователя выходного сигнала, четвертый выход блока синхронизации соединен с вторым адресным входом формирователя выходного сигнала, выход которого является выходом кодера, информационный вход последовательного .регистра является информационным входом кодера.2. Кодер по и. 1, о т л и ч а ющ и й с я тем, что блок преобразования кода содержит первый - четвертый триггеры, счетчик цифровой суммы в кодовой группе, счетчик цифровой суммы на границе кодовых групп, элемент памяти и формирователи символа в кодовой группе, первые, вторые и третьи информационные входы формирователей символа в кодовой группе объединены соответственно и являются первым, вторым и третьим входами блока, выход каждого формирователя символа в кодовой группе подключен к первому входу одноименного триггера, выходы всех триггеров подключены к соответствующим входам счетчика цифровой суммы в кодовой группе, выходы которого подключены к информационным входам счетчика цифровой суммы на границе кодовых групп, выходы которого подключены к информационным входам элемента памяти, выходы которого подключены к соответствующим адресным входам счетчика цифровой суммы на границе кодовых групп и формирователей символа в кодовой группе, тактовый вход элемента памяти является четвертым входом блока, вторые входы всех триггеров объединены и являются пятым входом блока, выходы всех триггеров являются выходами блока.3. Кодер по и. 1, о т л и ч а ющ и й с я тем, что формирователь выходного сигнала содержит триггерТаблица 1 Кодируемые АлфавитЦС в АлФавитЦС в АлфавитЦС вгруппы ТЦС= -2 группе ТЦС = О группе ТЦС = +2 группе 0011 0011 0 0011 000 0100 1101 1101 001 001 0 100 1001 0 010 0 0101 0101 0 01 О 1010 0 1010 ОО 0110 0110 010 101 0010 0030 1011 110 0 1100 1 300 0 100 Т а б л и ц а 2 АВ, Х, Х )-зг Тэ .1 01 0 0 0 0 0 1 1 03 0 0 1 1 1 0 1 01 0 1 0 1 0 0 1 01 0 1 1 0 3 0 1 01 1 О 0 1 0 1 0 01 1 0 1 0 1 1 О 01 1 1 0 1 0 1 3 1 1 1 1 1 0 0 00 0 0 0 0 0 1 1 00 0 0 1 1 1 0 1 7 1444 и мультиплексор, выход которого подключен к первому входу триггера, второй вход и выход которого являются соответственно тактовым входом5 и выходом Формирователя, информационные и первый и второй адресные входы мультиплексора являются одноименными входами Формирователя.3 О4, Кодер по п. 1, о т л и ч а ющ и й с я тем, что блок синхрониза-. ции выполнен на делителях частоты, фазовом детекторе и элементе НЕ, вы 964 8ход которого является вторым выходом блока, выход первого делителя частоты подключен к входу второго делителя частоты и является четвертью выходом блока, выход второго делителя частоты подключен к входу элемента НЕ, первому входу Фазового детектора и является третьим выходом блока, второй вход Фазового детектора, его выход и вход первого делителя частоты являются соответственно первыми входом и выходом и вторьи входом блока.

СмотретьЗаявка

4067200, 01.04.1986

ПРЕДПРИЯТИЕ ПЯ Р-6609

КОТИКОВ ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 13/13

Метки: 3в4в-3, двоичного, кода, кодер

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/10-1444964-koder-dvoichnogo-koda-3v4v-3.html" target="_blank" rel="follow" title="База патентов СССР">Кодер двоичного кода 3в4в-3</a>

Предыдущий патент: Декодирующее устройство -разрядного кода

Следующий патент: Устройство для контроля данных, представленных в коде к из

Случайный патент: Устройство для дистанционного управления двухпозиционными элементами