Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

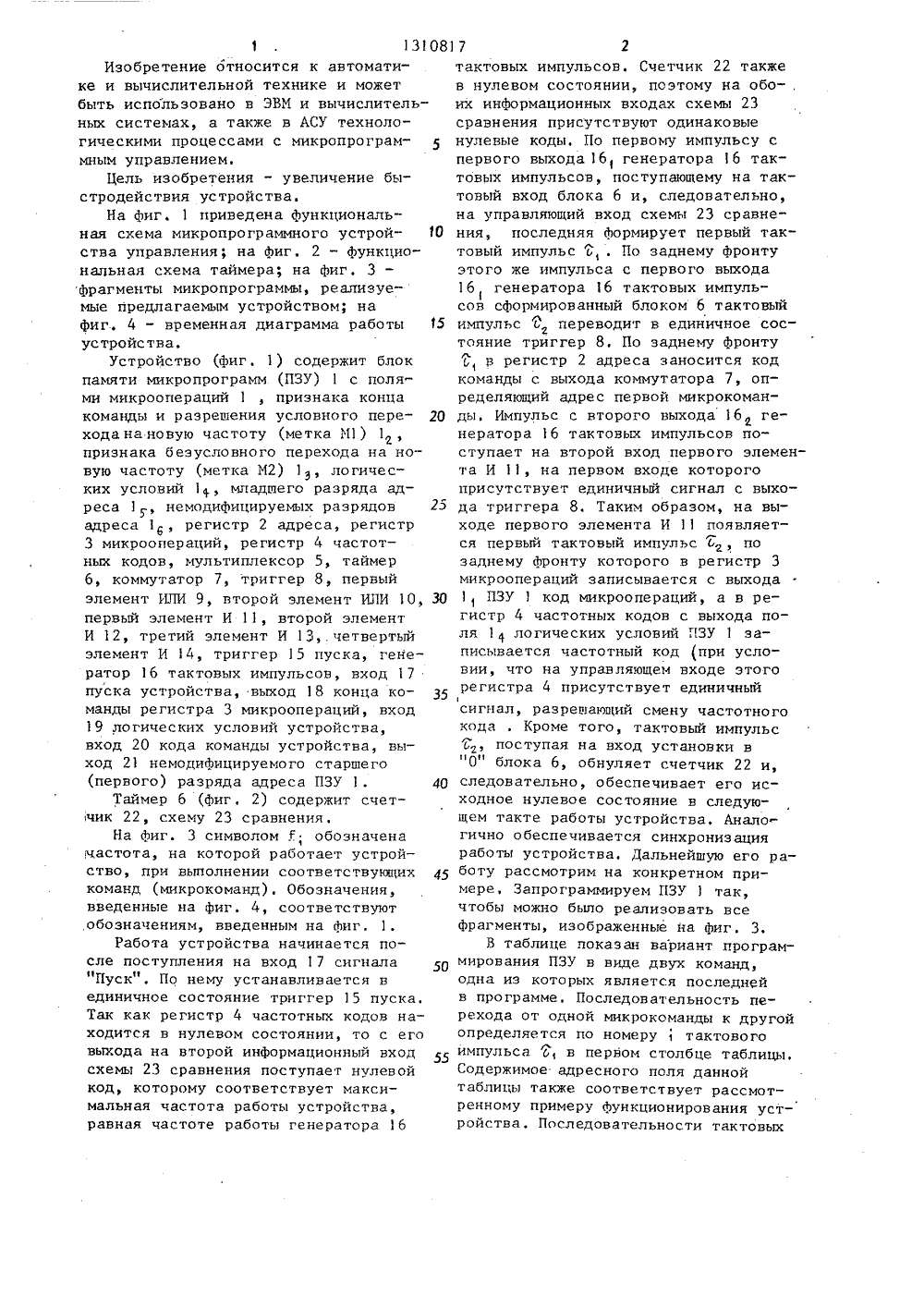

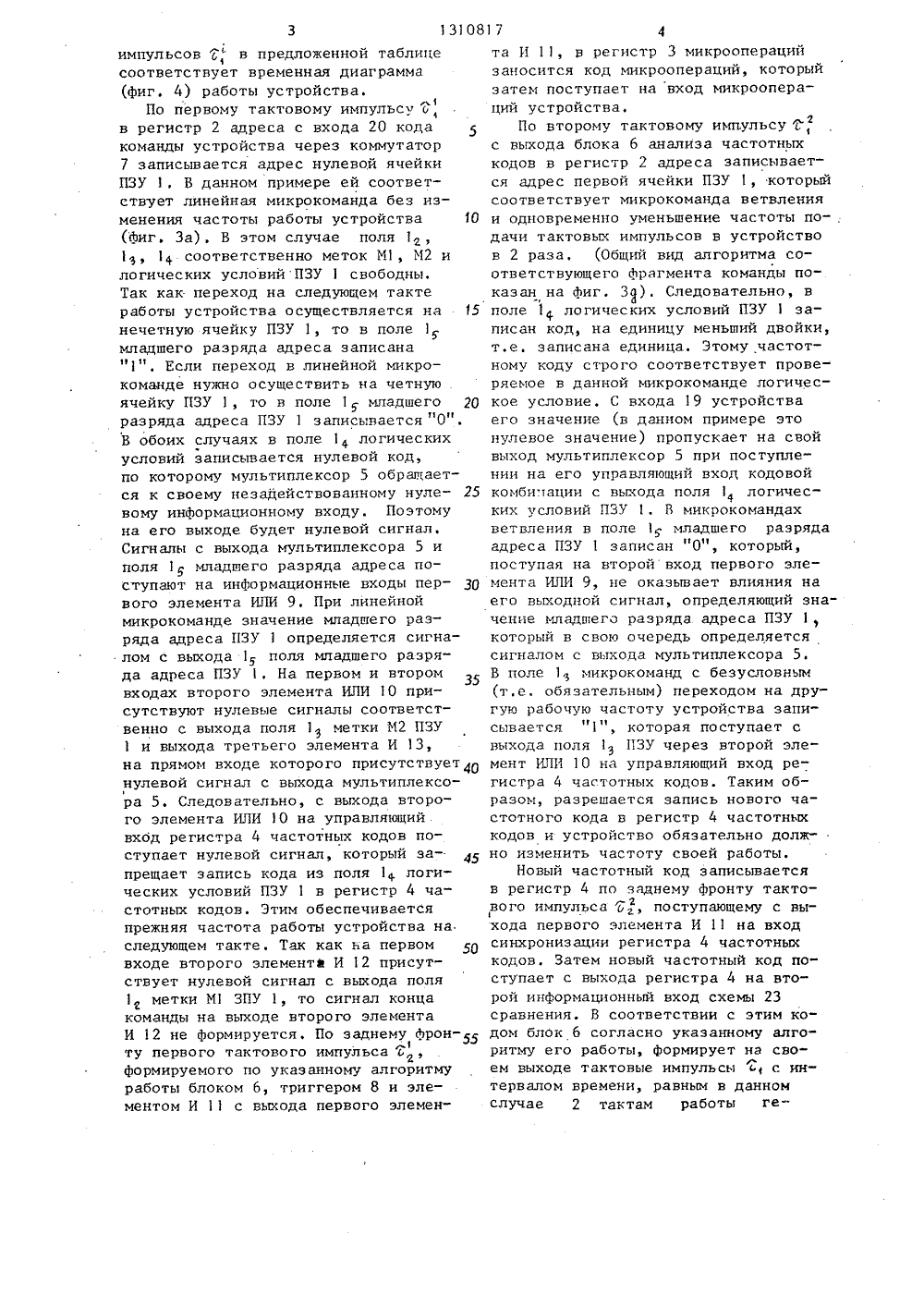

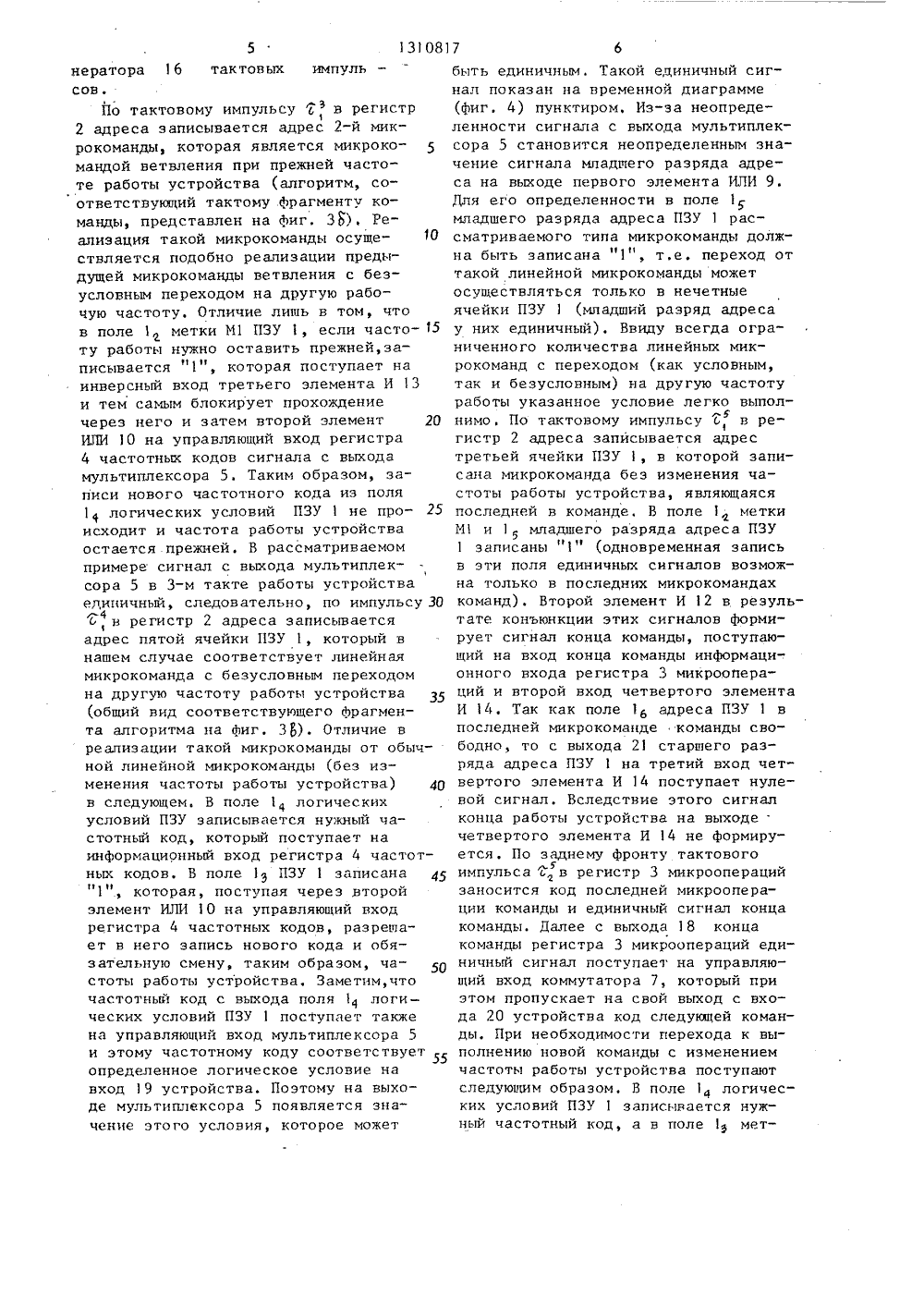

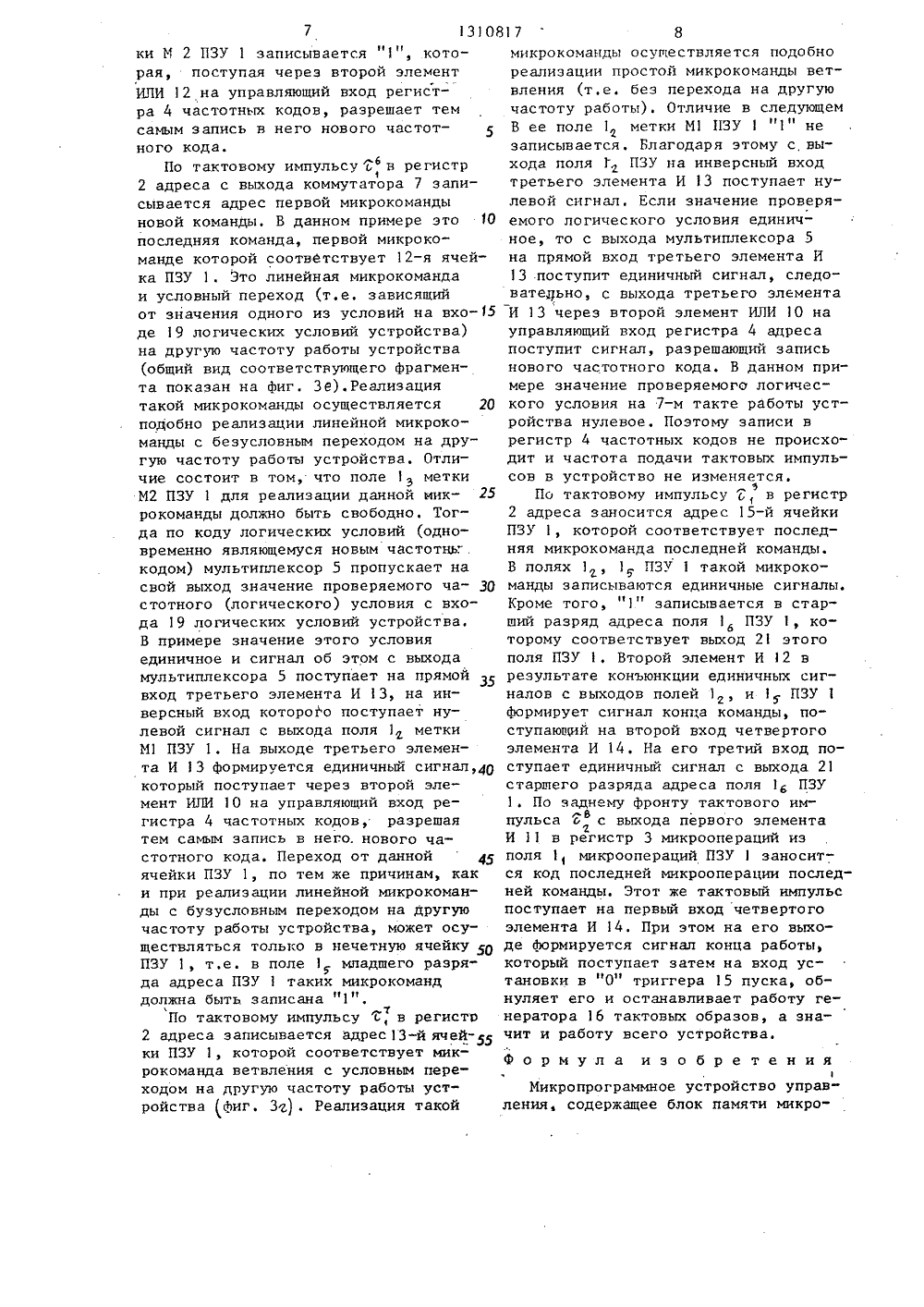

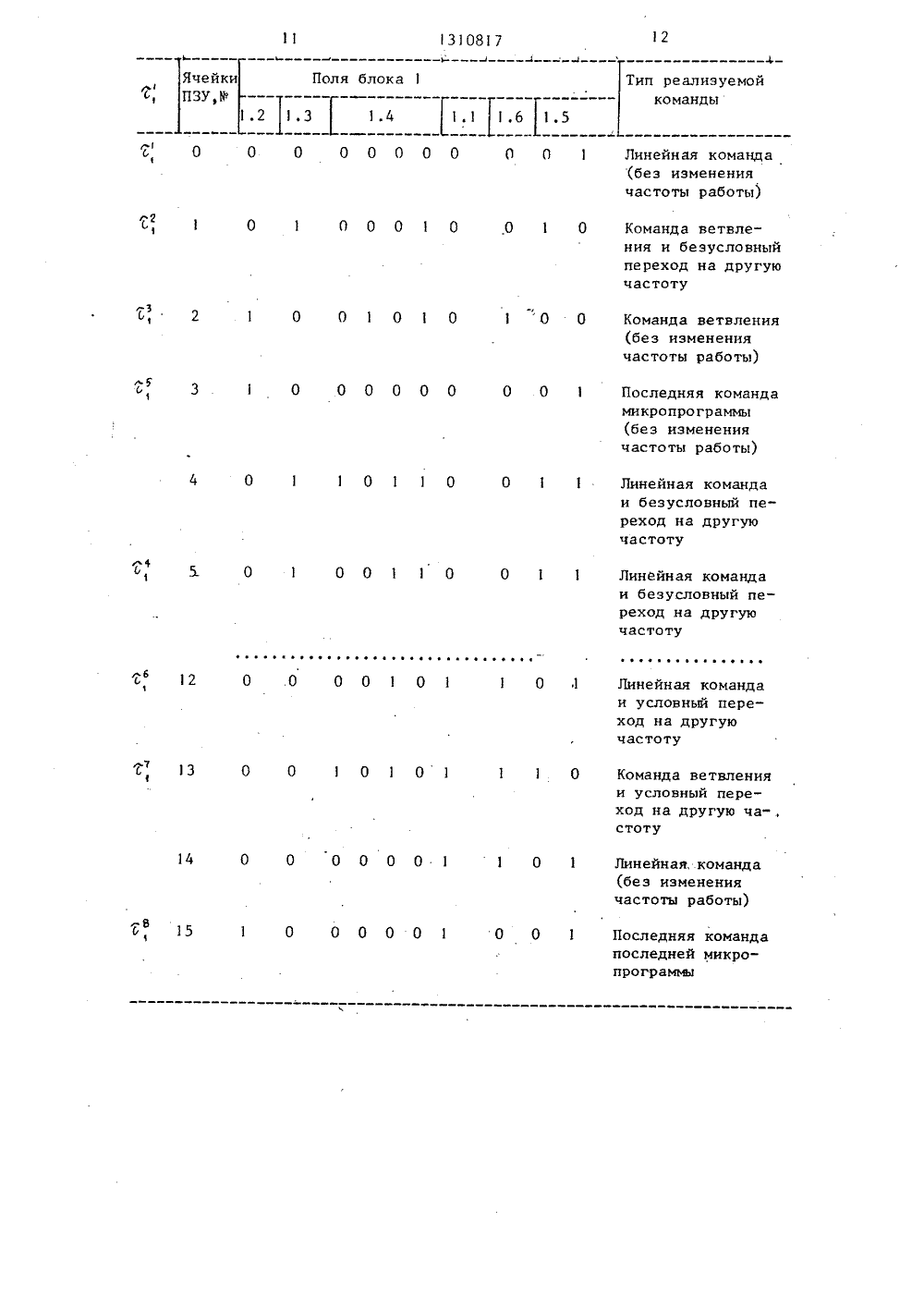

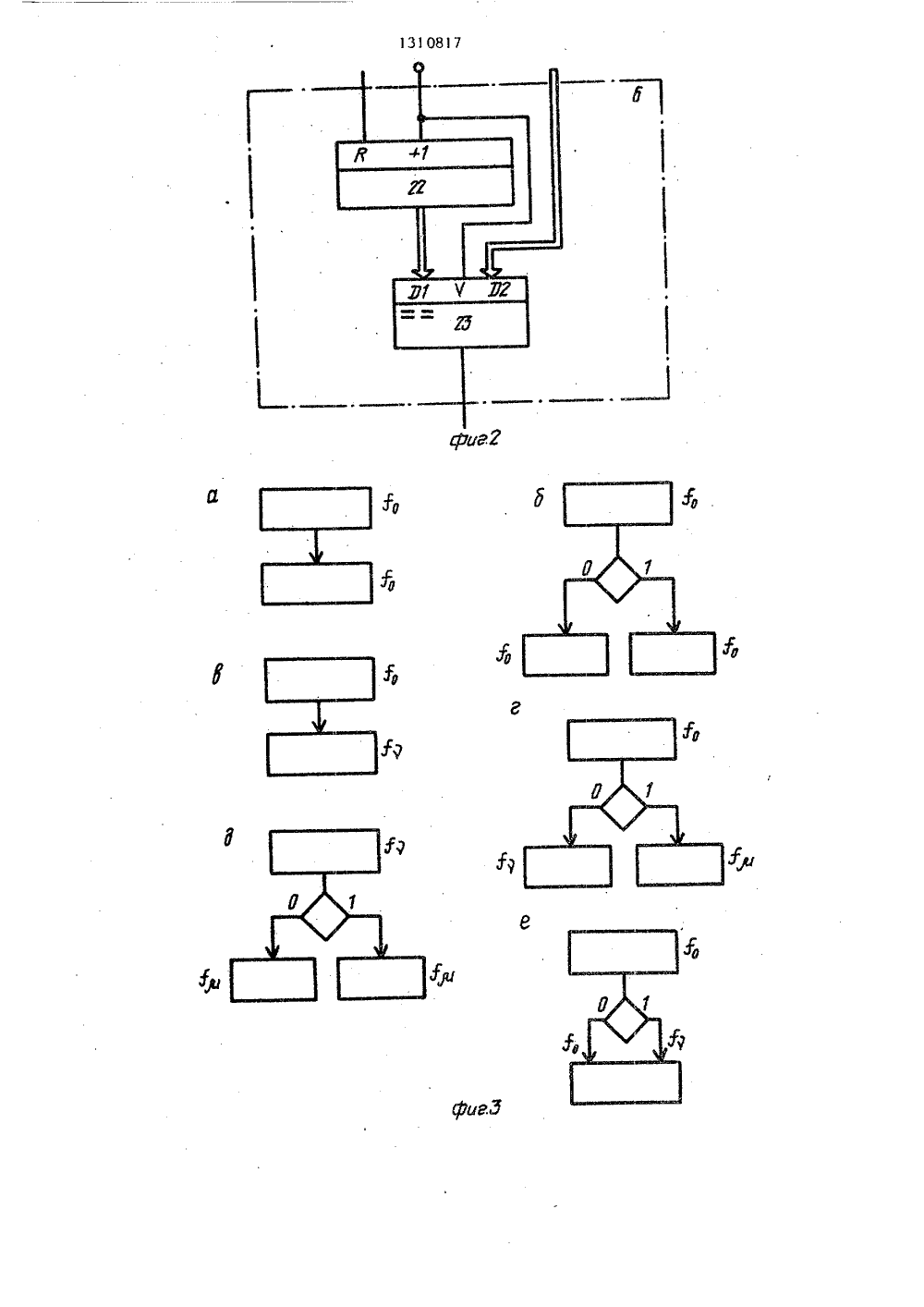

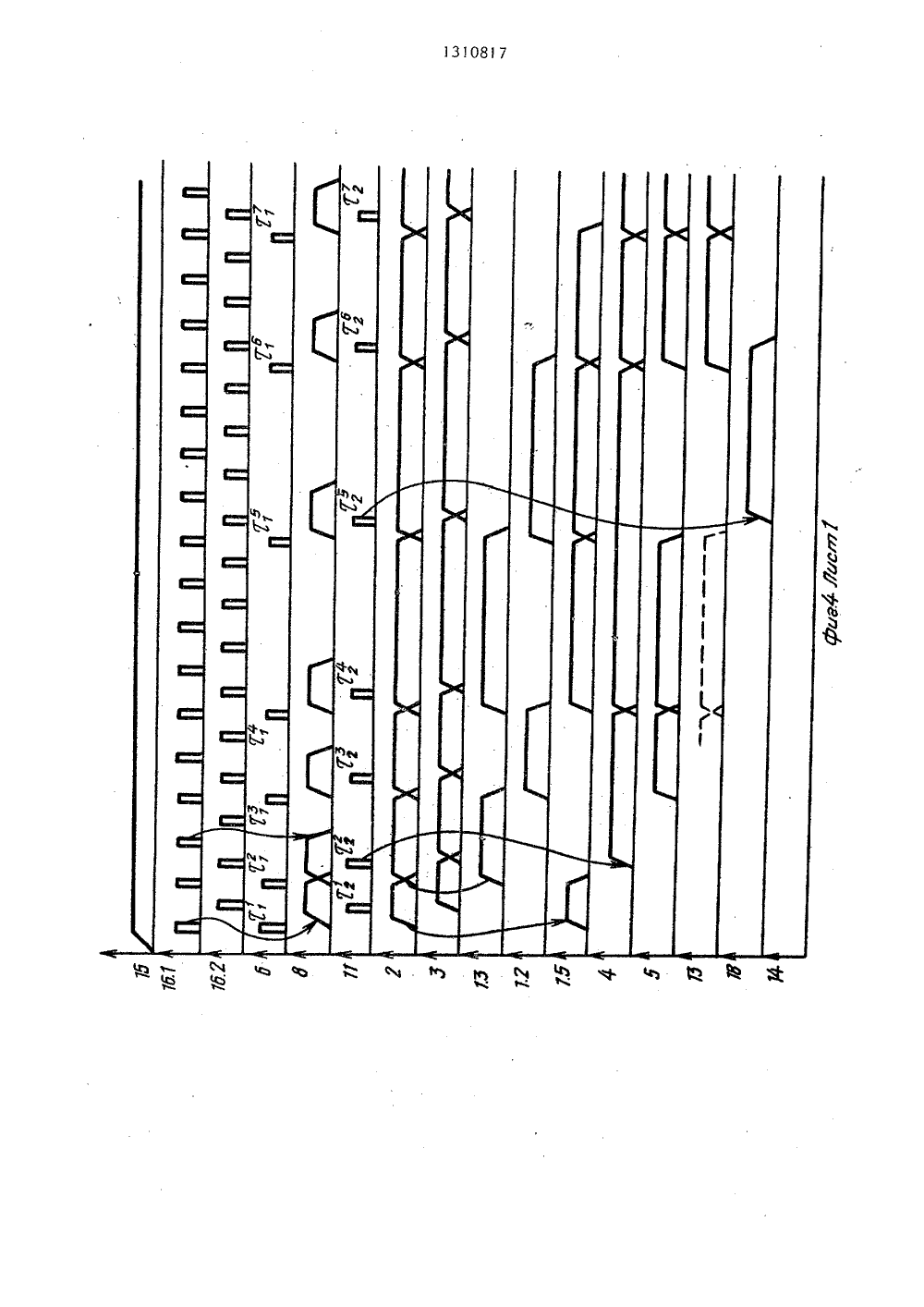

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 119) 111 51)4 С 06 Р 9/22 РЕТЕНИ ИСАНИ ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ А ВТОВСНОМУ СВИДЕТЕЛЬСТВУ(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЗВМ и вычислительных системах, а также в АСУс микропрограммным управлением. Дельизобретения - увеличение быстродействия и расширение области примененияпутем обеспечения возможности выполнения ветвлений различных типов по"частотным логическим условиям. Микропрограммное устройство управлениясодержит ПЗУ 1, регистры адреса 2,микроопераций 3, частотных кодов 4мультиплексор 5, таймер 6, коммутатор 7, триггер 8, элементы ИЛИ 9 и10, элементы И 11-.14, триггер 15 пуска, генератор 16 импульсов. 4 ил1 31081 7 Составитель А,МихайлТехред Л.Олейник корректор А Редактор М,Дыль аказ 1892 е роизводственно-полиграфическое предприятие, г, Ужгород, ул. Проектная Тираж 673 ВНИИПИ Государственного ко по делам изобретений и 35, Москва, Ж, РаушскаяПодпи итета ССС ткрытий наб д.1 131081Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в ЗВМ и вычислительных системах, а также в АСУ технологическими процессами с микропрограммным управлением.Цель изобретения - увеличение быстродействия устройства.На Фиг. 1 приведена Функциональная схема микропрограммного устройства управления; на Фиг. 2 - Функционапьная схема таймера; на фиг. 3 -Фрагменты микропрограммы, реализуемые предлагаемым устройством; нафиг. 4 - временная диаграмма работы 15устройства,Устройство (Фиг. 1) содержит блокпамяти микропрограмм (ПЗУ) 1 с полями микроопераций 1 , признака концакоманды и разрешения условного перехода на новую частоту (метка Г 1) 1,признака безусловного перехода на новую частоту (метка М 2) 1, логических условий 11, младшего разряда ад -реса 1, немодифицируемых разрядов 25адреса 1, регистр 2 адреса, регистр3 микроонераций, регистр 4 частотных кодов, мультиплексор 5, таймерб, коммутатор 7, триггер 8, первыйэлемент ИЛИ 9, второй элемент ИЛИ 10, 30первый элемент И 11, второй элементИ 12, третий элемент И 13,.четвертыйэлемент И 14, триггер 15 пуска, генератор 16 тактовых импульсов, вход 17пуска устройства, выход 18 конца команды регистра 3 микроопераций, вход19 логических условий устройства,вход 20 кода команды устройства, вы -ход 21 немодифицируемого старшего(первого) разряда адреса ПЗУ 1, 40Таймер 6 (Фиг, 2) содержит счетчик 22, схему 23 сравнения.На Фиг. 3 символом Г; обозначеначастота, на которой работает устройство, при выполнении соответствующих 45команд (микрокоманд). Обозначения,введенные на фиг. 4, соответствуютобозначениям, введенным на Фиг. 1,Работа устройства начинается после поступления на вход 17 сигнала"Пуск", По нему устанавливается вединичное состояние триггер 15 пуска.Так как регистр 4 частотных кодов находится в нулевом состоянии, то с еговыхода на второй информационный входсхемы 23 сравнения поступает нулевойкод, которому соответствует максимальная частота работы устройства,равная частоте работы генератора 6 7 2тактовых импульсов, Счетчик 22 также в нулевом состоянии, поэтому на обо-, их информационных входах схемы 23 сравнения присутствуют одинаковые нулевые коды. По первому импульсу с первого выхода 16 генератора 16 тактовых импульсов, поступающему на тактовый вход блока 6 и, следовательно, на управляющий вход схемы 23 сравнения, последняя Формирует первый тактовый импульс ь, . По заднему фронту этого же импульса с первого выхода 16 генератора 16 тактовых импульсов сформированный блоком 6 тактовый импульс ь переводит в единичное состояние трйггер 8. По заднему Фронтув регистр 2 адреса заносится код команды с выхода коммутатора 7, определяющий адрес первой микрокоманды. Импульс с второго выхода 16 генератора 16 тактовых импульсов поступает на второй вход первого элемента И 11, на первом входе которого присутствует единичный сигнал с выхода триггера 8. Таким образом, на выходе первого элемента И 11 появляется первый тактовый импульс 6, по заднему Фронту которого в регистр 3 микроопераций записывается с выхода 1, ПЗУ 1 код микроопераций, а в регистр 4 частотных кодов с выхода полялогических условий ПЗУ 1 записывается частотный код (при условии, что на управляющем входе этого регистра 4 присутствует единичный 1сигнал, Разрешающий смену частотного кода . Кроме того, тактовый импульс т, поступая на вход установки в "0" блока 6, обнуляет счетчик 22 и, следовательно, обеспечивает его исходное нулевое состояние в следующем такте работы устройства. Аналогично обеспечивается синхронизацияработы устройства. Дальнейшую его работу рассмотрим на конкретном примере, Запрограммируем ГЗУ 1 так, чтобы можно было реализовать все фрагменты, изображенные на Фиг3.В таблице показан вариант программирования ПЗУ в виде двух команд,одна из которых является последнЕйв программе. Последовательность перехода от одной микрокоманды к другойопределяется по номерутактовогоимпульса 3, в первом столбце таблицы.Содержимое адресного поля даннойтаблицы также соответствует рассмотренному примеру Функционирования устройства, Последовательности тактовых131 081 7 импульсов с" в предложенной таблице соответствует временная диаграмма (фиг. 4) работы устройства.л 1По первому тактовому импульсу о в регистр 2 адреса с входа 20 кода команды устройства через коммутатор 7 записывается адрес нулевой ячейки ПЗУ 1. В данном примере ей соответствует линейная микрокоманда без изменения частоты работы устройства О (Лиг. За), В этом случае поля 1, 1 з, 1 соответственно меток М 1, М 2 и логических условий ПЗУ 1 свободны.Так как переход на следующем такте работы устройства осуществляется на 15 нечетную ячейку ПЗУ 1, то в поле 1 младшего разряда адреса записана "1", Если переход в линейной микрокоманде нужно осуществить на четную ячейку ПЗУ 1, то в поле 1 младшего 20 разряда ацреса ПЗУ 1 записывается "0". В обоих случаях в поле 1 логических условий записывается нулевой код, по которому мультиплексор 5 обращается к своему незадействованному нуле вому инАормационному входу. Поэтому на его выходе будет нулевой сигнал.Сигналы с выхода мультиплексора 5 и поля 1 младшего разряда адреса поступают на информационные входы пер вого элемента ИЛИ 9, При линейной микрокоманде значение младшего разряда адреса ПЗУ 1 определяется сигналом с выхода 1 поля младшего разряда адреса ПЗУ 1. На первом и втором входах второго элемента ИЛИ 10 присутствуют нулевые сигналы соответственно с выхода поля 1 метки М 2 ПЗУ 1 и выхода третьего элемента И 13, на прямом входе которого присутствует 40 нулевой сигнал с выхода мультиплексора 5. Следовательно, с выхода второго элемента ИЛИ 10 на управляющий.вход регистра 4 частотных кодов поступает нулевой сигнал, который запрещает запись кода из поля 1 логических условий ПЗУ 1 в регистр 4 частотных кодов. Этим обеспечивается прежняя частота работы устройства на следующем такте. Так как ьа первом входе второго элемента И 12 присутствует нулевой сигнал с выхода поля 1 метки М 1 ЗПУ 1, то сигнал конца команды на выходе второго элемента И 12 не Формируется, По заднему Аронту первого тактового импульсаФормируемого по укаэанному алгоритму работы блоком 6, триггером 8 и элементом И 11 с выхода первого элемен 4та И 11, в регистр 3 микрооперацийзаносится код микроопераций, которыйзатем поступает на вход микроопераций устройства,По второму тактовому импульсу Т,с выхода блока 6 анализа частотныхкодов в регистр 2 адреса записывается адрес первой ячейки ПЗУ 1, которыйсоответствует микрокоманда ветвлеиияи одновременно уменьшение частоты подачи тактовых импульсов в устройствов 2 раза. (Общий вид алгоритма соответствующего Арагмента команды показан на Аиг. 3). Следовательно, вполелогических условий ПЗУ 1 заФписан код, на единицу меньший двойки,т.езаписана единица. Этому частотному коду строго соответствует проверяемое в данной микрокоманде логическое условие. С входа 19 устройстваего значение (в данном примере этонулевое значение) пропускает на свойвыход мультиплексор 5 при поступлении на его управляющий вход кодовойкомбинации с выхода поля 1 логических условий ПЗУ 1. В микрокомандахветвления в поле 1 младшего разрядаадреса ПЗУ 1 записан "0", который,поступая на второйвход первого элемента ИЛИ 9, не оказывает влияния наего выходной сигнал, определяющий значение младшего разряда адреса ПЗУ 1который в свою очередь определяетсясигналом с выхода мультиплексора 5.В поле 1 з микрокоманд с безусловным(т.е. обязательным) переходом на другую рабочую частоту устройства записывается "1", которая поступает свыхода поля 1 ПЗУ через второй элемент ИЛИ 10 на управляющий вход регистра 4 частотных кодов. Таким образом, разрешается запись нового частотного кода в регистр 4 частотныхкодов и устройство обязательно должно изменить частоту своей работы.Новый частотный код записываетсяв регистр 4 по заднему Фронту тактоВого импульса 62) поступающему с выхода первого элемента И 11 на входсинхронизации регистра 4 частотныхкодов. Затем новый частотный код поступает с выхода регистра 4 на второй информационный вход схемы 23сравнения. В соответствии с этим кодом блок 6 согласно укаэанному алгоритму его работы, Формирует на своем выходе тактовые импульсы , с интервалом времени, равным в данномслучае 2 тактам работы ге 5310816 тактовых импульнераторасов.По тактовому импульсуз в регистр1 2 адреса записывается адрес 2-й микрокоманды, которая является микрокомандой ветвления при прежней частоте работы устройства (алгоритм, соответствующий тактому фрагменту команды, представлен на фиг, 3 ), Реализация такой микрокоманды осуще О ствляется подобно реализации предыдущей микрокоманды ветвления с безусловным переходом на другую рабочую частоту. Отличие лищь в том, что в поле 1 метки М 1 ПЗУ 1 если часто ту работы нужно оставить прежней,записывается "1", которая поступает на инверсный вход третьего элемента И 13 и тем самым блокирует прохождение через него и затем второй элемент 20 ИЛИ 10 на управляющий вход регистра 4 частотных кодов сигнала с выхода мультиплексора 5. Таким образом, записи нового частотного кода из поля 1 логических условий ПЗУ 1 не про исходит и частота работы устройства остается прежней. В рассматриваемом примере сигнал с выхода мультиплексора 5 в 3-м такте работы устройства единичный, следовательно, по импульсу 304ьв регистр 2 адреса записывается адрес пятой ячейки ПЗУ 1, который в нашем случае соответствует линейная микрокоманда с безусловным переходом на другую частоту работы устройства(общий вид соответствующего фрагмента алгоритма на фиг, 3 ). Отличие в реализации такой микрокоманды от обычной линейной микрокоманды (без изменения частоты работы устройства) 40в следующем. В поле 1 логическихусловий ПЗУ записывается нужный частотный код, который поступает на информационный вход регистра 4 частотных кодов, В поле 1 ПЗУ 1 записана"1", которая, поступая через второйэлемент ИЛИ 10 на управляющий входрегистра 4 частотных кодов, разрешает в него запись нового кода и обязательную смену, таким образом, частоты работы устройства, Заметим,чточастотный код с выхода поля 1 логи -ческих условий ПЗУ 1 поступает такжена управляющий вход мультиплексора 5и этому частотному коду соответствует 5 определенное логическое условие на вход 19 устройства. Поэтому на выходе мультиплексора 5 появляется значение этого условия, которое может быть единичным. Такой единичный сигнал показан на временной диаграмме (фиг. 4) пунктиром. Из-за неопределенности сигнала с выхоца мультиплексора 5 становится неопределенным значение сигнала младшего разряда адреса на выходе первого элемента ИЛИ 9. Для его определенности в поле 1 младшего разряда адреса ПЗУ 1 рассматриваемого типа микрокоманды должна быть записана "1", т.е. переход оттакой линейной микрокоманды может осуществляться только в нечетные ячейки ПЗУ 1 (младший разряд адреса у них единичный). Ввиду всегда ограниченного количества линейных микрокоманд с переходом (как условным, так и безусловным) на другую частотуработы указанное условие легко выполнимо, По тактовому импульсу ь в регистр 2 адреса записывается адрестретьей ячейки ПЗУ 1, в которой записана микрокоманда без изменения частоты работы устройства, являющаяся последней в команде. В поле 1 метки М и 1 младшего разряда адреса ПЗУ 1 записаны "1" (одновременная записьв эти поля единичных сигналов возможна только в последних микрокомандахкоманд). Второй элемент И 12 в результате конъюнкции этих сигналов формирует сигнал конца команды, поступающий на вход конца команды информационного входа регистра 3 микрооперанции и второи вход четвертого элементаИ 14, Так как поле 16 адреса ПЗУ 1 впоследней микрокоманде команды свободно, то с выхода 21 старшего разряда адреса ПЗУ 1 на третий вход четвертого элемента И 14 поступает нулевой сигнал. Вследствие этого сигнал конца работы устройства на выходе четвертого элемента И 4 не формируется. По заднему фронту тактовогоимпульсав регистр 3 микроопераций ,в, 1заносится код последней микрооперации команды и единичный сигнал концакоманды. Далее с выхода 18 конца команды регистра 3 микроопераций единичный сигнал поступает на управляющий вход коммутатора 7, который при этом пропускает на свой выход с входа 20 устройства код следующей команды. При необходимости перехода к выполнению новой команды с изменением частоты работы устройства поступаютследующим образом. В поле 1 логических условий ПЗУ 1 записывается нужный частотный код, а в поле 1 мет3 О 87 8микрокоманды осуществляется подобнореализации простой микрокоманды ветвления (т.е. без перехода на другуючастоту работы), Отличие в следующемВ ее поле 1 метки М 1 ПЗУ 1 "1" незаписывается. Благодаря этому с выр хода поляПЗУ на инверсный входтретьего элемента И 13 поступает нулевой сигналЕсли значение проверя 1 О емого логического условия единичное, то с выхода мультиплексора 5й- на прямой вход третьего элемента И13 поступит единичный сигнал, следоватедьно, с выхода третьего элементав 5 И 13 через второй элемент ИЛИ 10 на) управляющий вход регистра 4 адресапоступит сигнал, разрешающий записьнового частотного кода. В данном примере значение проверяемого логичес 20 кого условия на 7-м такте работы устройства нулевое. Поэтому записи врегистр 4 частотных кодов не происходит и частота подачи тактовых импульсов в устройство не изменяется.э25 По тактовому импульсу , в регистр2 адреса заносится адрес 15-й ячейкиПЗУ 1, которой соответствует последняя микрокоманда последней команды.В полях 1 г, 1 ПЗУ 1 такой микроко 30 манды записываются единичные сигналы.Кроме того, "1" записывается в старший разряд адреса поля 16 ПЗУ 1, которому соответствует выход 21 этогополя ПЗУ . Второй элемент И 2 врезультате конъюнкции единичных сигналов с выходов полей 1 г, и 1 ПЗУ 1формирует сигнал конца команды, поступающий на второй вход четвертогоэлемента И 14, На его третий вход по,40 ступает единичный сигнал с выхода 21старшего разряда адреса поля 16 ПЗУ1. По заднему фронту тактового импульсас выхода первого элементагИ 11 в регистр 3 микроопераций из45 поля 1 микроопераций ПЗУ 1 заноситк ся код последней микрооперации последней команды. Зтот же тактовый импульспоступает на первый вход четвертогоэлемента И 14. При этом на его выходе формируется сигнап конца работы,который поступает затем на вход установки в "О" триггера 15 пуска, обнуляет его и останавливает работу гер нератора 16 тактовых образов, а значит и работу всего устройства,Формула ки М 2 ПЗУ 1 записывается "1", кото рая, поступая через второй элемент ИЛИ 12 на управляющий вход регистра 4 частотных кодов, разрешает тем самым запись в него нового частотного кода.По тактовому импульсу ь в регист 2 адреса с выхода коммутатора 7 запи сывается адрес первой микрокоманды новой команды, В данном примере это последняя команда, первой микрокоманде которой соответствует 12-я яче ка ПЗУ 1. Это линейная микрокоманда и условный переход (т.езависящий от значения одного из условий на вхо де 19 логических условий устройства на другую частоту работы устройства (общий вид соответствующего фрагмента показан на фиг. 36).Реализация такой микрокоманды осуществляется подобно реализации линейной микрокоманды с безусловным переходом на дру гую частоту работы устройства. Отличие состоит в том, что поле 1 э метки М 2 ПЗУ 1 для реализации данной иикрокоманды должно быть свободно. Тогда по коду логических условий (одновременно являющемуся новым частотнь".кодом) мультиплексор 5 пропускает на свой выход значение проверяемого частотного (логического) условия с вхо да 19 логических условий устройства В примере значение этого условия единичное и сигнал об этом с выхода мультиплексора 5 поступает на прямои вход третьего элемента И 13, на инверсный вход которого поступает нулевой сигнал с выхода поля 1 г метки М 1 ПЗУ 1. На выходе третьего элемента И 13 формируется единичный сигнал который поступает через второй элемент ИЛИ 10 на управляющий вход регистра 4 частотных кодов, разрешая тем самым запись в него. нового частотного кода. Переход от данной ячейки ПЗУ 1, по тем же причинам, ка и при реализации линейной микрокоман ды с бузусловным переходом на другую частоту работы устройства, может осу ществляться только в нечетную ячейку ПЗУ 1, т,е. в поле 1 м адшего разря да адреса ПЗУ 1 таких микрокоманд должна быть записана "1".По тактовому импульсу 7 в регист 2 адреса записывается адрес 3-й ячей 55 ки ПЗУ 1, которой соответствует микрокоманда ветвления с условным переходом на другую частоту работы устройства фиг. Зг) . Реализация такой из обре тенияМикропрограммное устройство управления, содержащее блок памяти микропрограмм, регистр адреса, регистр микроопераций, мультиплексор, коммутатор, триггер пуска, генератор тактовых импульсов, первый элемент ИЛИ, триггер, причем вход пуска устройства 5 соединен с входом установки в "1" триггера пуска, выход которого соединен с входом генератора тактовых импульсов, выход признака конца команды регистра микроопераций и вход ко О да команды устройства соединены соответственно с управляющим и первым информационным входами коммутатора, выход которого соединен с информационным входом регистра адреса, выход 15 которого соединен с адресным входом блока памяти микропрограмм, выход поля микроопераций блока памяти микропрограмм соединен с информационным входом регистра микроопераций, выход 2 О .которого соединен с выходом микро- операций устройства, выход поля логических условий блока памяти микропрограмм соединен с управляющим входом мультиплексора, выход поля 25 младшего разряда адреса блока памяти микропрограмм соединен с первым входом первого элемента ИЛИ, вход логических условий устройства соединен с информационным входом мультиплек- ЗО сора, выход которого соединен с вторым входом первого элемента ИЛИ,группа (1.-1) выходов (х=2,3) немодифицируемых разрядов адреса блока памяти микропрограмм соединена с второй группой (х) информационных входов коммутатора, -й информационный вход второй группы которого соединен с выходом первого элемента ИЛИ, о т л и,ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены таймер, регистр частотных кодов, второй эле-мент ИЛИ, с первого по четвертыйэлементы И, причем первый выход ге нератора тактовых импульсов соединен с тактовым входом таймера и входом синхронизации триггера, выход которого соединен с первым входом первого элемента. И, второй выход гене-"ратора тактовых импульсов соединенс вторым входом первого элемента И,выходы признака конца команды и разрешения условного перехода на новуючастоту блока памяти микропрограммсоединены соответственно с первымвходом второго элемента И и с инверсным входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход поля младшего разряда адреса блока памяти микропрограмм соединен с вторымвходом второго элемента И, выходпервого элемента И соединен с входомустановки в "О" таймера, с первымвходом четвертого элемента И и входомсинхронизации регистра микрооперацийи входом синхронизации регистра частотных кодов, выход второго элемента И соединен с информационным входомрегистра микроопераций и с вторымвходом четвертого элемента И, выходмультиплексора соединен с прямым входом третьего элемента И, выход признака безусловного перехода на новуючастоту блока памяти микропрограммсоединен с вторым входом второго элемента ИЛИ, выход которого соединен свходом разрешения записи регистра.частотных кодов, выход поля логическихусловий блока памяти микрокоманд соединен с информационным входом регистра частотных кодов, выход которогосоединен с входом уставки таймера, выход которого соединен с информацион".ным входом триггера и входом синхронизации регистра адреса, первый выход группы выходов немодифицируемыхразрядов адреса блока памяти микропрограмм соединен с третьимвходом четвертого элемента И,выход которого соединен с входом установки в " О " триггерапуска.12 1310817 Тип реализуемой команды Поля блока 1 ЯчейкиПЗУ,М г 1 0 1 0 0 0 0 0 0 0 0 0 0 0 О 0 0 1 0 0 0 1 0 02 1 0 0 1 0 1 0 1 О 3 1 0 0 0 0 0 0 0 0 0 1 1 0 1 1 0 0 1 5. 0 1 0 0 1 1 0 0 1 с 12 0 0 0 0 1 0 1 13 0 0 1 О 1 01 1 14 0 0 0 0 0 0 1 Г, 15 1 О 0 0 О 0 1 1 Линейная команда (беэ изменения частоты работы) 0 Команда ветвления и безусловный переход на другую частоту 0 Команда ветвления (без изменения частоты работы) 1 Последняя командамикропрограммы (без изменения частоты работы) 1 Линейная команда и безусловный переход на другую частоту 1 Линейная командаи безусловный переход на другуючастоту Линейная командаи условный переход на другуючастоту 0 Команда ветвления и условный переход на другую ча-, стоту 1 Линейная, команда (без изменения частоты работы) 1 Последняя командапоследней микро- программа

СмотретьЗаявка

4013865, 21.01.1986

ПРЕДПРИЯТИЕ ПЯ Г-4651

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, МАРКОВ ПЕТР ЕВГЕНЬЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.05.1987

Код ссылки

<a href="https://patents.su/10-1310817-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Стриппер для выталкивания болванок из изложниц