Устройство для распределения заданий процессорам

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

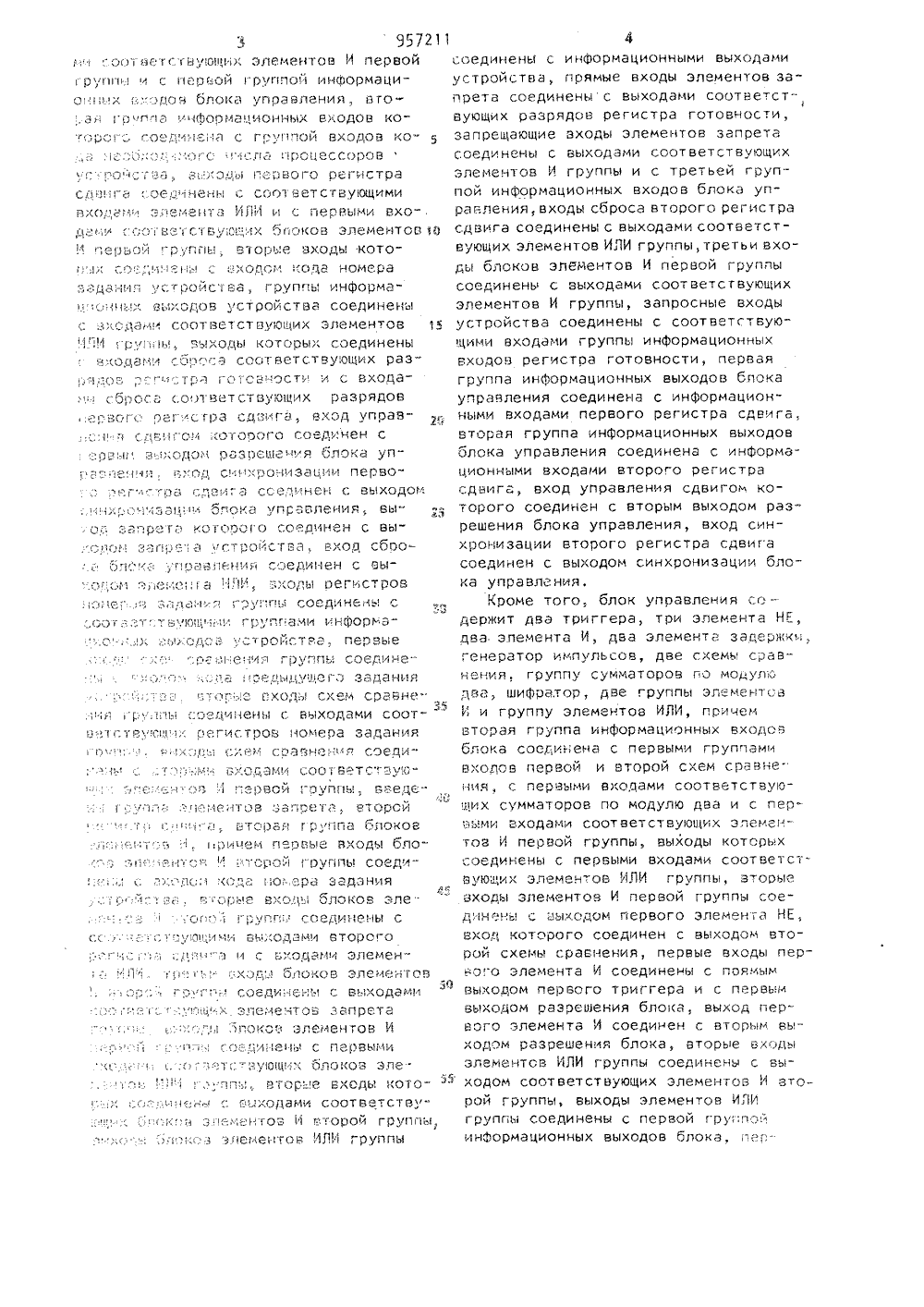

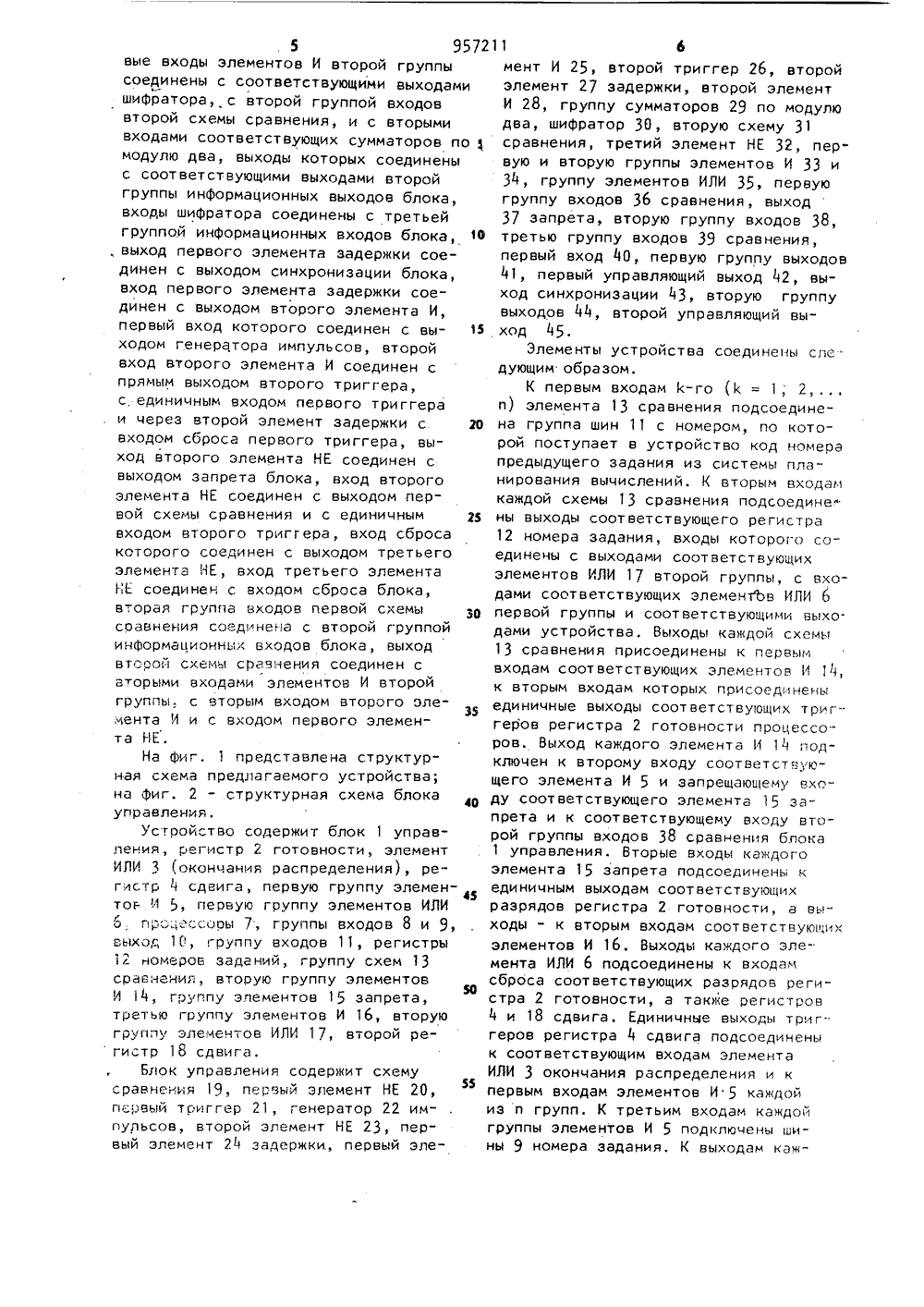

Союз СоветскинСоциапистическинРеспублик ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 1 9572 Иао делам наебретеннй н отерытнй(54) УСТРОЙСТ 80 ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙПРОЦЕССОРАИ роцесс ния на ых системахзки между проИзобретение относится к вычислительной технике и может найти приме нение в многоп орндля распределе груцессорами.Известно устройство для управлений 5 запуском программ, содержащее элементы ИЛИ. триггеры очередности, распредели-.епь импульсов 13.Недостатками устройства являютсяо невозможность программного изменения адреса запроса и низкое быстродействие, обусловленное последовательным опросом триггеров очереднос"15Наиболее близким техническим решением к предлагаемому изобретению явля:тся устройство для распределения заданий процессорам, содержащее блок управления, регистр готовности, що элемент ИЛИ, регистр сдвига, первую группу элементов И, первую группу элементов ИЛИ, процессоры, группы входов, выход отказа, регистры номе 2ра задания, группу элементов сравнения, вторую группу элементов И, вторую группу элементов ИЛИ, триггеруправления, элемент ИЛИ сброса триггера, элемент ИЛИ объединения циклического переноса из и-го и первогоразряда кода числа процессоров, шиныномера непосредственно предшествующего задания 2 1.Недостатком этого устройства явля"ется низкое быстродействие.Цель изобретения - повышение быстродействия устройства,Поставленная цель достигается тем,что в устройство для распределениязаданий процессорам, содержащее блокуправления, регистр готовности, элемент ИЛИ, первый регистрсдвига, группу элементов И, первую группу блоковэлементов И, группу регистров номеровзадания, группу элементов ИЛИ, группублоков элементов ИЛИ, группу схемсравнения, причем выходы регистраготовности соединены с первыми входа Ог8гВушщХ ЭЛРмеНТОВ И ПЕр вой ру 10: и с первойруппсй информаци О 1; Х 1 ХОДОВ ОЛОКЗ упраВЛЕНИя, В Гс . ар0.1 а Информационных входо е когоОГ, Оде,дине 1 гп С Г;." Г Ой ВХОДОВ КОа.:,;оды первого регистра С г:Г;", гг 1 НРН 1-СОСТ ВВТСТВУЮЩИМИ в хо.1,:; э пем 811 т а И Л 11 и с и Р р еыми Вхс ,18 ки; сствесВу 1 ее их бгоков элементов ОгЕгЕой руПГ 1 Ы, В 10;Ь 18 ВХОДЫ КОТО;. ;: 1: 81 ь ,: ХОДОК Кода НОМЕра З;ДЗН 11 П Уст РОЙ СТ ВаГРУПгЬ ИНФОРМа .1;Он 1 х выходов устройства соединены С ,:;ХОДми ССОтВЕтСтвуащИХ ЗЛЕМЕНтОВ З 1,И р,г ы Выходы которых сое,цинены, броса соответствующих разрядов , 8-.ВГ,Гс 08":.с Гра сцсГа, Вхсц упоавсдв.см ;оторсго соединен сре, 11 з; 1;, .гьон ра:,решен. я бг 1 ока уп -11 я. Вход сГхро:.-изации перво 8 Г - тса С. ВИ;а Ссе,гН 8 Н С ВЫХОДОКблока управления Вы- д , О ЭВ 1 РО Га КОТСООГО СОВДИН 8 Н С ВЬ 1Сгг.,1 З;1-,;.;, СтройС 1 ва ВХОД Сбос.-а8 Н И С 1Е ДЛ 1Е 1 1 г В Ы:., Х:СДСВ, СтРС Стеа. ПЕРВЬЕ1 Р 1 ИРУ 1 пыссеИ Н 8- ОГН 18 ВХОДЫ СХЕМ СРВВН 8351 я Гр, -ь :, .1 инены с выходами соот .1 сР "181,1 х 18 Гис тосе ИОЫРра яаданиР,С:. ;:,- г-ОРЬ 8 ВХОДЬ СЛО КО В ЭЛЕ"С, 1-РГГ" Г 081 ИНР 1 Ы СГС :-,.Рг ,И 1 И Вы ОдаМЛ ВтсрСГОз и с вхоцам элемен 1:. т;:к ,.хо,:. блоков эле 18 нтсвг;г " С 08 ДИ ВНЫ С ВЫХОДамиГгг;, " .,Х 11 Х ЗЛемеНТОБ ЗВПрЕТаспоко. элементов ИСОСЦ;ИЕНЫ С ПЕОВЬМИс:; "810 Вуюц 1 х Олскоз эле г8 г, ;. Г 1.,1 ХОДами СОСТ В 8 ТСТ ВУ Ь гТОРсй 1-РУППЫ) гс 3 31 ем 81.тсв ИПИ Группысоединены с информационными выходами устройства, прямые входы элементов запрета соединеныс выходами соответствующих разрядов регистра готовности, запрещающие Входы элементов запрета соединены с выходами соответствующих элементов И группь и с третьей группой информационных входов блока управления,входы сброса второго регистра сдвига соединены с выходами соответствующих элементов ИЛИ группы, третьи входы Олсков элементов И первой группы соединень с Выходами соответствующих элементов И группь 1, запросные входы устройства соединены с соответствующими Входами группь, информационных Входов регистра готовности, первая группа информационных Выходов бпока управления соединена с информационными входами первого регистра сделга, Вторая группа информационньх выходов блока управления соединена с информационными входами второго регистра сдвига, вход управления сдвигом которого соедиьен с вторым выходом разрешения блока управления, вход синхронизации Второго регистра сдвига соединен с Выходом синхронизации блока управления.Кроме того блок управления сов держит два триггера, три элемента Н., два э.пемента И, два элемента задержки генератор импульсов, две схемы сравнения группу сумматоров ГО модулю два, шифратор, две группы элементов И и группу элементов ИЛИ, причем вторая группа информационных входов блока сосдинена с первыми группами Входов первой и второй схем сравне. ния с первыми вхоцами соответствуюших сумматоров по модулю два и с Гервыми Входами соответствующих элементов И первой группы, выходы которых соединень с первыми входами соответствующих элементов ИЛИ группы, вторые Входы элементов И первой группы соедингь с выходом первого злемен 1-а НЕ Вход которого соединен с выходом второй схемы сравнения, первые входы пер.-Ого элемента И соединены с поямым выходом первого триггера и с первым вь 1 ходом разрешения блока, выход первого элемента И соединен с вторым Вь- ходом разрешения блока, вторые входы эгементсв ИЛИ группы соединены с Выходом соответствующих элементов И второй группы, вь 1 ходы элементов И 1 И групГь соединены с первой Гру:;пой информационных выходов блока, -ер9572вые входы элементов И второй группысоединены с соответствующими выходамишифратора с Второи Группои ВходОВвторой схемы сравнения, и с вторымивходами соответствующих сумматоров по 5модулю два, выходы которых соединеныс соответствующими выходами второйгруппы информационных выходов блока,входы шифратора соединены с третьейгруппой информационных входов блока, 10, выход первого элемента задержки соединен с выходом синхронизации блока,вход первого элемента задержки соединен с выходом второго элемента И,первый вход которого соединен с выходом генератора импульсов, второйвход второго элемента И соединен спрямым выходом второго триггера,с, единичным входом первого триггераи через второй элемент задержки с 20входом сброса первого триггера, выход второго элемента НЕ соединен свыходом запрета блока, вход второгоэлемента НЕ соединен с выходом первой схемы сравнения и с единичным двходом второго триггера, вход сбросакоторого соединен с выходом третьегоэлемента НЕ, вход третьего элементаНЕ соединен с входом сброса блока,вторая группа входов первой схемысоавнения соединена с второй группойинформационных входов блока, выходвторой схемы сравнения соединен свторыми входами элементов И второйгруппы,. с вторым входом второго элемента И и с входом первого элемента НЕ,На фиг. 1 представлена структурная схема предлагаемого устройства;на фиг. 2 - структурная схема блокауправления,Устройство содержит блок 1 управления, регистр 2 готовности, элементИЛИ 3 окончания распределения), регистр 4 сдвига, первую группу элементо М 5, первую группу элементов ИЛИ6 процессоры 7, группы входов 8 и 9,выход 10, группу входов 11, регистры12 номеров заданий, группу схем 13сравнения, вторую группу элементовИ 14, группу элементов 15 запрета,третью группу элементов И 16, вторуюгруппу элементов ИЛИ 17, второй регистр 18 сдвига,Блок управления содержит схемусравнения 19, первый элемент НЕ 20,55первый триггер 21, генератор 22 импульсов, второй элемент НЕ 23, первый элемент 24 задержки, первый эле 11 6мент И 25, второй триггер 26, второйэлемент 27 задержки, второй элементИ 28, группу сумматоров 29 по модулюдва, шифратор 30, вторую схему 31сравнения, третий элемент НЕ 32, первую и вторую группы элементов И 33 и34, группу элементов ИЛИ 35, первуюгруппу входов 36 сравнения, выход37 запрета, вторую группу входов 38,третью группу входов 39 сравнения,первый вход 40, первую группу выходов41, первый управляющий выход 42, выход синхронизации 43, вторую группувыходов 44, второй управляющий выход 45.Элементы устройства соединены сле "дующим образом,К первым входам -го ( = 1; 2,и) элемента 13 сравнения подсоединена группа шин 11 с номером, по которой поступает в устройство код номеоапредыдущего задания из системы планирования вычислений. К вторым Входамкаждой схемы 13 сравнения подсоедине"ны выходы соответствующего регистра12 номера задания, входы которого соединены с выходами соответствующихэлементов ИЛИ 17 второй группы, с входами соответствующих элементЬВ ИЛИ 6первой группы и соответствующими Выхо.дами устройства, Выходы каждой схемы13 сравнения присоединены к первымвходам соответствующих элементов Ик вторым входам которых присоединеныединичные выходы соответствующих триггеров регистра 2 готовности процессоров. Выход каждого элемента И 14 подключен к второму входу соответствующего элемента И 5 и запрещающему входу соответствующего элемента 15 запрета и к соответствующему входу второй группы входов 38 сравнения бпока1 управления, Вторые входы каждогоэлемента 15 запрета подсоединены кединичным выходам соответствующихразрядов регистра 2 готовности, а выходы - к вторым входам соответствующихэлементов И 16. Выходы каждого элемента ИЛИ 6 подсоединены к входамсброса соответствующих разрядов регистра 2 готовности, а также регистров4 и 18 сдвига. Единичнце выходы триггеров регистра 4 сдвига подсоединенык соответствующим входам элементаИЛИ 3 окончания распределения и кпервым входам элементов И 5 каждойиз и групп. К третьим входам каждойгруппы элементов И 5 подключены шины 9 номера задания. к выходам каж 957 дой руппы элементов И 5 подключены первые входы соответствуощих элементов ИЛИ 17. Единичные выходы триггеоов регистра 18 сдвига подсоединены К СООтВЕТСтВУЮЩИМ ВХОдаМ ЭЛЕМЕНта ИЛИ 3 и к первым входам элементов И 16 каждой из и групп". К третьим входам каждой группы элементов И 18 нодклочены лны 9 номера задания, К Выходам каждой группы элементов 16 Й 16 подключень Вторые ВхОДы соот ветствующих элементов ИЛИ 17, выходы которых подсоединены к соответствующим инФормационным входам процессоров 7 Выходы процессоров 7 15 поцсоецинены к установочным входам :риггеров регистра 2 готовности. Единичные выходы триггеров регистра 2 готовностл подсоединены к соответстВующим входам сравнения третьей груп пы Входов 39 блока 1 управления. 1 ины 8 кода числа процессоров подсоединень к первой группе входов 36 Олока 1 управления. К первому входу О бгОка 1 управления подключен вы ход элемента ИЛИ 3 окончания распредепения, ервый управляющий Вы ход 42 блока 1 управления подсоединен к входу регистра 4 сдвига, управляющему приемом информации в регистр зосдвига, Второй управляющий выход 45 олока уг равления 1 подсоединен к В;Оцу 1 управ.яюему приемом инфор :ВцлБ реГ;лстр 18 сдвиГд, ВыхОД син хронизации 43 блока 1 управления под 35 соединен к входу, управляющему сдвлг ом в регистресдвига и к входу, управлявшему сдвигом в регистре 18 СДВИГВ, Нрвая Группа ВыхОДОВ 41 блока управления подсоединена к ус- таНОВОЧНЫМ ВХОДаМ РЕГИСтРаСДВИГа, а ВтораяруПа выходоВ 44 к уста лОвочдьм входам 1 е гистра 20 цикличес- кого сдвига.ЗтВменты блока управления соедине 45 ны следющим Ооразом.первая группа входов 36 сравнения блока поцсоецинена к первой группе входов схемы 19 сравнения, первым Входал соответствующих сумматоров 29модулю два, первой Группе Входов5 О сх .ы 31 сравнения и к первым входам Оотв.стоуощлх элементов И 34, Выхо"1:,ГО из и элелетов И 3 под со: в ;,:.Инены к первым входам соответствующих элементов ИЛИ 37, Вторые Входы55 каждого гпемента И 34 подсоединены к Выход; элемента НЕ 32, к входу ко,орого подсоединен выход схемы 3 8сравнения. Выход схемы 31 сравнения подсоединен к первым входам каждого из и элементов И 33 и к первому входу элемента И 28. Второй вход элемента И 28 подсоединен к прямому Выходу триггера 26 и к первому управляющему выходу 42 блока, Выход элемента И 28 подсоединен к второму управляющему выходу 45 блока. Вторые входы каждого из и элементов ИЛИ 35 подсоединены к выходам соответствующих элементов И 33. Выходы элементов ИЛИ 35 подсоединены к первой группе информационных выходов 41 блока. Вторые входы каждого из п элементов И 33 подсоединены к соответствующим выходам шифрат тора 30, к вторым входам соответствующих сумматоров 29 по модулю два и к второй группе входов схемы 31 сравнения. Выходы каждого из и сумматоров 29 по модулю два подсоединены к соответствующим выходам второй группы информационных выходов 44 блока, Входы шифратора 30, подсоединены к второй группе входов 38 блока, Выход элемента 27 задержки подсоединен к выходу 43 синхронизации блока, а вход - к выходу элемента И 25. Первый вход элемента И 25 подсоединен к выходу генератора 22 импульсов, а второй вход - к единичному выходу триггера 21, входу элемента 24 задержки и установочному входу триггера 26. Вход сброса триггера 26 подсоединен к выходу элемента 24 задержки, Выход элемента НЕ 23 подсоединен к вьходу 37 запрета блока, Вход элемента НЕ 23 подсоединен к выходу схемы 19 сравнения и к установочному входу триггера 21. К входу сброса триггера 21 подсоединен выход элемента НЕ 20.Вход элемента НЕ 20 подсоединен к первому входу 40 блока. Вторая группа входов схемы 19 сравнения подсоединена к третьей группе входов 39 сравнения блока.Предлагаемое устройство работает с.чедующим образом.Распределение заданий по процессорам с учетом существующих информационно-управляющих связей между заданиями осуществляется за один цикл работы устройства. При этом в первую очередь осуществляется одновременное выделение процессоров, выполнивших задание, непосредственно предшествующего данному (процессоры первого типа), и остальных потребных свободньх процессоров (процессоры второго типа).95721110 вует сигнал на выходе элемента ИЛИто триггер 21 остается в единичном соЗатем параллельно выполняется распределение заданий на имеющиеся в вычислительной системе процессоры первого типа и на необходимое количество процессоров второго типа, 5По шинам 8 в блок 1 управления поступает код числа необходимых для выполнения задания процессоров, вырабатываемых в системе планирования вычислений. Схемы 19 сравнения срав о нивает потребное число процессоров с количеством свободных процессоров, данные о готовности которых хранятся в регистре 2 готовности. Если число свободных процессов меньше количества потребных,то схема 19 сравнения сигнал на выход не выдает. При этом на выходе элемента НЕ 26 появится сигнал отказа, свидетельствующий о невозможности выполнения задания. Если чис ло свободных процессоров не меньше чем требуется для выполнения задания, на выходе схемы 19 сравнения появится сигнал, устанавливающий триггер 21 пуска в единичное состояние. Сиг- д нал с выхода триггера 21 устанавливает в единичное состояние триггер 26 управления, При этом на первом управляющем выходе 42 блока 1 управления появляется сигнал записи кода с выходов элементов ИЛИ 35 в регистр 4 сдвига.Поедположим,. что потребное количество процесоров отражается в коде на шинах 8 количеством единиц в соот 35 ветствующих оазрядах, Соответственно по входу 9 на группы элементов И 5 и 16 поступает код номера задания, которого должны отрабатывать выбранные процессоры, а по шинам 11 на элементы сравнения 3 подается код номера задания, непосоедственно предшествующего данному, На регистрах 12 хранятся коды номеров заданий, назначенных на соответствующие процессоры при45 предшествующих циклах работы устройства. При оступлении кода номера задами:-, кепосредственно предшествующего даккому, по шинам 11 на выходах некоторых .лементов И 14 появляются сигналы ооразующие код числа про 50 це. соров, выполнивших непосредственна предшествующее задание. Номер элемента И 14 определяется совпадением единичных разрядов в регистре 2 готовности и сигналов, вырабатываемых схе 5 мами 3 сравнения при совпадении ко", да, хранящегося на регистре 12 и кода, .поступающего по шикам 11. Одновременно с этим на выходах некоторыхэлементов 15 запрета появляются сигналы, образующие код количества свободных процессоров. Номер элемента 15 запрета определяется совпадением единичных разрядов в регистре 2 готовности и нулевых сигналов, вырабаты. ваемых элементами И 14. Код количества процессоров, выполнивших непосредственно предшествующее задание, с выходов элементов И 14 поступает на входы шифратора 30, а с его выходов подается на входы соответствующих сумматоров 29 по модулю два и схемы 31 сравнения,Если для выполнения задания потребуется количество процессоров, не превышающее количество процессов,выполнивших предыдущее задание, схема31 сравнения сигнал не вырабатывает,При этом на выходе элемента НЕ 32 появляется сигнал, разрешающий выдачу. кода числа необходимых процессоровна шинах 8 через элементы И 34 и ИЛИ35 на инФормационные входы регистра сдвига, С появлением сигнала на выходе элемента 24 задержки происходит сброс триггера 26 управления и снятие 3сигнала записи кода из шин 8 в регистр 4 сдвига,После записи кода в регистр 4 сдвига на выходах определенных групп элементов И 5 появляются сигналы коданомера задания. Номер элемента группыИ 5 определяется совпадением одкоименных единичных сигналов с разрядом регистра 4 сдвига и выходом элементов И 14. С выхода группы элементов И 5 код номера задания выдается в соответствующий процессор 7 и регистр 1номера задания, а через элементИЛИ 6 сбрасывает соответствующиеразряды регистров 2, 4 и 18. Если при этом в регистре 4 сдвига остались единичные разряды, о чем свидетельстстоянии. В этом случае импульсы сдвига, вырабатываемые генератором 22 импульсов,поступают через элемент И 25 и элемент задержки 27 на вход регистрасдвига. После определенного количества сдвигов кода в регистре 4 сдвигавсе разряды регистра будут обнулены,При этом сигнал с выхода элементаИЛИ 3 снимается, а на выходе элементаНЕ 20 появляется сигнал, сбрасываюший триггер 21 в нулевое состояние. Этоозначает, что задание распределеномежду теми процессорами, которые завершили выполнение непосредственнопредшествующего задания.Гсли необходимое число процессоровпревышае г количество процессоров,завершивших выполнение непосредствен-.но предшествующего задания, то, кромерегистра 4 сдвига, в устройстве используется дополнительный ,регистр18 сдвига для одновременного распре-оделения заданий на любые свободные процессоры. 8 этом слуцае сигнал с выходасхемы 31 сравнения разрешает выдацув регистр 4 сдвига кода количествапроцессоров, завершивших выполнение 15задания, непосредственно предшествующего данному, При налиции этогосигнала на выходе элемента И 28 появляется сигнал, поступающий в регистр18 сдвига и разрешающий прием кода с 2 цвыходов группы сумматоров 29 по модулю два. Количество единиц в этом коде равно разности между количествомнеобходимых и свободных процессоров,выполнивших предыдущее задание. Тепесь при сдвиге кода в регистресдвл га и в регистре 18 сдвига код номера задания появится на выходе соответствующих групп элементов И 5 и 16,При совпадении одноименных единичныхзразрядов в регистре 4 сдвига и сигналов на выходах элементов И 14, атакже регистра 18 сдвига и сигналовна выходах элементов И 16 код номеразадания выдается в соответствующиепроцессоры 7 и регистры 12 а черезэлементы ИЛИ 6 обнуляет соответствующие разряды реги стров 2, 4 и 18, Приобнулении всех разрядов регистрасдвига и регистра 18 сдвига сигналвыхода элемента ИЛИ 3 снимается.Этосзнацает, что задание распределенореди всех процессоров, выполнившихнепосредственно предшествующее задание, а также среди необходимого коли 45чества свободных процессоров.7 аким образом, г,редлагаемое устройство обеспечивает одновременное выделение для выполнения задания процессоров, выполнивших непосредственно5 Опредшествующее задание, и необходимого числа свободных процессоров засчет чего и повышается бьстродействиеусгройства,Формула изобретенияустройство для распределения заданий процессорам, содержащее бпок управления, регистр готовности, элемент ИЛИ, первый регистр сдвига, групу элементов И, первую группу блоковэлементов И, группу регистров номеров задания, группу элементов ИЛИ,группу блоков элементов ИЛИ, группусхем сравнения, причем выходы регистра готовности соединены с первымивходами соответствующих элементов Ипервой группы и с первой группой информационных входов блока управлениявторая группа информационных входовкоторого соединена с группой входовкода необходимого числа процессоровустройства, выходы первого регистрасдвига соединены с соответствующимивходами элемента ИЛИ и с первыми входами соответствующих блоков элементоИ первой группы, вторые входы которых соединены с входом кода номеразадания устройства, группы информационных выходов устройства соединеныс входами соответствующих элементовИЛИ группы, выходы которых соединеныс входами сброса соответствующих разрядов регистра готовности и с входамсброса соответствующих разрядов первого регистра сдвига, вход управленисдвигом которого соединен с первымвыходом разрешения блока управления,вход синхронизации первого регистрасдвига соединен с выходом синхронизации блока управления, выход запрета которого соединен с выходом загрета устройства, вход сброса блока управления соединен с выходом элементаИЛИ, входы регистров номеров заданиягруппы соединены с соответствующимигруппами информационных выходов устройства, первые входы схем сравнениягруппы соединены с входом кода предыдущего задания устройства, вторыевходы схем сравнения группы соединены с выходами соответствующих регистров номера задания группы, выходысхем сравнения группы соединены с втрыми входами соответствующих элементов И первой группы, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия, в него введеныгруппа элементов запрета, второй регистр сдвига, вторая группа блоковэлементов И, причем первые входь блоков элементов И второй группы соединены с входам кода номера заданияустройства, вторые входы блоков элементов И второй группы соединены ссоответствующими выходами второгорегистра сдвига и с входами эл-:.не та9572 ИЛИ, третьи входы блоков элементовИ второй группы соединены с выходами соответствующих элементов запрета группы, выходы блоков элементов И первой группы соединены с первыми входами соответствующих блоков элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих блоков элементов И второйгруппы, выходы блоков элементов ИЛИгруппы соединены с информационнымивыходами устройства, прямые входы элементов запрета соединены в выходами соответствующих разрядов регистраготовности, запрещающие входы элементов запрета соединены с выходамисоответствующих элементов И группыи с третьей группой информационныхвходов блока управления, входы сброса второго регистра сдвига соединеныс выходами соответствующих элементов ИЛИ группы, третьи входы блоков элементов И первой группы соединены с выходами соответствующих элементов Игруппы, запросные входы устройства соединены с соответствующими входамигруппы информационных входов регистра готовности, первая группа информационных выходов блока управлениясоединена с информационными входами первого регистра сдвига, втора группа инфор,ационных выходов блока управления соединена с информационны;."ходами второго регистра сдвига,вход управления сдвигом которого соединен с вторым выходом разрешения блока управления, вход синхронизации второго реги тра сдвига соединен с выходом синхронизации блока управления,35 Устройство пс и. 1, о т л и ц а а щ е е с я тем, что блок управления содержит деа триггера, три элене:- а НЕ, два элемента И, два эле 45 мента задержки, генератор импульсов, дее схс:.ь: сравнения, группу сумматор . ., .,с мс -улю два, шифратор, двегру-ь элементов И и группу элементов ИЛИ, причем вторая группа инфор 50 мационных входов блока соединена с первыми группами вхсдое первой и вто- роГ схе., сравнения, с первыми входами :сответстзующих сумматоров по мс. улю два и с первыми входами соответг" с 4с " вующи х эл е и ем тс в , первой группы ,55 :".ыходы которых соединены с первыми ,.ходами соответствующих элементов 1114ИИ группы, вторые входы элементов И первой группы соединены с выходом первого элемента НЕ, вход которого соединен с выходом второй схемы сравнения, первые входы первого элемента И соединены с прямым выходом первого триггера и с первым выходом разрешения блока, выход первого элемента И соединен с вторым выходом разрешения блока, вторые входы элементов ИЛИ группы соединены с выходом. соответствующих элементов И второй группы, выходы элементов ИЛИ группы соединены с первой группой информационных выхо" дов блока, первые входы элементов И второй группы соединены с соответствующими выходами шифратора, с второй группой входов второй схемы сравнс ия и с вторыми входами соответствующих сумматоров по модулю два, выходы которых соединены с соответствующими выходами, второй группы информационных выходов блока, входы шифратора соединены с третьей группой информационных входов блока, выход первого элемента задержки соединен с выходом синхрони" зации блока, вход первого элемента задержки соединен с выходом второго элемента И, первый вход которого соединен с выходом генератора импульсов, второй вход второго элемента И соединен с прямым выходом второго триггера, с единичным входом первого триггера и через второй элемент задержки с входом сброса первого триг- гера, выход второго элемента НЕ соединен с выходом запрета блока, вход второго элемента НЕ соединен с выходом первой схемы сравнения и с. ед". - ничным входом второго триггера, вход сброса которого соединен с выходом третьего элемента НЕ, вход третьего элемента НЕ соединен с входом сброса блока, вторая группа входов первой схемы сравнения соединена с второй группой информационных входов блока, выход второй схемы сравнения соединен с вторыми входами элементов И второй группы, с вторым входом второго элемента И и с входом первого элемента КЕ.Источники информации.принятые во внимание при экспертизе1. Авторское свидетельство СССРй Й 68240, кл. 6 06 Г 9/00, 1972.2. Авторское свидетельство СССРпо заявке М 2919250, кл, С 06 Г 9/6,1980 (прототип).957211 оставитель М. Кудряшевехред С.Мигунова Корректор М, Кост Редактор И. Тыкей Заказ 6600/3 Тираж 731 ВНИИПИ Государствен по делам изобрет 13035., Москва, Ж, Подписноеого комитета СССРний и открытийРаушская наб д. 4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная,

СмотретьЗаявка

3263093, 25.03.1981

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ ОРДЕНОВ ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПВО ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

ГАНИТУЛИН АНАТОЛИЙ ХАТЫПОВИЧ, ШУТИЛОВ АЛЕКСАНДР ИУСТИНОВИЧ, ДИЯРОВ РАШИТ МИННЕХАЗИЕВИЧ

МПК / Метки

МПК: G06F 9/50

Метки: заданий, процессорам, распределения

Опубликовано: 07.09.1982

Код ссылки

<a href="https://patents.su/9-957211-ustrojjstvo-dlya-raspredeleniya-zadanijj-processoram.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для распределения заданий процессорам</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Устройство для контроля и диагностики гибридных блоков

Случайный патент: Установка для вибрационной очистки изделий