Цифровой демодулятор сигналов относительной фазовой манипуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

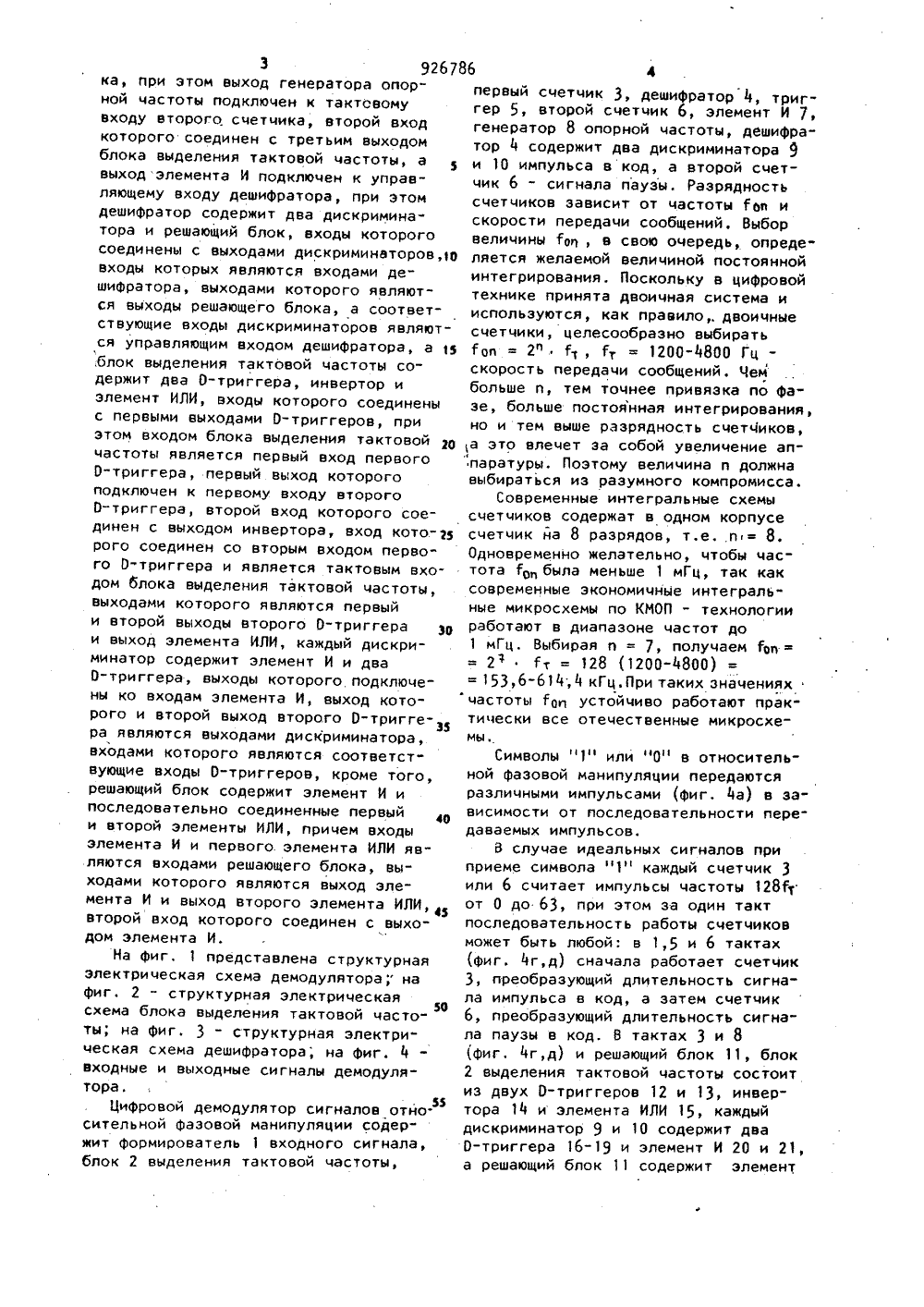

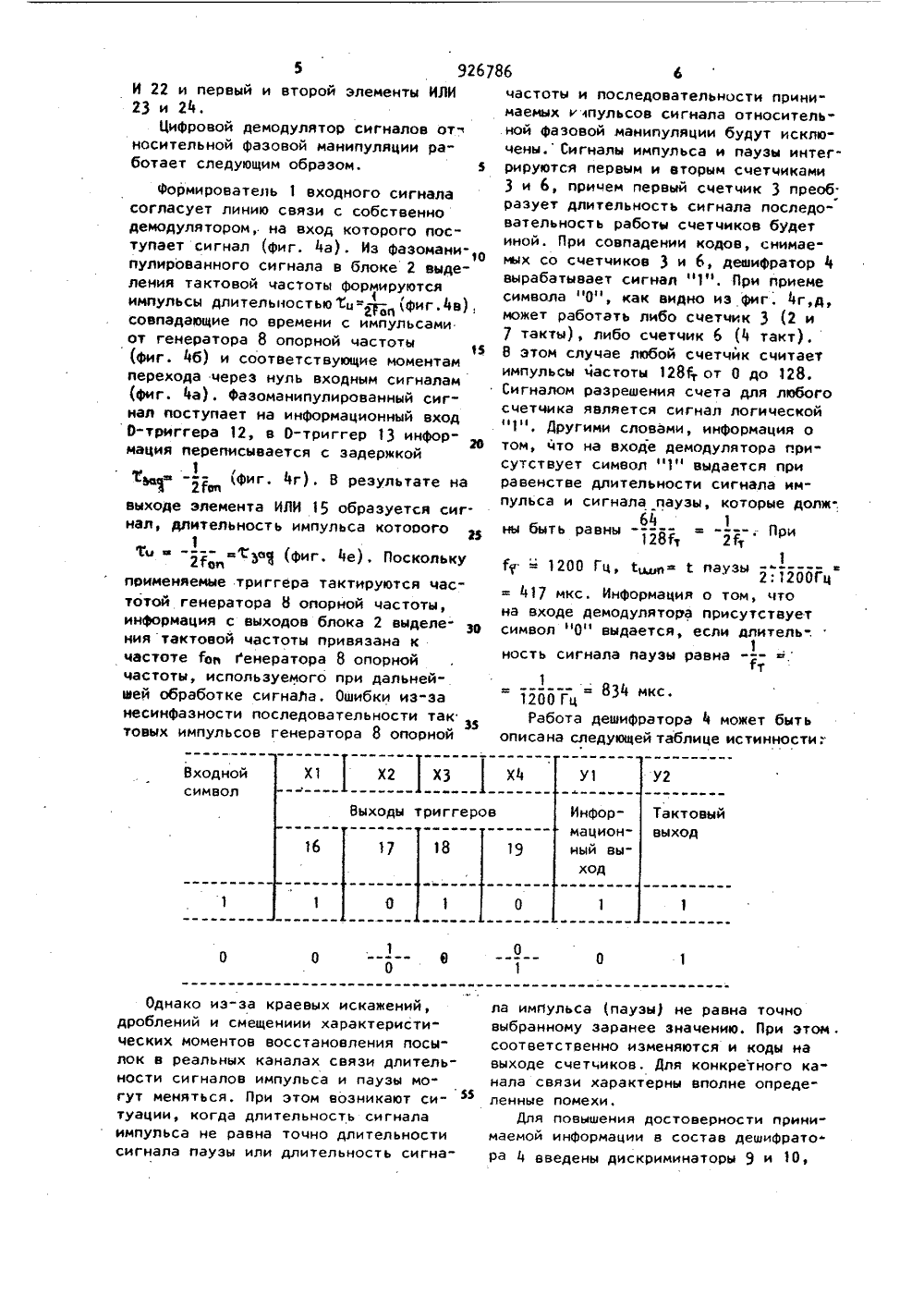

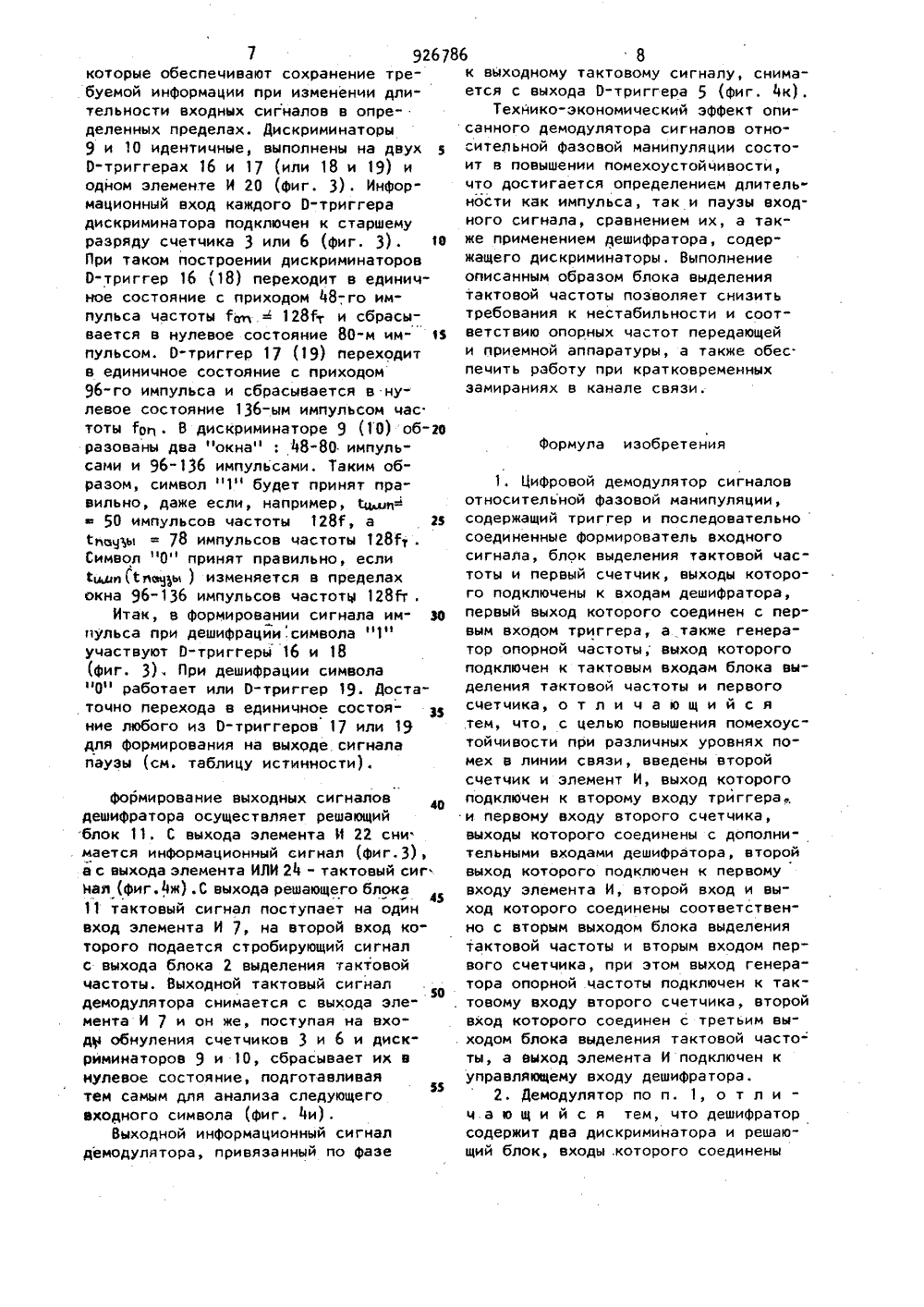

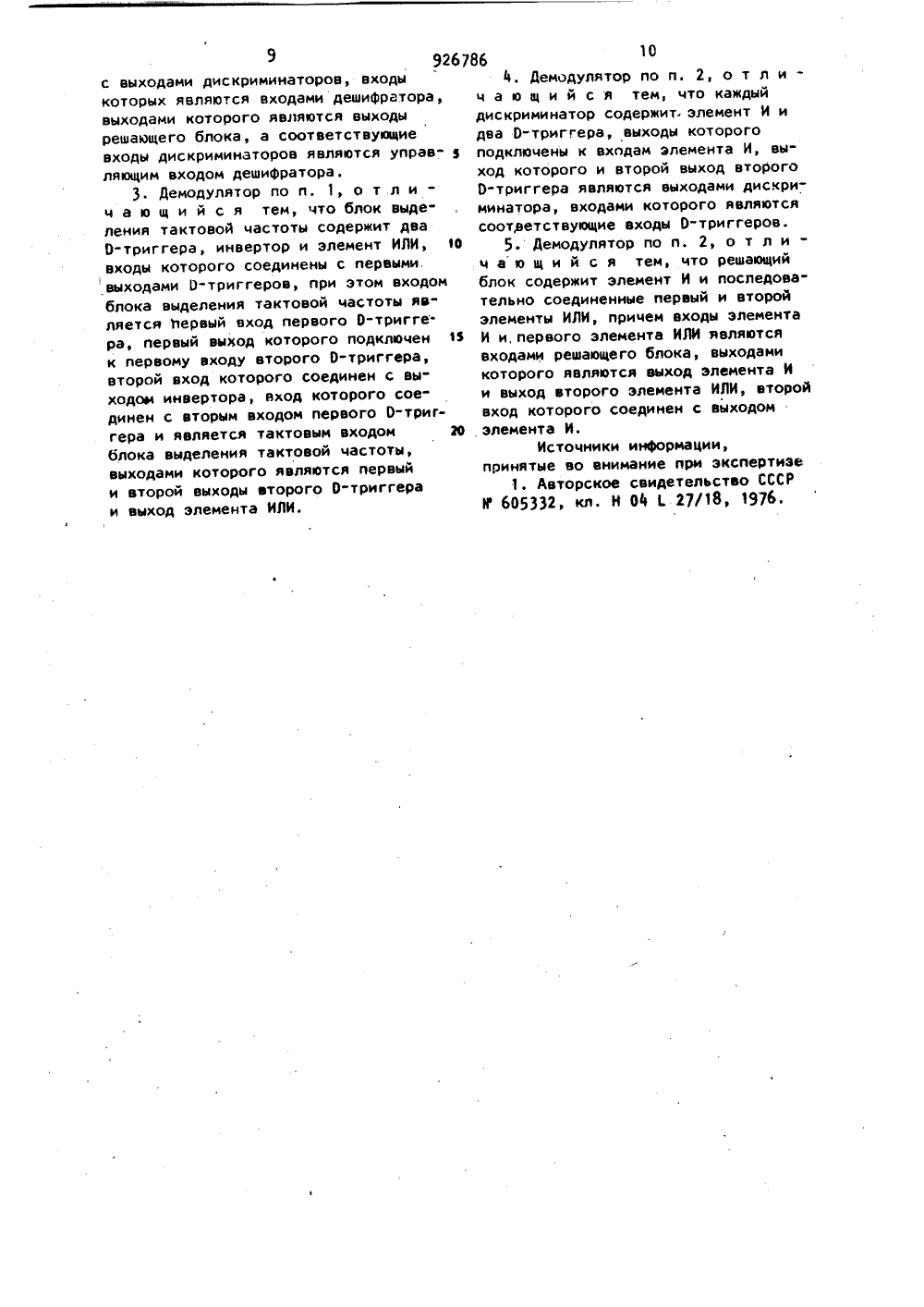

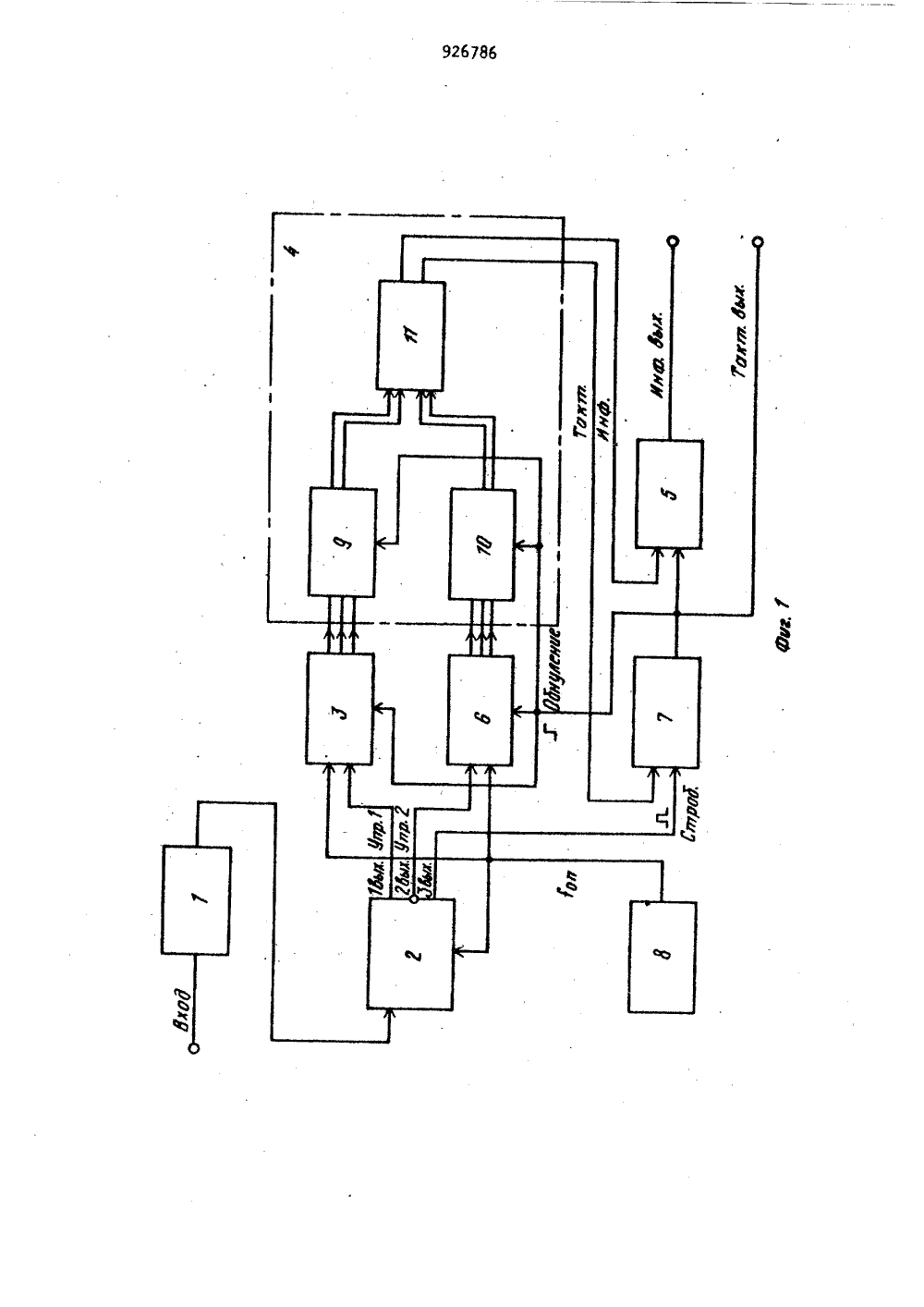

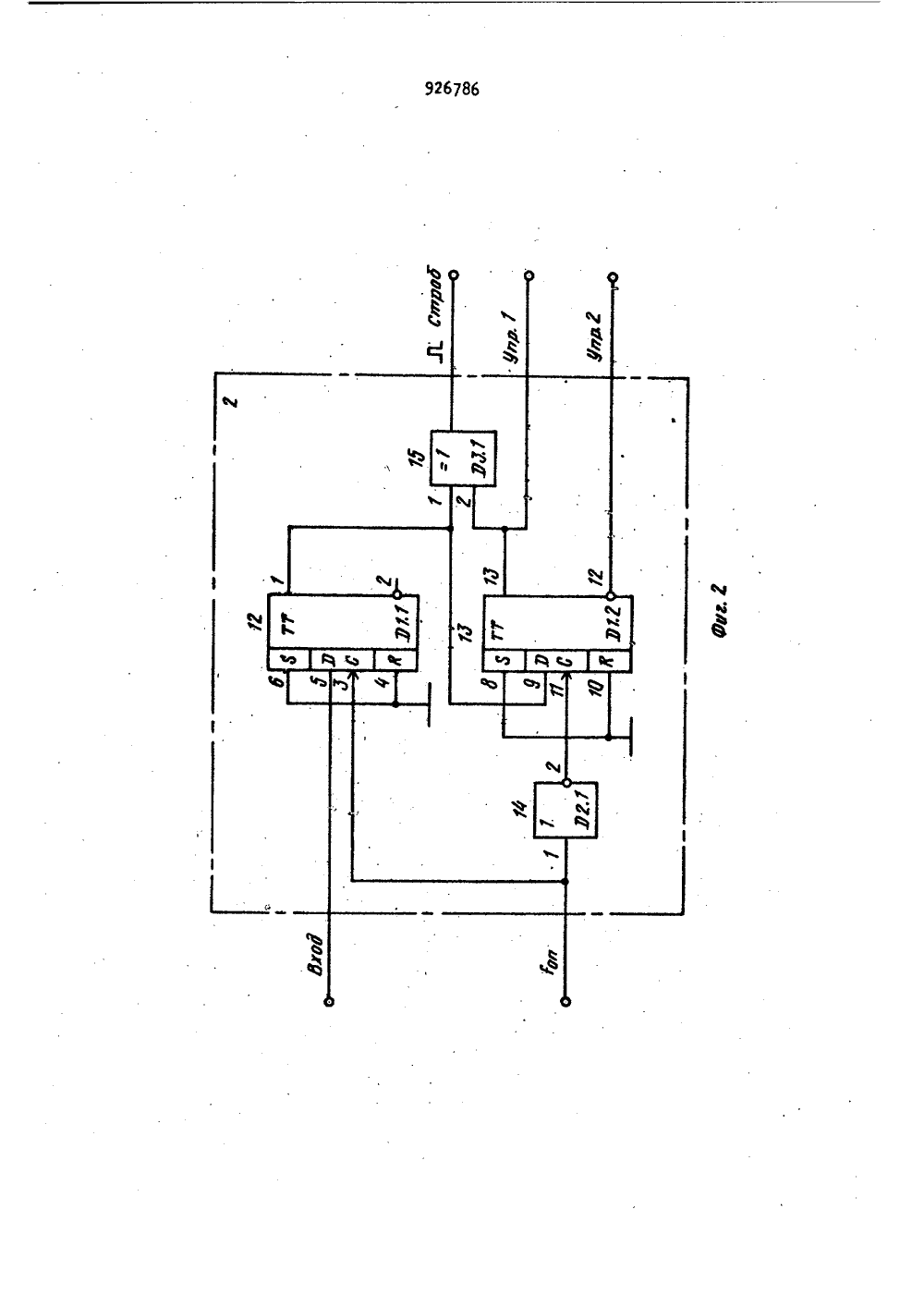

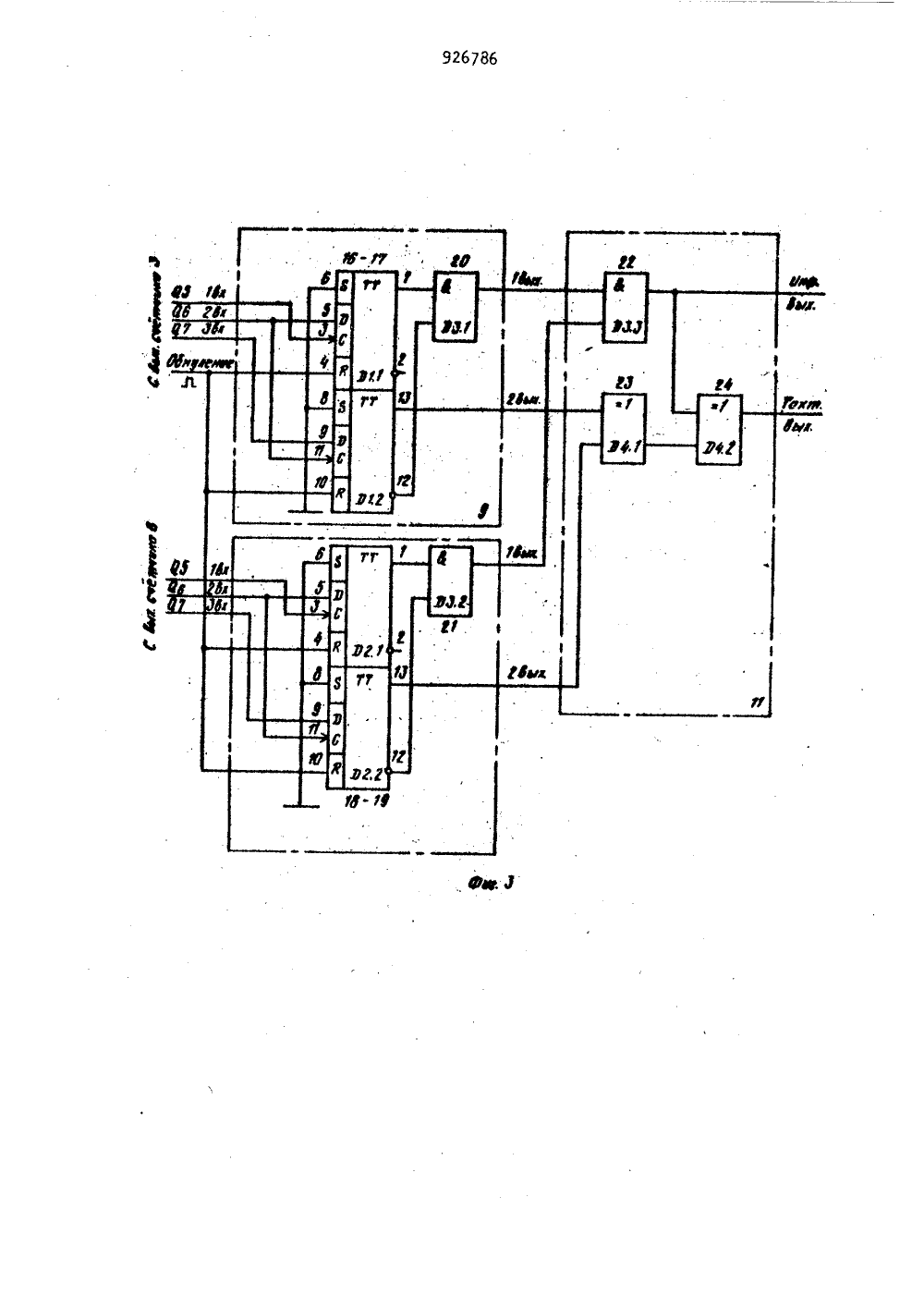

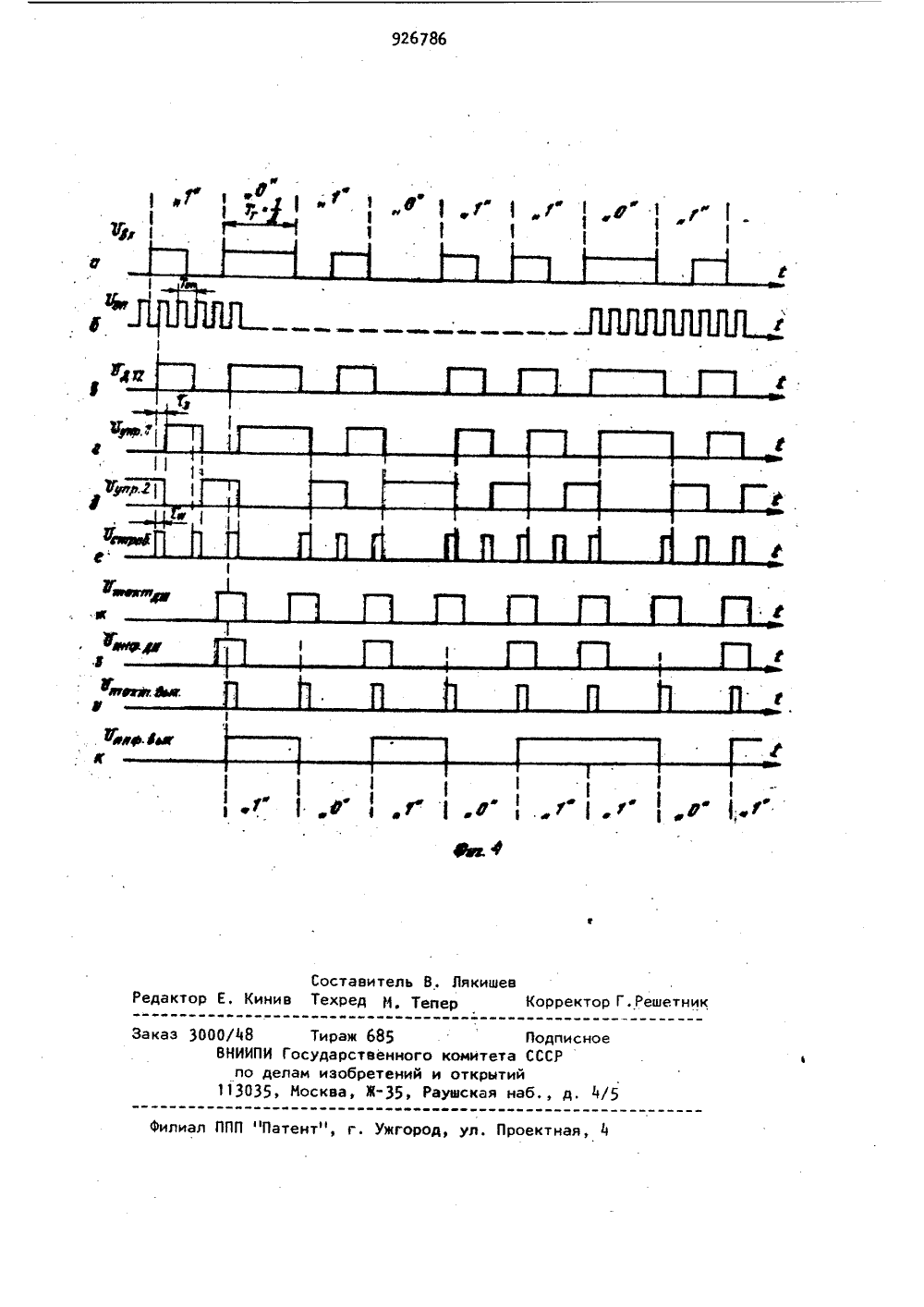

(51) М. Кл. Н 0427/22 1 ЬвударетюаЮ квввтвт СССР еф деан извбрвтевиЯ в вткрытвЯОпубликовано 07 . 05. 82 . Бюллетень М 17 Дата олубликовання описания 07.05.82(54) ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ Изобретение относится к технике связи и может использоваться.в системах обмена дискретными сообщениями для приема сигналов относительной фазовой манипуляции.Известен цифровой демодулятор сигналов относительной фаэовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены ко вхсдам дешифратора, первый выход которого соединен с первым входом триГгера, а также генератор опорной частоты, выход которого подключен к тактовым входам блока выделения тактовой частоты и первого счетчика (11.Однако такой демодулятор обладает низкой помехоустойчивостью при различных уровнях помех в линии связи.Цель изобретения - повйшение помехоустойчивости при различных уровнях помех в линии связи Цель достигается тем, что в цифровой демодулятор сигналов относительной Фазовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены к входам дешифратора, пер" вый выход которого соединен с первым входом триггера, а также генератор опорной частоты, выход которого подключен к тактовым входам блока выделения тактовой частоты и первого счетчика, введены второй счетчик и элемент И, выход которого подключен к второму входу триггера и.первому входу второго счетчика, выходы которого соединены с дополнительными входами дешифратора, второй выход которого подключен к первому входу элемента И, второй вход и выход которого соединены соответственно со вторым выходом блока выделения тактовой час" тоты и вторым входом первого счетчи3 92678ка, при этом выход генератора опорной частоты подключен к тактовомувходу второго. счетчика, второй входкоторого соединен с третьим выходомблока выделения тактовой частоты, авыход элемента И подключен к управляющему входу дешифратора, при этомдешифратор содержит два дискриминатора и решающий блок, входы которогосоединены с выходами дискриминаторов,1 овходы которых являются входами дешифратора, выходами которого являются выходы решающего блока, а соответствующие входы дискриминаторов являются управляющим входом дешифратора, а 15 ,блок выделения тактовой частоты содержит два О-триггера, инвертор иэлемент ИЛИ, входы которого соединеныс первыми выходами О-триггеров, приэтом входом блока выделения тактовой щчастоты является первый вход первогоО-триггера, первый выход которогоподключен к первому входу второгоО-триггера, второй вход которого соединен с выходом инвертора, вход кото-г 5рого соединен со вторым входом первого О-триггера и является тактовым входом блока выделения тактовой частоты,выходами которого являются первыйи второй выходы второго О-триггера 5 ви выход элемента ИЛИ, каждый дискриминатор содержит элемент И и дваО-триггера, выходы которого подключены ко входам элемента И, выход которого и второй выход второго О-тригге 35ра являются выходами дискриминатора,входами которого являются соответствующие входы О-триггеров, кроме того,решающий блок содержит элемент И ипоследовательно соединенные первыйи второй элементы ИЛИ, причем входыэлемента И и первого элемента ИЛИ являются входами решающего блока, выходами которого являются выход элемента И и выход второго элемента ИЛИ,второй вход которого соединен с выходом элемента И.На фиг. 1 представлена структурнаяэлектрическая схема демодулятора нафиг. 2 - структурная электрическаясхема блока выделения тактовой частоты; на фиг. 3 - структурная электрическая схема дешифратора, на фиг. 4 входные и выходные сигналы демодулятора.55Цифровой демодулятор сигналое отно. сительной фазовой манипуляции содержит формирователь 1 входного сигнала, блок 2 выделения тактовой частоты,6 4первый счетчик 3, дешифратор 4, триггер 5, второй счетчик 6, элемейт И 7генератор 8 опорной частоты, дешифратор 4 содержит два дискриминатора 9и 10 импульса в код, а второй счетчик 6 - сигнала паузы. Разрядностьсчетчиков зависит от частоты тьв искорости передачи сообщений. Выборвеличины акоп, в свою очередь, опреде"ляется желаемой величиной постояннойинтегрирования. Поскольку в цифровойтехнике принята двоичная система ииспользуются, как правило,. двоичныесчетчики, целесообразно выбиратьоп = 2"Ф 1, Гт щ 1200-4800 Гцскорость передачи сообщений. Чембольше и, тем точнее привязка по фазе, больше постоянная интегрирования,но и тем выше разрядность счетчиков,а это влечет за собой увеличение аппаратуры. Поэтому величина и должнавыбираться из разумного компромисса.Современные интегральные схемысчетчиков содержат в одном корпусесчетчик йа 8 разрядов, т.еп= 8.Одновременно желательно, чтобы частота Го была меньше 1 мГц, так каксовременные экономичные интегральные микросхемы по КМОП - технологииработают в диапазоне частот до1 мГц. Выбирая и = 7, получаем Гоп ==1536-614;4 кГц.При таких значенияхчастоты Гоп устойчиво работают практически все отечественные микросхемы.,Символы "1" или "0" в относительной фазовой манипуляции передаютсяразличными импульсами (фиг, 4 а) в зависимости от последовательности передаваемых импульсов.В случае идеальных сигналов приприеме символа "1" каждый счетчик 3или 6 считает импульсы частоты 1286от 0 до 63, при этом за один тактпоследовательность работы счетчиковможет быть любой: в 1,5 и 6 тактах(фиг. 4 г,д) сначала работает счетчик3, преобразующий длительность сигнала импульса в код, а затем счетчик6, преобразующий длительность сигнала паузы в код. В тактах 3 и 8(фиг. 4 г,д) и решающий блок 11, блок2 выделения тактовой частоты состоитиз двух О-триггеров 12 и 13, инвертора 14 и элемента ИЛИ 15, каждыйдискриминатор 9 и 10 содержит дваО-триггера 16-19 и элемент И 20 и 21,а решающий блок 11 содержит элемент5 92 б 7 И 22 и первый и второй элементы ИЛИ 23 и 24.Цифровой демодулятор сигналов от носительной фазовой манипуляции работает следующим образом. 5 частоты и последовательности прини" маемыхпульсов сигнала относительной фазовой манипуляции будут исключены. Сигналы импульса и паузы интег" рируются первым и вторым счетчиками 3 и 6, причем первый счетчик 3 преоб. разует длительность сигнала последовательность работы счетчиков будет иной. При совпадении кодов, снимаемых со счетчиков 3 и 6, дешифратор 4 вырабатывает сигнал "1". При приеме символа "О", как видно из Фиг, 4 г,д, может работать либо счетчик 3 (2 и 7 такты), либо счетчик 6 (4 такт). В этом случае любой счетчик считает импульсы частоты 128 тт от 0 до 128. Сигналом разрешения счета для любого счетчика является сигнал логической "1". Другими словами, информация о том, что на входе демодулятора при" сутствует символ "1" выдается при равенстве длительности сигнала импульса и сигнала паузы, которые долж .64 1 ны быть равны. При128 Гт 2 т1 Фу ф 200 Гц, йод, й паузы -" а2:2 ООГц = 417 мкс. Информация о том, что на входе демодулятора присутствует символ "0" выдается, если алитель-.1 ность сигнала паузы равна.Гт== 834 мкс.200 ГцРабота дешифратора 4 может бытьописана следующей таблице истинности: Входнойсимвол У 1 У 2 Тактовыйвыход Инфор- мационный выВыходы триггеров 17 18 19 ход 0 9 0ла импульса (паузы) не равна точно выбранному заранее значению. При этом соответственно изменяются и коды на выходе счетчиков. Для конкретного канала связи характерны вполне определенные помехи.Для повышения достоверности принимаемой информации в состав дешифрато Ра 4 введены дискриминаторы 9 и 10,Однако иэ-за краевых искажений, дроблений и смещениии характеристических моментов восстановления посылок в реальных каналах связи длительности сигналов импульса и паузы могут меняться. При этом возникают ситуации, когда длительность сигнала импульса не равна точно длительности сигнала паузы или длительность сигнаформирователь 1 входного сигнала согласует линию связи с собственно демодулятором, на вход которого поступает сигнал (фиг. 4 а). Из фазомани- о10 пулированного сигнала в блоке 2 выделения тактовой частоты формируются импульсы длительностью 1 о= (фиг.4 в),Й оп совпадающие по времени с импульсами от генератора 8 опорной частоты (Фиг. 4 б) и соответствующие моментам перехода через нуль входным сигналам (фиг. 4 а). Фазоманипулированный сигнал поступает на информационный вход О-триггера 12, в О-триггер 13 инфор 26 мация переписывается с задержкойгТьз -"- фиг. 4 г). В результате на2 Гевыходе элемента ИЛИ 15 образуется сиг. нал, длительность импульса которого1Ти-2 т- Ту (фиг. 4 е), Посколькувпприменяемые триггера тактируются частотой генератора 8 опорной частоты, информация с выходов блока 2 выделения тактовой частоты привязана к частоте Гвя генератора 8 опорной частоты, используемого при дальнейвей обработке сигнала, Ошибки из-эа несинфазности последовательности так товых импульсов генератора 8 опорной86 Формула изобретения 7 9267 которые обеспечивают сохранение требуемой информации при изменении длительности входных сигналов в определенных пределах. Дискриминаторы 9 и 1 О идентичные, выполнены на двух з Р-триггерах 16 и 17 (или 18 и 19) и одном элементе И 20 (фиг. 3). Информационный вход каждого Р-триггера дискриминатора подключен к старшему разряду счетчика 3 или 6 (фиг. 3), 16 При таком построении дискриминаторов Р-триггер 16 (18) переходит в единичное состояние с приходом 18-,го импульса частоты 1 щ .= 128 Гт и сбрасывается в нулевое состояние 80-м им% пульсом. Р"триггер 17 (19) переходит в единичное состояние с приходом 96-го импульса и сбрасывается в нулевое состояние 136-ым импульсом час тоты акоп . В дискриминаторе 9 (1 О) образованы два "окна" : 48-80 импульсами и 96- 136 импульсами, Таким образом, символ "1" будет принят правильно, даже если, например, ц,чп-" е 50 импульсов частоты 1281, а 23 поды = 78 импульсов частоты 128 Гт . Символ "0" принят правильно, если йод йпсмды ) изменяется в пределах окна 96- 136 импульсов частоты 128 тг .Итак в формировании сигнала им 30 пульса при дешифрацйи.символа "1" участвуют Р-триггеры 16 и 18 (фиг. 3), При дешифрации символа "0" работает или Р-триггер 19. Достаточно перехода в единичное состояние любого из Р-триггеров 17 или 19 для формирования на выходе сигнала паузы (см. таблицу истинности). формирование выходных сигналов дешифратора осуществляет решающий блок 11. С выхода элемента И 22 сни , мается информационный сигнал (фиг.3), в с выхода элемента ИЛИ 21 - тактовый сиг. Нал (фиг,чж) .С выхода решающего блока 11 тактовый сигнал поступает на один вход элемента И 7, на второй вход которого подается стробирующий сигнал с выхода блока 2 выделения тактовой частоты. Выходной тактовый сигнал демодулятора снимается с выхода элемента И 7 и он же, поступая на входы обнуления счетчиков 3 и 6 и дискриминаторов 9 и 10, сбрасывает их в нулевое состояние, подготавливаяИ тем самым для анализа следующего входного символа (фиг. чи).Выходной информационный сигнал демодулятора, привязанный по фазе к выходному тактовому сигналу, снимается с выхода 0-триггера 5 (фиг, 1 к).Технико-экономический эффект описанного демодулятора сигналов относительной фазовой манипуляции состоит в повышении помехоустойчивости, что достигается определением длитель" ности как импульса, так и паузы входного сигнала, сравнением их, а также применением дешифратора, содержащего дискриминаторы, Выполнение описанным образом блока выделения тактовой частоты позволяет снизить требования к нестабильности и соответствию опорных частот передающей и приемной аппаратуры, а также обес. печить работу при кратковременных замираниях в канале связи. 1. Цифровой демодулятор сигналов относительной фазовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены к входам дешифратора, первый выход которого соединен с первым входом триггера, а также генератор опорной частоты, выход которого подключен к тактовым входам блока выделения тактовой частоты и первого счетчика, о т л и ч а ю щ и й с я .тем, что, с целью повышения помехоустойчивости при различных уровнях помех в линии связи, введены второй счетчик и элемент И, выход которого подключен к второму входу триггера и первому входу второго счетчика, выходы которого соединены с дополнительными входами дешифратора, второй выход которого подключен к первому входу элемента И, второй вход и выход которого соединены соответственно с вторым выходом блока выделения тактовой частоты и вторым входом первого счетчика, при этом выход генератора опорной частоты подключен к тактовому входу второго счетчика, второй вход которого соединен с третьим выходом блока выделения тактовой часто- ты, а выход элемента И подключен к управляющему входу дешифратора,2. Демодулятор по и. 1, о т л ич,а ю щ и й с я тем, что дешифратор содержит два дискриминатора и решающий блок, входы .которого соединены9261 с выходами дискриминаторов, входыкоторых являются входами дешифратора,выходами которого являются выходырешающего блока, а соответствующиевходы дискриминаторов являются управ 5ляющим входом дешифратора,3. Демодулятор по и. 1, о т л ич а ю щ и й с я тем, что блок выделения тактовой частоты содержит дваО-триггера, инвертор и элемент ИЛИ, Овходы которого соединены с первыми.выходами О-триггеров, при этом входомблока выделения тактовой частоты является первый вход первого О-триггера, первый выход которого подключен 1%к первому входу второго О-триггера,второй вход которого соединен с выходом инвертора, вход которого соединен с вторым входом первого О-триггера и является тактовым входом 20блока выделения тактовой частоты,выходами которого являются первыйи второй выходы второго О-триггераи выход элемента ИЛИ. 8610Демодулятор по и. 2, о т л ич а ю щ и й с я тем, что каждый дискриминатор содержит элемент И и два О-триггера, выходы которого подключены к входам элемента И, выход которого и второй выход второго О-триггера являются выходами дискриминатора, входами которого являются соответствующие входы О-триггеров.5 Демодулятор по и. 2, о т л ич а ю щ и й с я тем, что рещающий блок содержит элемент И и последовательно соединенные первый и второй элементы ИЛИ, причем входы элемента И и. первого элемента ИЛИ являются входами реаающего блока, выходами которого являются выход элемента И и выход второго элемента ИЛИ, второй вход которого соединен с выходом элемента И.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР И 6 ОБЗЗ 2, . Н ОЬИ/18, ЕУ 6.,/ 121 с ак ПодписноСССР к ф д Г ефеЕу Составитель В. ЛякишевКинив ТехРед и, Тепер КоРРектоР Г.Решетник000/48 Тираж ВНИИПИ Государст по делам изоб 113035 Москва, 85енного комитетатений и открытий35 Рауаская натиал ППП "Патент", г. Ужгород, ул. Проектная,

СмотретьЗаявка

2904490, 04.04.1980

ПРЕДПРИЯТИЕ ПЯ А-3706

МАКАРОВ ВЛАДИМИР ВАСИЛЬЕВИЧ, ЦВЕТКОВ ВАСИЛИЙ АНАТОЛЬЕВИЧ, ЛУКИН БОРИС МИХАЙЛОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, манипуляции, относительной, сигналов, фазовой, цифровой

Опубликовано: 07.05.1982

Код ссылки

<a href="https://patents.su/9-926786-cifrovojj-demodulyator-signalov-otnositelnojj-fazovojj-manipulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов относительной фазовой манипуляции</a>

Предыдущий патент: Устройство для детектирования фазоманипулированных сигналов

Следующий патент: Устройство для измерения статистических параметров телефонного сообщения

Случайный патент: Весоизмерительное устройство