Устройство для детектирования фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 926785

Авторы: Елагин, Кропачев, Павличенко, Рахович

Текст

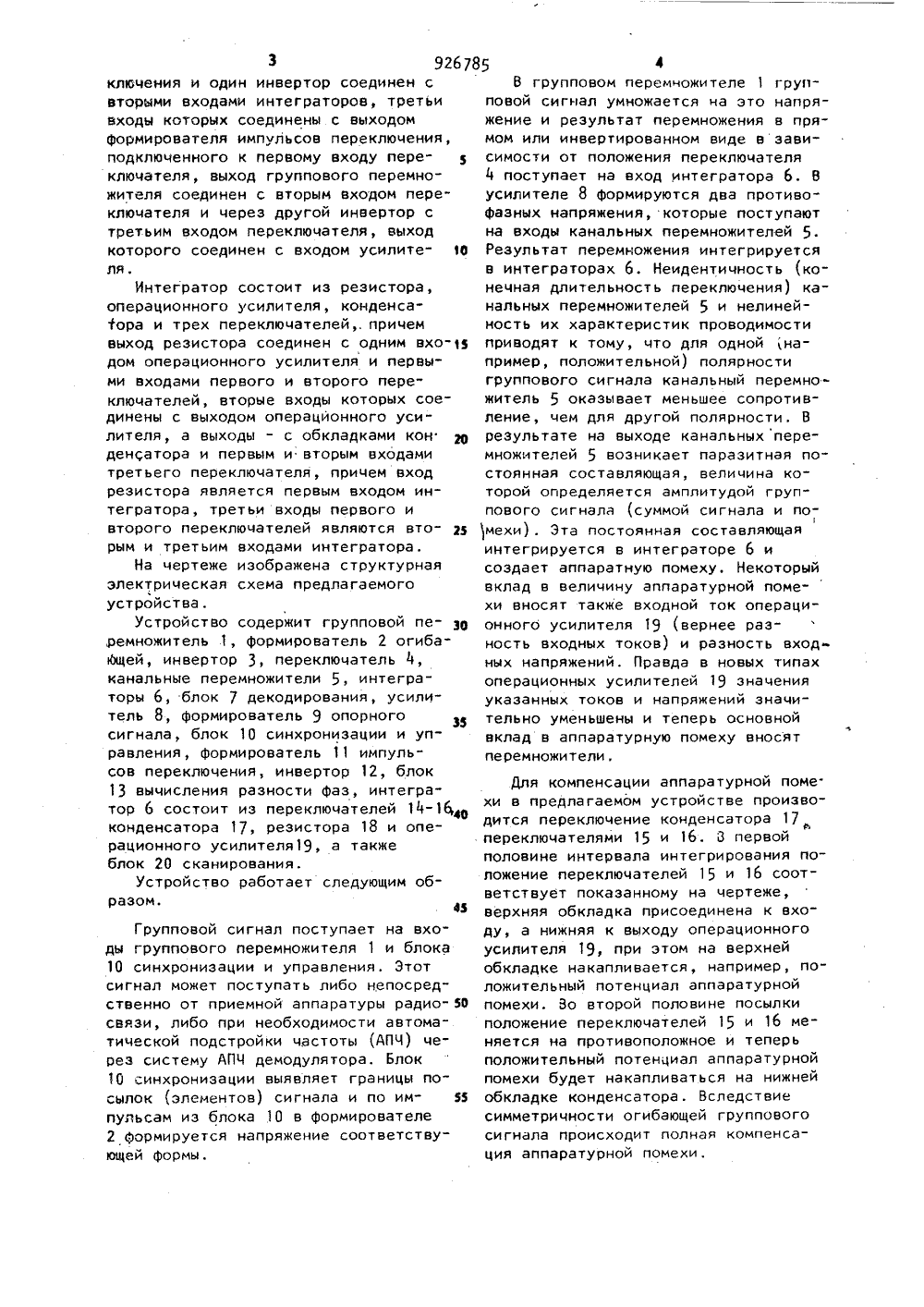

Сефз СеватеннкСфцнаннетнчвени кРвенублнн ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Заявитель Ч 54) УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАН ФАЗОИАНИПУЛИРОВАННЫХ СИГНАЛО сится к элект о" меиИзобретение отно р связи.Известно устройство для детектирования фаэоманипулированных сигналов, содержащее формирователь опорного сигнала, выход которого соединен с первыми .входами канальных перемножителей, вторые и третьи входы которых соединены с выходами усилителя, а выходы соединены с первыми входами интеграторов, выходы которых соединены с входами блока сканирования, выходы которого соединены с входами блока вычисления разности фаэ,подключенного к блоку декодирования, последовательно соединенные блок синхронизации и управления, формирователь огибающий и групповой перемножитель 111 .Однако в известном устройстве недостаточная помехоустойчивость.Цель изобретения " повцаение по хоустойчивости путем комйенсации а паратурной помехи. Указанная цель достигается тей; что в устройство для детектирования фазоманипулированных сигналов содержащее формирователь опорного сигнала, выход которого соединен с первыми входами канальных перемножителей вторые и третьи входы которых соединены с выходами усилителя, а выходы соединены с первыми входами интЕгра торов, выходы которых соединены с входами блока сканирования, выходы которого соединены с входами блок 4 вычисления разности фаэ, подключенно го к блоку декодирования, последовательно соединенные блок синхронизации и управления, формирователь огибающей и групповой перемножитель, введены формирователь импульсов переключе.ния два инвертора и переключатель, причем другой вход группового пере- множителя соединен с входом блока синхронизации и управления, выход которого через последовательно соеди-: ненные Формирователь импульсов пере 3 9267 ключения и один инвертор соединен с вторыми входами интеграторов, третьи входы которых соединены с выходом формирователя импульсов переключения, подключенного к первому входу переключателя, выход группового перемножителя соединен с вторым входом переклюцателя и через другой инвертор с третьим входом переключателя, выход которого соединен с входом усилите ля.Интегратор состоит из резистора, операционного усилителя, конденсатора и трех переключателей причем выход резистора соединен с одним входом операционного усилителя и первыми входами первого и второго переключателей, вторые входы которых соединены с выходом операцйонного усилителя, а выходы - с обкладками кон денсатора и первым и вторым входами третьего переключателя, причем вход резистора является первым входом интегратора, третьи входы первого и второго переключателей являются вто- д рым и третьим входами интегратора.На чертеже изображена структурная электрическая схема предлагаемого устройства.УстРойство содержит групповой пе,ремножитель 1, формирователь 2 огибающей, инвертор 3, переключатель 4, канальные перемножители 5, интеграторы 6, блок 7 декодирования, усилитель 8, формирователь 9 опорного сигнала, блок 10 синхронизации и управления, формирователь 11 импульсов переключения, инвертор 12, блок 13 вычисления разности фаз, интегратор 6 состоит иэ переключателей 14-14 конденсатора 17, резистора 18 и операционного усилителя 19, а также блок 20 сканирования.Устройство работает следующим образом.45Групповой сигнал поступает на входы группового перемножителя 1 и блока 10 синхронизации и управления. Этот сигнал может поступать либо непосредственно от приемной аппаратуры радио связи, либо при необходимости автоматической подстройки частоты (АПЧ) через систему АПЧ демодулятора, Блок 10 синхронизации выявляет границы посылок (элементов) сигнала и по им пульсам иэ блока 10 в формирователе 2 формируется напряжение соответствующей формы. В групповом перемножителе 1 групповой сигнал умножается на это напря жение и результат перемножения в пря мом или инвертированном виде в зависимости от положения переключателя 4 поступает на вход интегратора 6, В усилителе 8 формируются два противофазных напряжения, которые поступают на входы канальных перемножителей 5. Результат перемножения интегрируется в интеграторах 6. Неидентичность (ко нечная длительность переключения) ка нальных перемножителей 5 и нелинейность их характеристик проводимости приводят к тому, что для одной (например, положительной) полярности группового сигнала канальный перемно житель 5 оказывает меньшее сопротивление, чем для другой полярности. В результате на выходе канальных пере- множителей 5 возникает паразитная по стоянная составляющая, величина которой определяется амплитудой группового сигнала (суммой сигнала и по 1 мехи). Эта постоянная составляющая интегрируется в интеграторе 6 и создает аппаратную помеху. Некоторый вклад в величину аппаратурной помехи вносят также входной ток операционного усилителя 19 (вернее разность входных токов) и разность вход ных напряжений. Правда в новых типах операционных усилителей 19 значения укаэанных токов и напряжений значительно уменьшены и теперь основной вклад в аппаратурную помеху вносят перемножители. Для компенсации аппаратурной поме. хи в предлагаемом устройстве производится переключение конденсатора 17 переключателями 15 и 16. В первой половине интервала интегрирования положение переключателей 15 и 16 соответствует показанному на чертеже, верхняя обкладка присоединена к входу, а нижняя к выходу операционного усилителя 19, при этом на верхней обкладке накапливается, например, положительный потенциал аппаратурной помехи. Во второй половине посылки положение переключателей 15 и 16 меняется на противоположное и теперь положительный потенциал аппаратурной помехи будет накапливаться на нижней обкладке конденсатора. Вследствие симметричности огибающей группового сигнала происходит полная компенсация аппаратурной помехи.5 926Для того, чтобы не происходила компенсация результата накопления сигнала, одновременно с переключением обкладок конденсатора 17 производится изменение полярности (инверти рование) группового сигнала с помощью переключателя 4 и инвертора 3.Результат интегрирования сигнала поступает для дальнейшей обработки через блок 20 сканирования в блок 13 о вычисления разности фаз и затем в блок 7 декодирования, в котором происходит выделение и браковка символов пораженных сосредоточенной помехой, и выдача на выход устройства информа ционных символов. с максимальным правдоподобием, т,е. реализуется за счет информационной избыточности высокая помехоустойчивость.20формула изобретения1. Устройство для детектирования фаэоманипулированных сигналов, содер-И жащее формирователь опорного сигнала, выход которого соединен с первыми вхо дами канальных перемножителей, вторые и третьи входы которых соединены с выходами усилителя, а выходы соединены с первыми входами интеграторов,выходы которых соединены с входами бло,ка сканирования, выходы которого соединены с входами блока вычисления разности фаз, подключенного к блоку декодирования, последовательно соединенные блок синхронизации и управления, формирователь огибающей и групповой перемножитель, о т л и ч а ющ е е с я тем, что, с целью повыше- О ния помехоустойчивости путем компен 785 6сации аппаратурной помехи, введеныформирователь импульсов переключения,два инвертора и переключатель, при-.чем другой вход группового перемножи"теля соединен с входом блока синхронизации и управления, выход которогочерез последовательно соединенныеформирователь импульсов переключенияи один инвертор соединен с вторымивходами интеграторов, третьи входыкоторых соединены с выходом Формирователя импульсов переключения, подключенного к первому входу переключа.теля, выход группового перемножителясоединен с вторым входом переключателя и через другой инвертор с третьимвходом переключателя, выход которогосоединен с входом усилителя,2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что интеграторсостоит из резистора, операционногоусилителя, конденсатора и трех переключателей, причем выход резисторасоединен с одним входом операционного усилителя и первыми входами первого и второго переключателей, вторыевходы которых соединены с выходом опе.рационного усилителя, а выходы - собкладками конденсатора и первым ивторым входами третьего переключателя, причем вход резистора являетсяпервым входом интегратора, третьивходы, первого и второго переключателей являются вторым и третьим входами интегратора,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРпо заявке й 2683036/09,.кл. Н 0427/22, 09. 11. 78 (прототип).926785 ВНИИРИ Заказ 3000/48 Тираж 685 Подписное Филиал ППП "Патент", г. Ужгород, ул. Проектная,

СмотретьЗаявка

2889787, 19.02.1980

ПРЕДПРИЯТИЕ ПЯ В-8161, ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ЕЛАГИН АЛЕКСЕЙ ВЛАДИМИРОВИЧ, КРОПАЧЕВ ДМИТРИЙ АЛЕКСАНДРОВИЧ, ПАВЛИЧЕНКО ЮРИЙ АГАФОНОВИЧ, РАХОВИЧ ЛЕО МОИСЕЕВИЧ

МПК / Метки

МПК: H04L 27/26

Метки: детектирования, сигналов, фазоманипулированных

Опубликовано: 07.05.1982

Код ссылки

<a href="https://patents.su/4-926785-ustrojjstvo-dlya-detektirovaniya-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для детектирования фазоманипулированных сигналов</a>

Предыдущий патент: Детектор частотно-манипулированных сигналов

Следующий патент: Цифровой демодулятор сигналов относительной фазовой манипуляции

Случайный патент: Устройство для измерения давления ударной волны