Цифровой преобразователь параллельно-последовательного следящего уравновешивания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 866487

Автор: Петренко

Текст

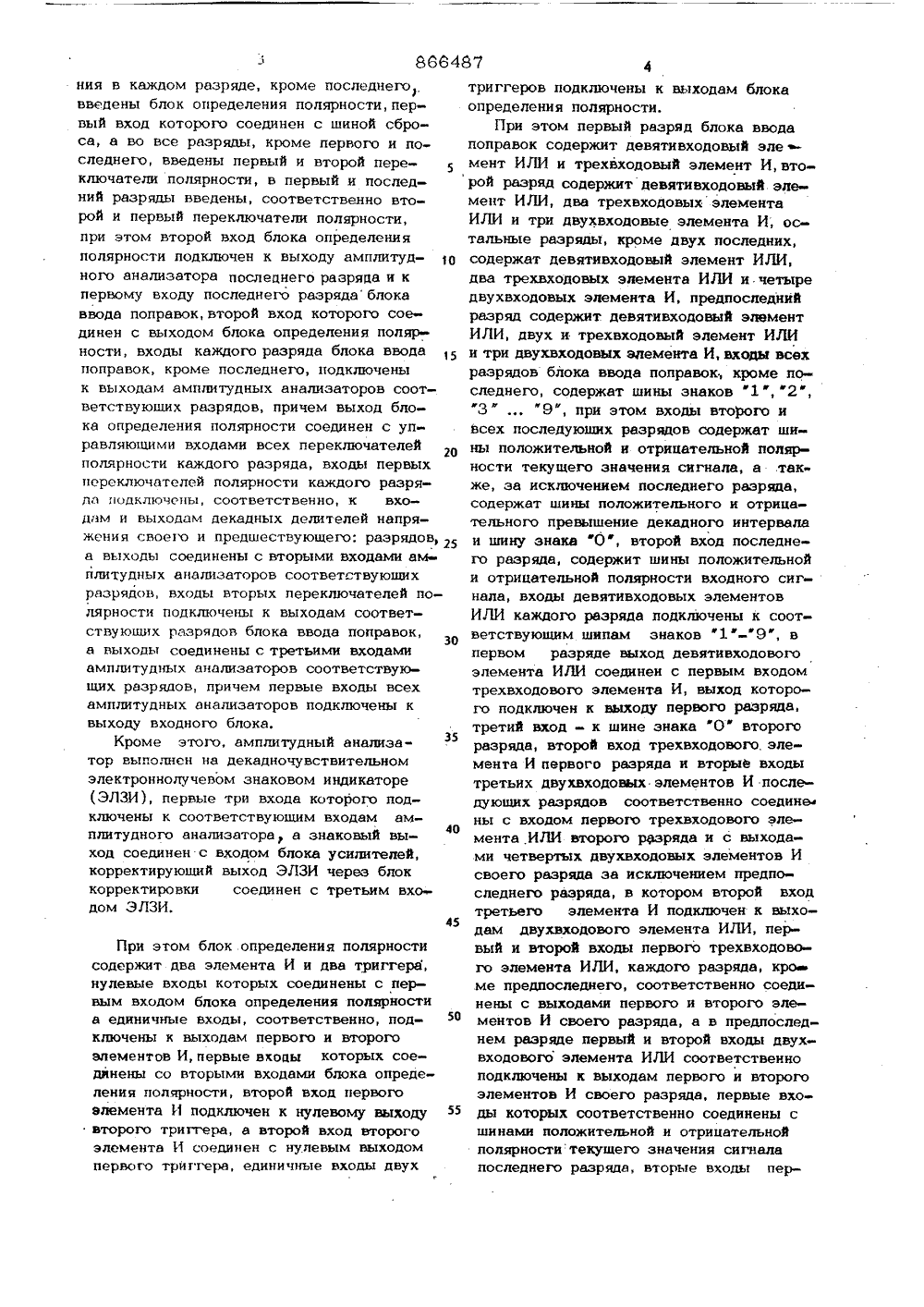

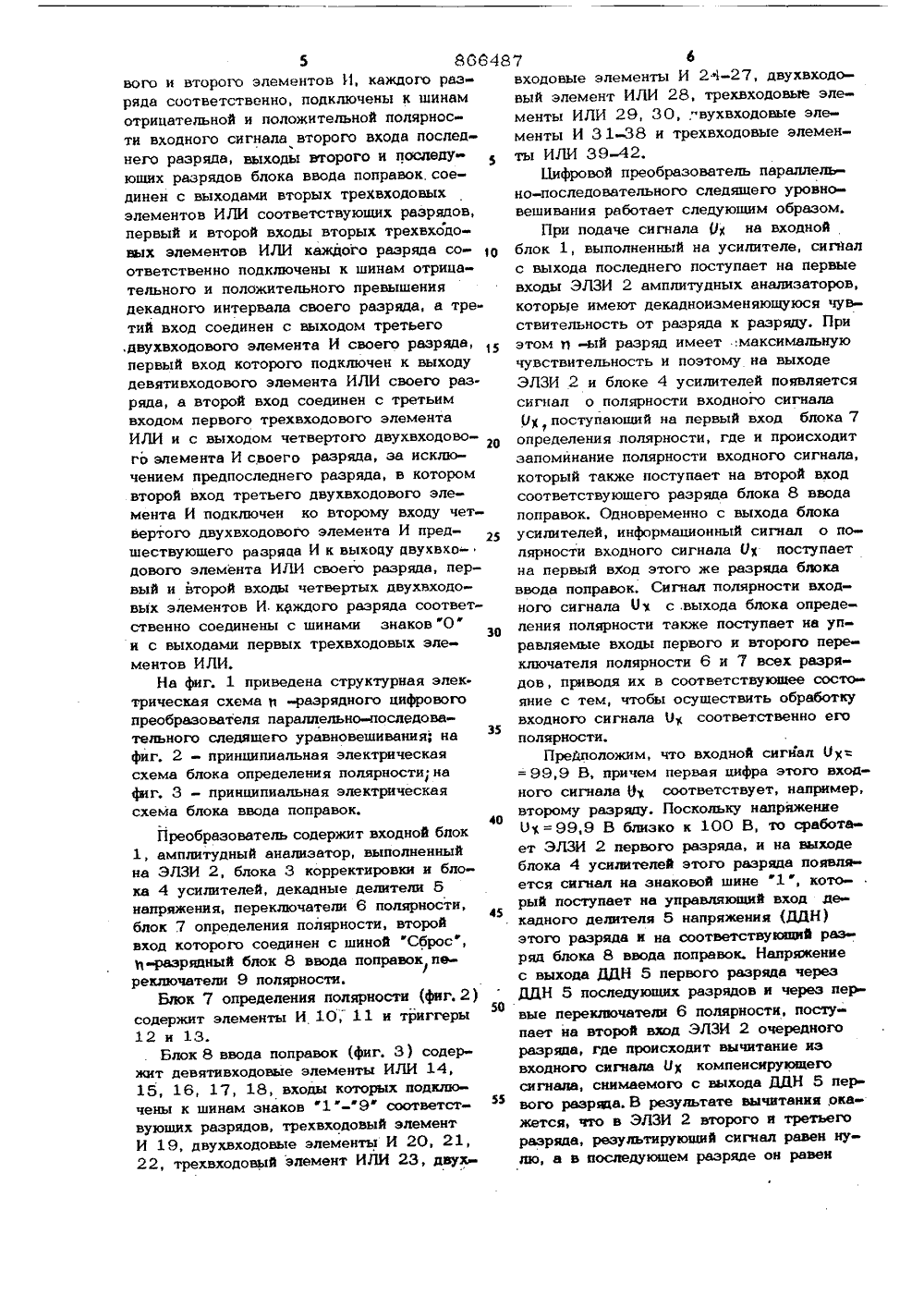

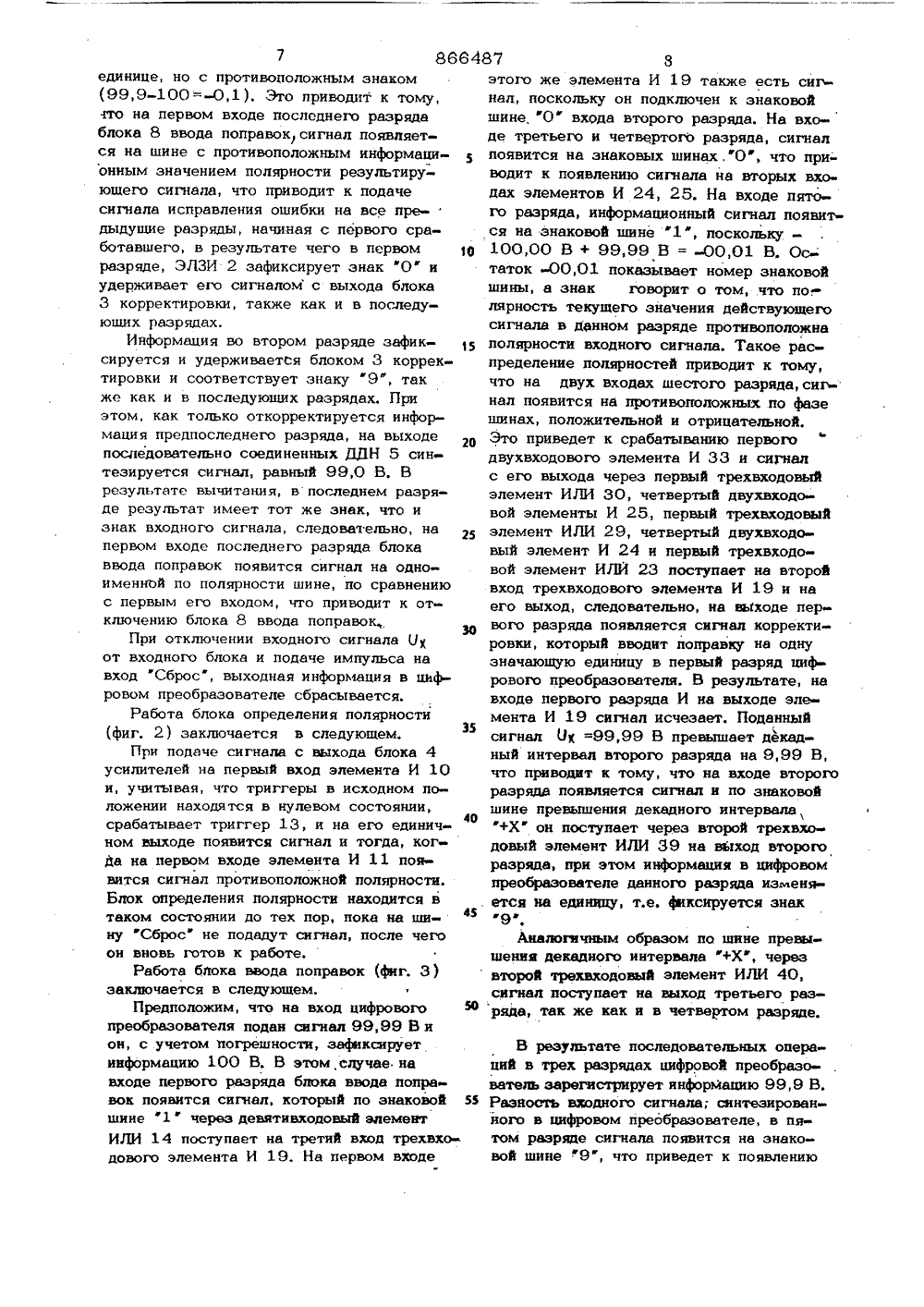

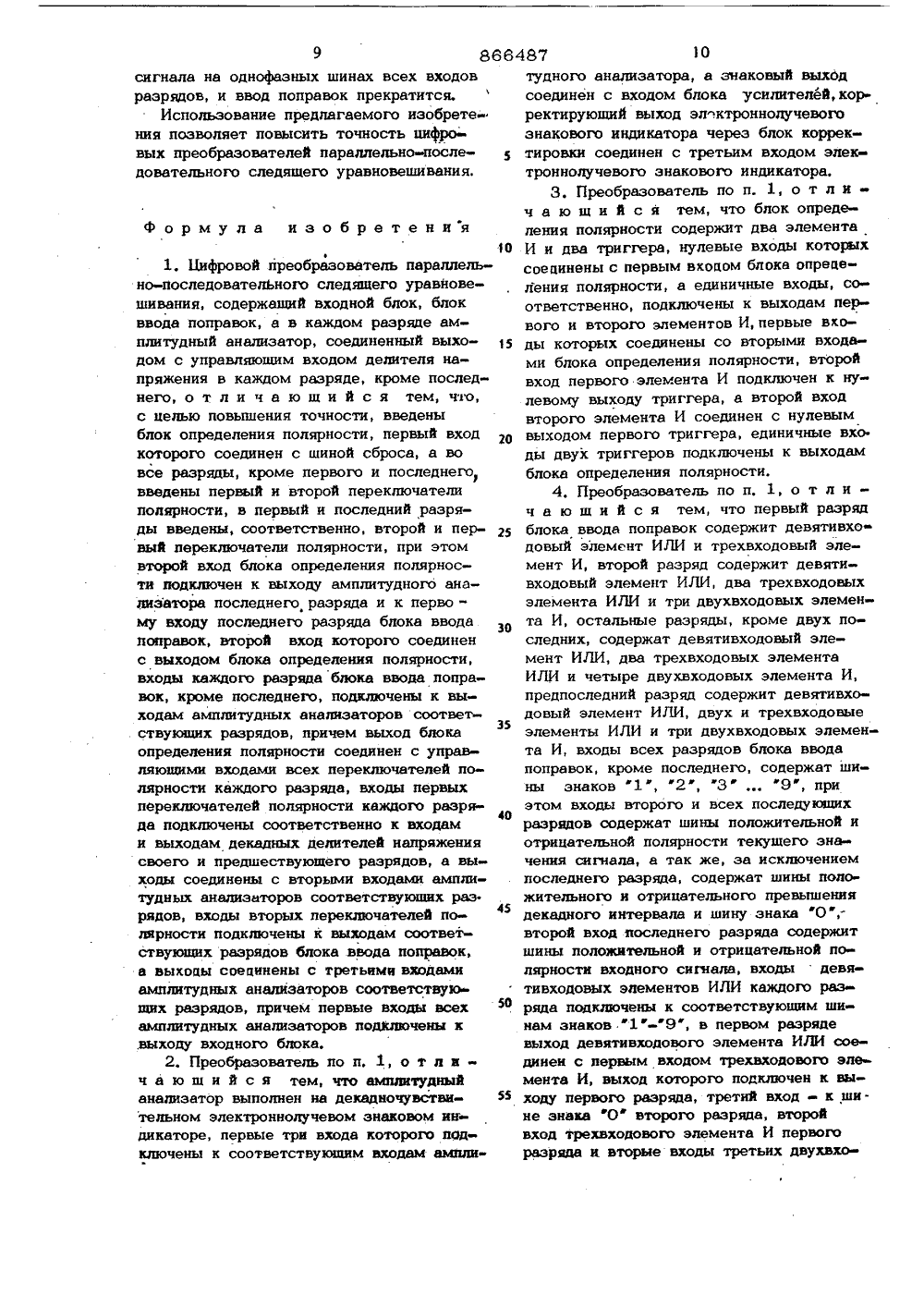

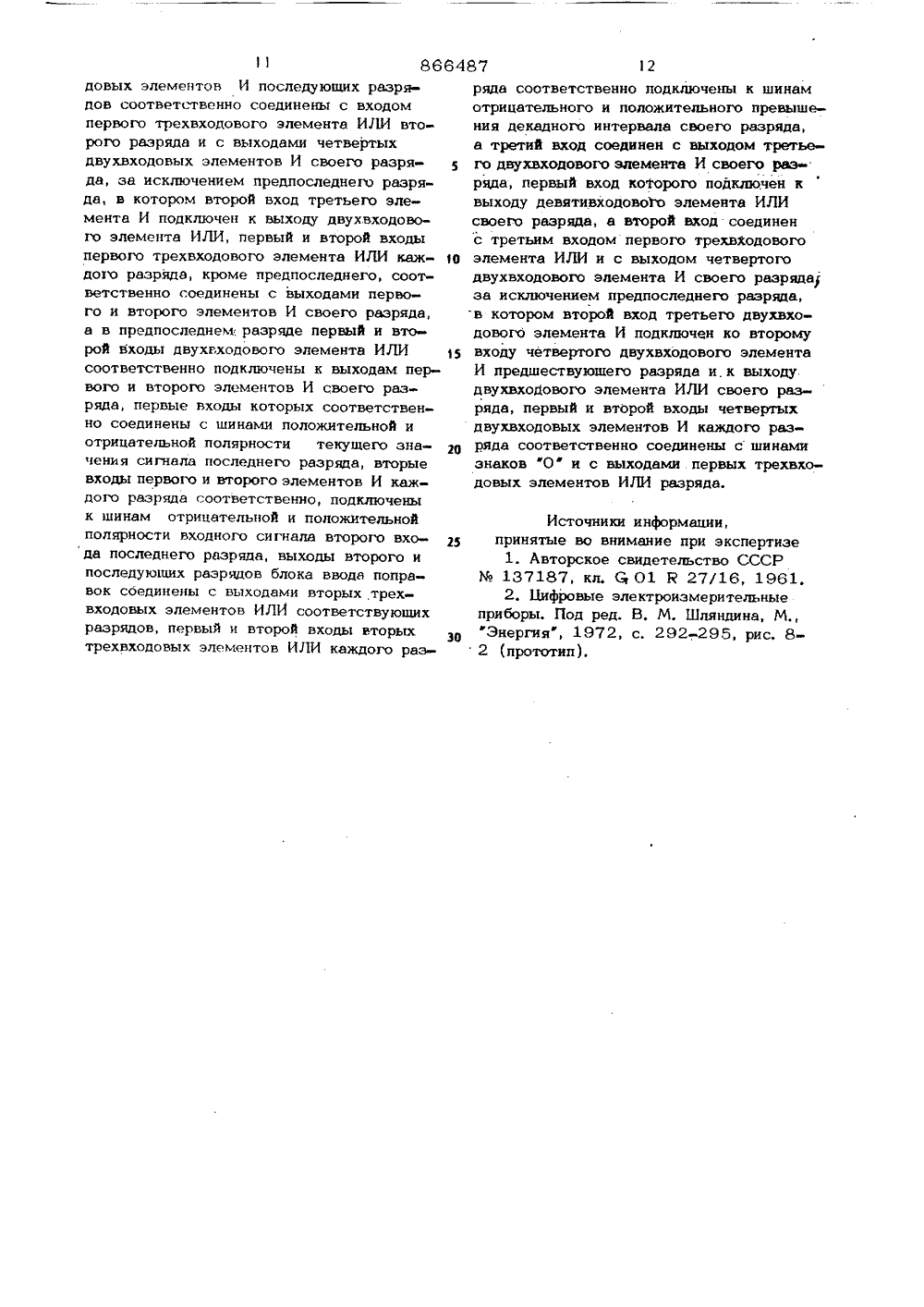

(54) ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНО- ПОСЛЕДОВАТЕЛЬНОГО СЛЕДЯЩЕГО УРАВНОВЕШИВАНИЯ Изобретение относится к цифровой измерительной технике, и может быть использовано при измерении постоянных и медленно меняющихся напряжений.Известен цифровой преобразователь параллельно-последовательного уравновеши- ф вания, в каждый разряд которого включен амплитудный анализатор, делитель напряжения и блок ввода поправок Г 11.Недостатком этого преобразователя яв ляется низкая точность.Известен также цифровой преобразова тель параллельно-последовательного урав новешивания, разряд которого содержит ам плитудный анализатор, делитель напряже 15 ния, блок ввода поправок и вычитакацее устройство, при этом входная шина, через ключ соединена со входом первого амплитудного анализатора и через соответству ющее вычитаюшее устройство н ключ - с20 последующим амплитудным анализатором очередного разряда, а выходы делителей напряжения через ключ соединены со вторым входом вычитаюшего устройства, выход которого через ключ соединен с входом блока ввода поправок, выход последнего соединен со вторым входом делителя напряжения, первый же вход соединен с выходом амплитудного анализатора 23,Недостатком известного преобразователя является низкая точность из м наличия ошибок, порядок которых соответст ь вует весу последующего разряда, а также дополнительных погрешностей, вносимых устройством определения полярности при подключении последнего на входе устройства, Так, при подаче на вход напряже ния 99,9 В, известное устройство не может внести в цифровой выход поправку и выдает на выходе не 99,9 В, а 100 В,Цель изобретения - повышение точности.Поставленная цель достигается тем, что в цифровой преобразователь параллельно- последовательного следящего уравновешивания, содержащий входной блок, блок ввода поправок, а в каждом разряде ампли- тудный анализатор, соединенный выходом с управляющим входом делителя напряжения в каждом разряде, кроме последнеговведены блок определения полярности, первый вход которого соединен с шиной сброса, а во все разряды, кроме первого и последнего, введены первый и второй переключатели полярности, в первый и последний разряды введены, соответственно второй и первый переключатели полярности,при этом второй вход блока определенияполярности подключен к выходу амплитудного анализатора последнего разряда и кпервому входу последнего разряда блокаввода поправок, второй вход которого сое 10 динен с выходом блока определения поляр ности, входы каждого разряда блока ввода поправок, кроме последнего, подключены к выходам амплитудных анализаторов соответствующих разрядов, причем выход блока определения полярности соединен с управляющими входами всех переключателей 15 20 полярности каждого разряда, входы первых переключателей полярности каждого разряла подключены, соответственно, к входам и выходам декадных делителей напряплитудных анализаторов соответствующихразрядов, входы вторых переключателей полярности подключены к выходам соответствующих разрядов блока ввода поправок,а выходы соединены с третьими входамиамплитудных анализаторов соответствующих разрядов, причем первые входы всехамплитудных анализаторов подключены квыходу входного блока,Кроме этого, амплитудный анализатор выполнен на декадночувствительномэлектроннолучевом знаковом индикаторе(ЭЛЗИ), первые три входа которого подключены к соответствующим входам амплитудного анализатора, а знаковый выход соединен с входом блока усилителей,корректирующий выход ЭЛЗИ через блоккорректировки соединен с третьим входом ЭЛЗИ,30 35 40 При этом блок определения полярности содержит два элемента И и два триггер, нулевые входы которых соединены с первым входом блока определения полярности а единичные входы, соответственно, подключены к выходам первого и второго элементов И,первые вкоды которых соединены со вторыми входами блока определения полярности, второй вход первого элемента И подключен к нулевому выходу второго триггера, а второй вход второго элемента И соединен с нулевым выходом первого триггера, единичные входы двух 50 55 женин своего и предшествующего: разрядов,25а выходы соединены с вторыми входами ам триггеров подключены к выходам блока определения полярности.При этом первый разряд блока ввода поправок содержит девятивходовый эле мент ИЛИ и трехвходовый элемент И,второй разряд содержит девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и три двухвходовые элемента И, остальные разряды, кроме двух последних, содержат девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и четыре двухвходовых элемента И, предпоследний разряд содержит девятивходовый элемент ИЛИ, двух и трехвходовый элемент ИЛИ и три двухвходовых элемента И, входы всех разрядов блока ввода поправок; кроме последнего, содержат шины знаков "1 , "2", "3 ""9", при этом входы второго и всех последующих разрядов содержат шины положительной и отрицательной полярности текущего значения сигнала, а также, за исключением последнего разряда, содержат шины положительного и отрицательного превышение декадного интервала и шину знака "О, второй вход последнего разряда, содержит шины положительной и отрицательной полярности входного сигнала, входы девятивходовых элементов ИЛИ каждого разряда подключены к соответствующим шипам знаков "1"-9", в первом разряде выход девятивходового элемента ИЛИ соединен с первым входом трехвходового элемента И, выход которого подключен к выходу первого разряда, третий вход - к шине знака "О" второго разряда, второй вход трехвходового,элемента И первого разряда и вторые входы третьих двухвходовых элементов И последующих разрядов соответственно соедине ны с входом первого трехвходового элемента .ИЛИ второго разряда и с выходами четвертых двухвходовых элементов И своего разряда за исключением предпоследнего разряда, в котором второй вход третьего элемента И подключен к выходам двухвходового элемента ИЛИ, первый и второй входы первого трехвходового элемента ИЛИ, каждого разряда, кро ме предпоследнего, соответственно соединены с выходами первого и второго элементов И своего разряда, а в предпоследнем разряде первый и второй входы двухвходового элемента ИЛИ соответственно подключены к выходам первого и второго элементов И своего разряда, первые входы которых соответственно соединены с шинами положительной н отрицательной полярноститекущего значения сигнала последнего разряда, вторые входы первходовые элементы И 2 4-27, двухвходовый элемент ИЛИ 28, трехвходовые элементы ИЛИ 29, 30 мвухвходовые элементы И 31-38 и трехвходовые элементы ИЛИ 39-42,Цифровой преобразователь параллельно-последовательного следящего уровновешивания работает следующим образом.При подаче сигнала У на входнойблок 1, выполненный на усилителе, сигналс выхода последнего поступает на первыевходы ЭЛЗИ 2 амплитудных анализаторов,которЫе имеют декадноизменяюшуюся чувствительность от разряда к разряду. Приэтом и -ый разряд имеет, максимальнуючувствительность и поэтому на выходеЭЛЗИ 2 и блоке 4 усилителей появляетсясигнал о полярности входного сигналаО поступающий на первый вход блока 7определения полярности, где и происходитзапоминание полярности входного сигнала,который также поступает на второй входсоответствующего разряда блока 8 вводапоправок. Одновременно с выхода блокаусилителей, информационный сигнал о полярности входного сигнала Ох поступаетна первый вход этого же разряда блокаввода поправок. Сигнал полярности входного сигнала О с .выхода блока определения полярности также поступает на управляемые входы первого и второго переключателя полярности 6 и 7 всех разрядов, приводя их в соответствующее состояние с тем, чтобы осуществить обработкувходного сигнала 0 соответственно егополярности.Предположим, что входной сигнал О:= 99,9 В, причем первая цифра этого входного сигнала 9 соответствует, например,второму разряду. Поскольку напряжениеО =99,9 В близко к 100 В, то сработает ЭЛЗИ 2 первого разряда, и на выходеблока 4 усилителей этого разряда появляется сигнал на знаковой шине 1", который поступает на управляющий вход декадного делителя 5 напряжения (ДДН)этого разряда и на соответствующий разряд бпока 8 ввода поправок. Напряжениес выхода ДДН 5 первого разряда черезДДН 5 последующих разрядов и через первые переключатели 6 полярности, поступает на второй вход ЭЛЗИ 2 очередногоразряда, где происходит вычитание извходного сигнала ОХ компенсирующегосигнала, снимаемого с выхода ДДН 5 первого разряда, В результате вычитания,окажется, что в ЭЛЗИ 2 второго и третьегоразряда, результирующий сигнал равен нулю, а в последующем разряде он равен 5 8 М 487 6вого и второго элементов И, каждого разряда соответственно, подключены к шинамотрицательной и положительной полярности входного сигнала второго входа последнего разряда, выходы второго и последующих разрядов блока ввода поправок, соединен с выходами вторых трехвходовыхэлементов ИЛИ соответствующих разрядов,первый и второй входы вторых трехвходовых элементов ИЛИ каждого разряда соответственно подключены к шинам отрицательного и положительного превышениядекадного интервала своего разряда, а третий вход соединен с выходом третьего,двухвходового элемента И своего разряда,первый вход которого подключен к выходудевятивходового элемента ИЛИ своего разряда, а второй вход соединен с третьимвходом первого трехвходового элементаИЛИ и с выходом четвертого двухвходового элемента И своего разряда, за исключением предпоследнего разряда, в которомвторой вход третьего двухвходового элемента И подключен ко второму входу четвертого двухвходового элемента И предшествующего разряда И к выходу двухвкодового элемента ИЛИ своею разряда, первый и второй входы четвертых двухвходовых элементов И. каждого разряда соответственно соединены с шинами знаков "0"и с выходами первых трехвходовых элементов ИЛИ,На фиг, 1 приведена структурная электрическая схема и -разрядного цифровогопреобразователя параллельно-последовательного следящего уравновешивания, на35фиг, 2 - принципиальная электрическаясхема блока определения полярности; нафиг, 3 - принципиальная электрическаясхема блока ввода поправок,40Преобразователь содержит входной блок1, амплитудный анализатор, выполненныйна ЭЛЗИ 2, блока 3 корректировки и блока 4 усилителей, декадные делители 5напряжения, переключатели 6 полярности,блок 7 определения полярности, второйвход которого соединен с шиной "Сбросф,Н-разрядный блок 8 ввода поправок пвреключатели 9 полярности.Блок 7 определения полярности (фиг. 2)50содержит элементы И 10; 11 и триггеры12 и 13.Блок 8 ввода поправок (фиг. 3) содержит девятивходовые элементы ИЛИ 14,15, 16, 17, 18, входы которых подключены к шинам знаков 1 - 9 соответстфю ф 5вуюших разрядов, трехвходовый элементИ 19, двухвходовые элементы И 20, 21,22, трехвходовый элемент ИЛИ 23, двух(99,9-100=-0,1), Это приводит к тому,то на первом входе последнего разрядаблока 8 ввода поправок сигнал появляется на шине с противоположным информационным значением полярности результируюшего сигнала, что приводит к подачесигнала исправления ошибки на все пре-дыдущие разряды, начиная с первого сработавшего, в результате чего в первомразряде, ЭЛЗИ 2 зафиксирует знак "0" иудерживает его сигналом с выхода блока3 корректировки, также как и в последуюших разрядах.Информация во втором разряде зафиксируется и удерживается блоком 3 корректировки и соответствует знаку "9", также как и в последующих разрядах. Приэтом, как только откорректируется информация предпоследнего разряда, на выходепоследовательно соединенных ДОН 5 синтеэируется сигнал, равный 99,0 В, Врезультате вычитания, в последнем разряде результат имеет тот же знак, что изнак входного сигнала, следовательно, напервом входе последнего разряда блокаввода поправок появится сигнал на одноименной по полярности шине, по сравнениюс первым его входом, что приводит к отключению блока 8 ввода поправок,При отключении входного сигнала 0от входного блока и подаче импульса навход Сброс", выходная информация в цифровом преобразователе сбрасывается.Работа блока определения полярности(фиг. 2) заключается в следующем.При подаче сигнала с выхода блока 4усилителей на первый вход элемента И 10и, учитывая, что триггеры в исходном положении находятся в нулевом состоянии,срабатывает триггер 13, и на его единичном выходе появится сигнал и тогда, когда на первом входе элемента И 11 появится сигнал противоположной полярности.Блок определения полярности находится втаком состоянии до тех пор, пока на шину "Сброс" не подадут сигнал, после чегоон вновь готов к работе.Работа бйокв ввода поправок (фиг. 3)заключается в следующем,Предположим, что на вход цифровогопреобразователя подан сигнал 99,99 В ион, с учетом погрешности, зафиксируетинформацию 100 В. В этом, случае нввходе первого разряда блока ввода поправок появится сигнал, который по знаковойшине "1 " через девятивходовый элементИЛИ 14 поступает на третий вход трехвходового элемента И 19, На первом входе этого же элемента И 19 также есть сигнал, поскольку он подключен к знаковойшине "0" входа второго разряда, На входе третьего и четвертого разряда, сигналпоявится на знаковых шинах,"0", что приводит к появлению сигнала на вторых входах элементов И 24, 25. На входе пятого разряда, информационный сигнал появится на знаковой шине "1 ", поскольку 100,00 В + 99,99 В = -00,01 В. Ос-таток -00,01 показывает номер знаковойшины, а знак говорит о том, что по.- лярность текущего значения действующегосигнала в данном разряде противоположнаполярности входного сигнала. Такое распределение полярностей приводит к тому,что на двух входах шестого разряда,сигнал появится на противоположных по фазешинах, положительной и отрицательной.Это приведет к срабатыванию первогодвухвходового элемента И ЗЗ и сигналс его выхода через первый трехвходовыйэлемент ИЛИ 30, четвертый двухвходовой элементы И 25, первый трехвходовыйэлемент ИЛИ 29, четвертый двухвходовый элемент И 24 и первый трехвходовой элемент ИЛИ 23 поступает на второйвход трехвходового элемента И 19 и наего выход, следовательно, на выходе первого разряда появляется сигнал корректировки, который вводит поправку нв однуэнвчаюшую единицу в первый разряд цифрового преобразователя. В результате, нввходе первого разряда И иа выходе элемента И 19 сигнал исчезает, Поданный 35сигнал Ок =99,99 В превышает декадный интервал второго разряда на 9,99 В,что приводит к тому, что на входе второгоразряда появляется сигнал и по знаковой 40шине превышения декадного интервала,+Х" он поступает через второй трехвходовый элемент ИЛИ 39 на вйход второгоразряда, при этом информация в цифровомпреобразователе данного разряда из еня. ется иа единицу, т.е. фиксируется знак 159Аналогичным образом цо шине превышения декадного интервала+Х, черезвторой трехвходовый элемент ИЛИ 40,сигнал поступает нв выход третьего разряда, так же как и в четвертом разряде,В результате последовательных опера" ций в трех разрядах цифровой преобразователь зарегистрирует информацию 99,9 В. Разность входного сигнала; синтезирован- його в цифровом преобразователе, в пятом разряде сигнала появится нв знаковой шине "9", что приведет к появлению66487 10 1, Цифровой преобразователь параллельнопоследовательного следящего уравновешивания, содержащий входной блок, блок ввода поправок, а в каждом разряде амплитудный анализатор, соединенный выходом с управляющим входом делителя напряжения в каждом разряде, кроме последнего, отличающийся тем, что, с целью повышения точности, введены блок определения полярности, первый вход которого соединен с шиной сброса, а во все разряды, кроме первого и последнего, введены первый и второй переключатели полярности, в первый и последний разряды введены, соответственно, второй и первый переключатели полярности, при этом второй вход блока определения полярности подключен к выходу амплитудного анализатора последнего разряда и к перво " му входу последнего разряда блока ввода поправок, второй вход которого соединен с выходом блока определения полярности, входы каждого разряда блока ввода поправок, кроме последнего, подкшочены к выходам амплитудных анализаторов соответствующих разрядов, причем выход блока определения полярности соединен с управляющими входами всех переключателей полярности каждого разряда, входы первых переключателей полярности каждого разряда подключены соответственно к входам и выходам декадных делителей напряжения своего и предшествующего разрядов, а выходы соединены с вторыми входами амплитудных анализаторов соответствующих раэ. рядов, входы вторых переключателей полярности подключены к выходам соответствующих разрядов блока ввода поправок, в выходы соединены с третьими входами амплитудных анализаторов соответствую щих разрядов, причем первые входы всех амплитудных анализаторов подключены к .выходу входного блока.2, Преобразователь по п. 1, о т л ич а ю щ и й с я тем, что амплитудный анализатор выполнен на декадиочувствительном электроннолучевом знаковом ин дикаторе, первые три входа которого пМ ключены к соответствующим входам ампли 9 8 сигнала на однофаэных шинах всех входов разрядов, и ввод поправок прекратится.Использование предлагаемого изобретения позволяет повысить точность цифро. вых преобразователей параллельно-последовательного следящего уравновешивания. формула изобретения 5 10 15 го 25 зо 35 4 О 45 50 55 тудного анализатора, а знаковый выход соединен с входом блока усилителей, корректирующий выход эл".ктроннолучевого знакового индикатора через блок корректировки соединен с третьим входом электроннолучевого знакового индикатора,3. Преобразователь по и. 1, о т л ич а ю щ и й с я тем, что блок определения полярности содержит два элемента И и два триггера, нулевые входы которых соединены с первым входом блока определения полярности, а единичные входы, соответственно, подключены к выходам первого и второго элементов И, первые входы которых соединены со вторыми входами блока определения полярности, второй вход первого элемента И подключен к нулевому выходу триггера, а второй вход второго элемента И соединен с нулевым выходом первого триггера, единичные вхо. ды двух триггеров подключены к выходам блока определения полярности.4, Преобразователь по и. 1, о т л ич а ю щ и й с я тем, что первый разряд блока ввода поправок содержит девятивходовый элемент ИЛИ и трехвходовый элемент И, второй разряд содержит девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и три двухвходовых элемента И, остальные разряды, кроме двух последних, содержат девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и четыре двухвходовых элемента И, предпоследний разряд содержит девятивходовый элемент ИЛИ, двух и трехвходовые элементы ИЛИ и три двухвходовых элемента И, входы всех разрядов блока ввода поправок, кроме последнего, содержат ши ны знаков "1, 2", "3""9", при этом входы второго и всех последующих разрядов содержат шины положительной и отрицательной полярности текущего значения сигнала, а так же, за исключением последнего разряда, содержат шины положительного и отрицательного превышения декадного интервала и шину знака О,- второй вход последнего разряда содержит шины положительной и отрицательной полярности входного сигнала, входыдевятивходовых элементов ИЛИ каждого раз ряда подключены к соответствующим шинам знаков "1 "-9", в первом разряде выход девятивходового элемента ИЛИ соединен с первым входом трехвходового эле мента И, выход которого подключен к выходу первого разряда, третий вход - к ши . не знака О второго разряда, второй вход трехвходового элемента И первого разряда ы вторые входы третьих двухвхо2 6487 11 86 довых элементов И последующих разрядов соответственно соединены с входом первого трехвходового элемента ИЛИ второго разряда и с выходами четвертых двухвходовых элементов И своего разряда, за исключением предпоследнего разряда, в котором второй вход третьего элемента И подключен к выходу двухвходового элемента ИЛИ, первый и второй входы первого трехвходового элемента ИЛИ каждого разряда, кроме предпоследнего, соответственно соединены с выходами перво го и второго элементов И своего разряда, а в предпоследнем разряде первый и второй входы двухвходового элемента ИЛИ соответственно подключены к выходам первого и второго элементов И своего разряда, первые входы которых соответствен но соединены с шинами положительной и отрицательной полярности текущего значения сигнала последнего разряда, вторые входы первого и второго элементов И каждого разряда соответственно, подключены к шинам отрицательной и положительной полярности входного сигнала второго входа последнего разряда, выходы второго и последующих разрядов блока ввода поправок соединены с выходами вторых трехвходовых элементов ИЛИ соответствующих разрядов, первый и второй входы вторых трехвходовых элементов ИЛИ каждого разряда соответственно подключены к шинамотрицательного и положительного превышения декадного интервала своего разряда,а третий вход соединен с выходом третье го двухвходового элемента И своего разряда, первый вход которого подключен квыходу девятивходово 3 о элемента ИЛИсвоего разряда, а второй вход соединенс третьим входом первого трехвХодового 1 о элемента ИЛИ и с выходом четвертогодвухвходового элемента И своего разрядауза исключением предпоследнего разряда,в котором второй вход третьего двухвходового элемента И подключен ко второмувходу четвертого двухвходового элементаИ предшествующего разряда и, к выходудвухвходового элемента ИЛИ своего разряда, первый и второй входы четвертыхдвухвходовых элементов И каждого разряда соответственно соединены с шинамизнаков "0 и с выходами. первых трехвходовых элементов ИЛИ разряда. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР

СмотретьЗаявка

2825815, 04.10.1979

Заявитель Л. П. Петренко

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ

МПК / Метки

МПК: G01R 19/00

Метки: параллельно-последовательного, следящего, уравновешивания, цифровой

Опубликовано: 23.09.1981

Код ссылки

<a href="https://patents.su/9-866487-cifrovojj-preobrazovatel-parallelno-posledovatelnogo-sledyashhego-uravnoveshivaniya.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой преобразователь параллельно-последовательного следящего уравновешивания</a>

Предыдущий патент: Мост переменного тока для измерения индуктивности

Следующий патент: Устройство для определения центра видеоимпульса

Случайный патент: Гидравлический привод рабочего оборудования одноковшового экскаватора