Формирователь квадратурных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

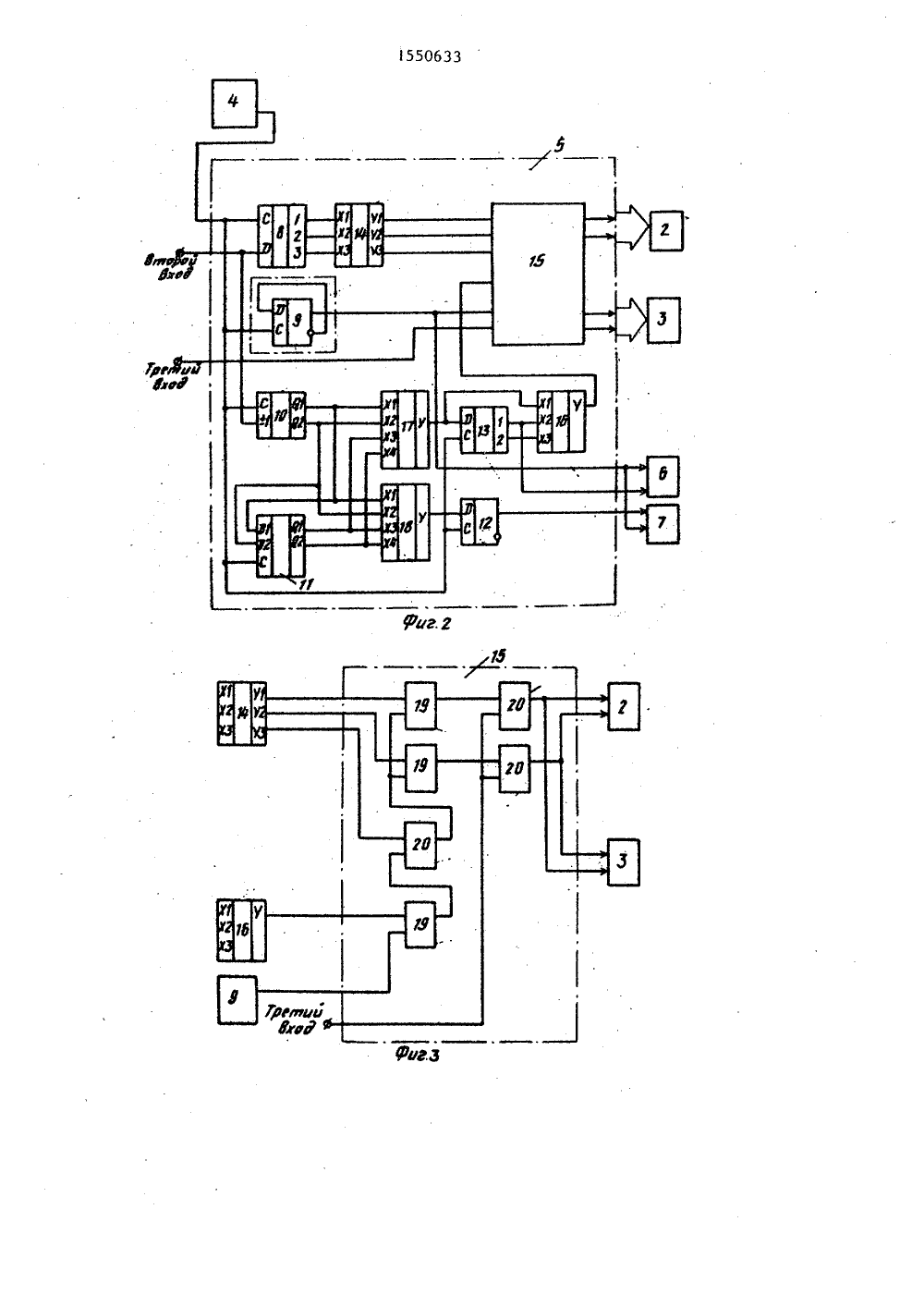

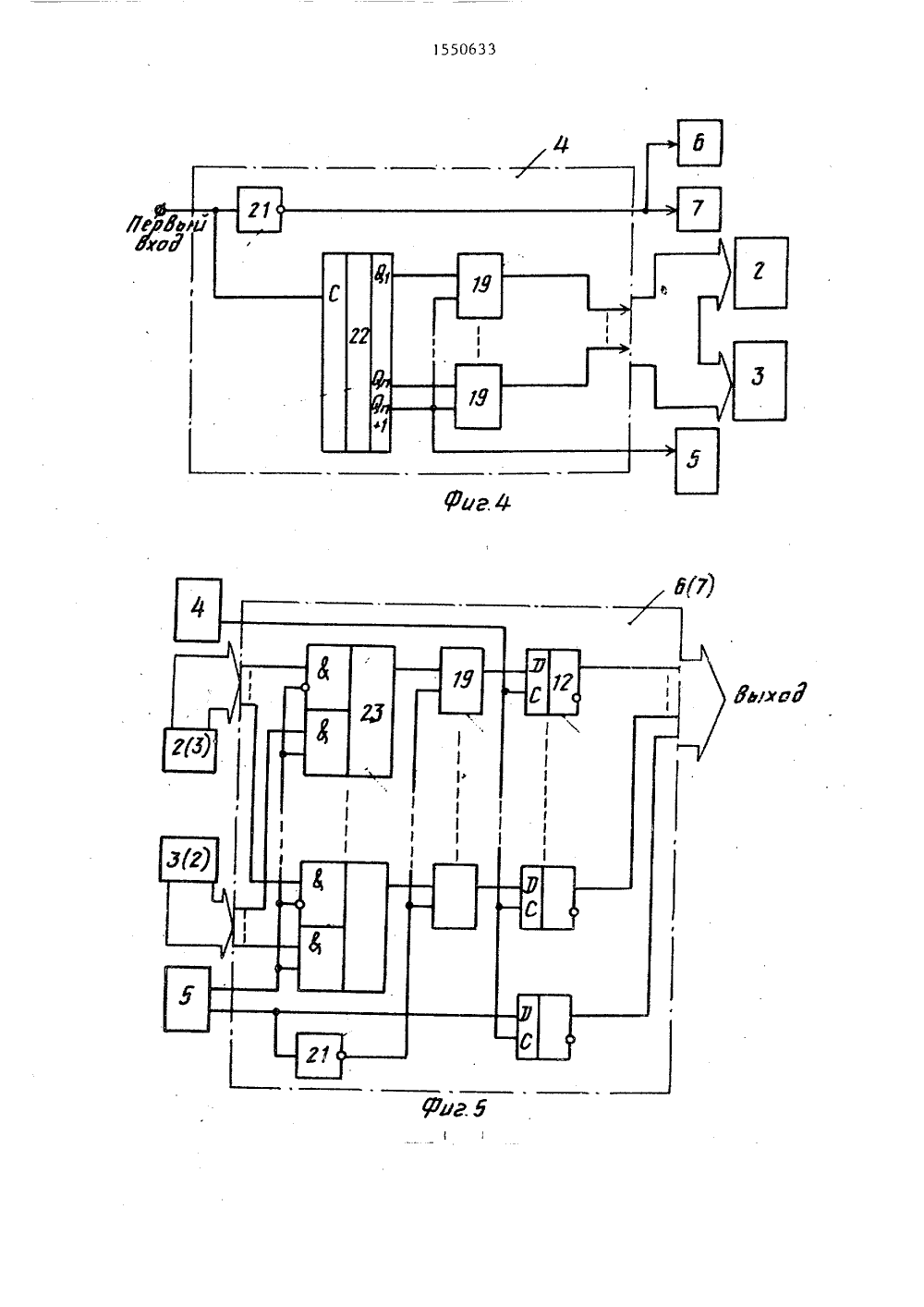

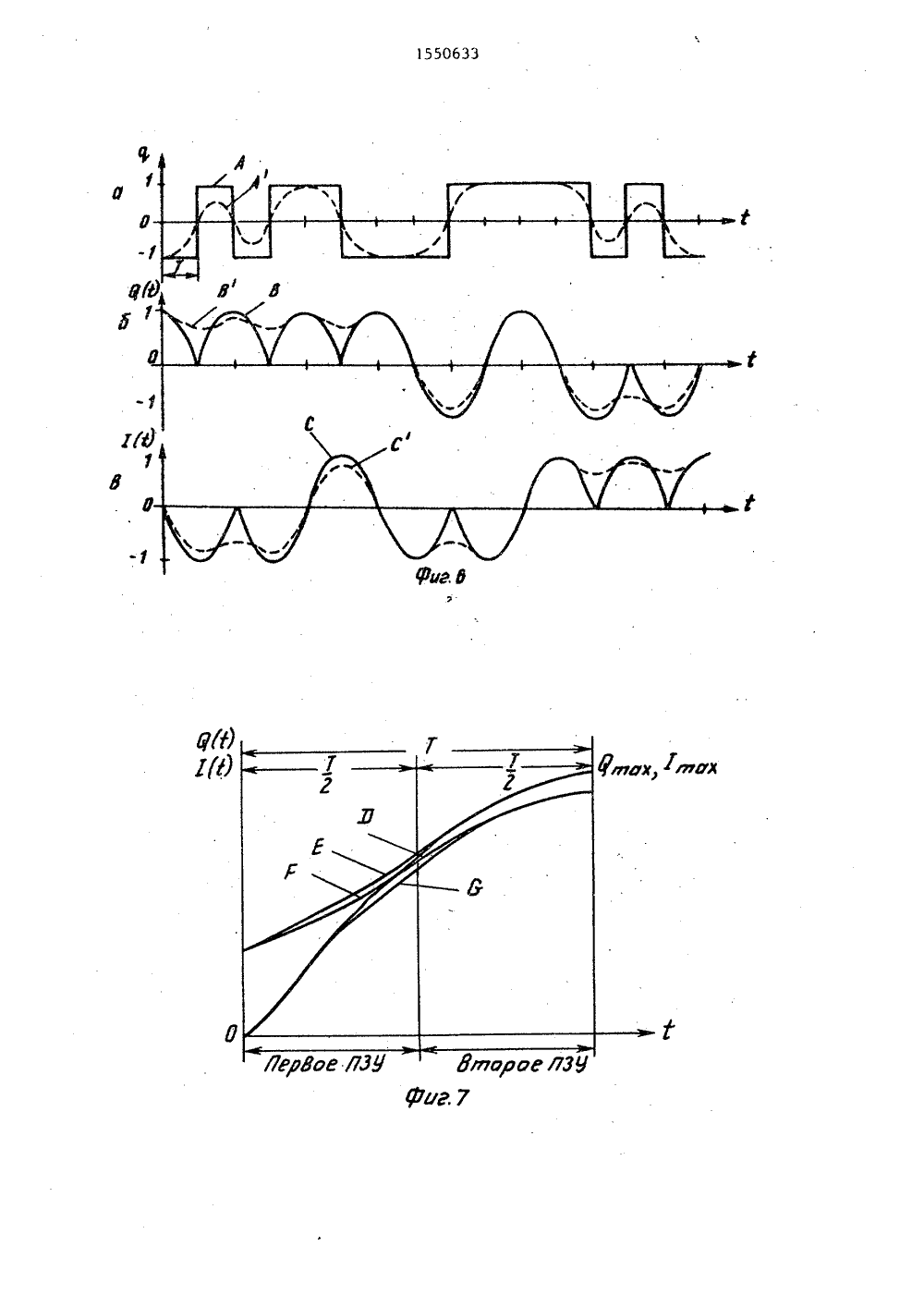

Изобретение относится к техйикесвязи и может использоваться при построении квадратурного типа передатчиков сигналов минимальной частотнойманипуляции с предмодуляционнойфильтрацией,Целью изобретения является повышение точности Формирования квадра"турных сигналов путем снижения уровня шумов квантования при одновременном уменьшении объема записи постоянных запоминающих устройств.На фиг. 1 приведена структурнаяэлектрическая схема Формирователя;на фиг, 2 - схема блока управления;на фиг. 3 - схема бКока коммутации;на фиг. 4 - схема блока опорных частот; на Фиг. 5 - схема мультиплексора; на фиг. 6 - диаграмма входных и 20соответствующих квадратурных сигналов; на Фиг. 7 - возможные траектории Формируемых сигналов на интервале манипуляции; на фиг, 8 - временные диаграммы, поясняоцие работу блока управления.формирователь содержит блок 1считывания, первое 2 и второе 3 постоянные запоминающие устройства (ПЗУ).блок 4 опорных частот, блок 5 управ- З 0ления, первый 6 и второй 7 мультиплексоры. Блок 4 опорных частот содержит первый 8 регистр сдвига, делитель 9 частоты на два, реверсивныйсчетчик 10, параллельный регистр 11,О-триггер 12, второй регистр 13 сдвига, дешифратор 14 кода траектории,блок 15 коммутации, дешифратор 16смены знака косинуса, дешиФратор 17знака косинуса, дешиФратор 18 знака 40синуса, Блок 15 коммутации содержитэлемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и элемент2 И 20. Блок 4 опоРных частот содержит элемейт ИСКЛЮЧАЮЩЕЕ ИЛИ 19 элемент НЕ 21 и двоичный счетчик 22. 45Мультиплексоры 6 и 7 содержат 0-триг. геры 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19,элемент НЕ 21 и элемент И-ИЛИ 23.формирователь квадратурных сигналов работает следующим образом.На первый вход Формирователя поступает сигнал дискретизации с частотой иР , где Р = 1/Т; Т - тактовыйинтервал; и - количество отсчетовзначений Формируемых квадратурныхсигналов (Фиг. 8 б). На второй входформирователя поступает информационный сигнал в виде логицеских "0" и"1" длительностью, равной Т (Фиг.8 а) . На третий вход формирователя постоянно подается либо логическая "1", лиЬо логический "0".С блока 4 опорных частот на младшие адресные входы ПЗУ 2 и ПЗУ 3 поступают сигналы считывания отсчетов значений Формируемых квадратурных сигналов, записанных в ПЗУ в виде двоичного в-разрядного кода. На старшие адресные входы ПЗУ 2 и ПЗУ 3 с блока 5 управления поступают сигналы считывания, определяющие тип формируемой траектории П, Е, Р, С на интервале Т (фиг. 7). Управляющие сигналы с блока 5 управления (Фиг. 8 в, г, д) по-. ступают на мультиплексоры 6 и 7, производя их переключение (фиг. 8 в) и пропуская сигналы с ПЗУ 2 через мультиплексор 6, с ПЗУ 3 через мультиплек. сор 7, либо с ПЗУ 2 через мультиплексор 7 и с ПЗУ 3 через мультиплексор 6, а также производя инвертирование (см фиг, 8 г, д) поступающих с ПЗУ 2 и ПЗУ 3 сигналов и Формируя старшие ,разряды сигналов.На входы синхронизации мультип лексоров 6 и 7 поступает инверсный" сигнал дискретизации для стробирования выходных сигналов, представленных двоичным а-разрядным кодом с целью одновременной смены состояний этих сигналов.При подаце на первый вход Формиро вателя сигналов дискретизации начинает раЬоту двоичный счетчик 22 с разрядностью и+1 в блоке 4 опорных частот, Выходной сигнал счетчика инвертируется при появлении состояния логической "1" на выходе (и+1)-го разряда двоицного счетчика 22 при помощи элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19, Таким образом, на первые групповые входы ПЗУ 2 и ПЗУ 3, представляющие собой младшие адресные входы, непрерывно поступают сигналы с блока 4 опорных частот в виде двоичного кода, меняющен 11" до "00", перебирая адреса ПЗУ в прямом и затем в обратном порядке. Это приводит к появлению на выходах ПЗУ 2 и 3 сигналов в виде двоичного ш-разрядного кода записанных в ПЗУ отсчетов значений сигналов одного из четырех типов траекторий О, Е, Р, С (Фиг, 7) на одном тактовом интервале, из которых формируются квадратурные сигналы ч(с) и т.(с) (фиг, 6 Ь, в, траектории В и С ), 5 1 Ясоответствующие входному информационному сигналу, пропущенному черезпредмодуляционный Фильтр (Фиг. 6 а,траектория А ),Отсчеты значений Формируемых квадратурных сигналов записаны в каждомИЗУ 2 и ИЗУ 3 следующим образом.: впервом ИЗУ 2 записаны отсчеты значений сигналов, соответствующие траекториям О, Е, Р, С на первой половиТне тактового интервала -;-, причемменьшие значения записаны начиная снулевого адреса; во второе ИЗУ 3 записаны отсчеты значений сигналов, соответствующие траекториям Б, Е, Р,С на второй половине тактового инТтервала;, причем большие значениязаписаны с нулевого адреса. Вид траектории на Фиг. 7 определяется старшими адресными входами ПЗУ, представляющими собой второй групповой вход.Траектории Р соответствует поступающий на старший адресный вход сигналдвоичного кода "00", траектории Е"10", траектории С - "01" и траектории Р - "11", Поскольку квадратурныесигналы повторяют свои значения соТсдвигом во времени на интервал -, тотакая запись значений сигналов в ПЗУ,а также введение двух дополнительныхмультиплексоров 6 и 7, передающих навходы отсчеты значений сигналов либос первого ИЗУ 2, либо со второго ПЗУ3, позволяют обойтись минимально. возможным количеством отсчетов значенийу,=(х,+ х,+ х,) + (х, х, х); х, (х,+х+ ) (,+,+х),3 1 г 10 где 1 1 гсалы на выходдешифратора;Х Хг, Х- сигналы на входахдешифратора.Сигналы с выхода дешифратора 14 кодатраектории (Фиг8 ж, з, и) через блок15 коммутации (фиг. 3) поступают на 20 вторые групповые входы ПЗУ 2 и ПЗУ 3(Фиг. Як). Каждый Ьит информационногосигнала дает приращение Фазы сигналовминимальной частотной манипуляции на+90 или -90 ф. Знак квадратурных сос таеляющих определяется набегом фазы./1 еухразрядный реверсивный счетчик 10имеет четыре состояния, имеющие следующее соответствие: "00" - О , "01.н90, ф 10 н - 180, "11 н - 270 . Счет 30 вперед или назад определяет этот набег Фазы. Дешифраторы знаков косинуса 17 и синуса 18 определяют знакиквадратурных сигналов, используя текущее состояние реверсивного счетчика 10 и предыдущего состояния, записанного е параллельный регистр 11,Работа дешифратора 17 знака косинуса описывается следующим выражениембулевой алгеЬры: 15 06336от состояния трех бит информационного сигнала, последовательно записанных в первый регистр 8 сдвига, 5Работа дешифратора 14 описываетсяследующим выражением булевой алгебры:(3) Сигналы с выходов дешифратора зна"ка синуса 18 и косинуса 17 задерживаются на один тактовый интервал в В- триггере 12 и втором регистре 13 сдвига, так как время задержки всех управляющих сигналов должно быть одинаковым. сигнала.Какие именно отсчеты значений сигналов считывать в данный момент времени, определя ет блок 5 уп ра вления,работающий следующим образом,На тактовый вход Ьлока 5.управления поступает сигнал тактовой частоты с выхода (п+1)-го разряда двоичного счетчика 22 блока 4 опорных частот, по фронту которого происходятвсе переключения в блоке 5 управления, На информационный вход блока 5управления поступает информационныйсигнал е виде логических "О" и "1"длительностью Т (Фиг, Ва). Этот сигнал записывается в первый сдвигающийрегистр 8 и поступает на вход управления реверсивного счетчика 10. Дешифратор 14 кода траектории позволяетвыбрать код траектории е зависимости т.= (х,+ х,+ х,) (х,+ х,+ х,), (2) где Х Х, Х, Х - сигналы на входахдешифратора;У - сигнал на выходедешифратора .Работа деиифратора 18 знака синусаописывается следующим выражениембулевой алгебры:6 и г налы с выхода 1)-т ри гг ера 12 и первого выхода параллельного регистра 13 (Фиг. Вг, д) поступают.на входы мультиплексоров 6 и 7, где они оп ределяют знак формируемого сигнала, производя инвертирование двоичного кода отсчетов значений сигналов, записанных в ПЗУ 2 и ПЗУ 3 и поступающих на групповые входы мультиплексо ров 6 и 7, Одновременно они являются старшими разрядами записанных в ПЗУ отсчетов значений сигналов, что позволяет не ваписывать их в ПЗУ.Траектории Б и Р (фиг. 7) исполь 15 зуются для Формирования квадратурного и синфазного сигналов одновременно. Если для Формирования квадратур- ного сигнала используется траектория Е, то для Формирования синфазного сигнала используется траектория С, и наоборот, Какая именно траектория Е и С используется для Формирования квадратурного и соответственно синФазного сигналов, определяется де шифратором 16 смены знака косинуса, на который поступает сигнал с второго регистра 13 сдвига. Если знак косинуса меняется на протяжении трех тактовых интервалов, то сигнал с вы хода дешифратора 16 смены знака косинуса (Фиг, 8 е), поступающий на блок 15 коммутации, не производит инверсию кода траектории при помощи элементов ИСКЛЮЧИ)ЩЕЕ ИЛИ 19 в Ьлоке коммутации 15 (Фиг. 3). Инверсии не происходит, если для Формирования квадратурных сигналов используются траектории Б и Г. По сигналу с выхода У (Фиг, 8 и) дешифратора 14 кода тра ектории сигнал с выхода дешифратора 16 смены знака косинуса блокируется при помощи элемента 2 И 20 (Фиг. 3),Работа дешифратора 16 смены знака косинуса описывается следующим выра жением булевой алгебры:(4)где Х Х, Хсигналы на входах 50фдешифра тора;У - сигнал на выходе дешифратора.Сигнал с выхода делителя 9 часто,ты на два (Фиг. 8 в) производит пере 1 ключение мультиплексоров. По состоянию логического "0" мультиплексор 6 пропускает сигнал с ПЗУ 2, мультиплексор 7 - с ПЗУ 3, по состоянию логической "1" мультиплексор 6 пропускает сигнал с ПЗУ 3, а мультиплексор 7 - с ПЗУ 2. Если в этот момент Формирование сигналов происходит при помощи траекторий Е и С, то коды траекторий, поступающие на ПЗУ 2 и ПЗУ 3, необходимо поменять местами на время переключения мультиплексора, Это происходит при помощи инвертирования сигнала с выхода дешифратора 16 смена знака косинуса на элементе ИСКЛЮЧИВ,ЕЕ ИЛИ 19 в блоке 15 коммутации по сигналу с выхода делителя 9 частоты на два. На третий вход Формирова-. теля квадратурных сигналов на блок 15 коммутации поступает сигнал блокировки в виде логического "0"Код траектории блокируется на элементах 2 И 20 (Фиг. 3), на выходе которых устанавливается состояние "0", что соответствует коду траектории Р, т.е. чистой синусоиде. При этом Формирователь формирует квадратурные сигналы, соответствующие входному информационному сигналу без предмодуляционной фильтрации (Фиг, ба, кривая А). Для того, чтобы смена состояний двоичного кода на выходах Формирователя квадратурных сигналов была одновременной, в мультиплексорах 6 и 7 используются В-триггеры 12 (Фиг. 5), на тактовые входы которых поступает сигнал синхронизации с блока 4 опорных частот, пред-. ставляющий собой проинвертированный на элементе НЕ 21 сигнал частоты дискретизации, поступающий на первый вход Формирователя квадратурных сигналов. Сигналы с выходов 0-триггеров 12 (Фиг. 9) являются выходными сигналами Формирователя квадратурных сигналов, поступающими далее на цифроаналоговые преобразователи (фиг. 1),формула изобретения1. Формирователь квадратурных сигналов, содержащий блок считывания, первый и второй входы которого являются соответственно тактовым и инФормационным входами формирователя, и первое и второе постоянные запоминающие устройства, о т л и ч а ю щ и йс я тем, что, с целью повышения точности Формирования квадратурных сигналов путем снижения уровня шумов квантования при одновременном уменьшении объема записи постоянных запоминающих устройств, введены первый и9 155063 второй мультиплексоры, выходы которых ,являются выходами формирователя, а блок считывания содержит последовательно соединенные блок опорных частот и блок управления, третий вход5 блока счит ыва ния я вляется входом управления Формирователем, первый и второй выходы устройства считывания соединены соответственно с первым и вторым входами первого и второго мультиплексоров, третий и четвертый выходы устройст ва сцитыва ния подключены к третьему входу соответственно первого и второго мультиплексоров, 15 первая группа выходов устройства считывания соединена с первыми группами входов первого и второго постоянных запоминающих устройств, вторая и третья группы выходов устройства сцитыва- Ю ния подключены к второй группе входов соответственно первого и второго постоянных запоминающих устройств, выходы которых соединены с первыми и вторыми группами входов первого и второ го мультиплексоров, первый, второй и третий входы устройства считывания являются соответственно входом блока опорных частот, вторым и третьим входами блока управления, первый, вто рой, третий и четвертый выходы устройства считывания являются соответственно вторым выходом блока опорных частот, первым, вторым и третьим выхода,ми блока управления,а первая, вторая и третья грчппы выходов устройства считывания являются соответственно группой выходов блока опорных частот первой и второй группой выходов блока управления. 402, Формирователь по и. 1, о т л и" ч а ю щ и й с я тем, что блок управления содержит последовательно соединенные первый регистр сдвига, дешиф 310ратор кода траектории и блок коммутации, делитель частоты на два, после" довательно соединенные реверсивный счетчик, дешифратор знака косинуса, второй регистр сдвига и дешифратор смены знака косинуса и последовательно соединенные параллельный регистр, дешифратор знака синуса и Р- триггер, выход которого является третьим выходом блока управления, тактовый вход первого регистра сдвига соединен с входом делителя частоты на два, с тактовыми входами реверсивного счетчика, параллельного регистра, П-триггера и второго регистра сдвига и является первым входом блока управления, информационный вход первого регистра сдвига соединен с входом управленияя счетом реверсивного счетчика и является вторым входом блока управления, первый управляющий вход блока коммутации является третьим входом блока управления, выход дели" теля частоты на два соединен с вторым управляющим входом блока коммута" ции и является первым выходом блока управления, выход дешифратора знака косинуса подключен к другому входу дешифратора смены знака косинуса, выход которого соединен с третьим уп" равляющим входом блока коммутации, первый выход второго регистра сдвига является вторым выходом блока управления, выходы реверсивного счетчика соединены с другими входами дешифратора знака синуса и с соответствующими инФормационными входами параллельного регистра, выходы которого подключены к соответствующим входам дешифратора знака косинуса, а первая и вторая группы выходов блока коммутации являются соответственно первой и второй группами выходов блока управления.ставитель И. КотикохреА Л,Олийнык ректор Н. Ревс Н. Ывыдкая РеЛ аз 279 Тираж 524 ПНИИПИ Государственного комитета по изобретения 1 13035, Москва, Ж, Раушская писное и ГКНТ СС и открытия б д. 4/5 В Гагарина, 1011Производственно"издательский комбинат Патент , г, Ужгоро

СмотретьЗаявка

4351897, 28.12.1987

ОРГАНИЗАЦИЯ ПЯ М-5222

ФИЛАТОВ ВИТАЛИЙ ДМИТРИЕВИЧ, ПИСАРЕВ СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/12

Метки: квадратурных, сигналов, формирователь

Опубликовано: 15.03.1990

Код ссылки

<a href="https://patents.su/9-1550633-formirovatel-kvadraturnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь квадратурных сигналов</a>

Предыдущий патент: Устройство для обучения радиотелеграфистов

Следующий патент: Устройство для частотной манипуляции

Случайный патент: Устройство автоматического управления кольцевой слиткоподачей блюмингов и слябингов