Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

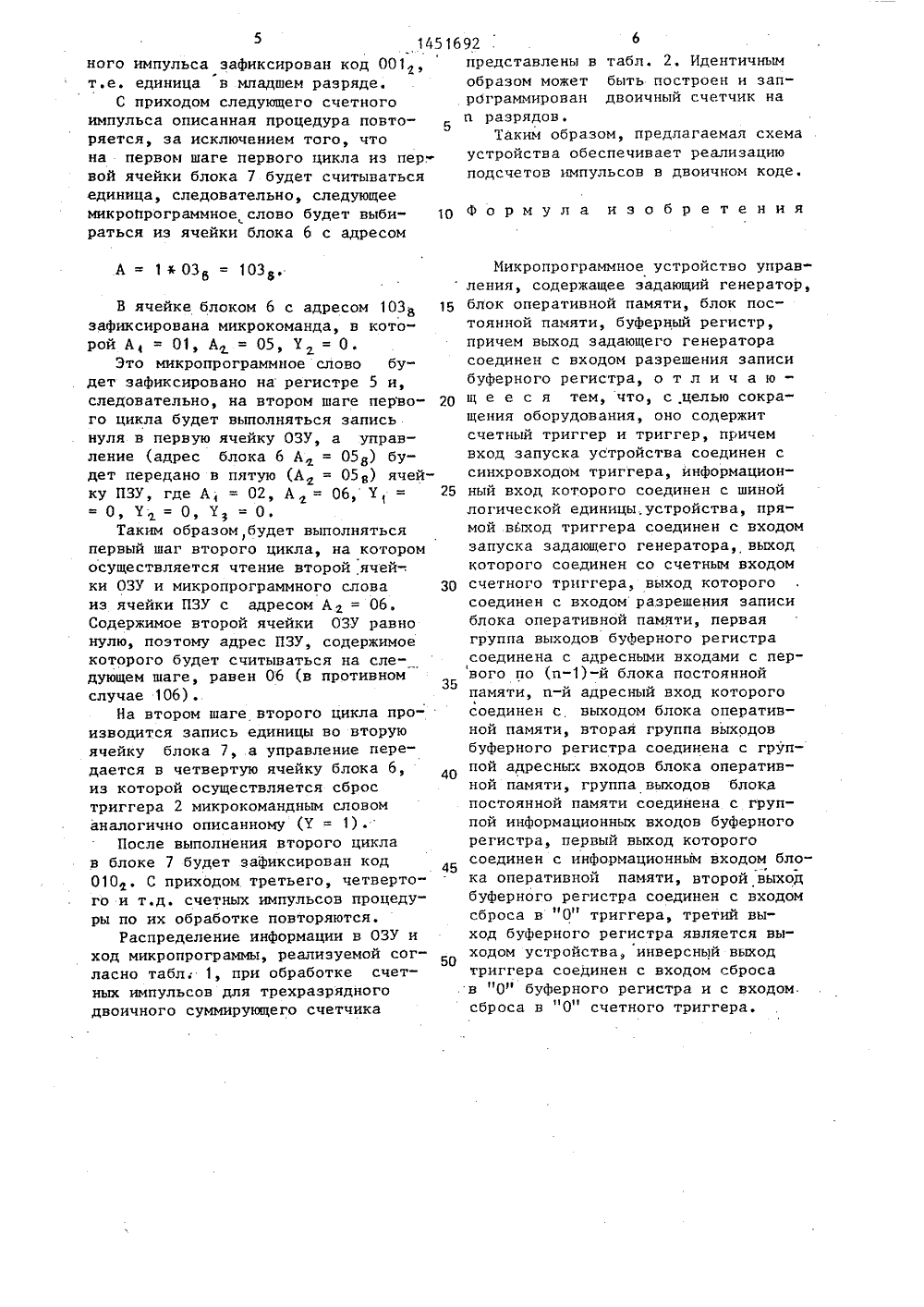

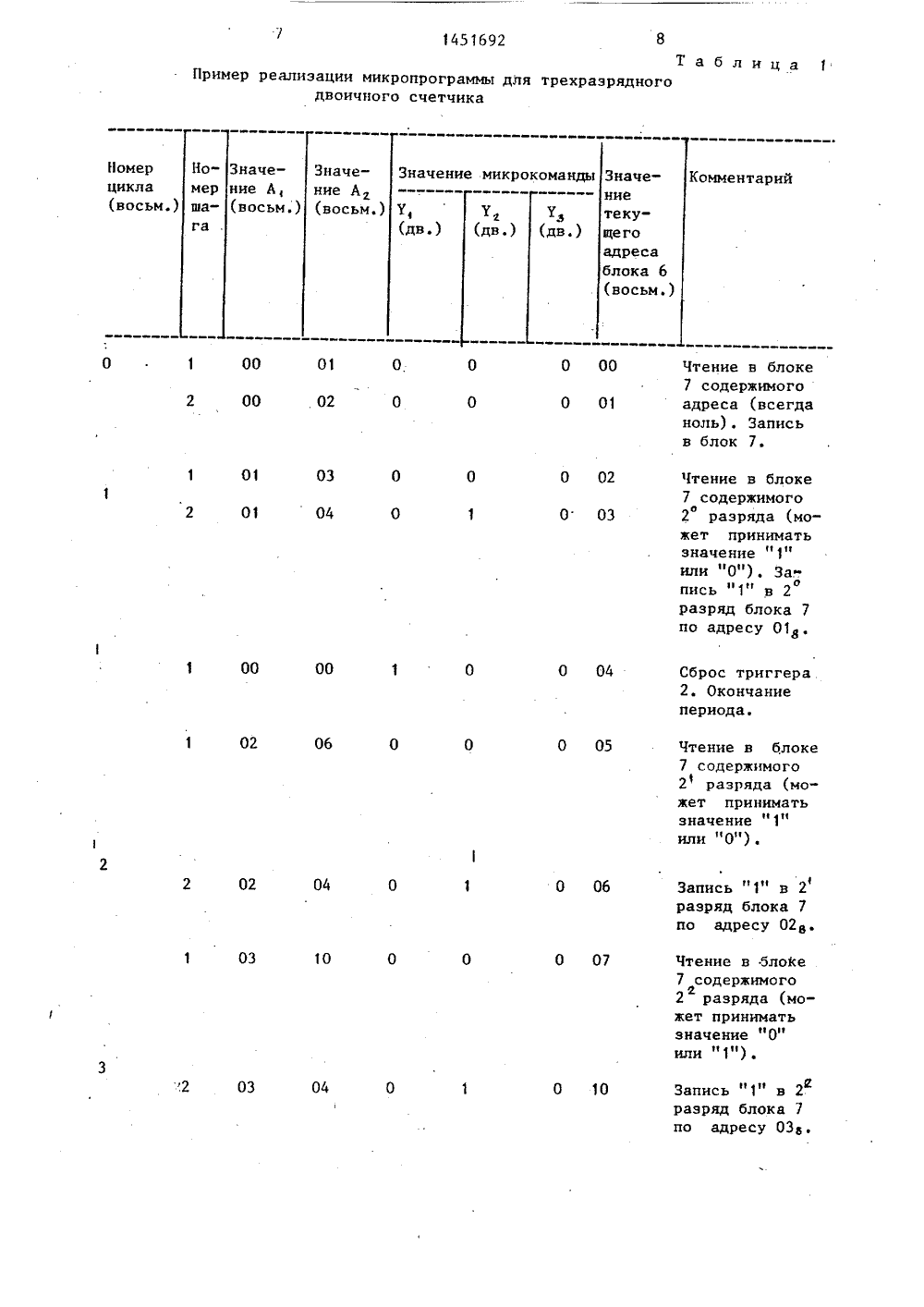

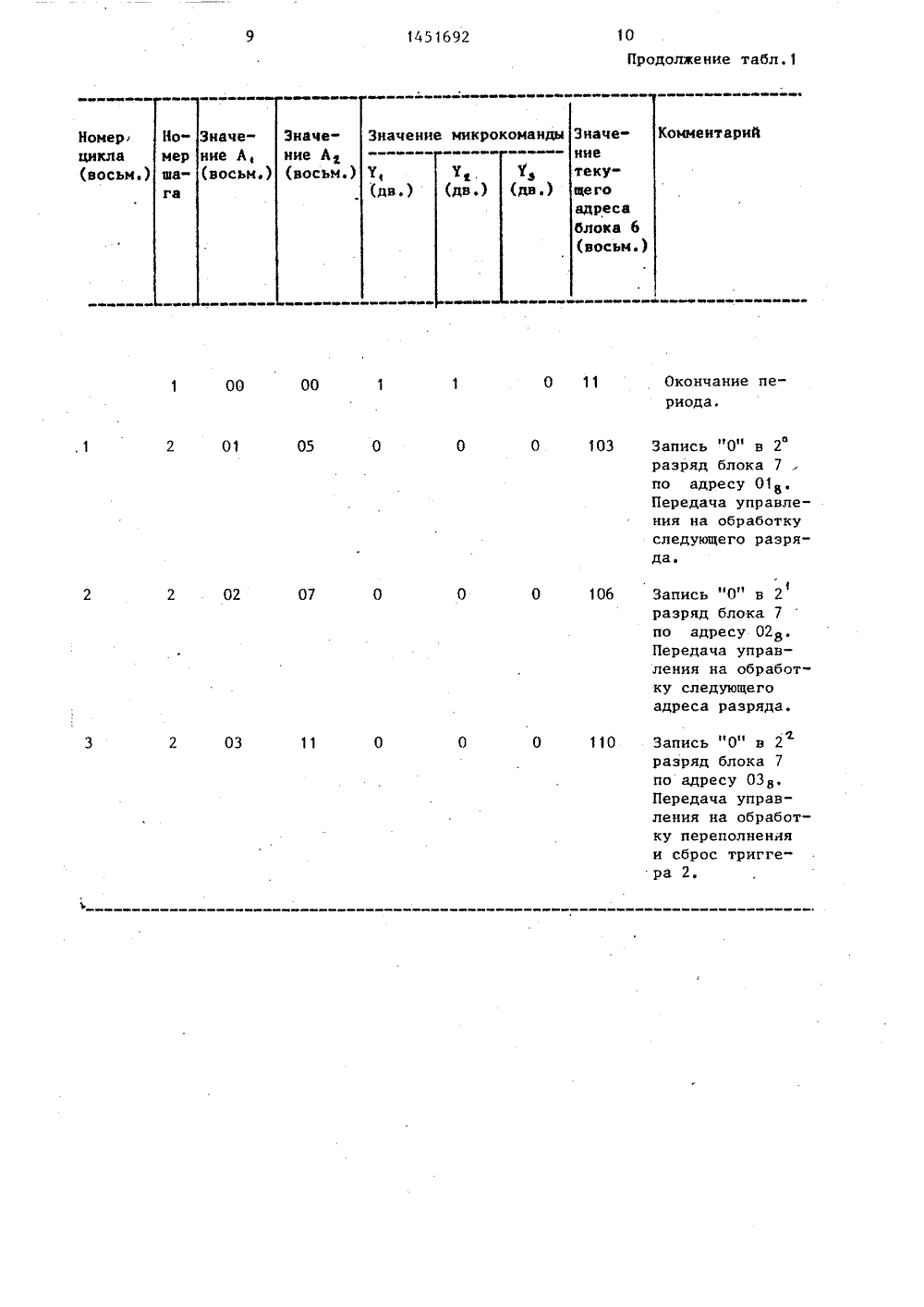

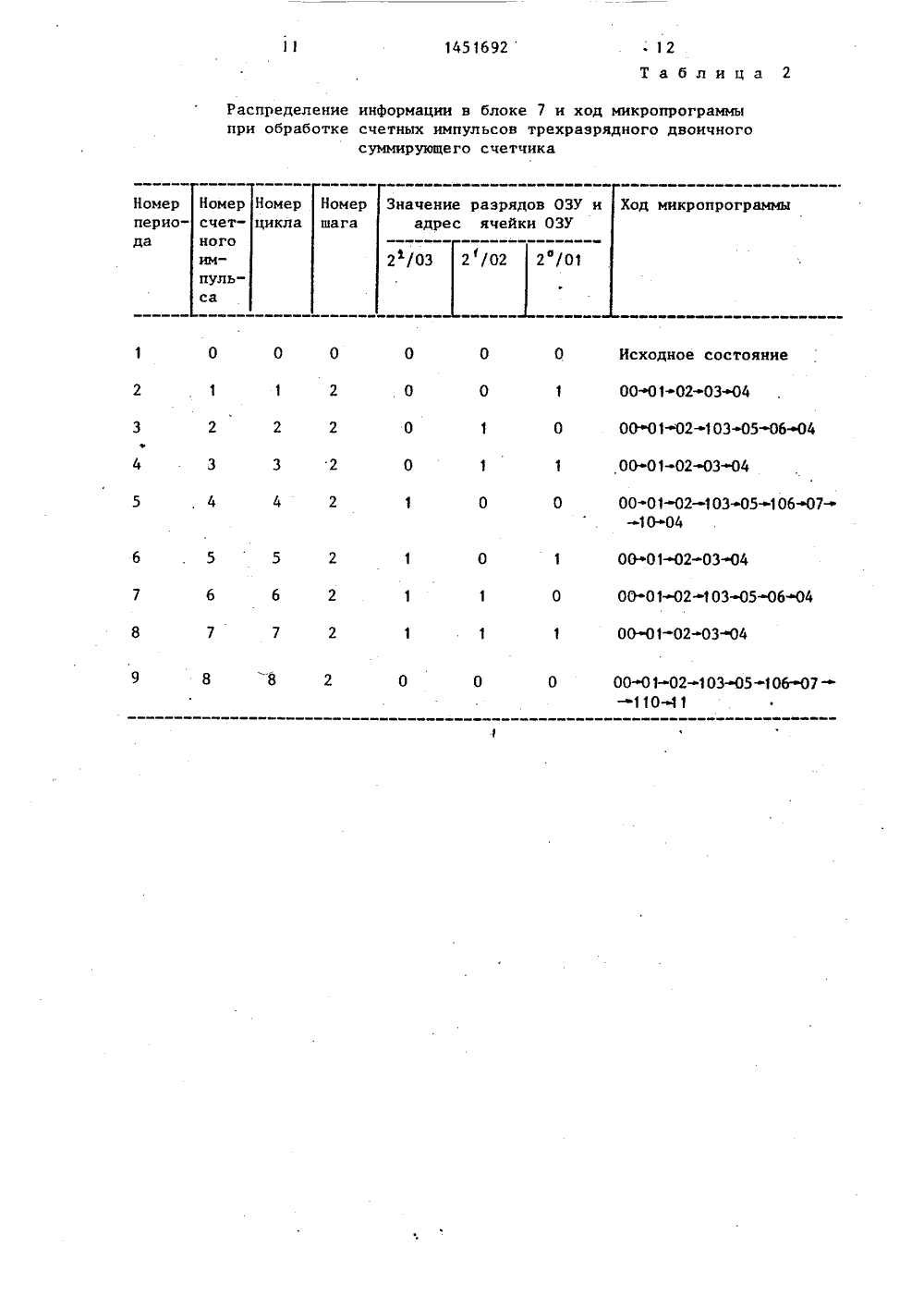

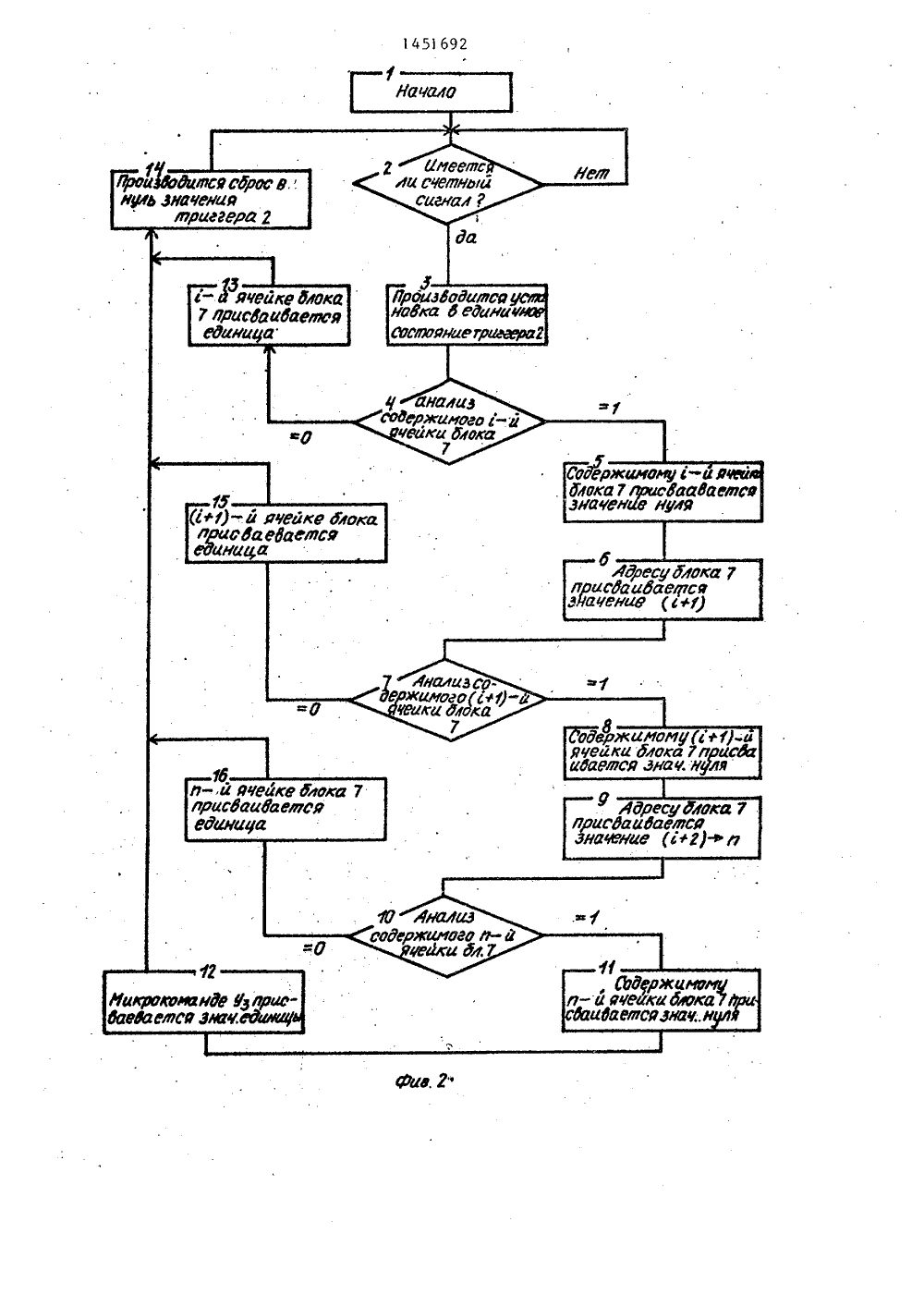

(191 (111 И 4 С 06 Г 9 ЯПОЕ УСТРОЙСТВО 24-2 относится к обласехники и может У 2В.Глонти Бюл его, В.В,К 088.8 е сви С 06 етельство СС Р 9/22, 1970 ельство СССР Г 9/22, 198 виде С 0 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОП(РЫТИЯПРИ ГКНТ СССР Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Изобретениевычислительнойбыть использованпрограммного упрпрограммными цикния - сокращениеройство содержитгенератор 3, счебуферный регистрной памяти, блокмяти. Устройстволизацию подсчетаном коде. 3 ил.,о в устроиствах авления с длительным лами. Цель изобретеоборудования. Уст" триггер 2, задающий тный триггер 4, 5, блок 6 постоян оперативной паобеспечивает реаимпульсов в двоич табл.Изобретение относится к вычислительной технике и может быть использовано в устройствах программного управления с длительными программны ми циклами.Цель изобретения - сокращение оборудования.На фиг. 1 представлена функциональная схема устройства, на фиг,2 - 10 обобщенный рабочий алгоритм устройствау на фиг, 3 - временные диаграммы, поясняющие работу устройства.Устройство содержит вход 1 запуска, триггер 2, задающий генератор 15 3, счетный триггер 4, буферный регистр 5, блок б постоянной памяти, блок 7 оперативной памяти и выход 8.Устройство работает следующим образом. 20Устройство работает по принципу микропрограммного счетчика. После поступления сигнала на вход 1 устройства триггер 2 устанавливается в единичное состояние (операторы 2 и 25 3, фиг. 2) . Затем производится анализ состояния соответствующего разря" да счетчика. Так как все разряды счетчика упакованы в соответствующие биты (ячейки) блока 7, причем каждо- .30 му такому биту блока 7 соответствуют определенный адресный код блока 7, то анализ состояния соответствующего разряда счетчика выливается в анализ содержимого соответствующего бита блока 7.Анализ производится для определения сигнала переноса в более старший по отношению к анализируемому разряд счетчика, При этом если анализируемый разряд счетчика (соответствующий бит) блока 7 равен единице, то он обнуляется, анализируется следующий разряд. Последовательность этихдействий повторяется до тех пор, пока не встречается разряд с нулевым значением, при этом ему присваивается значение единицы и анализ прекращается. Если все разряды счетчика за время предыдущего счета были установлены в единичное состояние, то все они в соответствии с описанной процедурой анализа и в соответствии с операторами 4-11 (фиг. 2) обнуляются, а микрокоманде переполнения разрядной сетки присваивается единичное значение.Из алгоритма работы устройства видно, что последовательность действий, составляющая алгоритм, регулярна и циклична. При этом процедуру счета можно условно разбить на следующие этапы: период, цикл и шаг.Под периодом будем понимать все действия (операции), связанные с отработкой счетного сигнала.Период разбивается на циклы, во время действия которых производится анализ состояния соответствующего разряда счетчика и определение переноса в более старшйй (1-й) разряд счетчика.Период разделен шагами, на каждом периоде выполняются два шага; считывание информации из ОЗУ и запись информации (нуля и единицы) в ОЗУ по соответствующему адресу.Рассмотрим работу устройства более подробно.Исходное состояние функциональных элементов устройства в момент его включения может быть любым, однако для простоты описания будем считать его кулеви.Нулевое состояние устройства характеризуется нулевым состоянием триггера 2, счетного триггера 4, разрядов буферного регистра 5 и нулевым значением содержимого ячеек блока 7 оперативной памяти. Это означает, что на выходах этих элементов - низкий потенциал (нулевой потенциал) .Таким образом, в начальный момент времени на адресные входы блока 7 и блока б поданы нулевые значения адресных кодов, на управляющий вход блока 7 подан нулевой потенциал, что означает режим записи нулевой информации,Для управления режимом работы блока 7 принимается:для режима чтения ячейки блока 7 с соответствующим адресом - высокий потенциал на управляющем входе,для режима записи информации в ячейку блока 7 соответствующим адресом - низкий потенциал на управляющем входе, при этом в ячейку производится запись единицы, если информационный вход равен единице, и нуля, если информационный вход равен нулю. По переднему фронту счетного сигнала, поступающего на синхровход триггера 2, последний устанавливается в единичное состояние,А = 0 + САсРз145Единичным сигналом с прямого выхода триггера 2 запускается генератор 3 опорной частоты.С задержкой относительно переднего фронта запускающего сигнала генератор 3 опорной частоты генерирует (формирует) импульсную последовательностьЗапускающий сигнал (от триггера 2) и последовательность задающего генератора 3 сфазированы таким образом, что по переднему фронту запус.кающего сигнала формируется передний фронт опорной частоты (фиг. Зб, в).Импульсы опорной частоты поступают на счетный вход триггера 4, который формирует меандровую (со скважностью 2) последовательность импульсов (фиг. Зг), период которой определяет цикличность работы устройства. При этом эа положительный полу- период выполняется первый шаг - чтение информации из соответствующей ячейки блока 7. За отрицательный полупериод выполняется второй шаг - запись информации в соответствующую ячейку блока 7. Соответствующие адреса блока 7(адресные коды) и блока 6 Формируются (выбираются) из блока 6 через буферный регистр 5,Адресация блоков 7 и 6 построенатаким образом, что на каждый сформированный адрес блока 7 формируютсядва адреса блока 6 (табл. 1) .Адресация блока 6 осуществляетсягруппой и строится таким образом,что в каждой текущей (выбираемой)ячейке блока 6 фиксируется адресследующей ячейки. Например, в нулевой ячейке (табл. 1) зафиксированадрес первой (018), в первой - адрес028, во второй - адрес 038 и т.д.,Выбираемая иэ блока 6 информацияфиксируется передним фронтом импуль"сов опорной частоты на буферном .Регистре 5 (фиг. Зд, е).Тогда в начальный момент времени(определим его как нулевой цикл)полный адрес (А) ПЗУ всегда равен где ( Ар 1пзу- содержимое нулевойячейки ПЗУ.На первом шаге нулевого цикла осуществляется чтение нулевой ячейки 16 С 2ОЗУ и нулевой ячейки ПЗУ. Управлениеперерается на первую ячейку ПЗУ (А == 01 в)На втором шаге нулевого циклапроизводится запись нуля в нулевуюячейку ОЗУ (У = 0), управление передается на вторую ячейку ПЗУ (А == 02 в)10 Нулевой цикл выполняется для того, чтобы вывести счетчик из исходного состояния. Нулевой цикл является холостым, а работа счетчика начинается с первого цикла.1 Б На первом шаге первого цикла про-.изводится чтение первой ячейки блока7, что соответствует содержимомуопервого (2 ) младшего разряда счетчика. При этом на адресный вход бло 20 ка 7 подается код 01, а на адресныйвход блока 6 подается код 028, зафиксированные на регистре 5 в нулевомцикле,Под действием этих кодов из пер 25 вой ячейки блока 7 считывается нуль;второй ячейки блока 6 считывается содержимое микропрограммного слова, вкотором (табл. 1) А, 01, А = 038,У, = О, У = О, Уэ = О, тогда с при-,ходом переднего фронта очередногоимпульса это микрокомандное словозафиксируется на регистре 5.На втором шаге первого цикла в35первую ячейку ОЗУ заносится (записывается) единица, так как А= 01 ви У, = 1 зафиксированы на регистре5 и подаются на ОЗУ.На этом же шаге производится счи 40 тывание из третьей ячейки ПЗУ (таккак А = 03) микропрограммного слова,вкотором А, = 01, А = 04 У = О,У = 1; У = О. Эта информация будетзафиксирована на регистре 5 перед 45 ним ФРонтом следующего импульсаопорного сигнала.Таким образом, на следующем шагевыбирается содержимое четвертойячейки блока 7, в которой зафиксиро 50вана микрокоманда 71 = 1, осуществляющая сброс в "0" триггера 2(фиг. 2). Высоким потенциалом сигнала инверсного плеча триггера 2 сбрасывается в "0" содержимое триггера4 и буферного регистра 5.55 Устройство приведено в исходноесостояние за исключением блока , вкотором после обработки одного счет5 1451 ного импульса зафиксирован код 001, т.е. единица в младшем разряде.С приходом следующего счетного импульса описанная процедура повто ряется, за исключением того, что на первом шаге первого цикла из пер.- вой ячейки блока 7 будет считываться единица, следовательно, следующее микропрограммное, слово будет выби раться из ячейки блока 6 с адресом 692 6представлены в табл. 2. Идентичным образом может быть построен и эапрдграммирован двоичный счетчик на и разрядов.Таким образом, предлагаемая схема устройства обеспечивает реализацию подсчетов импульсов в двоичном коде. формула изобретенияМикропрограммное устройство управ ления, содержащее задающий генератор, блок оперативной памяти, блок постоянной памяти, буферный регистр, причем выход задающего генератора соединен с входом разрешения записи буферного регистра, о т л и ч а ю - щ е е с я тем, что, с целью сокращения оборудования, оно содержит счетный триггер и триггер, причем вход запуска устройства соединен с синхровходом триггера, информационный вход которого соединен с шиной логической единицы. устройства, прямой выход триггера соединен с входом запуска задающего генератора, выход которого соединен со счетным входом счетного триггера, выход которого соединен с входом разрешения записи блока оперативной памяти, первая группа выходов буферного регистра соединена с адресными входами с первого по (и)-й блока постоянной памяти, и-й адресный вход которого соединен с выходом блока оперативной памяти, вторая группа выходов буферного регистра соединена с группой адресных входов блока оперативной памяти, группа выходов блокапостоянной памяти соединена с группой информационных входов буферного регистра, первый выход которого соединен с информационным входом блока оперативной памяти, второй выход буферного регистра соединен с входомсброса в "0" триггера, третий выход буферного регистра является выходом устройства, инверсный выходтриггера соединен с входом сброса в "0" буферного регистра и с входом.сброса в "0" счетного триггера. А 1 ф 035 103 в В ячейке блоком 6 с адресом 103 15зафиксирована микрокоманда, в которой А = 01, А = 05, У = О.Это микропрограммное слово будет зафиксировано на регистре 5 и,следовательно, на втором шаге первого цикла будет выполняться записьнуля в первую ячейку ОЗУ, а управление (адрес блока 6 А = 05 я) будет передано в пятую (А = 05 в) ячейку ПЗУ, где А = 02, А = 06, У, = 25= О, У = О, У = О.Таким образом, будет выполнятьсяпервый шаг второго цикла, на которомосуществляется чтение второй ячей-.ки ОЗУ и микропрограммного слова 30из ячейки ПЗУ с адресом А= 06.Содержимое второй ячейки ОЗУ равнонулю, поэтому адрес ПЗУ, содержимоекоторого будет считываться на следующем шаге, равен 06 (в противномслучае 106),35На втором шаге второго цикла производится запись единицы во вторуюячейку блока 7, а управление передается в четвертую ячейку блока 6, 40из которой осуществляется сбростриггера 2 микрокомандным словоманалогично описанному (У = 1).После выполнения второго циклав блоке 7 будет зафиксирован код010. С приходом третьего, четвертого и т.д. счетных импульсов процедуры по их обработке повторяются.Распределение информации в ОЗУ иход микропрограммы, реализуемой согласно табло 1, при обработке счетных импульсов для трехразрядногодвоичного суммирующего счетчика(восьм,) Значение микрокоманды мер шаУ".2 03 Пример реализации микропрограммы для трехраэрядного двоичного счетчика Значениетекущегоадресаблока 6(дв.) га О 11 00 1 00 103 Запись "О" в 2разряд блока 7по адресу 01Передача управления на обработкуследующего разряда. 0 2 01 05 0 0 106 0 2 02 07 0 0 0 2 03 110 Значение микрокоманды Значениетекущегоадресаблока 6(восьм.) Окончание периода,Запись "0" в 2 разряд блока 7 по адресу 02. Передача управления на обработку следующего адреса разряда,Запись "0" в 2й разряд блока 7 по адресу 038, Передача управления на обработку переполнения и сброс триггера 2.14516922Ход микропрограммы Таблица 2 Распределение информации в блоке 7 и ход микропрограммыпри обработке счетных импульсов трехразрядного двоичногосуммирующего счетчика Номер цикла Номер счетНомер шага Номерпериода Значение разрядов ОЗУ и адрес ячейки ОЗУ, Ю9+1)-й ячейке блокаР оба вбаеясю Ю Жимаюоадерлажага д же Щ фои дЬжУаЭж г нуяь значениююриггера 2 Ю с- ячвйкв вьюка 7 прис 8 аибаеясяаУини а л-,й ячейке Жэкаприсбаидаеася единица Иикроееенде грюбавдаеяса зиач.едиац у Ыщеяс ии сияний сигал Р р ифтнаМз Ф единичсосаояниетриж 1 оа 2 анализ содержикоео с-й чеики алака 7гЬализ соиюого с-и киФ а Са ержимаиу с-и Рцж . Юцка 7 ярисдаабаеясвзначение нулю ЮгОресу алакаисбаибаврсю ачениу садвржииоиу(с +4)-и8 ячейки блока 7 п иай ибаеася знач. и я адресу Флака 7присдаибаеясазна ение 8)-ь л И1451 б 92 оставитель Н.Торопова ехред А.Кравчук К ектор А.Обруча едактор А а оизводственно-полиграфическое предприятие, г. Ужгород, ул . Проектная, 4 Заказ 7081/47 Тир аж ВНИИПИ Государственного коми 113035, Москб 67 Подписноета по изобретениям иЖ, Раушская наб. открытиям при ГКНТ СССР д. 4/5

СмотретьЗаявка

4017141, 05.02.1987

ПРЕДПРИЯТИЕ ПЯ А-7162

КРИВЕГО ВЛАДИМИР АЛЕКСАНДРОВИЧ, ГЛОНТИ ЕВГЕНИЙ ВЛАДИМИРОВИЧ, ПОЛЕХА ВАСИЛИЙ АНАТОЛЬЕВИЧ, КРИВЕГО ВАДИМ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.01.1989

Код ссылки

<a href="https://patents.su/9-1451692-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для сложения и вычитания чисел по модулю

Следующий патент: Приоритетное устройство

Случайный патент: Способ получения привитых сополимеров