Устройство для кодирования звуковых сигналов с инерционным компандированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1450113

Авторы: Анисимов, Ванде-Кирков, Матвеев, Шепелев

Текст

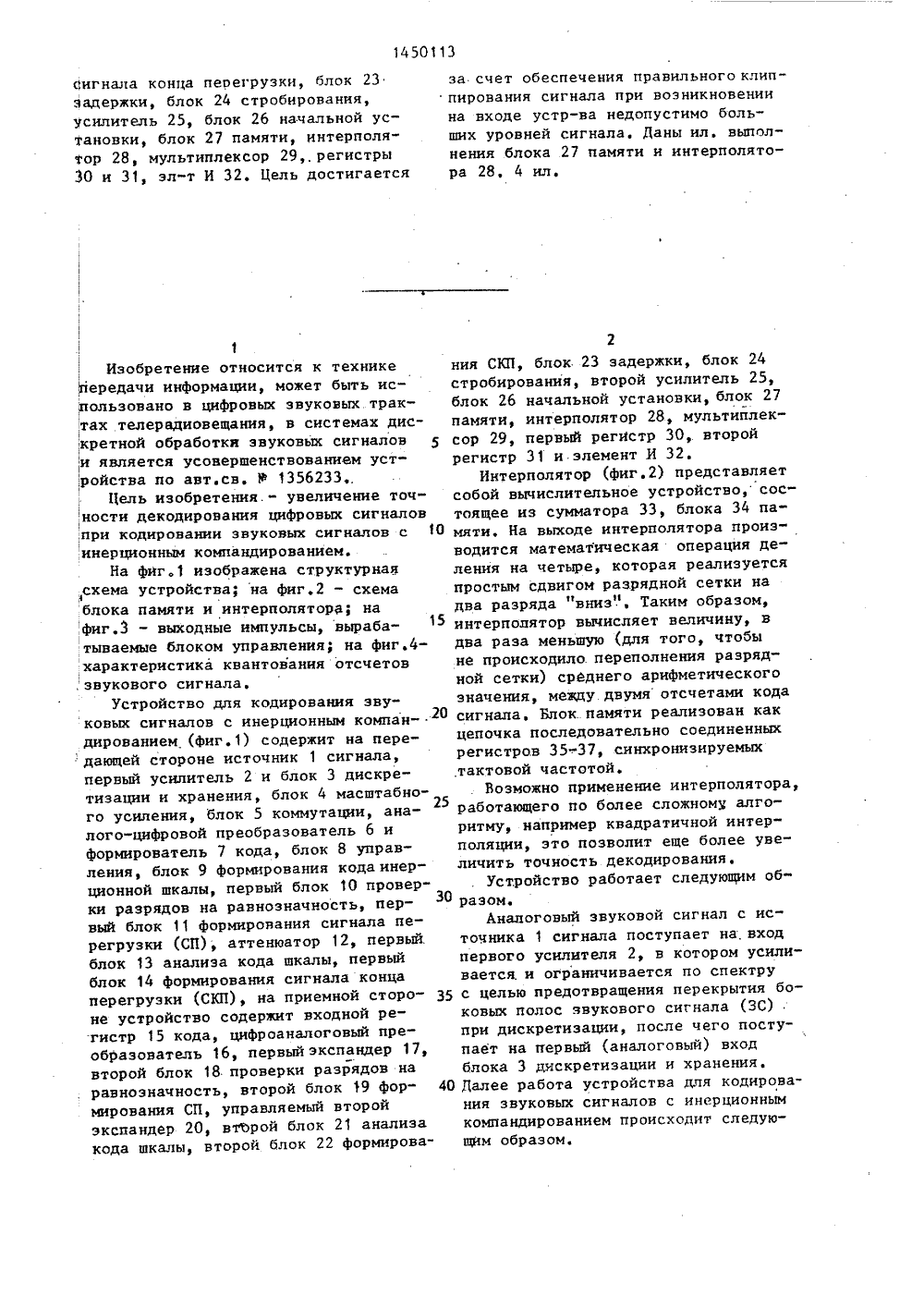

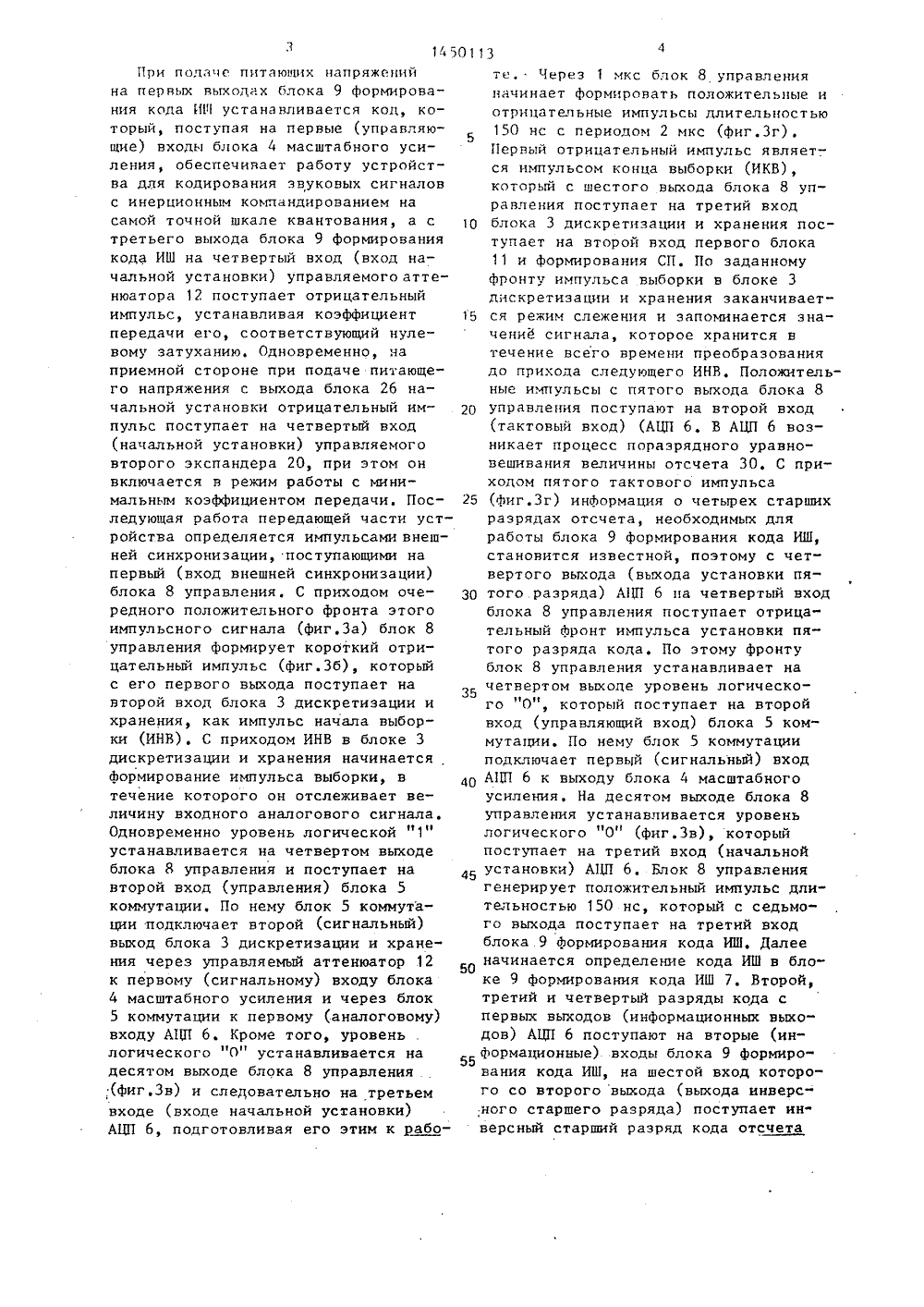

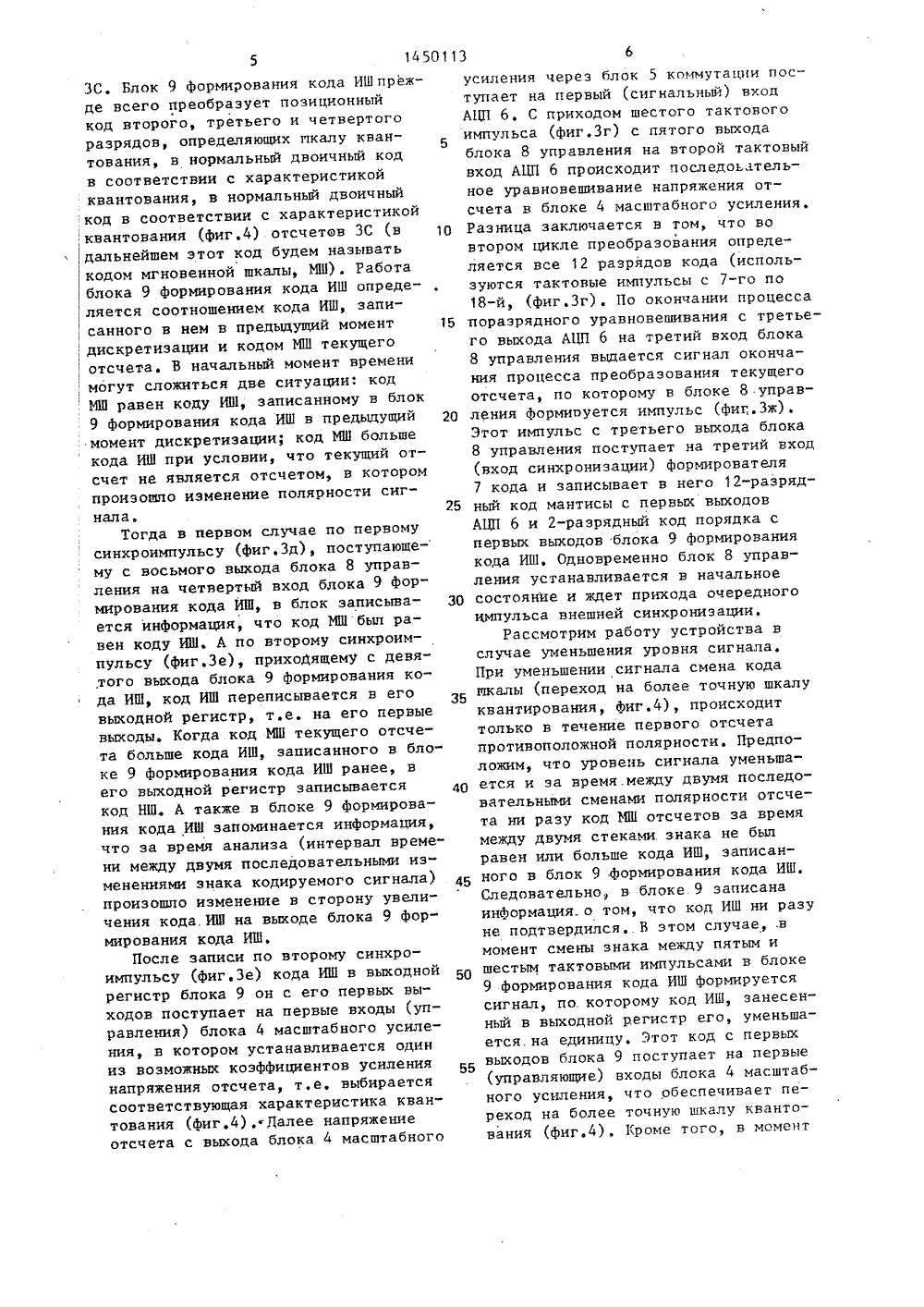

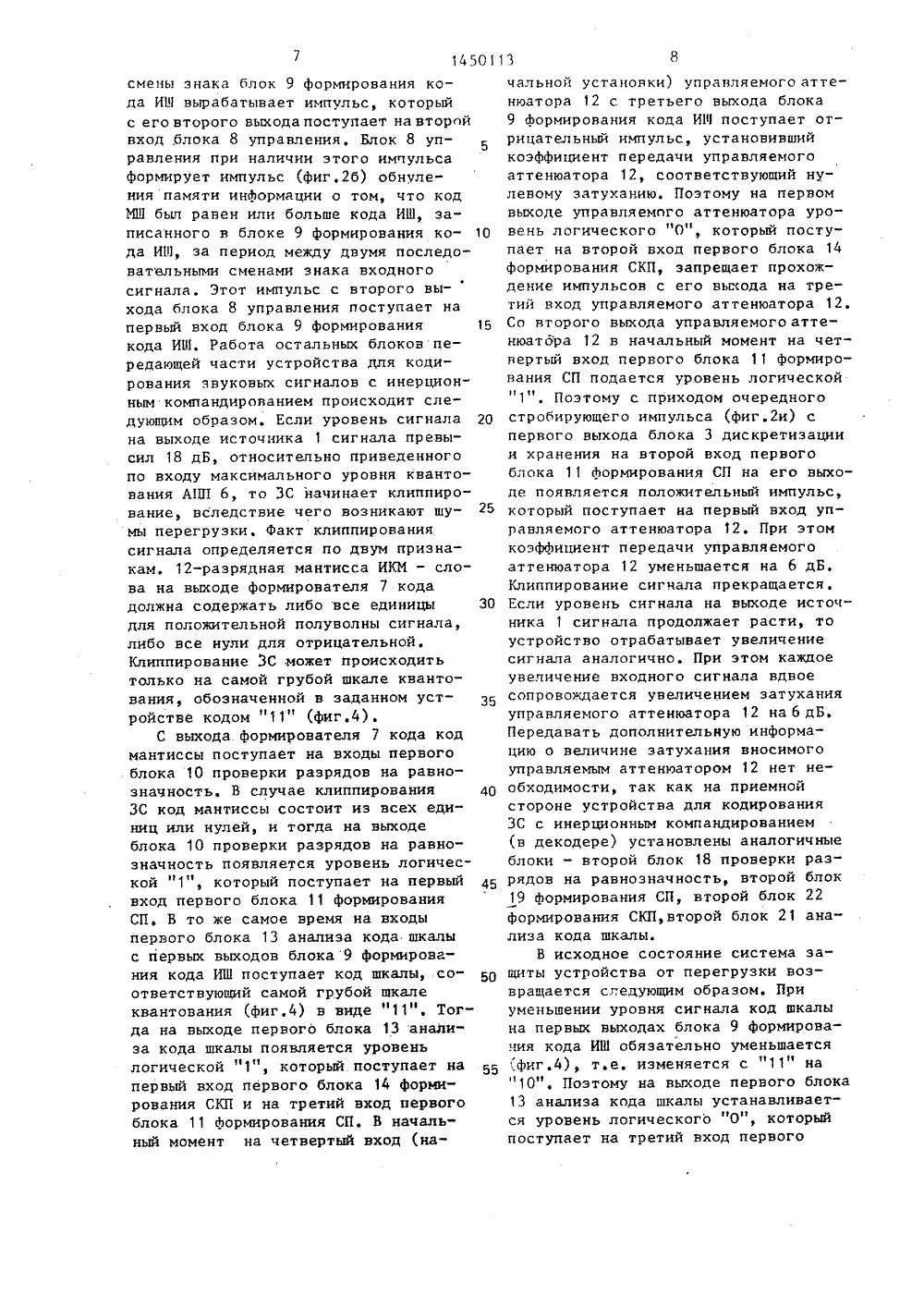

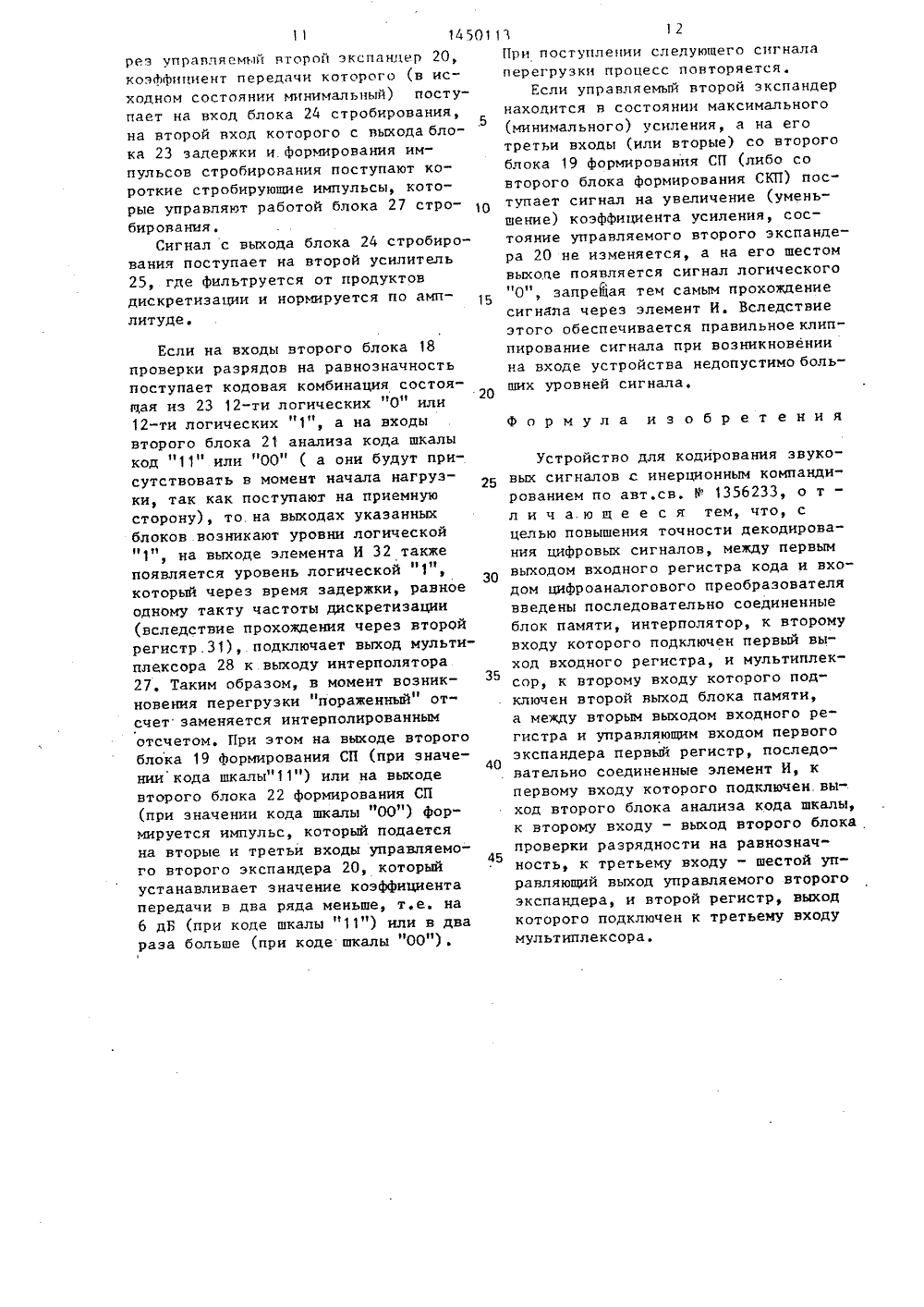

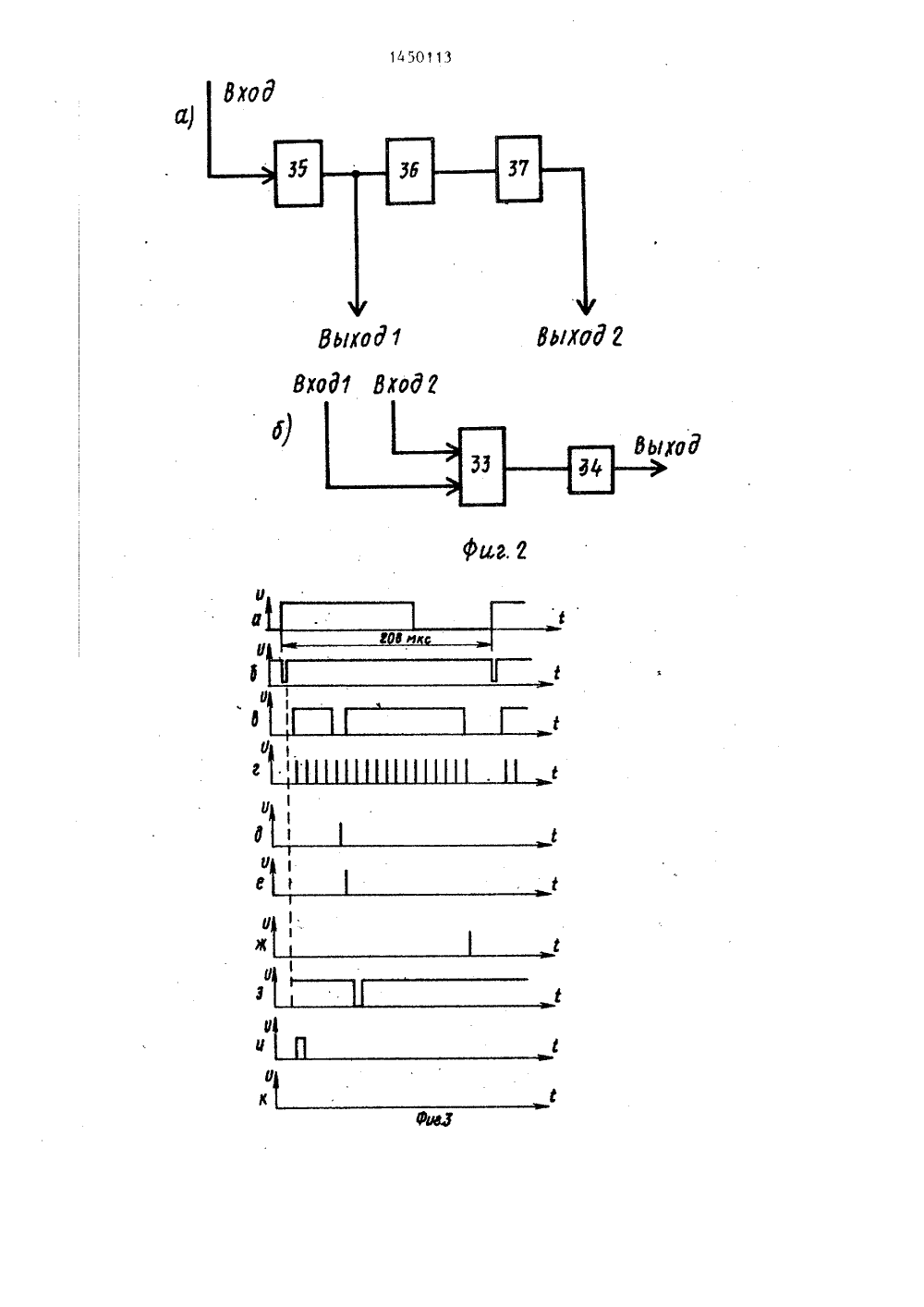

1450113 1Изобретение относится к техникепередачи информации, может быть использовано в цифровых звуковых.трактах телерадиовещания, в системах дискретной обработки звуковых сигналови является усовершенствованием устройства по авт.св. Р 1356233Цель изобретения. - увеличение точ,ности декодирования цифровых сигналов,при кодировании звуковых сигналов с 10инерционным компандированием.На фиг.1 изображена структурнаясхема устройства; на фиг,2 - схемаблока памяти и интерполятора; нафиг.3 - выходные импульсы, вырабатываемые блоком управления; на фиг.4 характеристика квантования отсчетов,звукового сигнала,Устройство для кодирования звуковых сигналов с инерционным компандированием (фиг. 1) содержит на пере дающей стороне источник 1 сигнала,первый усилитель 2 и блок 3 дискретизации и хранения, блок 4 масштабного усиления, блок 5 коммутации, ана 25лого-цифровой преобразователь 6 иформирователь 7 кода, блок 8 управления, блок 9 формирования кодаинерционной шкалы, первый блок 10 провер"ки разрядов на равнозначность, первый блок 11 формирования сигнала перегрузки (СП), аттенюатор 12, первый.блок 13 анализа кода шкалы, первыйблок 14 формирования сигнала концаперегрузки (СКП), на приемной стороне устройство содержит входной регистр 15 кода, цифроаналоговый преобразователь 16, первый зкспандер 17,второй блок 18 проверки разрядов наравнозначность, второй блок 19 фор" 40мирования СП, управляемый второйэкспандер 20, втЬрой блок 21 анализакода шкалы, второй блок 22 формирова 2ния СКП, блок 23 задержки, блок 24 стробирования, второй усилитель 25, блок 26 начальной установки, блок 27 памяти, интерполятор 28, мультиплексор 29, первый регистр 30, второй регистр 3 1 и элемент И 32.Интерполятор (фиг.2) представляет собой вычислительное устройство, состоящее из сумматора 33, блока 34 памяти, На выходе интерполятора производится математическая операция деления на четыре, которая реализуется простым сдвигом разрядной сетки на два разряда "вниз", Таким образом, интерподятор вычисляет величину, в два раза меньшую (для того, чтобы не происходило переполнения разрядной сетки) среднего арифметического значения, между двумя отсчетами кода сигнала. Блок. памяти реализован как цепочка последовательно соединенных регистров 35-37, синхронизируемых тактовой частотой.Возможно применение интерполятора, работающего по более сложному алгоритму, например квадратичной интерполяции, это позволит еще более уве" личить точность декодирования.Устройство работает следующим об" разом.Аналоговый звуковой сигнал с источника 1 сигнала поступает на, вход первого усилителя 2, в котором усиливается, и ограничивается по спектру с целью предотвращения перекрытия боковых полос звукового сигнала (ЗС), при дискретизации, после чего поступает на первый (аналоговый) вход блока 3 дискретизации и храненияДалее работа устройства для кодирования звуковых сигналов с инерционным компандированием происходит следующим образом Сигнала конца перегрузки, блок 23задержки, блок 24 стробирования,усилитель 25, блок 26 начальной установки, блок 27 памяти, интерполятор 28, мультиплексор 29 регистры30 и 31, эл-т И 32. Цель достигается эа счет обеспечения правильного клиппирования сигнала при возникновениина входе устр-ва недопустимо больших уровней сигнала, Ланы ил, выполнения блока 27 памяти и интерполятора 28. 4 ил.При подаче питающих напряжений на первых выходах блока 9 формирования кода ИШ устанавливается код, который, поступая на первые (управляющие) входы блока 4 масштабного усиления, обеспечивает работу устройства для кодирования звуковых сигналов с инерционным компандированием на самой точной шкале квантования, а с третьего выхода блока 9 формирования кода ИШ на четвертый вход (вход начальной установки) управляемого аттенюатора 2 поступает отрицательный импульс, устанавливая коэффициент передачи его, соответствующий нулевому затуханию. Одновременно, на приемной стороне при подаче питающего напряжения с выхода блока 26 начальной установки отрицательный импульс поступает на четвертый вход (начальной установки) управляемого второго экспандера 20, при этом он включается н режим работы с минимальным коэффициентом передачи. Последующая работа передающей части устройства определяется импульсами внешней синхронизации, поступающими на первый (вход внешней синхронизации) блока 8 управления, С приходом очередного положительного фронта этого импульсного сигнала (фигЗа) блок 8 управления формирует короткий отрицательный импульс (фиг.Зб), который с его первого выхода поступает на второй вход блока 3 дискретизации и хранения, как импульс начала выборки (ИНВ). С приходом ИНВ в блоке 3 дискретизации и хранения начинается формирование импульса выборки, в течение которого он отслеживает величину входного аналогового сигнала, Одновременно уровень логической "1" устанавливается на четвертом выходе блока 8 управления и поступает на второй вход (управления) блока 5 коммутации, По нему блок 5 коммутации подключает второй (сигнальный) выход блока 3 дискретизации и хранения через управляемый аттенюатор 12 к первому (сигнальному) входу блока 4 масштабного усиления и через блок 5 коммутации к первому (аналоговому) входу АЦП 6. Кроме того, уровень логического "О" устанавливается на десятом выходе блока 8 управления(фиг.Зв) и следовательно на третьем входе (входе начальной установки) АЦП 6, подготовливая его этим к рабооте. Через 1 мкс блок 8 управленияначинает формировать положительные иотрицательные импульсы длительностью150 нс с периодом 2 мкс (фиг,Зг),Первый отрицательный импульс являет-.ся импульсом конца выборки (ИКВ),который с шестого выхода блока 8 управления поступает на третий вход 10 блока 3 дискретизации и хранения поступает на второй вход первого блока11 и формирования СП. По заданномуфронту импульса выборки в блоке 3дискретизации и хранения заканчивает ся режим слежения и запоминается значение сигнала, которое хранится втечение всего времени преобразованиядо прихода следующего ИНВ, Положительные импульсы с пятого выхода блока 8 20 управления поступают на второй вход(тактовый вход) (АЦП 6, В АЦП 6 возникает процесс поразрядного уравновешивания величины отсчета 30, С приходом пятого тактового импульса 25 (фиг.Зг) информация о четырех старшихразрядах отсчета, необходимых дляработы блока 9 формирования кода ИШ,становится известной, поэтому с четвертого выхода (выхода установки пя того разряда) АЦП 6 па четвертый входблока 8 управления поступает отрицательный фронт импульса установки пятого разряда кода, По этому фронтублок 8 управления устанавливает начетвертом выходе уровень логического "О", который поступает на второйвход (управляющий вход) блока 5 коммутации, По нему блок 5 коммутацииподключает первый (сигнальный) вход 40 АЦП 6 к выходу блока 4 масштабногоусиления, На десятом выходе блока 8управления устанавливается уровеньлогического "0 (фиг,Зв), которыйпоступает на третий вход (начальной 45 установки) АЦП 6. Блок 8 управлениягенерирует положительный импульс длительностью 150 нс, который с седьмого выхода поступает на третий входблока 9 формирования кода ИШ, Далееначинается определение кода ИШ В блоке 9 формирования кода ИШ 7, Второй,третий и четвертый разряды кода спервых выходов (информационных выходов) АЦП 6 поступают на вторые (информационные) входы блока 9 формирования кода ИШ, на шестой вход которого со второго выхода (выхода инверсного старшего разряда) поступает ин"версный старший разряд кода отсчетаЗС. Блок 9 формирования кода ИШ прежде всего преобразует позиционныйкод второго, третьего и четвертогоразрядов, определяющих шкалу квантования, в нормальный двоичный кодв соответствии с характеристикойквантования, в нормальный двоичный код в соответствии с характеристикой квантования (фиг.4) отсчетов ЗС (в 10 ,дальнейшем этот код будем называть кодом мгновенной шкалы, МШ). Работа блока 9 формирования кода ИШ определяется соотношением кода ИШ, запи, санного в ием в предыдущий момент 15дискретизации и кодом МШ текущего , отсчета. В начальный момент времени ,могут сложиться две ситуации: кодМШ равен коду ИШ, записанному в блок 9 формирования кода ИШ в предыдущий 20 момент дискретизации; код МШ больше кода ИШ при условии, что текущий отсчет не является отсчетом, в котором произошло изменение полярности сигнала, 25Тогда в первом случае по первому синхроимпульсу (фиг.Зд), поступающему с восьмого выхода блока 8 управления на четвертый вход блока 9 Формирования кода ИШ, в блок записыва ется информация, что код МШ быравен коду ИШ. А по второму синхроимпульсу (фиг.Зе), приходящему с девя,того выхода блока 9 формирования кода ИШ, код ИШ переписывается в его выходной регистр, т.е. на его первые выходы, Когда код МШ текущего отсчета больше кода ИШ, записанного в блоке 9 формирования кода ИШ ранее, вего выходной регистр записываетсякод НШ. А также в блоке 9 формирования кода ИШ запоминается информация, что за время анализа (интервал времени между двумя последовательными изменениями знака кодируемого сигнала) произошло изменение в сторону увеличения кода. ИШ на выходе блока 9 формирования кода ИШ.После записи по второму синхроимпульсу (фиг.Зе) кода ИШ в выходнойрегистр блока 9 он с его первых выходов поступает на первые входы (управления) блока 4 масштабного усиления, в котором устанавливается одиниз возможных коэффициентов усиления напряжения отсчета, т,е. выбирается соответствующая характеристика квантования (фиг,4),Палее напряжениеотсчета с выхода блока 4 масштабного усиления через блок 5 коммутации поступает на первый (сигнальный) вход АЦП 6. С приходом шестого тактового импульса (фиг.Зг) с пятого выхода блока 8 управления на второй тактовый вход АЦП 6 происходит последоьательное уравновешивание напряжения отсчета в блоке 4 масштабного усиления, Разница заключается в том, что во втором цикле преобразования определяется все 12 разрядов кода (используются тактовые импульсы с 7-го по 18-й, (фиг.Зг). По окончании процесса поразрядного уравновешивания с третьего выхода АЦП б на третий вход блока 8 управления выдается сигнал окончания процесса преобразования текущего отсчета, по которому в блоке 8 управления формиоуется импульс (фигЗж). Этот импульс с третьего выхода блока 8 управления поступает на третий вход (вход синхронизации) формирователя 7 кода и записывает в него 12-разрядный код мантисы с первых выходов АЦП 6 и 2-разрядный код порядка с первых выходов блока 9 Формирования кода ИШ. Одновременно блок 8 управления устанавливается в начальное состояние и ждет прихода очередного импульса внешней синхронизации.Рассмотрим работу устройства в случае уменьшения уровня сигнала. При уменьшении сигнала смена кода шкалы (переход на более точную шкалу квантирования, фиг.4), происходит только в течение первого отсчета противоположной полярности. Предположим, что уровень сигнала уменьшается и эа время. между двумя последовательными сменами полярности отсчета ни разу код МШ отсчетов за время между двумя стеками знака не был равен или больше кода ИШ, записанного в блок 9 формирования кода ИШ. Следовательно, в блоке 9 записана информация. о том, что код ИШ ни разу не подтвердился,. В этом случаев момент смены знака между пятым и шестым тактовыми импульсами в блоке 9 формирования кода ИШ формируется сигнал, по.которому код ИШ, занесенный в выходной регистр его, уменьшается.на единицу. Этот код с первых выходов блока 9 поступает на первые (управляющие) входы блока 4 масштабного усиления, что обеспечивает переход на более точную шкалу квантования (фиг.4), Кроме того, в моментсмены знака блок 9 формирования кода ИШ вырабатывает импульс, который с его второго выходапоступает на второй вход блока 8 управления, Блок 8 управления при наличии этого импульса формирует импульс (фиг,2 б) обнуления памяти информации о том, что код МШ был равен или больше кода ИШ, записанного в блоке 9 формирования ко да ИШ, за период между двумя последовательными сменами знака входного сигнала, Этот импульс с второго выхода блока 8 управления поступает на первый вход блока 9 формирования 15 кода ИШ, Работа остальных блоковпередающей части устройства для кодирования звуковых сигналов с инерционным компандированием происходит следующим образом. Если уровень сигнала 20 на выходе источника 1 сигнала превысил 18 дБ, относительно приведенного по входу максимального уровня квантования АИП 6, то ЭС начинает клиппирование, вследствие чего возникают шу мы перегрузки. Факт клиппирования сигнала определяется по двум признакам, 12-разрядная мантисса ИКМ - слова на выходе формирователя 7 кода должна содержать либо все единицы 30 для положительной полуволны сигнала, либо все нули для отрицательной. Клиппирование ЗС может происходить только на самой грубой шкале квантования, обозначенной в заданном устройстве кодом "11" (фиг,4).С выхода формирователя 7 кода код мантиссы поступает на входы первого . блока 10 проверки разрядов на равнозначность. В случае клиппирования 40 ЗС код мантиссы состоит из всех еди" ниц или нулей, и тогда на выходе блока 10 проверки разрядов на равнозначность появляется уровень логической 1, который поступает на первый 45 вход первого блока 11 формирования СП, В то же самое время на входы первого блока 13 анализа кода шкалы с первых выходов блока 9 формирования кода ИШ поступает код шкалы, со ответствующий самой грубой шкале квантования (фиг,4) в виде "11". Тогда на выходе первого блока 13 анализа кода шкалы появляется уровень логической "1", который поступает на первый вход первого блока 14 формирования СКП и на третий вход первого блока 11 формирования СП. В начальный момент на четвертый вход (начальнай установки) управляемого аттенюатора 12 с третьего выхода блока 9 формирования кода ИИ поступает отрицательный импульс, установивший коэффициент передачи управляемого аттенюатора 12, соответствующий нулевому затуханию, Поэтому на первом выходе управляемого аттенюатора уровень логического "0", который поступает на второй вход первого блока 14 формирования СКП, запрещает прохождение импульсов с его вьиода на третий вход управляемого аттенюатора 12, Со второго выхода управляемого аттенюатора 12 в начальный момент на четвертый вход первого блока 11 формирования СП подается уровень логической "1". Поэтому с приходом очередного стробирующего импульса (фиг.2 и) с первого выхода блока 3 дискретизации и хранения на второй вход первого блока 11 формирования СП на его выходе появляется положительный импульс, который поступает на первый вход управляемого аттенюатора 12, При этом коэффициент передачи управляемого аттенюатора 12 уменьшается на 6 дБ. Клиппирование сигнала прекращается. Если уровень сигнала на выходе источника 1 сигнала продолжает расти, то устройство отрабатывает увеличение сигнала аналогично. При этом каждое увеличение входного сигнала вдвое сопровождается увеличением затухания управляемого аттенюатора 12 на 6 дБ, Передавать дополнительную информацию о величине затухания вносимого управляемым аттенюатором 12 нет необходимости, так как на приемной стороне устройства для кодирования ЗС с инерционным компандированием (в декодере) установлены аналогичные блоки - второй блок 18 проверки разрядов на равнозначность, второй блок 19 формирования СП, второй блок 22 формирования СКП,второй блок 2 1 анализа кода шкалы.В исходное состояние система защиты устройства от перегрузки возвращается следующим образом. При уменьшении уровня сигнала код шкалы на первых выходах блока 9 формирования кода ИШ обязательно уменьшается (фиг,4), т.е. изменяется с "11" на "10". Поэтому на выходе первого блока 13 анализа кода шкалы устанавливает" ся уровень логического "0", который поступает на третий вход первого9 145011 блока 11 формирования СП, блокируя его, и на первый вход первого блока 14 формирования ВКП, В последнем по отрицательному Фронту вырабаты"5 вается положительный импульс, которьй поступает на третий вход управ" л 4 емого аттенюатора 12 и уменьшает затухание отсчета ЗС, подаваемого с третьего выхода управляемого аттен атора 12 на. второй вход (сигнальн вход) блока 4 масштабного усил ния и на третий вход блока 5 комм тации.В процессе работы уровень сигнала н выходе источника 1 сигнала может о азаться несколько большим, что д же при максимальном затухании, в осимом управляемым аттенюатором 12, п оисходит клиппирование сигнала, В этом случае на выходе первого бло-, к 10 проверки разрядов на равноз ачность появляется уровень логич ской "1", который поступает на перв вход первого блока 11 формирова н я СП, на третьем входе которого с в ода первого блока 11 формирования С , на третьем входе которого с вых да первого блока 13 анализа кодаалы также уровень логической "1". О нако при достижении максимального з тухания на втором выходе управляем го аттенюатора 12 и соответственно н четвертом входе первого блока 11 Формирования СП устанавливается уровень логического "О", запрещая прохождение импульсов с его выхода на пЕрвый вход управляемого аттенюатора 12, т.е. блокируя дальнейшее увелнчение затухания, вносимого управ ляемым аттенюатором 12. Что гарантирует его правильную работу. Аналогично, при уменьшении уровня сигнала на выходе источника 1 сигнала, формируется запрет на увеличение коэффициен та передачи управляемого аттенюатора 12. При достижении минимального коэфФИциента передачи (соответствующего нУлевому затуханию) на первом выходе уйравляемого аттенюатора 12 появляет ся уровень логическогб "0", который, поступая на второй вход первого блока 14 Формирования СКП, запрещает прохождение импульсов с его выхода на третий вход управляемого аттенюатора 12.На этом обработка сигнала с в передающей части устройства для кодирования звуковых сигналов с инер ого кпередач ления и Аналоги да перв устанавливает коэффициентнеобходимый для восстановходного значения отсчета. ный дискретный сигнал с выхо го экспандера 17 и далее чеционным компандированием заканчивается. Рассмотрим работу приемной части (декодера ЗС).В момент подачи питающих напряжений блок 26 начальной установки вырабатывает импульс, который устанавливает управляемый второй экспандер 20 в состояние максимального коэффициента перегрузки. При поступлении на вход внешней синхронизации приемной части устройства импульсного сигнала с частотой 48 кГц по его положительному фронту вырабатывается короткие положительные импульсы, которые поступают на третий вход второго блока 19 Формирования СП и на вход блока 23 задержки и формирования импульсов стробирования. 14-разрядный код величины отсчетов ЗС через входной регистр кода 15 поступает на блок 27 памяти, где обеспечивается его запоминание и сдвиг предыдущих отсчетов кода сигнала, на первый вход интерполятора и на второй блок 18 проверки разрядов на равнозначность, на выходе которого появляется логическая "1", в случае, если значения всех разрядов кода одновременно имеют значение либо логической "1" либо логического "0", а на вторые входы интерполятора 28 поступают с первого выхода блока памяти коды отсчетов предыдущих и последующих тактов. Интерполятор 28 по нескольким отсчетам входного сигнала вычисляет интерполированное значение отсчета, код которого подается на первый вход мультиплексора 29, на вторые входы которого подается сигнал со второго выхода блока 27 памяти. Мультиплексор 29 обеспечивает прохождение сигнала на ЦАП либо с выхода интерполятора 28, либо со второго выхода блока 27 памяти в зависимости от управляющего сигнала на третьем входе мультиплексора 29.Два разряда порядка кода входного сигнала поступают со второго входа входного регистра 15 кода, через первый регистр 30, осуществляющий задержку сигнала на один такт, вторые входы управления первого экспандера 17, который в зависимости от значения4501рез управляемый второй экспандер 20,коэффициент передачи которого (в исходном состоянии минимальный) поступает на вход блока 24 стробирования,5на второй вход которого с выхода блока 23 задержки и Формирования импульсов стробирования поступают короткие стробирующие импульсы, которые управляют работой блока 27 стробирования,Сигнал с выхода блока 24 стробирования поступает на второй усилитель25, где фильтруется от продуктовдискретизации и нормируется по амплитуде. Если на входы второго блока 18 проверки разрядов на равнозначность поступает кодовая комбинация состоящая из 23 12-ти логических "0" или20 12-ти логических "1", а на входывторого блока 21 анализа кода шкалы код "11" или "00" ( а они будут присутствовать в момент начала нагрузки, так как поступают на приемную сторону), то. на выходах указанных блоков возникают уровни логической "1", на выходе элемента И 32 также появляется уровень логической "1",ЗО который через время задержки, равное одному такту частоты дискретизации (вследствие прохождения через второй регистр.31), подключает выход мультиплексора 28 к выходу интерполятора 27, Таким образом, в момент возникновения перегрузки "пораженный" отсчет заменяется интерполированнымотсчетом, При этом на выходе второго блока 19 Формирования СП (при значениикода шкалы"11 ) или на выходеи 1140 второго блока 22 формирования СП(при значении кода шкалы "00") формируется импульс, который подается на вторые и третьи входы управляемого второго экспандера 20, который45 устанавливает значение коэффициента передачи в два ряда меньше, т.е, на 6 дБ (при коде шкалы "11") или в два раза больше (при коде шкалы "00"). 1 12При поступлении следующего сигнала перегрузки процесс повторяется.Если управляемый второй экспандер находится в состоянии максимального (минимального) усиления, а на его третьи входы (или вторые) со второго блока 19 формирования СП (либо со второго блока формирования СКП) поступает сигнал на увеличение (уменьшение) коэффициента усиления, состояние управляемого второго экспандера 20 не изменяется, а на его шестом выходе появляется сигнал логического "0", запрещая тем самым прохождение сигнала через элемент И. Вследствие этого обеспечивается правильное клиппирование сигнала при возникновении на входе устройства недопустимо больших уровней сигнала,Формула изобретенияустройство для кодирования звуковых сигналов с инерционным компандированием по авт,св. У 1356233, о тл и ч а.ю щ е е с я тем, что, с целью повышения точности декодирова" ния цифровых сигналов, между первым выходом входного регистра кода и входом цифроаналогового преобразователя введены последовательно соединенные блок памяти, интерполятор, к второму входу которого подключен первый выход входного регистра, и мультиплексор, к второму входу которого подключен второй выход блока памяти, а между вторым выходом входного регистра и управляющим входом первого экспандера первый регистр, последовательно соединенные элемент И, к первому входу которого подключен. выход второго блока анализа кода шкалы, к второму входу - выход второго блока проверки разрядности на равнозначность, к третьему входу - шестой управляющий выход управляемого второго экспандера, и второй регистр, выход которого подключен к третьему входу мультиплексора.1450113 зою Я Самборск актор Г.Волков Производственно-полиграфическое предприятие, г. Укгород, ул. Проектная,каз 6977/55 ИИПИ Госуда иЯ Ф Составитель Л.ТимошинаТехред М.Дидык Корре Тирык 660 Подписноеенного комитета по изобретениям и открытиям при ГКНТ ССС13035, Москва, Ж, Раушская наб., д, 4/5

СмотретьЗаявка

4292255, 30.07.1987

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

АНИСИМОВ СЕРГЕЙ ВАСИЛЬЕВИЧ, ВАНДЕ-КИРКОВ ВЛАДИМИР ВАДИМОВИЧ, МАТВЕЕВ НИКОЛАЙ ЕВГЕНЬЕВИЧ, ШЕПЕЛЕВ ВАДИМ ИВАНОВИЧ

МПК / Метки

МПК: H04B 1/64

Метки: звуковых, инерционным, кодирования, компандированием, сигналов

Опубликовано: 07.01.1989

Код ссылки

<a href="https://patents.su/9-1450113-ustrojjstvo-dlya-kodirovaniya-zvukovykh-signalov-s-inercionnym-kompandirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования звуковых сигналов с инерционным компандированием</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Устройство для калибровки электрической части системы телеизмерений

Случайный патент: 416246