Формирователь сигналов с заданным законом изменения фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

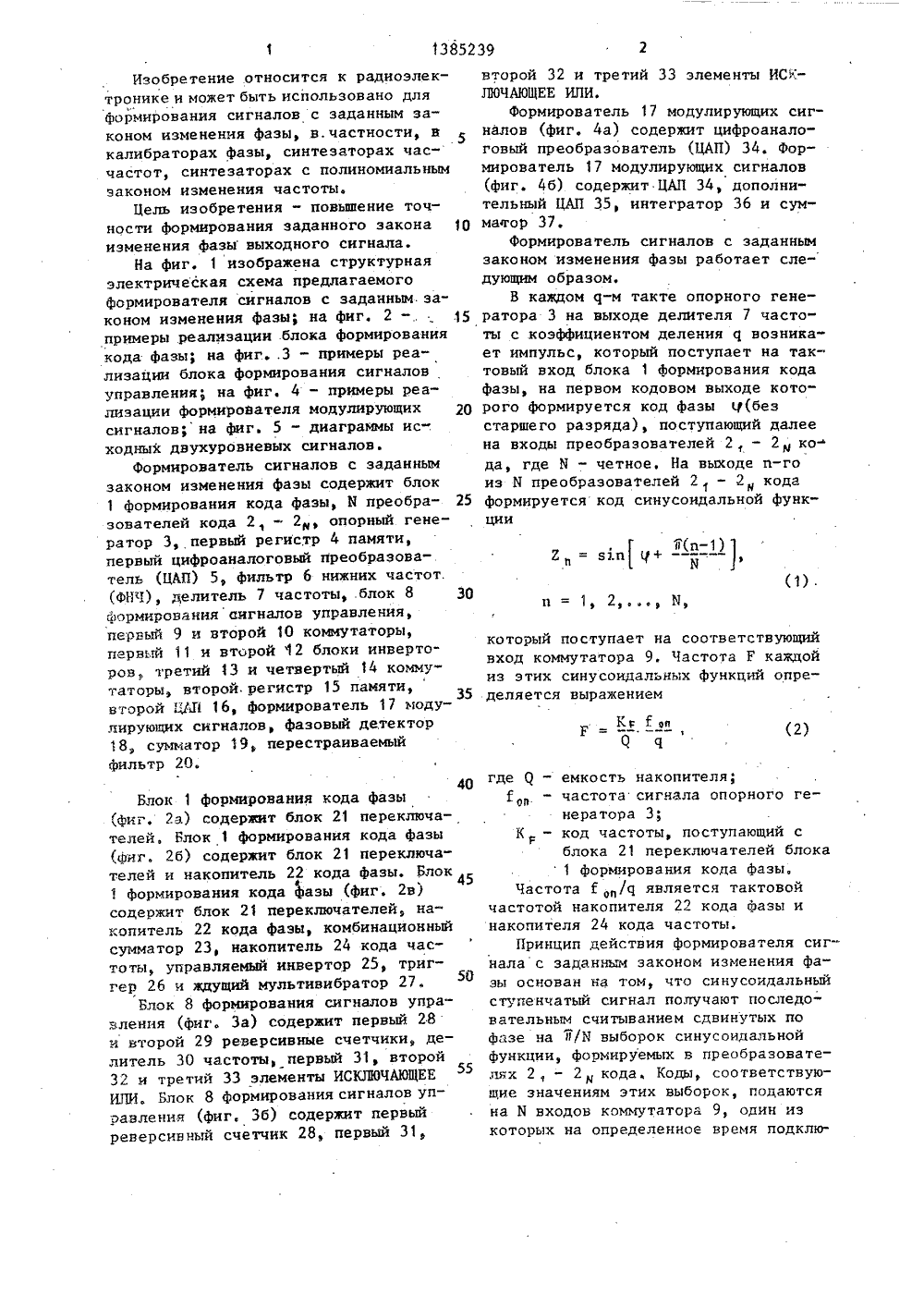

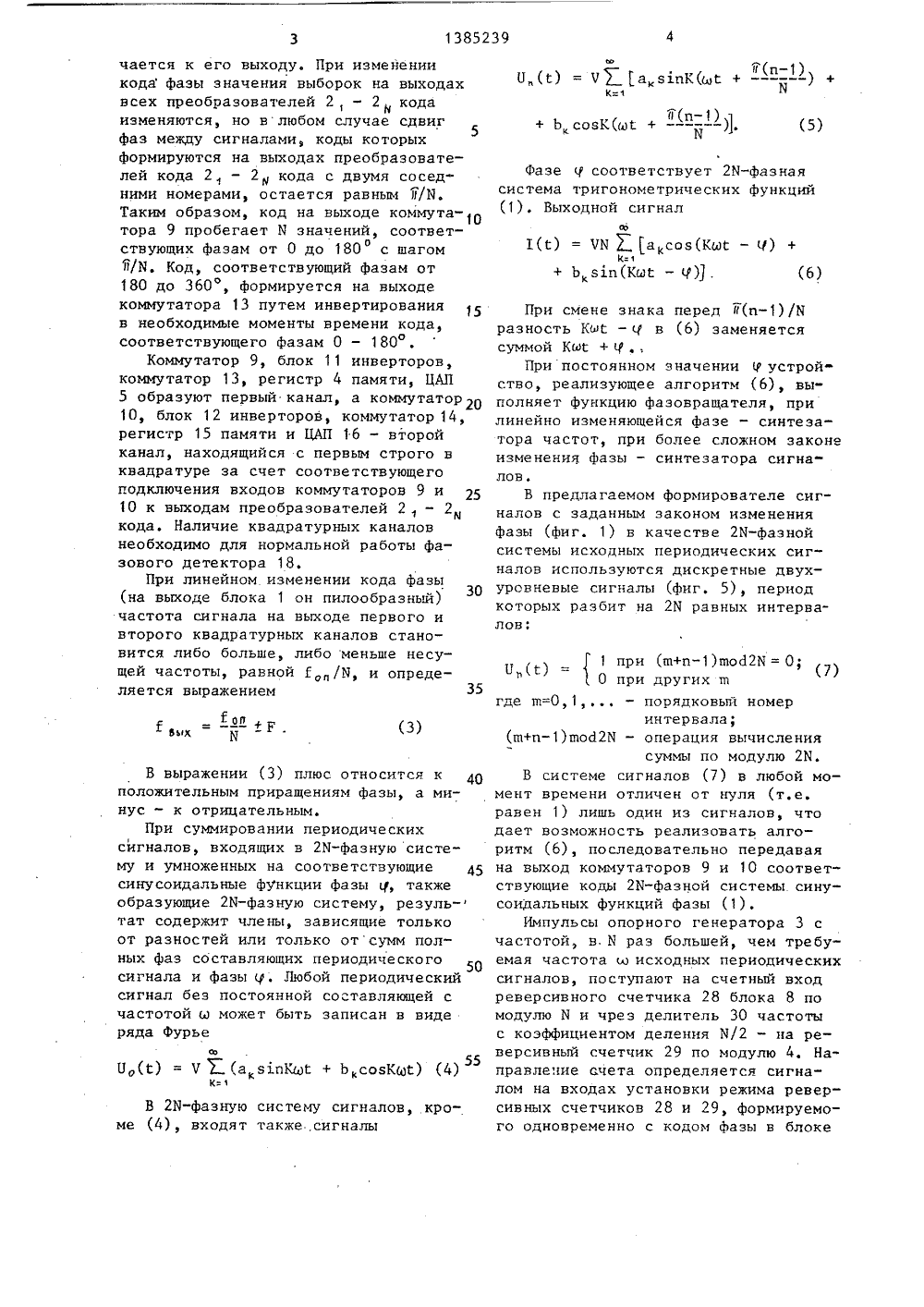

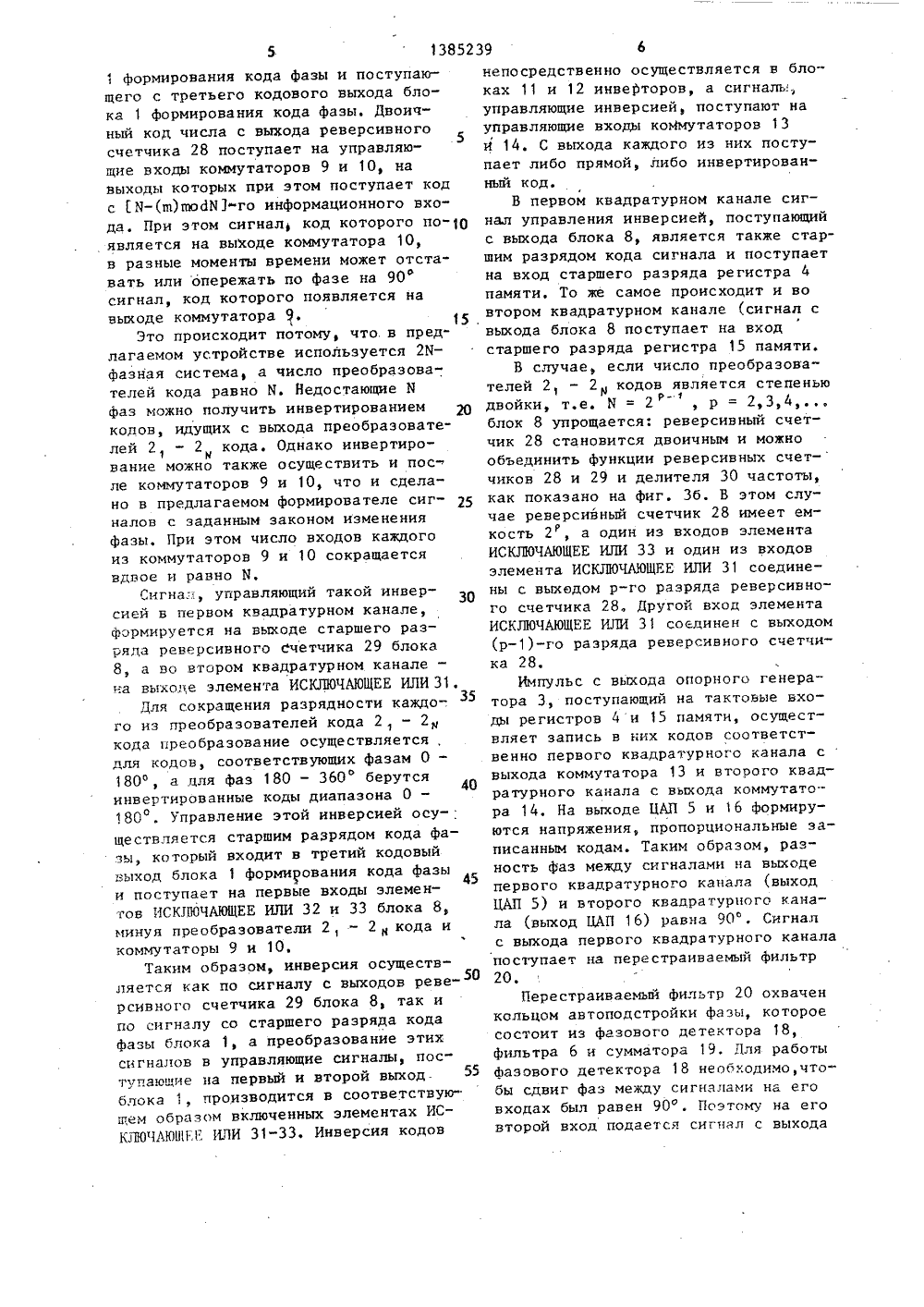

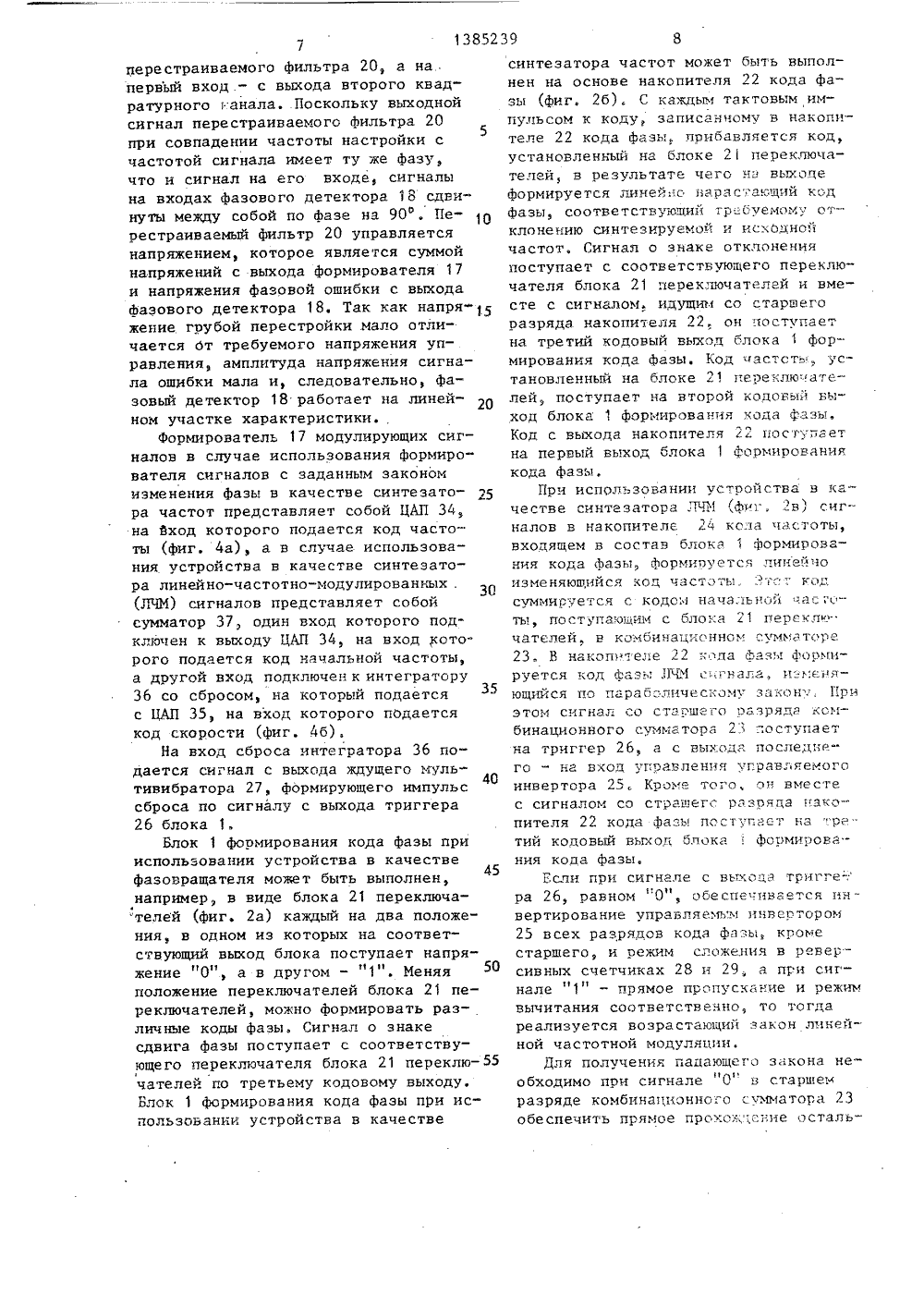

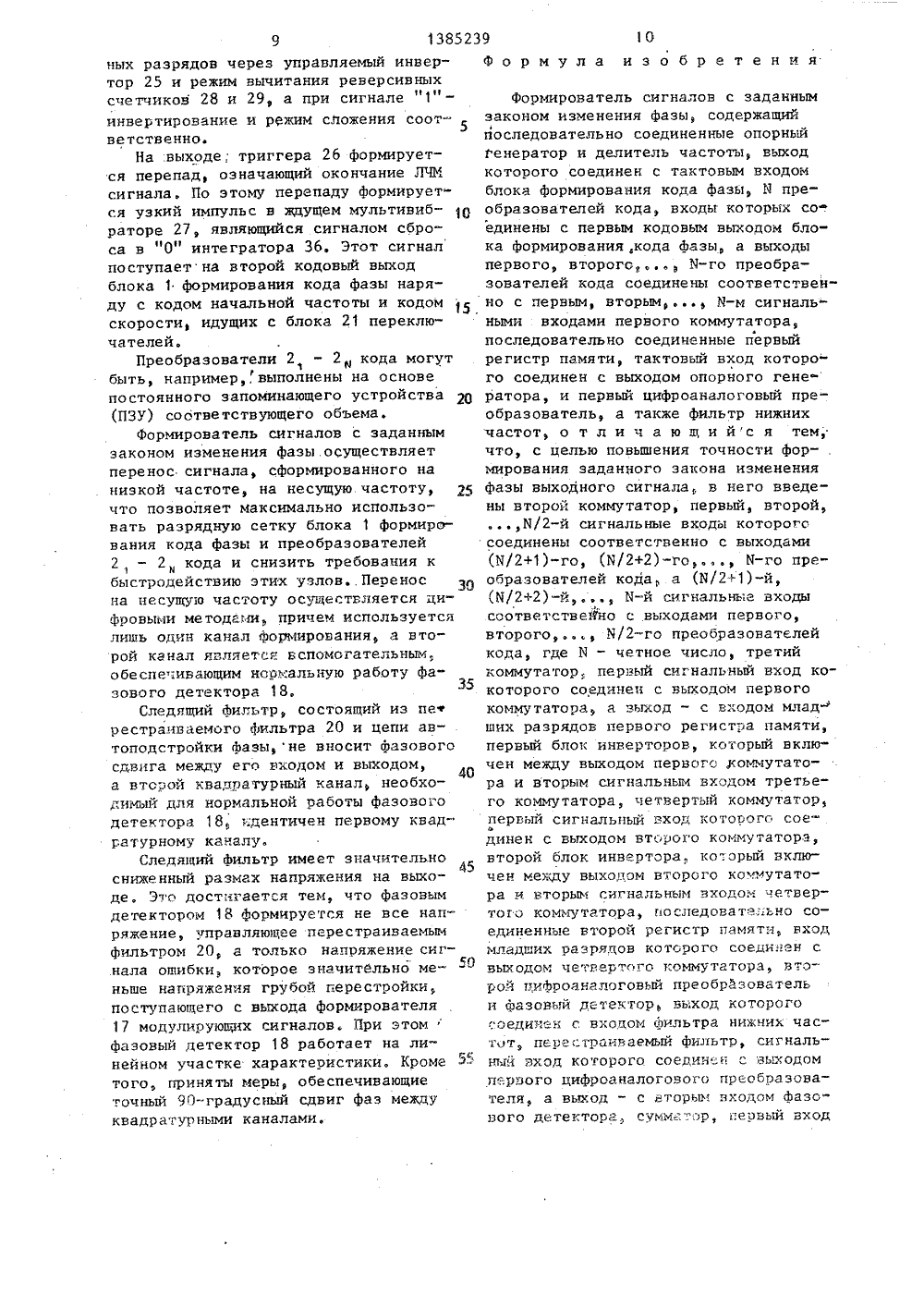

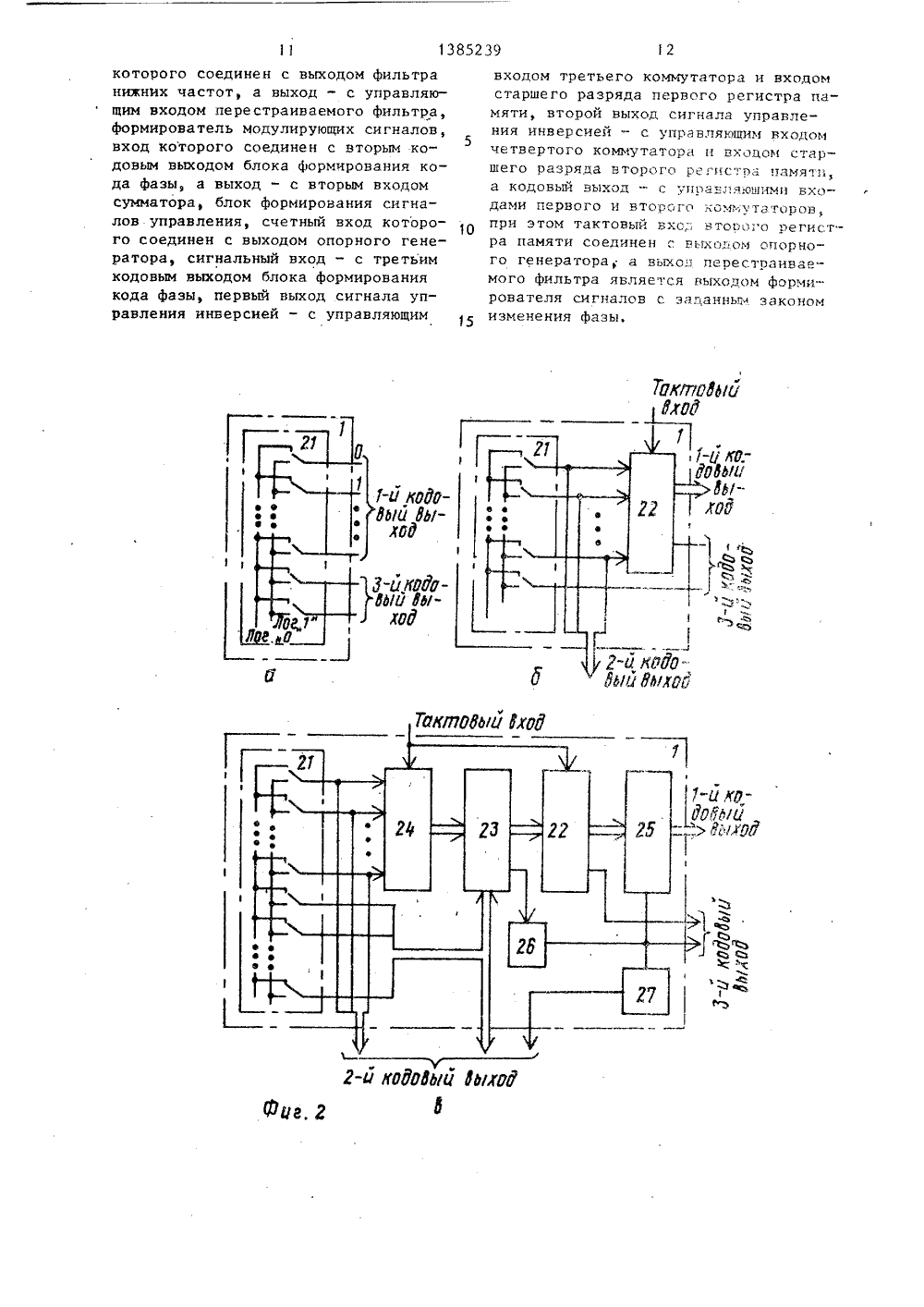

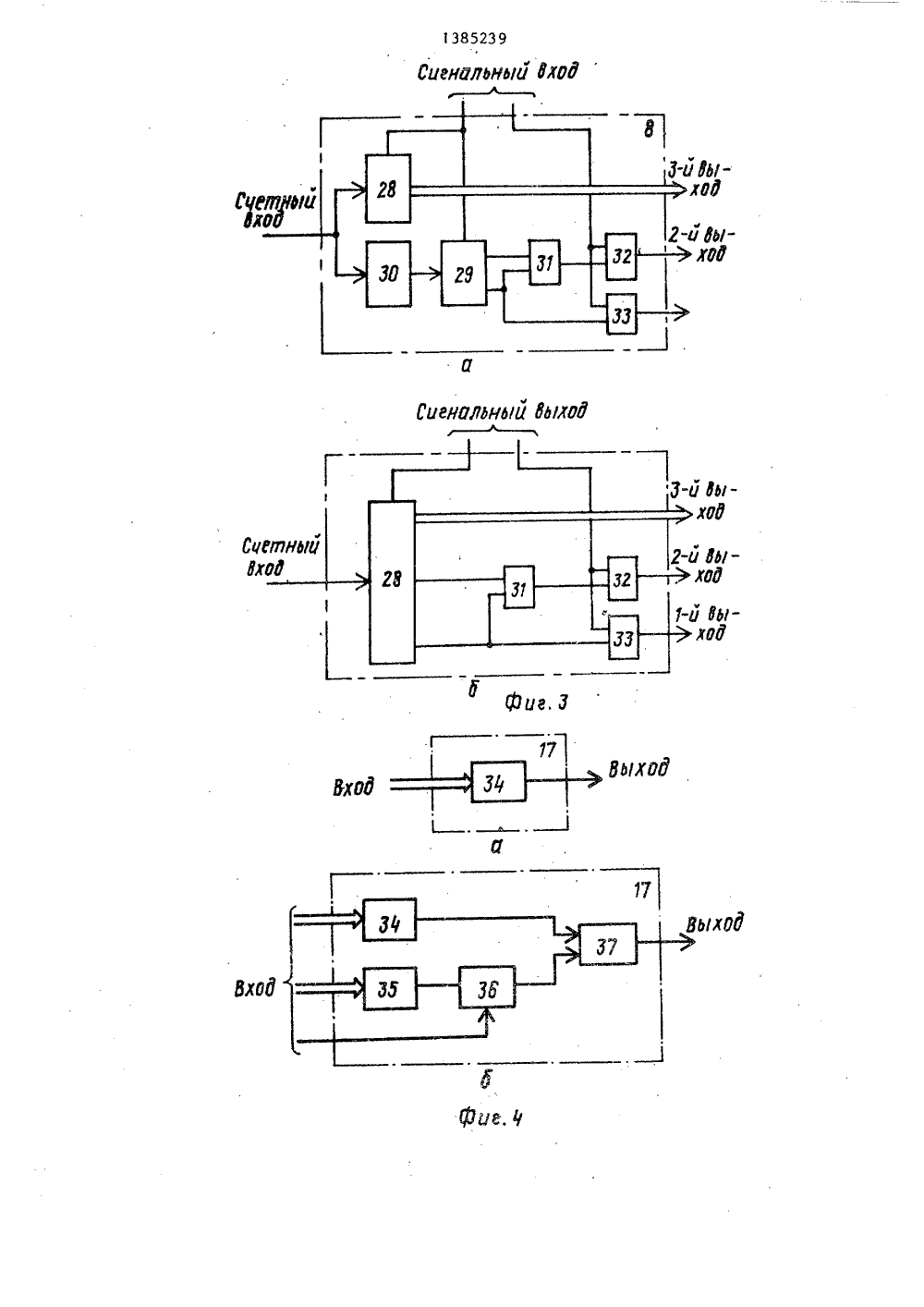

.ьРьЯИЯ 1",ИСАНИЕ ИЗОБРЕТ Котик вы ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВ(7 1) Всесоюзный заочный электротехнический институт связи(56) Авторское свидетельство СССРВ 1327267, кл. Н 03 С 3/00, 20,02,86,(54) ФОРМИРОВАТЕЛЬ СИГНАЛОВ С ЗАДАННЫМ ЗАКОНОМ ИЗМЕНЕНИЯ ФАЗЫ(57) Изобретение относится к радиоэлектронике. Для повышения точностиформирования заданного закона изменения фазы выходного сигнала в устрво введены блок 8 формирования сигналов управления, коммутаторы (К) 10,13 и 14, блоки 11 и 12.инверторов,регистр 15 памяти ЦАП 16, формирователь 17 модулирующих сигналов, фазовый детектор 18, сумматор 19, перестраиваемый фильтр 20, В каждом 2-м тракте опорного г-ра 3 на выходе делителя 7 частоты с коэф. делениявозникает импульс, к-рый поступает натактовый вход блока 1 формированиякода фазы. На 1-м кодовом выходе блока 1 формируется код фазы 4, поступающий на преобразователи (П) 21- 2),кода. На выходе и-го из П 21 - 2формируется код зхп-функции, поступающий на соответствующий вход К 9.Принцип действия устр-ва основан натом, что зп-ступенчатый сигнал получают последовательным считываниемсдвинутых по фазе на Я/И выборок зпфункции, формируемых в2, - 2ды, соответствующие значениям эвыборок, подаются на И входов ХПри изменении кода фазы значения выборок на выходах П 2, - 2 )изменяются. Но сдвиг фаз между сигналами, коды к-рых формируются на выходах П2 1 - 2 с двумя соседними номерами,остается равным и/И, 5 ил.Изобретение относится к радиоэлектронике и может быть использовано дляформирования сигналов с заданным законом изменения фазы, в.частности, вкалибраторах фазы, синтезаторах часчастот, синтезаторах с полиномиальнымзаконом изменения частоты.Цель изобретения - повышение точности формирования заданного закона 10изменения фазы выходного сигнала.На Фиг. 1 изображена структурнаяэлектрическая схема предлагаемогоформирователя сигналов с заданным законом изменения Фазы; на фиг. 2 - ,примеры реализации .блока формированиякода фазы; на фиг, .3 - примеры реализации блока формирования сигналовуправления; на фиг. 4 - примеры реализации формирователя модулирующих 20сигналов; на фиг. 5 - диаграммы исходных двухуровневых сигналовФормирователь сигналов с заданнымзаконом изменения фазы содержит блокформирования кода фазы, И преобразователей кода 2 - 2 я, опорный генератор 3, первый регистр 4 памяти, первый цифроаналоговый преобразователь (ЦАП) 5, фильтр 6 нижних частот.(ФНЧ), делитель 7 частоты, блок 8 30 формирования сигналов управления, первый 9 и второй 10 коммутаторы, первый 11 и второй 1 2 блоки инверторов, третий 13 и четвертый 14 коммутаторы, второй. регистр 15 памяти, второй Б/Л 16, формирователь 17 модулирующих сигналов, Фазовый детектор18, сумматор 19, перестраиваемый фильтр 2 О.40Блок 1 формирования кода фазы(фиг, 2 а) содержит блок 21 переключателей. Блок 1 формирования кода фазы (фиг. 2 б) содержит блок 21 переключателей и накопитель 22 кода фазы. Блок 1 формирования кода Фазы (Фиг. 2 в) соцержит блок 21 переключателей, накопитель 22 кода фазы, комбинационный сумматор 23, накопитель 24 кода частоты, управляемый инвертор 25, триггер 26 и ждущий мультивибратор 27Блок 8 формирования сигналов управления (фиг. За) содержит первый 28 и второй 29 реверсивные счетчики, делитель ЗР частоты, первый 31, второй 32 и третий 33 элементы ИСКЛЮЧАЮЩЕЕ55 ИЛИ, Блок 8 формирования сигналов управления (фиг. Зб) содержит первый реверсинный счетчик 28, первый 31, второй 32 и третий 33 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,Формирователь 17 модулирующих сигналов (фиг. 4 а) содержит цифроаналоговый преобразователь (ЦАП) 34, формирователь 17 модулирующих сигналов (фиг. 4 б) содержит ЦАП 34, дополнительный ЦАП 35, интегратор 36 и суммагор 37.Формирователь сигналов с заданным законом изменения фазы работает следующим образом.В каждом с-м такте опорного генератора 3 на выходе делителя 7 частоты с коэффициентом деления с возникает импульс, который поступает на тактовый вход блока 1 формирования кода фазы, на первом кодовом выходе которого формируется код Фазы у(без старшего разряда), поступающий далее на входы преобразователей 2, - 2ко да, где И - четное. На выходе п-го из М преобразователей 2- 2 я кода Формируется код скнусоидальной функ- ции Йп) 1= зхп д+ --и = 1, 2. который поступает на соответствующийвход коммутатора 9. Частота Р каждойиз этих синусоидальных функций определяется выражением Кг ГопР0 Ч(2) где Я - емкость накопителя;Г- частота сигнала опорного генератора 3;К- код частоты, поступающий сблока 21 переключателей блока1 формирования кода фазы,Частота Е /Ч является тактовой частотой накопителя 22 кода Фазы и накопителя 24 кода частоты.Принцип действия формирователя сигнала с заданным законом изменения фазы основан на том, что синусоидальный ступенчатый сигнал получают последовательным считыванием сдвинутых по фазе на 7/И выборок синусоидальной функции, формируемых в преобразователях 2, - 2 я кода. Коды, соответствующие значениям этих выборок, поцаются на М входов коммутатора 9, один из которых на определенное время подключается к его выходу. При изменении кода фазы значения выборок на выходах всех преобразователей 2, - 2кода изменяются, но в любом случае сдвиг фаз между сигналами, коды которых5 формируются на выходах преобразователей кода 2- 2кода с двумя соседними номерами, остается равным 7(/И. Таким образом, код на выходе коммутатора 9 пробегает И значений, соответствующих фазам от 0 до 180 с шагом Я/И, Код, соответствующий фазам от 180 до 360 , формируется на выходе коммутатора 13 путем инвертирования в необходимые моменты времени кода, соответствующего фазам 0 - 180Коммутатор 9, блок 11 инверторов, коммутатор 13, регистр 4 памяти, ЦАП 5 образуют первый канал, а коммутатор 20 10, блок 12 инверторов, коммутатор 14, регистр 15 памяти и ЦАП 16 - второй канал, находящийся с первым строго в квадратуре за счет соответствующего подключения входов коммутаторов 9 и 10 к выходам преобразователей 2 - 2н кода. Наличие квадратурных каналов необходимо для нормальной работы фазового детектора 18.При линейном изменении кода фазы (на выходе блока 1 он пилообразный) частота сигнала на выходе первого и второго квадратурных каналов становится либо больше, либо меньше несущей частоты, равной Е/Ч, и определяется выражением 35(3)В выражении (3) плюс относится кположительным приращениям фазы, а минус - к отрицательным.При суммировании периодическихсигналов, входящих в 2 И-фазную систему и умноженных на соответствующие 45синусоидальные ФУнкции Фазы , такжеобразующие 2 И-фазную систему, резуль-тат содержит члены, зависящие толькоот разностей или только отсумм полных Фаз составляющих периодическогосигнала и фазы у . Любой периодическийсигнал без постоянной составляющей счастотой ы может быть записан в виде ряда ФурьеП = Ч С.(азпКы + ЬсозКцс) (4)55к:1В 2 И-фазную систему сигналов, .кроме (4), входят также сигналы+ Ьзп(ЕЯ У)3 (6) При смене знака перед Й(п)/М разность КыС -в (6) заменяется суммой Кы + ч"При постоянном значенииустройство, реализующее алгоритм (6), выполняет функцию фазовращателя, при линейно изменяющейся Фазе - синтезатора частот, при более сложном законе изменения Фазы - синтезатора сигналов.В предлагаемом формирователе сигналов с заданным законом изменения фазы (фиг. 1) в качестве 2 М-фазной системы исходных периодических сигналов используются дискретные двухуровневые сигналы (фиг. 5), период которых разбит на 2 И равных интервалов: 1 при (т+и)тос 12 М = 0;1 0 при других тпгде щ=0,1, - порядковый номеринтервала;(ш+п)тод 2 М - операция вычислениясуммы по модулю 2 И,В системе сигналов (7) в любой момент времени отличен от нуля (т.е.равен 1) лишь один из сигналов, чтодает возможность реализовать алгоритм (6), последовательно передаваяна выход коммутаторов 9 и 10 соответствующие коды 2 И-фазной системы синусоидальных функций фазы (1),Импульсы опорного генератора 3 счастотой, в. И раз большей, чем требуемая частотаисходных периодическихсигналов, поступают на счетный входреверсивного счетчика 28 блока 8 помодулю И и чрез делитепь 30 частотыс коэффициентом деления И/2 - на реверсивный счетчик 29 по модулю 4, Направление счета определяется сигналом на входах установки режима реверсивных счетчиков 28 и 29, формируемого одновременно с кодом Фазы в блоке1 формирования кода Фазы и поступающего с третьего кодового выхода блока 1 формирования кода фазы, Двоичный код числа с выхода реверсивногосчетчика 28 поступает на управляющие входы коммутаторов 9 и 10, навыходы которых при этом поступает кодс И-(т)шоЙИ 3"го информационного входа, При этом сигнал код которого по"10является на выходе коммутатора 10,в разные моменты времени может отставать или опережать по фазе на 90сигнал, код которого появляется навыходе коммутатора 9.15Это происходит потому, что в предлагаемом устройстве используется 2 МФазная система, а число преобразователей кода равно М. Недостающие ЯФаз можно получить инвертированием 20кодов, идущих с выхода преобразователей 2, - 2 кода. Однако инвертирование можно также осуществить и после коммутаторов 9 и 10, что и сделано в предлагаемом формирователе сигналов с заданным законом измененияфазы. При этом число входов каждогоиз коммутаторов 9 и 10 сокращаетсявдвое и равно И,Сигна., управляющий такой инверсией в первом квадратурном канале,Формируется на выходе старшего разряда реверсивного счетчика 29 блока8, а во втором квадратурном канале -на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31.Для сокращения разрядности каждо-.го из преобразователей кода 2- 2кода преобразование осуществляется,для кодов, соответствующих фазам 0 -180, а для фаз 180 - 360 берутсяинвертированные коды диапазона 0 -180 . Управление этой инверсией осуществляется старшим разрядом кода фазы, который входит в третий кодовыйвыход блока 1 формиования кода Фазыи поступает на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 32 и 33 блока 8,минуя преобразователи 2, - 2 я кода икоммутаторы 9 и 10,Таким образом, инверсия осуществляется как по сигналу с выходов реверсивного счетчика 29 блока 8, так ипо сигналу со старшего разряда кодаФазы блока 1, а преобразование этихсигналов в управляющие сигналы, пос"тупающие на первый и второй выход. 55блока 1, производится в соответствующем образом включенных элементах ИСКЛЮЧА 10 ЩЕЕ ИЛИ 31-33. Инверсия кодов непосредственно осуществляется в блоках 11 и 12 инвесторов, а сигналь,управляющие инверсией, поступают науправляющие входы коммутаторов 13и 14. С выхода каждого из ннх поступает либо прямой, либо инвертированныи код.В первом квадратурном канале сигнал управления инверсией, поступающийс выхода блока 8, является также старшим разрядом кода сигнала и поступаетна вход старшего разряда регистра 4памяти. То же самое происходит и вовтором квадратурном канале (сигнал свыхода блока 8 поступает на входстаршего разряда регистра 15 памяти.В случае, если число преобразова"телей 2, - 2кодов является степеньюдвойки, т.е. Х = 2, р = 2,3,4,блок 8 упрощается: реверсивный счетчик 28 становится двоичным и можнообъединить функции реверсивных счет-чиков 28 и 29 и делителя 30 частоты,как показано на фиг. Зб. В этом случае реверсивный счетчик 28 имеет емкость 2 , а один из входов элементаИСКЛЮЧАЮЩЕЕ ИЛИ 33 и один из входовэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31 соединены с выхвдом р-го разряда реверсивного счетчика 28. Другой вход элементаИСКЛЮЧАЮЩЕЕ ИЛИ 3 соединен с выходом(р)-го разряда реверсивного счетчика 28,Импульс с выхода опорного генератора 3, поступающий на тактовые входы регистров 4 и 15 памяти, осуществляет запись в них кодов соответственно первого квадратурного канала свыхода коммутатора 13 и второго квадратурного канала с выхода коммутатора 14. На выходе ЦАП 5 и 16 Формируются напряжения, пропорциональные записанным кодам. Таким образом, раз"ность Фаз между сигналами на выходепервого квадратурного канала (выходЦАП 5) и второго квадратурнога канала (выход ЦАП 16) равна 90, Сигналс выхода первого квадратурного каналапоступает на нерестраиваемый Фильтр20.Перестраиваемьй фильтр 20 охваченкольцом автоподстройки Фазы, котороесостоит из Фазового детектора 18,Фильтра 6 и сумматора 19. Для работыФазового детектора 18 необходимо,чтобы сдвиг фаз между сигналами на еговходах был равен 90 . Поэтому на еговторой вход подается сигнал с выхода1385239 7перестраиваемого Фильтра 20, а на, первый вход. - с выхода второго квадратурного канала. Поскольку выходной сигнал перестраиваемога Фильтра 205 при совпадении частоты настройки с частотой сигнала имеет ту же фазу, что и сигнал на его входе, сигналы на входах Фазового детектора 18 сдвинуты меду собой па Фазе на 900 Пе рестраиваемый Фильтр 20 управляется напряжением, которое является суммой напряжений с выхода формирователя 17 и напряжения фазовой ошибки с выхода Фазового детектора 18, Так как напряжение грубой перестройки .мало отличается От требуемого напряжения управления, амплитуда напряжения сигнала ошибки мала и, следовательно, фазовый детектор 18 работает на линейном участке характеристики.Формирователь 17 модулирующих сигналов в случае использования формирователя сигналов с заданным законом изменения фазы в качестве синтезато ра частот представляет собой ЦАП 34, на вход которого подается код частоты (фиг. 4 а), а в случае использования устройства в качестве синтезатора линейно-частатно-модулированных .30 (ЛЧМ) сигналов представляет собой сумматор 37, один вход которого подключен к выходу ЦАП 34, на вход которого подается код начальной частоты, а другой вход подключен к интегратору 36 со сбросом, на который подается с ЦАП 35, на вход которого подается код скорости (Фиг. 46).На вход сброса чнтегратора 36 подается сигнал с выхода ждущего культивибраторя 27, формирующего импульс40 сброса по сигналу с выхода триггера 26 блока 1.Блок 1 Формирования кода фазы при использовании устройства в качестве фазовращателя может быть выполнен, например, в виде блока 21 переключа"телей (Фиг. 2 а) каждый на два положения в одном из которых на соответствующий выход блока поступает напряжение "0", а в другом - "1". Меняя положение переключателей блока 21 переключателей, можно формировать различные коды фазы, Сигнал а знаке сдвига Фазы поступает с соответствующего переключателя блока 21 переклю чателей по третьему кодовому выходу. Блок 1 Формирования кода фазы при использовании устройства в качестве синтезатора частот может быть выполнен на основе накопителя 22 кода Фазы (фиг, 26). С каждым тактовым импульсам к коду, записяннаму в нгкапителе 22 кода фязь 1, прибавляется кад,установленный на блоке 21 переключателей, в результате чего ня выхацеФормируется линей,с нарастающий кадФазы, соответствующий гр -буемому отклонению синтезируемай и искацнайчастот. Сигнал о знаке отклонения поступает с соответствующего переключателя блока 21 переключателей и вместе с сигналом, идущим са тяршега разряда накопителя 22, ан наступает на третий кодовый выход блока 1 формирования каца фгзы, Код чястат:, установленный на блоке 21 переключяте - лей, поступает на второй кадавы вы - хад блока 1 Формирования када фязь. Кад с выхода накопителя 2" поступает на первый выход блока 1 Формирования кода Фазы,Прч использовании устройства в качестве синтезатора ЛЧМ (Фиг, в) сиг= налав В накопителе 2 ч кала частоты входящем в состав блакя 1 формирования кода Фазы, формируется .инейча изменяющийся кац частоты. та". кац СуММИруЕтея С Кадош НяЧяЛЬНОй Чяара ты, поступающим с блакя 21 переклю-. чателей в камбиняц.;к ннам сумматс ре 23. В накопителе 22 кадя Фазы Формируется кад фазы .1 РМ с;гнала, и,м ня - ющийся па пяряб Оличе скам 1 закан; При зтам сигнал са стяршега рязряця бинацианнага сумматора 23:-,аступяет ня триггер 26, я с выходяга - ня вхац угравления управляемага инвертаря 25. Кроме тара, О-. вместе с сигналом са стряшсга рязряця някапителя 22 кода фязь наступает ня ре" тий кодовый вьглад блакя 1 Формирования кода фазы.Если при сигняле с выхаця тригге ра 26, равном 0", Обеспе-.ивяется ин - вертиравание упрявляемь.м инвертарам 25 всех разрядов кода Фязь, кроме старшего, и режим сложения в ревер - сивных счетчиках 28 и 29. я при сигнале "1" - прямое прапускяние и режим вычитания соответственна, та тогда реализуется возрастающий закон линейной частотной модуляции,Для получения падающего зяканя необходима при сигнале "О в старшем разряде комбинационного сумматора 23 обеспечить прямое прсхаси 1 е астяль 1385239ных разрядов через управляемый инвертор 25 и режим вычитания реверсивныхсчетчиков 28 и 29, а при сигнале "1" -инвертирование и режим сложения соот 5ветственно.На выходе; триггера 26 формируется перепад, означающий окончание ЛЧМсигнала. По этому перепаду Формируется узкий импульс в ждущем мультивибраторе 27, являющийся сигналом сброса в "О" интегратора 36. Этот сигналпоступает на второй кодовый выходблока 1 формирования кода фазы наряду с кодом начальной частоты и кодомскорости, идущих с блока 21 переключателей,Преобразователи 2, - 2 кода могутбыть, например"выполнены на основепостоянного запоминающего устройства(ПЗУ) соответствующего объема,Формирователь сигналов с заданнымзаконом изменения Фазы. осуществляетперенос сигнала, сформированного нанизкой частоте, на несущую частоту,что позволяет максимально использовать разрядную сетку блока 1 формирования кода Фазы и преобразователей2, - 2 кода и снизить требования кбыстродействию этих узловПереносна несущую частоту осуществляется цифровыми методами, причем используетсялишь один канал Формирования, а второй канал является вспомогательньи,обеспе .-иьающим нормальную работу Фа"зового детектора 18,Следящий фильтр, состоящий из перестраиваемого Фильтра 20 и цепи автоподстройки Фазы,не вносит Фазовогосдвига между его входом и выходом,а второй квадратурный канал, необходимый для нормальной работы фазовогодетектора 18, идентичен первому квадратурному каналу.Следящий фильтр имеет значительно45сниженный размах напряжения на выходе. Это достигается тем, что Фазовымдетектором 18 Формируется не все напряжение, управляюцее перестраиваемымфильтром 2 О, а только напряжение сигнала ошибки, которое значительно меньше напряжения грубой перестройки,поступающего с выхода Формирователя17 модулирующих сигналов. При этомФазовый детектор 18 работает на лиГ .,нейном участке характеристики. Кроме Р-того, приняты меры, обеспечивающиеточный 90-градусньй сдвиг Фаз междуквадратурными каналами,Формула изобретения Формирователь сигналов с заданным законом изменения Фазы, содержащий последовательно соединенные опорный генератор и делитель частоты, выход которого соединен с тактовым входом блока Формирования кода Фазы, И преобразователей кода, входы которых со-. единены с первым кодовым выходом блока формирования, кода Фазы, а выходы первого, второго И-го преобразователей кода соединены соответственно с первым, вторым,.ь И-м сигнальными входами первого коммутатора, последовательно соединенные первый регистр памяти, тактовый вход которого соединен с выходом опорного генератора, и первый цифроаналоговый преобразователь, а также фильтр нижних частот, о т л и ч а ю щ и йс я тем, что, с целью повышения точности формирования заданного закона изменения фазы выходного сигнала, в него введены второй коммутатор, первый, второй, ,Н/2-й сигнальные входы котсрогс соединены соответственно с выходами (И/2+1)-го, (И/2+2)-го М-го пре" образователей кода, а (И/2+1)-й, (И/2+2)-й М-й сигнальнье входы соответственно с выходами первого, второго Б/2-го преобразователей кода, где Ы - четное число, третий коммутатор, первый сигнальный вход кокоторого соединен с выходом первого коммутатора, а выход - с входом млад- ших разрядов первого регистра памяти, первый блок инверторов, который включен между выходом первого Коммутатора и вторым сигнальным входом третьего коммутатора, четвертый коммутатор, первьп сигнальный вход которого соелдинен с выходом второго коммутатора, второй блок инвертора, который включен между выходом второго коммутатора и вторым сигнальным входом четвертого коммутатора, последовате:.ьно соединенные второй регистр памяти, вход младших разрядов котсрого соединен с. выходом четвертого коммутатора второй цифроаналоговый преобразователь и Фазовый детектор, вьход которого соединен с вхопом Фильтра нижних частот, пере; траиваемый Фильтр, сигнальпай вход которого. соедин:н с выходом первого цифроаналогового преобразователя, а выход - с вторым входом фазового детектора., сумма.:ор, первый входкоторого соединен с выходом фильтранижних частот, а выход - с управляющим входом перестраиваемого фильтра,формирователь модулирующих сигналов,вход которого соединен с вторым кодовым выходом блока Формирования кода фазы, а выход - с вторым входомсумматора, блок формирования сигналов управления, счетный вход которого соединен с выходом опорного генератора, сигнальный вход - с третьимкодовым выходом блока формированиякода фазы, первый выход сигнала управления инверсией - с управляющим входом третьего коммутатора и входомстаршего разряда первого регистра памяти, второй выход сигнала управления инверсией - с управляющим входом четвертого коммутатора и входом старшего разряда второго раппства памяти, а кодовый выход - с управляющими входами первого и второго коммутаторов,при этом тактовый вхо второго регистра памяти соединен с вьгховом опорного генератора; а выход лерестраиваемого фильтра является выходом формирователя сигналов с эаданньги закономизменения фазы,1 385239 Составитель Г. ЗахарченКопча Техред М. Хода нич Редакт рректор В, Бутяг аз 1419/ одписно НИИП л 113035, Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,Тираж 928 Гс судар ств енно го елам изобретений сква, Ж, Раушс митета СССРоткрытийя наб., д, 4/5

СмотретьЗаявка

4149421, 20.11.1986

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

КОЧЕМАСОВ ВИКТОР НЕОФИДОВИЧ, ЖАРОВ АЛЕКСЕЙ НИКОЛАЕВИЧ, РАКОВ ИГОРЬ АРЬЕВИЧ, РЕВУН АЛЕКСАНДР ДМИТРИЕВИЧ, СОБОЛЕВ АЛЕКСАНДР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H03C 3/00

Метки: заданным, законом, изменения, сигналов, фазы, формирователь

Опубликовано: 30.03.1988

Код ссылки

<a href="https://patents.su/9-1385239-formirovatel-signalov-s-zadannym-zakonom-izmeneniya-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов с заданным законом изменения фазы</a>

Предыдущий патент: Формирователь сигналов с заданным законом изменения фазы

Следующий патент: Кварцевый частотный модулятор

Случайный патент: Бетонная смесь