Цифровой демодулятор частотно-манипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1058083

Автор: Романов

Текст

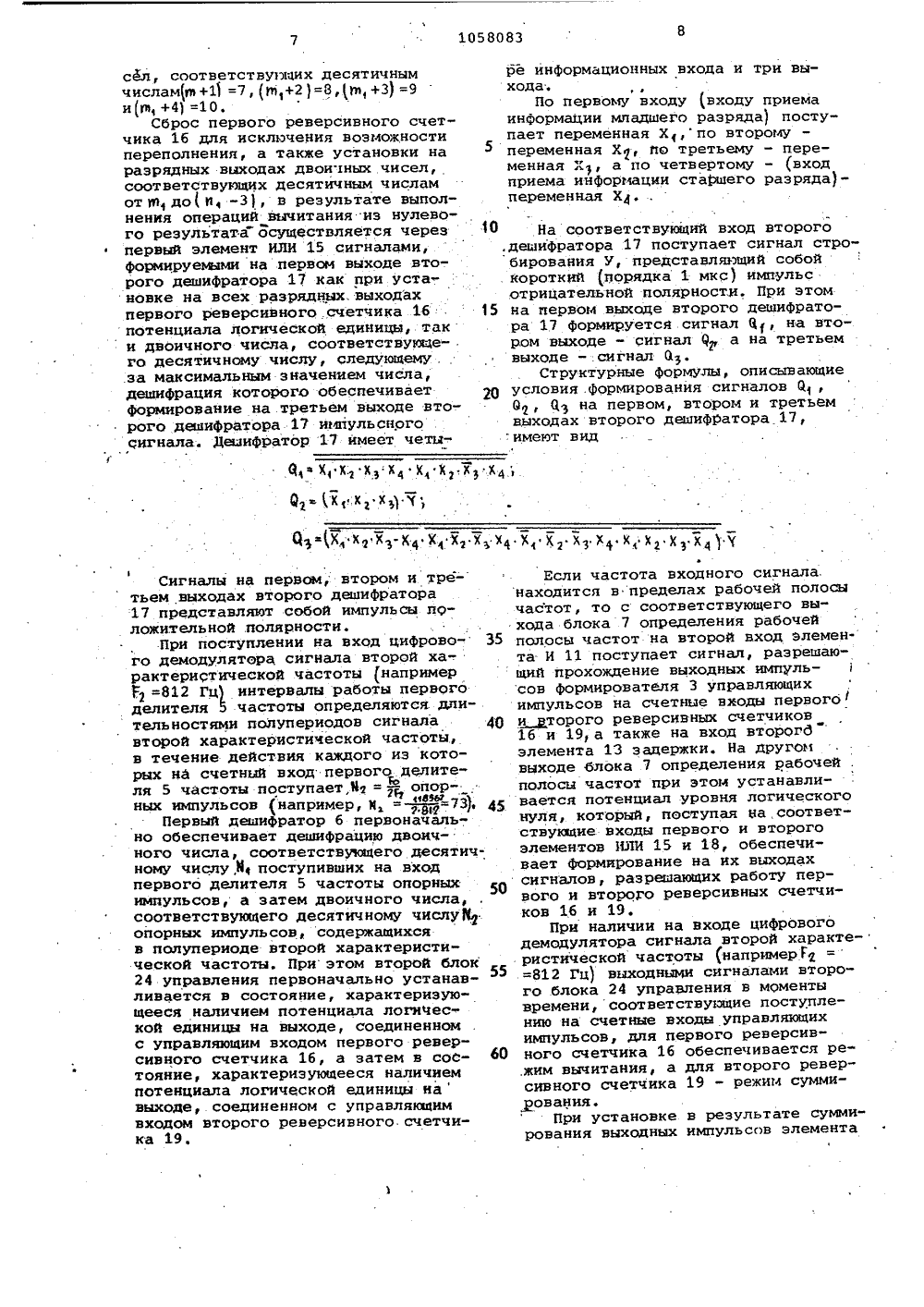

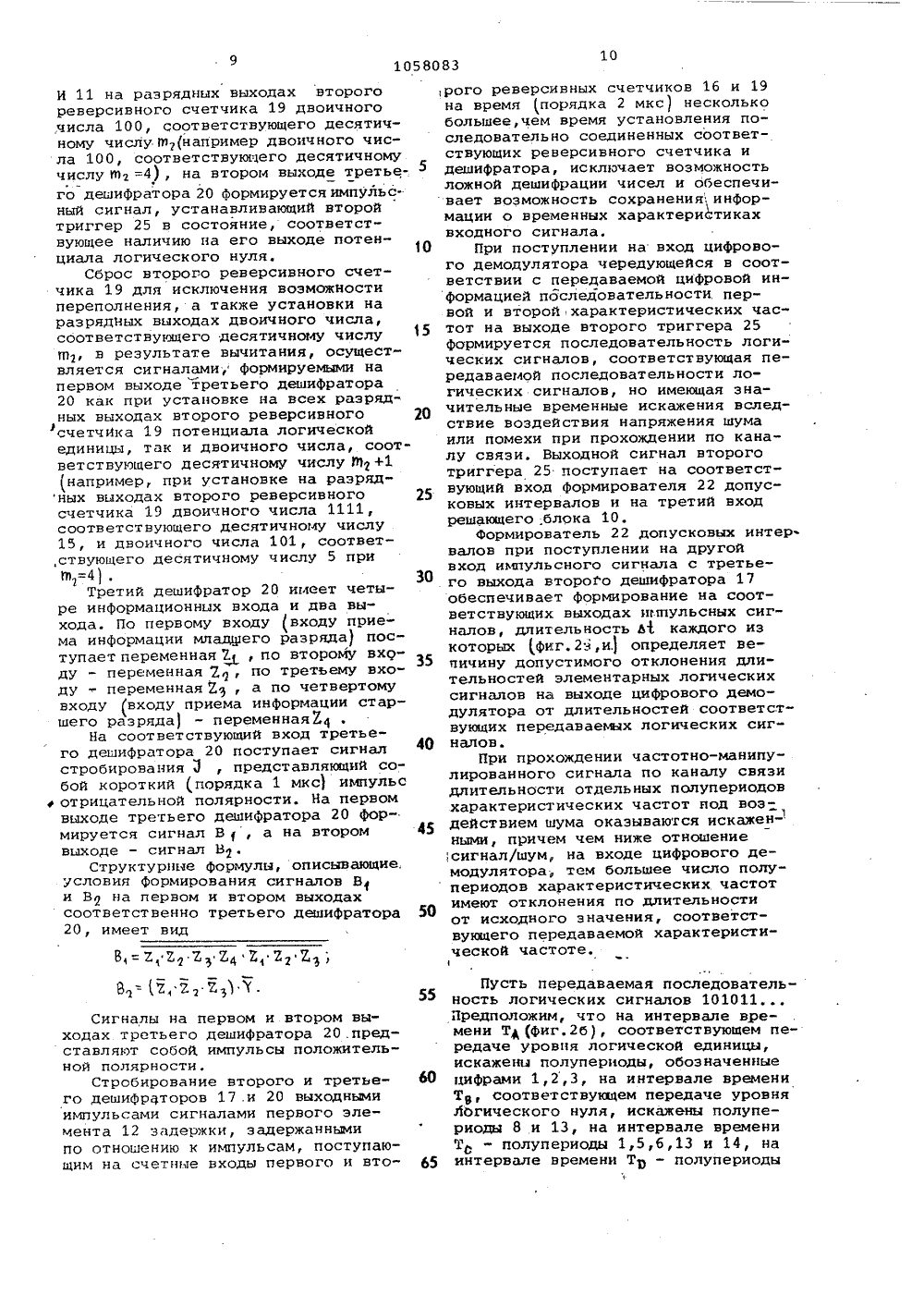

(19) (11) Ь 27 14 ЕТ ЕЛЬСТВ ДАРСТВЕННЫЙ КОМИТЕТ СССРЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ АВТОРСКОМУ СВ(56) 1. Патент франции Р 2266982,кл. Н 03 К 9/06, 1975.2. Авторское свидетельство СССРМ 545091, кл. Н 04 Ь 27/10, 1974(54)(57) ЦИФРОВОЙ ДЕМОДУЛЯТОР ЧАС. ТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ,содержащий редающий блок, последовательно аоединениые полосовойфильтр, ограничитель и Формирователь управляющих импульсов, генератор опорных импульсов, выход которого подключен к первому входу первого делителя частоты, выходи которого соединены с входами первогодешифратора и блока определениярабочей полосы частот, о т л ич а ю щ и й с я тем, что, с цельюповьааения точности демодуляции, вве.дены анализатор амплитуды, элемент, И, два элемента задержки, два блокауправления, два элемента ИЛИ, двареверсивных начетчика, второй и тре-тий дешифраторы, два триггера, Формирователь допусковых интервалов,блок сравнения и второй делительчастоты, первый вход и выход которого соединены соответственно с выходом генератора опорных импульсови с первым входом блока сравнения,вМходы которого подключены к входампервого блока управления, выходыкоторого соединены с вторыми третьимвходами второго делителя частбты,четвертый вход которого соединенс выходом первого триггера и с первым входом реыающего блока, второйи третий входы которого соединенысоответственно с выходом второго делителя частоты и с выходом второготриггера, который соединен с первым входом Формирователя допусковых.интервалов, первый выход которогоподключен к второму входу блока сравнения, третий вход которого соединенс вторым выходом Формирователя допусковых интервалов и с первым входомпервого триггера, второй вход которого соединен с выходом анализатораамплитуды, к входу которого пОдключен выход полосового фильтра, и спервым входом элемента И, второй итретий входы которого соединены соответственнО с первым выходом блокаопределения рабочей полосы частоти с выходом формирователя управляю.щих импульсов, который соединен свходом первого элемента задержки, ни-эход которого подключен к второмувходу первого делителя частоты, приэтом второй виход блока определениярабочей полосы частот подключен к первым входам первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с первыми выходами второго и третьего деыифраторов, входы которых соединены соответственно с выходами первого и вто 1 рого реверсивних счетчиков, первыевходи которых соединены соответст,венно с выходами первого и второго1элементов ИЛИ, а выход элемента Иподключен к вторым входам первогои второго реверсивных счетчиков,к третьим входам которых подключены выходы второго блока управления,и к входу второго элемента задержки, выход которого подключен к соответствующим входам второго и тре- фртьего дешифраторов, вторые выходыкоторых подключены к входам второготриггера, причем выходы первогодешифратора соединены с входамивторого блока управления, третийвыход второго дешифратора подключенк второму входу формирователя донусковых интервалов.Изобретение относится к техникесвязи и может использоваться дляприема дискретной информации в уст.ройствах телеуправления, телеконтроля и системах. передачи кодированных сообщений,Известен демодулятор волн, модулированных,по частоте, для системпередачи двоичной информации, содержащий полоссвой Фильтр, амплитудный ограничитель, Формировательимпульсов, генератор стабильных импульсов, порогоное устройство, счетчик, запоминающее устройство и цифроаналЬговый преобразователь 11 .Однако устройство не обладает высокой помехоустойчивостью, так какпри обработке сигнала в цифроаналоговом преобразователе не определяется какой полосе частот принадлекит обрабатываемый сигнал.Наиболее близким по техническойсущности к предлагаемому являетсяцифровой демодулятор частотно-манипулированных сигналов, содержащийрешающий блок, последовательносоединенные полосовой фильтр, ограничитель и формирователь управляющих импульсов, генератор опорныхимпульсов, выход которого подключен к первому входу первого делителя частоты, выходы которого соединены с входами первого дешифратораи блока определения рабочей полосычастот 2 .Недостаток известного демодуля-тора - низкая точность демодуляции.Цель изобретения - повыаение точности демодуляции.Для достижения поставленной цели в цифровой демодулятор частотноманипулированных сигналов, содержащий решающий блок, последовательно соединенные полосовой фильтр,ограничитель и формирователь упранляющих импульсов, генератор. опорных импульсов, выход которого подключен к первому входу первого делителя частоты, выходы которого соединены с нходами первого дешифратора и блока определения рабочей полосы частот, введены анализаторамплитуды, элемент И, два элементазадергкки, два блока управления,два элемента ИЛИ, два реверсивныхсчетчика, второй и третий дешифраторы, дна триггера, Формировательдопусковых интервалов, блок сравне-.ния и второй делитель частоты, первый вход и выход которого соединенысоответственно с выходом генератораопорных импульсов и с первым входомблока сравнения, выходы которого подключены к входам первого блока управления, выходы которого соединеныс вторым и третьим входами второгоделителя частоты, четвертый вход которого соедин".н с выходом первого триггера и с первым входом решающегоблока, второй и третий входы которогосоединены соответственно с выходомвторого делителя частоты и с выходомвторого триггера, который соединен 5 с первым входом формиронателя допусковых интервалов, первый выход кото.рого подключен к второму входу блокасравнения, третий вход которого соединен с вторым выходом Формировате ля допусконых интервалов. и с первымвходом первого триггера, второй входкоторого соединен с выходом анализатора амплитуды, к входу которогоподключен выход полосового фильтра,и с первым входом элемента И, второйи третий входы которого соединенысоответственно с первым выходом блока определения рабочей полосы частоти с выходом Формирователя управляющихимпульсов который соединен с входомпервого элемента задержки, выходкоторого подключен к второму входупервого делителя частоты, при этомвторой выход блока определения рабочей полосы частот подключен к первым нходам первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с первыми выходами второго и третьего дешифраторов,входы которых. соединены соответстЗ 0 венно с выходами первого и второгореверсинных счетчиков, первые входыкоторых соединены соответственновыходами первого и второго элементов ИЛИ, а выход элемента И подклю чен к вторым входам первого и второгореверсивных счетчиков, к третьимвходам которых подключены выходывторого блока управления, и к входувторого элемента задержки, выход 40 которого подключен к соответствующимвходам второго и третьего дешифраторов, вторые выходы которых подклю,чены к входам второго триггера, причем выходы первого дешифратора соединены с входами второго блока управления, третий выход второго дешифратора. подключен к второму входуФермирователя допусконых интервалов.На Фиг.1 представлена структурная электрическая схема демодулято ра; на Фиг,2 - эпюры напряжений,поясняющие его работу..-МДемодулятор содержит полосовойфильтр 1, ограничитель 2, формирователь 3 управляющих импульсов, генератор 4 опорных импульсов, первыйделитель 5 частоты, первый дешифратор 6, блок 7 определения рабочейполосы частот, анализатор 8 амплитуды, второй делитель 9 частоты, решающий блок 10, элемент И 11, первыйи второй элементы 12 и 13 задержки,соответственно, первый бЛок 14 управления первый элемент ИЛИ 15,первый реверсинный счетчик 16,второй дешифратор 17 стробирующего на соответствующий вход второгс ,блока 24 управления. При этом второй блок 24 управления устанавливается в состояние, соответствующее наличию на выходе, соединенном с управляющим входомфпервого реверсивного счетчика 16, потенциала логической единицы (Фиг,2 д), а на выходе,соедйнен- номс управляющим входом второго ре версивного счетчика 19, потенциала логического нуля.Если частота входного сигнала находится в пределах рабочей полосы частот, с соответствующего выхода блока 7 определения рабочей полосы, частот, на второй вход эле-. 15 мента И 11 поступает сигнал уровня логической единицы, разрешающий прохождение выходных импульсов Формирователя 3 управляющих импульсов на счетные входы первого и второго реверсивных счетчиков .16 и 19 а также на вход второго элемента 13 задержки. На другом выходе блока 7 определения рабочей полосы частот, .при этом устанавливается 25 потенциал уровня логического нуля, наличие которого на соответствующих входах первого и второго элементов ИЛИ 15 и 18 разрешает работу первого и:второго .реверсивных счетчиков 16 и 19.Так как соответствующими выходными сигналами второго блока 24 управления для первого реверсивного счетчика 16 обеспечивается режим суммирования, а для второго реверсивного счетчика 19 - режим вычитания, то в первом реверсивном счетчике 16 производится суммирование импульсов, поступающих на его счетный вход с выхода элемента И 11, 40 а во втором реверсивном счетчике 19 - вычитание.При установке на разрядных выходах первого реверсивного счетчика 16 логических сигналов, характе ризующих двоичное число 110, соответствующее десятичному числу П 11(например двоичное число 110, соответствующее десятичному числу Ю 1=6), и поступлении на вход второго дешифратора 17 стробирующего импульса на втором выходе второго дешифратора 17 формируется импульсный сигнал, устанавливающий второй триггер 25 в состояние, соответствующее наличию на его выходе потенциала логической единицы (Фиг.2 е).Число М, определяется из условия3+14 Ф с 01-Йгде 01 - число полупериодов первой характеристической частоты Р 1, содержащихся в интервале времени, соответствующем длительности Т р одного разряда цифровой информации передаваемой последовательности логических сигналов. 1,058083 бНапример, при 3 = 3 и л, =17 числов,может быть выбрано из ряда целыхположительных чисел от 4 до 15, Кроме того, число в определяющее количество накопленной информации о числе неискаженныхполупериодов первойхарактеристической частоты, поступивших на вход цифрового демодулятора,выбираетсяиз ряда целых чисел от(6+1) до( П,-2) с учетом необходимойпомехоустойчивости цифрового демодулятооа и соеднего значения отношения сигнал/шум на входе.;Так, напойиео, при высоких отношениях сигнал/шум (порядка 20-;40 дБ) на входе цифрового демодулятора числб .в может быть выбраноравным 4 +1) или близким к этому зна.:чению.При низких отношениях сигнал/шум (порядка 1-4 дБ) на.:входе цифрового демодулятора число Ф,можетбыть выбрано равным (и,-2) или близким к этому значению, однако приэтом задержка выходного сигналацифрового демодулятора, определяемая выбранным значением числа %1также значительна.ИмпульСные сигналы на третьемвыходе второго дешифратора 17(фиг.2 ж) при наличии на дополнительном входе стробирующих импульсов формируются при установке на разрядныхвыходах первого реверсивного счетчика 16 логических сигналов, характеризующих одно илн ряд последовательных двоичных чисел, соответствующихдесятичным числам, которые могутпринимать значения от (а,+1) до ( й,-3) .Число последовательнйх чисел, дешифрация которых обеспечивает формирование на третьел выходе второгодешифратора 17 импульсных сигналов,определяется на основании значенияотношения, сигнал/шум на входе цифрового демодулятора. Так, например,при высоких отношениях сигнал/шум(порядка 20-40 дГ) на входе цифрового демодулятора необходимым и достаточным условием формирования импульсного сигнала на третьем выходевторого дешифратора 17 является дешифрация двоичного числа, соответствующего десятичному числу(е,+1),При.низких отначениях сигнал/шум(порядка 1-40 дБ) на входе цифровогодемодулятора.с целью увеличения вероятности формирования по крайнеймере одного импульсного сигнала натретьем выходе второго дешифратора17 в качестве условия формированиясигналов выбирается дешифрация ряда чисел от(я+1) до (и) . Например,при отношении сигнал/иум на входецифрового демодулятора порядка 4 дБ,В=6, и й;=17, в качестве условияформирования сигналов на третьемвыходе второго дешифратора 17 можетбыть выбрана дешифрация двоичных чн1058083 10 На соответствующий вход второго,дешифратора 17 поступает сигнал стробирования У, представляющий собойкороткий порядка 1 мкс импульсотрицательной полярности. При этом 15 на первом выходе второго дешифратора 17 формируется сигнал Я 1, на втором выходе - сигнал Ц, а на третьемвыходе в .сигнал 03.Структурные формулы, описывающие р условия формирования сигналов Я 1,О, Я 3 на первом, вгором и трегьемвыходах второго дешифратора 17,имеют вид Ч 1 ф Х 1 Х 2 ХХ 4 ХХ.Х Х 4 ,9;х,. х, х .ч; 4 ЪХ., Хя Х,- Х, Х, Х,. Х Х,Сигналы на первом, втором и тре-тьем выходах второго дешифратора17 представляют собой импульсы положительной полярности.При поступлении на вход цифрового демодулятора сигнала второй характеристической частоты напримерР =812 Гц) интервалы работы первогоделителя 5 частоты определяются.длительностями цолупериодов сигнала 40второй характеристической частоты,в течение действия каждого из которых на счетный вход первого делителя 5 частоты поступает,йя = - опор% имных импульсов (например Я =-дую=73)е 45Первый дешифратор 6 первоначально обеспечивает дешифрацию двоичного числа, соответствующего десятичному числу,Н поступивших на входпервого делителя 5 частоты опорныхимпульсов, а затем двоичного числа,соответствующего десятичному числуВопорных импульсов, содержащихсяв полупериоде второй характеристической частоты. При этом второй блок24 управления первоначально устанавливается в состояние, характеризующееся наличием потенциала логической единицы на выходе, соединенномс управляющим входом первого реверсивного счетчика 16, а затем в состояние, характеризующееся наличиемпотенциала логической единицы навыходе, соединенном с управляющимвходом второго реверсивного.счетчика 19,сйт, соответствующих десятичным числамза+11 =7, (М +2) =8,ь, +3) =9 и(о+4) =10.Сброс первого реверсивного счегчика 16 для исключения возможности переполнения, а также установки на разрядных выходах двоичных. чисел, соответствующих десятичным числам от Ф 1 до и, -3), в результате выполнения операций вычитания "из нулевого результата осуществляется черезпервый элемент ИЛИ 15 сигналами,формируемыми на первом выходе второго дешифратора 17 как при установке на всех разрядных, выходах первого реверсивного .счетчика 16 потенциала логической единицы, так и двоичного числа, соответствующе-, го десятичному числу, следующему ..эа максимальным значением числа, Дешифрация которого обеспечивает Формирование на третьем выходе второго дешифратора 17 импульсного сигнала. Дешифратор 17 имеет четыре информационных входа и три выхода.По первому входу (входу приема информации младшего разряда) поступает переменная Х,по второму переменная Х, по третьему - переменная Х, а по четвертому - (вход приема информации старшего разряда)- переменная Х 4.ХХ, х х+ Х 1 х,.х,.х 1 уЕсли частота входного сигнала находится в пределах рабочей полосы частот, то с соответствующего выхода блока 7 определения рабочей полосы частот на второй вход элемента И 11 поступает сигнал, разрешающий прохождение выходных импульсов формирователя 3 управляющих импульсов на счетные входы первого и второго реверсивных счетчиков 16 и 19, а также на вход второгд элемента 13 задержки. На другом выходе блока 7 определения рабочей . полосы частот при этом устанавливается потенциал уровня логического нуля, который, поступая на,соответствукиаие входы первого и второго элементов ШП 4 15 и 18, обеспечивает формирование на их выходах сигналов, разрешающих работу первого и второго реверсивных счетчиков 16 и 19.При наличии на входе цифрового демодулятора сигнала второй характеристической частоты напримерГ =812 Гц) выходными сигналами второго блока 24 упраэления в мсменты времени, соответствующие поступлению на счетные входы управляющих импульсов, для первого реверсивного счетчика 16 обеспечивается ре,жим вычитания, а для второго реверсивного счетчика 19 - режим суммирования,При установке в результате суммирования выходных импульсов элемента1 7 "3 4 12в,= %,%,%7.Сигналы на первом и втором выходах третьего дешифратора 20.представляют собой импульсы положительной полярности.Стробирование второго и третьего дешифраторов 17 .и 20 выходными импульсами сигналами первого элемента 12 задержки, задержанными по отношению к импульсам, поступающим на счетные входы первого и вто 65 И 11 на разрядных выходах второго реверсивного счетчика 19 двоичного ,числа 100, соответствующего десятичному числу 1 л(например двоичного числа 100, соответствующего десятичному числу й =4), на втором выходе третьего дешифратора 20 Формируетсяимпульс ный сигнал, устанавливающий второй триггер 25 в состояние, соответствующее наличию на его выходе потенциала логического нуля.Сброс второго реверсивного счетчика 19 для исключения воэможности переполнения, а также установки на разрядных выходах двоичного числа, соответствующего десятичному числу щ, в результате вычитания, осуществляется сигналами, формируемыми на первом выходе третьего дешифратора 20 как при установке на всех разрядных выходах второго реверсивного 20 счетчика 19 потенциала логической единицы, так и двоичного числа, соответствующего десятичному числу Ф +1 например при установке на разрядных выходах второго реверсивного 25 счетчика 19 двоичного числа 1111, соответствующего десятичному числу 15, и двоичного числа 101, соответ,ствующего десятичному числу 5 при В =41, 30Третий дешифратор 20 имеет четыре информационных входа и два выхода. По первому входу входу приема информации младшего разряда) поступает переменная 7., по второму входу - переменная 2, по третьему входу переменная Е, а по четвертому входу входу приема информации старшего разряда) - переменнаяЕ 4На соответствующий вход третьего дешифратора 20 поступает сигнал ф стробирования Э , представляющий собой короткий (порядка 1 мкс) импульс ф отрицательной полярности. На первом выходе третьего дешифратора 20 формируется сигнал В , а на втором 45 выходе - сигнал В.Структурные формулы, описывающие.условия Формирования сигналов В и В на первом и втором выходах соответственно третьего дешифратора 50 20, имеет вид 1 рого реверсивных счетчиков 16 и 19 на время порядка 2 мкс) несколько большее,чем время установления последовательно соединенных соответствующих реверсивного счетчика и дешифратора, исключает возможность ложной дешифрации чисел и обеспечивает возможность сохранения, информации о временных характеристиках входного сигнала.При поступлении на вход цифрового демодулятора чередующейся в соответствии с передаваемой цифровой инФормацией последовательности первой и второй характеристических частот на выходе второго триггера 25 формируется последовательность логических сигналов, соответствующая передаваемой последовательности логических сигналов, но имеющая значительные временные искажения вследствие воздействия напряжения шума или помехи при прохождении по каналу связи. Выходной сигнал второго триггера 25 поступает на соответствующий вход формирователя 22 допусковых интервалов и на третий вход решающего блока 10,Формирователь 22 допусковых интервалов при поступлении на другой вход импульсного сигнала с третьего выхода второго дешифратора 17 обеспечивает формирование на соответствующих выходах импульсных сигналов, длительность Ь 1 каждого из которых фиг,2 э,и, определяет величину допустимого отклонения длительностей элементарных логических сигналов на выходе цифрового демодулятора от длительностей соответствующих передаваемых логических сигналов.При прохождении частотно-манипулированного сигнала по каналу связи длительности отдельных полупериодов характеристических частот под воздействием шума оказываются искаженными, причем чем ниже отношение сигнал/шум на входе цифрового демодулятора тем большее число полу- периодов характеристических частот имеют отклонения по длительности от исходного значения, соответствующего передаваемой характеристической частоте. Пусть передаваемая последовательность логических сигналов 101011Предположим, что на интервале времени Т (фиг. 2 б), соответствующем передаче уровня логической единицы, искажены полупериоды, обозначенные цифрами 1,2,3, на интервале времени Т, соответствующем передаче уровня Логического нуля, искажены полупериоды 8 и 13, на интервале времени Т - полупериоды 1,5,6,13 и 14, на интервале времени Т - полупериоды4 и 12, а на интервале времени ТЕискажения отсутствуют. При приеме такого частотно-манипулированного сигнала, имеющего искажения длительностей полупериодов:характеристических частот, сигнална управляющем входе первого реверсивного счетчика 16 имеет вид, показанный на фиг 2 Д 1 а выходной 10сигнал второго триггера 25 имеетвид, показанный на фиг,2 е, Моментыформирования импульсных сигналовна третьем выходе второго дешифратора 17 определяются поступлением надополнительный вход импульсов стробирования с выхода второго элементазадержки 13, которые имеют постоян. ную задержку по отношению к фронтам .входного сигнала первой характерис -тической частоты. Последнее обстоятельство позволяет йроизводить автоматическую подстройку интерваловследования выходных импульсов второго делителя 9 частоты с целью обеспечения соответствия длительности 25каждого из интервалов длительностиодного разряда Т.передаваемой последовательности логических сигналовиапример, Г д мо)В предлагаемомифровом демодуля. ЗПторе подстройка интервалов следования выходных импульсов втррого делителя 9 частоты производится с помощью формирователя, 22 допусковыхинтервалов, блока 23 сравнения и первого блока 14 управления,Первый импульсный сигнал, формируемый на третьем выходе второго дешифратора 17., от началагпоступленияна вход частотно-манипулированногосигнала обеспечивает запуск Формирователя 22 допусковых интервалов,Так как начало приема частотноманипулированного сигнала характеризуется наличием на выходе анали затора 8 амплитуды потенциала логической единицы фиг.2 в), поступающего на соответствующий вход первого триггера 21, то при поступлении с соответствующего выхода Формирователя 22 допусковых интервалов на другой вход первого триггера 21 импульсного сигнала (Фиг.2 и):первый триггер 21 устанавливается в состояние, характеризующееся наличием на выходе потенциала логической еди ницы (фиг.2 к) . Выходной сигнал первого триггера 21, поступая на. установочный вход второго делителя9 частоты, разрешает его работу.Так как установка первого триг гера 21 в состояние, соответствующее наличию на выходе потенциала логической единицы , производится при приеме сигнала первой характеристической частоты, то передншл 65 фронтом выходного сигнала первоготриггера 21 осуществляется установка решающегоОлока 10 при наличиина третьем входе потенциала логической единицы в состояние, характеризующееся наличием на его выходе потенциала логической единицыфиг.2 л м),Суммарное время задержки формирования на выходе решающего блока 10сигнала логической единицы по отношению к соответствующему фронтусигнала первой характеристическойчастоты без учета задержки, определяемой быстродействием логическихэлементов, может быть определеноиз выражения= + 1,1где аФ, - длительность выходныхимпульсов формирователя 22 допусковых интервалов, определяющая величину допустимого уменьшения периодаследования выходных импульсов второгоделителя 9 частоты,время задержки сигналавторым элементом 13 задержки.Величины Ь 1 и 1 постоянны, поэтомувременные характеристики выходногосигнала решающего блока 10 связаныс временными характеристиками входного частотно-манипулированного сигнала цифрового демодулятора.Одновременно с установкой навыходе первого триггера 21 потенциала логической единицы начинает работувторой делитель 9 частоты, на счетныйвход которого поступают опорные импульсы с частотой следования РО например Го =118562 Гц)Коэффициент деления второго делителя 9 частоты определяется выходными сигналами первого блока 14 управленияНачало второго делителя 9 частотыопределяется поступлением потенциала логической единицы на его соответствующий вход. При этом на выходе второго делителя 9 частоты формируется короткий импульс, временноеположение которого относительно момента поступления разрешающего сигнала на его установочный вход опре-,деляется коэффициентом деления К 1= 948,При наличии на управляющем входевторого делителя 9 частоты.потенциала логической единицы и при поступлении на его счетный вход девятьсотсорока девяти импульсов на.выходеформируется короткий импульс, временное положение которого относительнопредшествующего выходного импульсаопределяется коэффициентом деления К= 949,Второй делитель 9 частоты является делителем частоты с программируемым (перестраиваемым) коэффициентом деления,1058083 10 НИИПИ Заказ 9602/ 77 Подписное нал ППП Патент" жгород,ул.Проектная в модуляторе на передаюшей стороне,так и в предлагаемом цифровом демодуляторе частотно-манипулированныхсигналов на приемной стороне величина допусковых интервалов А 1 можетбыть выбрана, малой (например,.О =. з= 0,004 мс, а следовательно, точность воспроизведения временныхинтервалов последовательности логических сигналов на выходе решаюшего блока 10 может быть полученачрезвычайно высокая,Таким образом, эффективность предлагаемого цифрового демодуляторасостоит в том, что путем новых бло-ков и элементов достигается увели.чение точности воспроизведения на выходе цифрового демодулятора временных интервалов передаваемой последовательности,логических сигналов,т,е, увеличение точности демодуляции.Кроме высокой точности демодуляции цифровой демодулятор обладает повышенной помехоустойчивостью, что позволяет использовать для передачицифровой информации каналы связи сповышенным уровнем шума, а также увеличить дальность связи,Высокая точность демодуляции ивысокая помехоустойчивость предлагаемого цифрового демодулятора позволяютсократить количество полупериодовхарактеристических частот, приходящихся на элементарную посьшку, а следовательно, увеличить скорость передачи .цифровой информации.

СмотретьЗаявка

3491448, 06.09.1982

ПРЕДПРИЯТИЕ ПЯ Р-6120

РОМАНОВ ВИКТОР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/14

Метки: демодулятор, сигналов, цифровой, частотно-манипулированных

Опубликовано: 30.11.1983

Код ссылки

<a href="https://patents.su/9-1058083-cifrovojj-demodulyator-chastotno-manipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор частотно-манипулированных сигналов</a>

Предыдущий патент: Система передачи и приема сигналов с адаптивной дифференциальной импульсно-кодовой модуляцией

Следующий патент: Демодулятор фазоманипулированных сигналов

Случайный патент: Устройство для синхронного контроля подшипников скольжения