Демодулятор фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

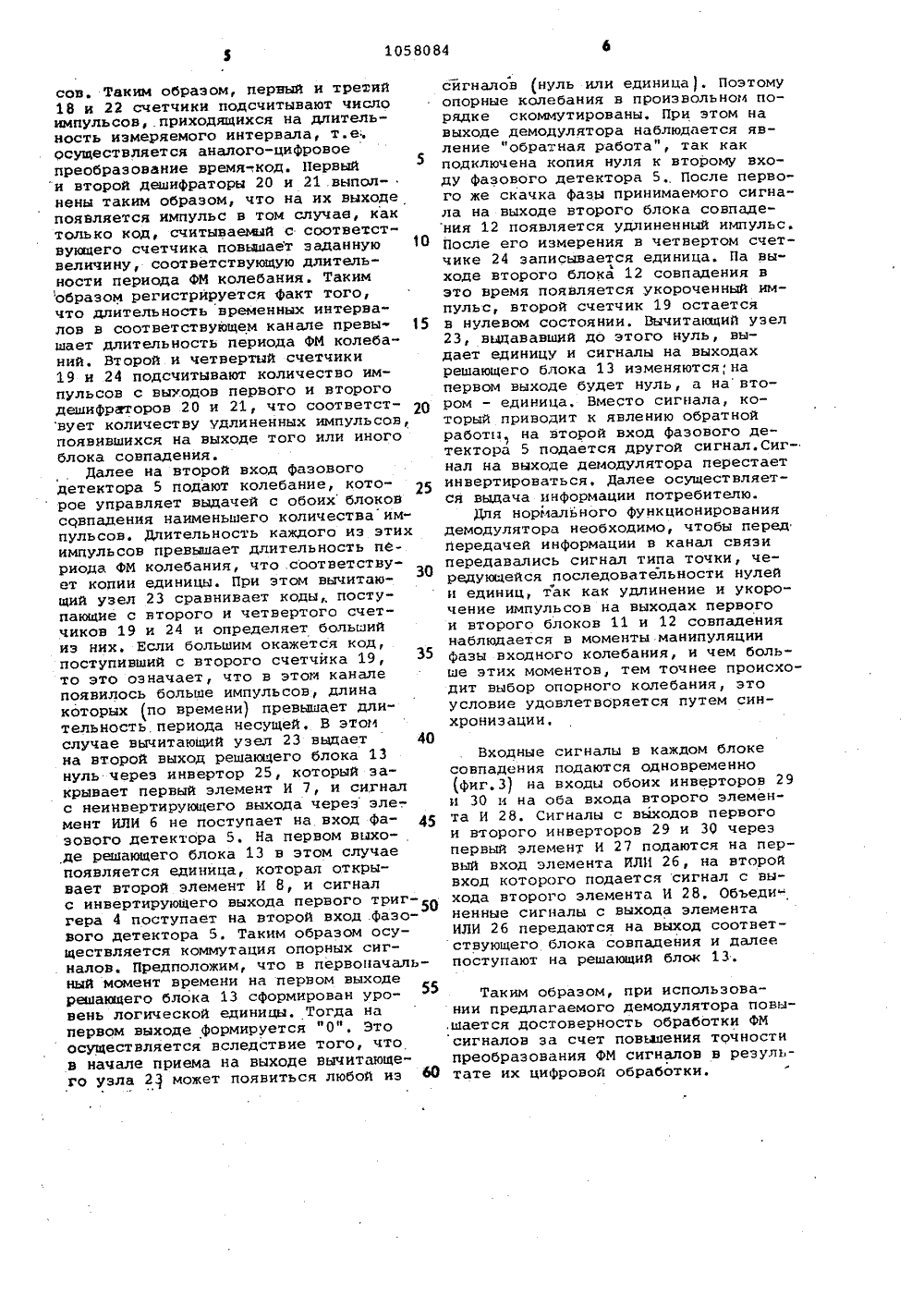

4 А СОЮЗ СОВЕТСНИСОЦИАЛИСТИЧЕСНРЕСПУБЛИК 151) Н 04 27 2 СТВУ Ви ТОРСК К льство СС02, 1974 ОСУДАРСТВЕННЫЙ КОМИТЕТ СССО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ИСАНИЕ ИЗО(56 ) 1. Заеэдный А.М. и др. Фазораз. ностная модуляция., М., "Связь", 1967, с.92-942. Авторское свидете СР Р 511716, кл, Н 04 Ь 7/(54)(57) 1, ДЕИОЦУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащий фазовый детектор, первый вход которого соединен с входом умножителя частоты, и последовательно соединенные дифференцирующий блок и первый триггер, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности, введены два усилителя-ФорМирователя, элемент ИЛИ, два элемента И, второй и третий триггерыидва блока совпадения, выходы которыхподключены к входам введенного решающего блока, выходы которого соединены с первыми входами первого и второго элементов И, выходы которых под-,ключены к входам элемента ИЛИ, выходкоторого соединен с вторым входомфазового детекора, первый вход кото-рого соединен с входом первого усилителя-формирователя, выход которогоподключен к первым входам первого.и второго блоков совпадения, вторыевходы которых соединены соответственно с выходом второго и третьего триггеров, входы которых соединены соответственно с вторыми входами первого и второго элементов И ис выходами первого триггера, а выход умножителя частоты через второй усилитель-формирователь подключен к входудифференцирующего блока.1058084 2. Демодулятор по п.1, о т л и ч а ю щ и й с я тем, что решакщий блок содержит инвертор, генератор импульсов, последовательно соединенные первый дифференцирующий элемент, первый счетчик, первый дешифратор и второй счетчик и последовательно соединенные второй дифференцирующий элемент, третий счетчик, второй дешифратор, четвертый счетчик и вычитающий узел, второй вход и выход которого соединены соответственно с выходом второго счетчика и с входом инвертора, вход и выход которого являются выходами решающего блока, входами которого являются входы перного и второго дифференцирующих элементов, а выход генератора импульсов подключен к вторым нходам первого и третьего счетчиков.3, Демодулятор по п.1, о т л и - ч а ю щ и й с я тем, что каждый блок совпадения содержит два инвертора элемент. ИЛИ и два элемента И, выходы которых подключены к входам элемента ИЛИ, выход которого являет, ся выходом блока совпадения, входами которого являются входы инверторов, выходы которых подключены к входам первого элемента И, а входы второго элемента И подключены соответственно к входам первого и второго иннерторон,2Изобретение относится к технике рого подключен к первым входам перво- электросвязи и может использоваться го и второго блоков совпадения втоР в системах пЕредачи данных с высоко- рые входы которых соединены соответсткачественными каналами связи. венно с выходами второго и третьегоИзвестно устройство для приема фа триггеров, входы которых соединены зоманипулированных сигналов (ФМ сиг- соответственно с вторыми входами перналов), содержащее преобразователь ного и второго элементов И и с вы.частоты, фильтр, фазонращатель, фазо- ходами перного триггера, а выход умновый детектор и пороговый блок 11 . жителя частоты через второй усилительНедостаток устройства - частичное. 10 формирователь подключен к входу дифподавление влияния эффекта "обратная ференцирующего блока.Иработа При этом решающий блок содержитНаиболее близким по техническойинвертор, генератор импульсов, после- сущности к предлагаемому является де- донательно соединенные первый диффемодулятор, фазоманипулированных сигна 15 ренцирующий элеглент, первый счетчик, лон, содержащий фазовый детектор, пер первый дешифратор и второй счетчик, вый вход которого соединен с вхо- и последовательно соединенные второй дом умножителя частоты, и последова- дифференцирующий элемент, третий тельно соединенные дифференцирующий счетчик, второй дешифратор, четвер- блок и первый триггер 2), тый счетчик и вычитающий узел, втоОднако известный демодулятор. имеет 2 рой вход и выход которого соединены20низкую достоверность. соотн етст не нно с выходом второгоцель изобретения - повышение дос- счетчика и с входом инвертора, вход товерности, и выход которого являются выходамидля достижения поставленной цели, решающего блока входами которого янв демодулятор фазоманипулированных ляются входы первого и второго диффе 25.1 сигналов, содержащий фазовый детектор, ренцирующих элементов, а выход гене- первый вход которого соединен с нхо- ратора импульсов подключен к вторым дом умножителя частоты, и последова- входам первого и третьего счетчиков. тельно соединенные дифференцирующийблок и первый триггер, введены два 30 Кроме того, каждый блок совпадения усилителя"формирователя, элемент ИЛИ,содержит два инвертора, элемент ИЛИ дна элемента И, второй и третий триг- и два элемента И, выходы которых подгеры и дна блока совпадения, выходы ключены к входам элемента ИЛИ, выход которых подключены к входам введенно- которого является выходом блока сонго решающего блока, выходы которого 35 падения, входами которого являются соединены с первыми входами первого входы инверторов, выходы которых поди второго элементов И, выходы которых ключены к входам первого элемента подключен к входам элемента ИЛИ, И, а входы второго элемента И подвыход которого соединен с вторым нхо- ключены соответственно к.входам пердом фазового детектора, первый вход 40 ного и второго иннерторов. которого соединен с входом первого На фиг.1 представлена структурная усилителя-Формирователя, выход кото- электрическая схема демодулятора;фиг,2 - решающий блок, вариант); на фиг.З - блок совпадения (вариант).Демодулятор фазоманипулированных сигналов (фиг.1) содержит умножитель 1 частоты, первый усилитель-формирователь 2, дифференцирующий блок 3, первый триггер 4, фазовый детектор 5, элемент ИЛИ 6, первый и второй элементы И 7 и 8 соответственно, второй и третий триггеры 9 и 10 соответст венно, первый и второй блоки 11 и 12 совпадения соответственно, решающий блок 13 и второй усилитель-формирователь 14. При этом решающий блок (фиг.2) состоит из первого дифференцирующего элемента 15, генератора 15 16 импульсов, второго дифференцирую - щего элемента 17, первого и второго счетчиков 18 и 19 соответственно первого и второго дешифраторов 20 и 21 соответственно, третьего счетчи О ка 22, вычитающего узла 23, четвертого счетчика 24 и инвертора 25. Причем каждый блок совпадения (фиг.З) состоит из элемента ИЛИ 26, первого и второго элементов И 27 и 28 соответственно, первого и второго инверторов 29 и 30 соответственно.Демодулятор работает следующим образом.Пусть в канал связи передается произвольная последовательность нулей и единиц. На вход демодулятора в этом случае с выхода канала связи поступает фазомодулированный сигнал. На выходе умножителя 1 формируется сигнал с удвоенной частотой. Второй усилитель-формирователь 14 преобразует колоколообразные импульсы, поступающие с выхода умножителя 1 частоты, в трапецеидальные. Дифференцирующий блок 3 выделяет фронты этих 40 импульсов, которые далее поступают на вход первого триггера 4, на неинвертирующем и иивертирующем выходах которого получаются два противоположных напряжения . Один из этих сиг налов является копией нуля, т,е. сов-. падает по фазе с нулевой посылкой, второй - копией единицы, причем фазы этих сигналов постоянны, без манипуляции фазы. Теперь необходимо определить, какой из этих сигналов является копией нуля, а какой - копией единицы, Если это будет осуществлено, то сигнал, являющийся копией единицы, можно использовать в качестве опорного. При этом явление "обратная работа" не наблюдается.Если разделить частоты сигналов с выходов первого триггера 4 на два с помощью второго и третьего триггеров 9 и 10, переключающихся при из менении входного сигнала из положе-. ния "0" в положение "1", получают соответствующие сигналы на выходах второго и третьего триггеров 9 и 10 соответственно. Полученные сигналы 65 подаются на входы первого и второго блоков 11 и 13 совпадения, на другие входы которых поступает сигнал с выхода первого усилителя-формирователя 2, который преобразует сигнал с входа демодулятора в последователь-, ность прямоугольных импульсов. Соответствующий блок совпадения выдает на выход единицу, если сигналы на его входах, совпадают,т.е. присутствуют либо два нулд, либо две единицы,Рассмотрим сигналы, формируемые на выходе блока совпадения, при условии, что в длительность элементарной посылки укладывается целое число периодов фазомодулированного (ФМ) колебания. Когда отсутствует манипуляция фазы входного сигнала, на выходе обоих блоков 11 и 12 совпадения имеются импульсы со Скважностью, равной двум и длительностью, равной длительности периода ФМ колебания. При наличии манипуляции фазы в моменты манипуляции на выходе одного из блоков совпадения появляются импульсы, длительность которых меньше длительности импульсов при отсутствии манипуляции фазы в 2 раза. На выходе второго блока 12 совпадения в это же время длительность импульсов увеличивается в 2 раза. Это справедливо только для случая, когда на длительности элементарной посылки укладывается целое число периодов ФМ колебания. В противном случае на выходах обоих блоков совпадения появляются сигналы, как укороченные, так и удлиненные в два раза по сравнению с обычными (их длительность определяется ФМ колебанием). При подаче на входы блоков совпадения преобразованного входного сигнала и сигнала, полученного после деления на два частоты сигнала, являющегося копией единицы, на их выходах формируются импульсы, максимальная длительность которых не превышает длительности периода ФМ сигнала.Если сравнить входной сигнал с сигналом, который получен из копии нуля после деления ее частоты на два, то максимальная длительность импульсов на выходе обоих блоков совпадения равна удвоенной длительности пе риода ФМ колебания. Таким образом, измеряя длительности импульсов на вы-. ходах обоих блоков совпадения, можно определить, какой из сигналов является копией нуля, а какой - копией единицы. Именно эти функции и выполняет решающий блок 13Первый и второй дифференцирующие блоки 15 и 17 (фиг.2) выделяют фронты импульсов, поступаю., щих на их входы. Эти импульсы устанавливают первый и второй счетчики 18 и 22 в нулевые состояния. На другие входы этих счетчиков подаются импульсы с выхода генератора 16 импуль 1058084сов. Таким образом, первый и третий 18 и 22 счетчики подсчитывают число импульсов,.приходящихся на длительность измеряемого интервала, т.е, осуществляется аналого-цифровое преобразование время-,код. Первый и второй дешифраторы 20 и 21 выполнены таким образом, что на их выходе появляется импульс в том случае, как только код, считываемый с соответствуяаего счетчика повышает заданную 10 величину, соответствующую длительности периода ФИ колебания. Таким образом регистрируется факт того, что длительность временных интервалов в соответствующем канале превы шает Длительность периода ФМ колебаний. Второй и четвертый счетчики 19 и 24 подсчитывают количество импульсов с выходов первого и второго дешифраторон 20 и 21, что соответствует количеству удлиненных импульсов, поянившихся на выходе того или иного блока совпадения.Далее на второй вход фазового детектора 5 подают колебание, которое управляет выдачей с обоих блоков совпадения наименьшего количестваимпульсов. Длительность каждого из этих импульсов превышает длительность периода ФМ колебания, что соответствует копии единицы. При этом вычитающий узел 23 сравнивает коды поступающие с второго и четвертого счетчиков 19 и 24 и определяет больший иэ них. Если большим окажется код, поступивший с второго счетчика 19, то это означает, что в этом канале появилось больше импульсов, длина которых по времени) превышает длительность периода несущей. В этом случае вычитающий узел 23 выдает 40 на второй выход решающего блока 13 нуль через иннертор 25, который закрывает первый элемент И 7, и сигнал с неинвертирующего выхода через эле-, мент ИЛИ 6 не поступает на вход фа эового детектора 5. На первом выходе решающего блока 13 в этом случае появляется единица, которая открывает второй элемент И 8, и сигнал с иннертирующего выхода первого тригО гера 4 поступает на второй вход фазового детектора 5. Таким образом осуществляется коммутация опорных сигналов. Предположим, что в первоначальный момент времени на первом выходе решающего блока 13 сформирован уровень логической единицы. Тогда на первом выходе формируется "0", Это осуществляется вследствие того, что в начале приема на выходе нычитающего Узла 2 может появиться любой из 60 сигналов (нуль или единица 1. Поэтому опорные колебания н произвольном порядке скоммутиронаны, При этом на выходе демодулятора наблюдается явление "обратная работа", так как подключена копия нуля к второму входу фазового детектора 5., После первого же скачка фазы принимаемого сигнала на выходе второго блока совпадения 12 появляется удлиненный импульс, После его измерения в четвертом счетчике 24 записывается единица, Па выходе второго блока 12 совпадения в это время появляется .укороченный импульс, второй счетчик 19 остается в нулевом состоянии, Вычитакщий узел 23, вццававший до этого нуль, выдает единицу и сигналы на выходах решающего блока 13 изменяются;на первом выходе будет нуль, а на втором - единица. ВмеСто сигнала, который приводит к явлению обратной работ на второй вход фазового детектора 5 подается другой сигнал.Сигнал на выходе демодулятора перестает иннертиронаться, Далее осуществляется выдача информации потребителю.Для нормального функционирования демодулятора необходимо, чтобы перед Передачей информации н канал связи передавались сигнал типа точки, чередующейся последовательности нулей и единиц, так как удлинение и укорочение импульсов на выходах первого и второго блоков 11 и 12 совпадения наблюдается в моменты манипуляции фазы входного колебания, и чем больше этих моментов, тем точнее происходит выбор опорного колебания, это условие удовлетворяется путем синхронизацииВходные сигналы в каждом блоке совпадения подаются одновременно (фиг,З) на входы обоих инверторон 29 и МО и на оба входа второго элемента И 28. Сигналы с выходов первого и второго инверторов 29 и 30 через первый Элемент И 27 подаются на первый вход элемента ИЛИ 26, на нторой вход которого подается сигнал с выхода второго элемента И 28, Объеди" ненные сигналы с выхода элемента ИЛИ 26 передаются на выход соответствующего блока совпадения и далее поступают на решающий блок 13,Таким образом, при использовании предлагаемого демодулятора повышается достоверность обработки ФМ сигналон за счет повыаения тОчности преобразования ФМ сигналов в результате их циФровой обработки.(урах Техред Л.Пилипенко Корректор Л.Зимокосов: едакт Тираж 677венного кобретений иЖРауш Филиал ППП "Патентф, г. Ужгород, ул, Проектная,Заказ 9602/58 ВНИИПИ Госу по делам 113035, .Моср и а Подпис ное митета СССР открытий ская наб., д. 4/5

СмотретьЗаявка

3485151, 17.08.1982

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ЗУБКОВ ЮРИЙ ПЕТРОВИЧ, КИРИЧЕНКО АНАТОЛИЙ ЛЕОНИДОВИЧ, ГАЛИЛОВ ПЕТР БОРИСОВИЧ, НЕФЕДОВ ЕВГЕНИЙ ИВАНОВИЧ

МПК / Метки

МПК: H04L 27/233

Метки: демодулятор, сигналов, фазоманипулированных

Опубликовано: 30.11.1983

Код ссылки

<a href="https://patents.su/5-1058084-demodulyator-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор фазоманипулированных сигналов</a>

Предыдущий патент: Цифровой демодулятор частотно-манипулированных сигналов

Следующий патент: Устройство для имитации телефонного канала

Случайный патент: Разделительное устройство