Способ формирования трехуровнего сигнала в релейных системах управления динамическим объектом и релейный регулятор для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1758633

Автор: Леденев

Текст

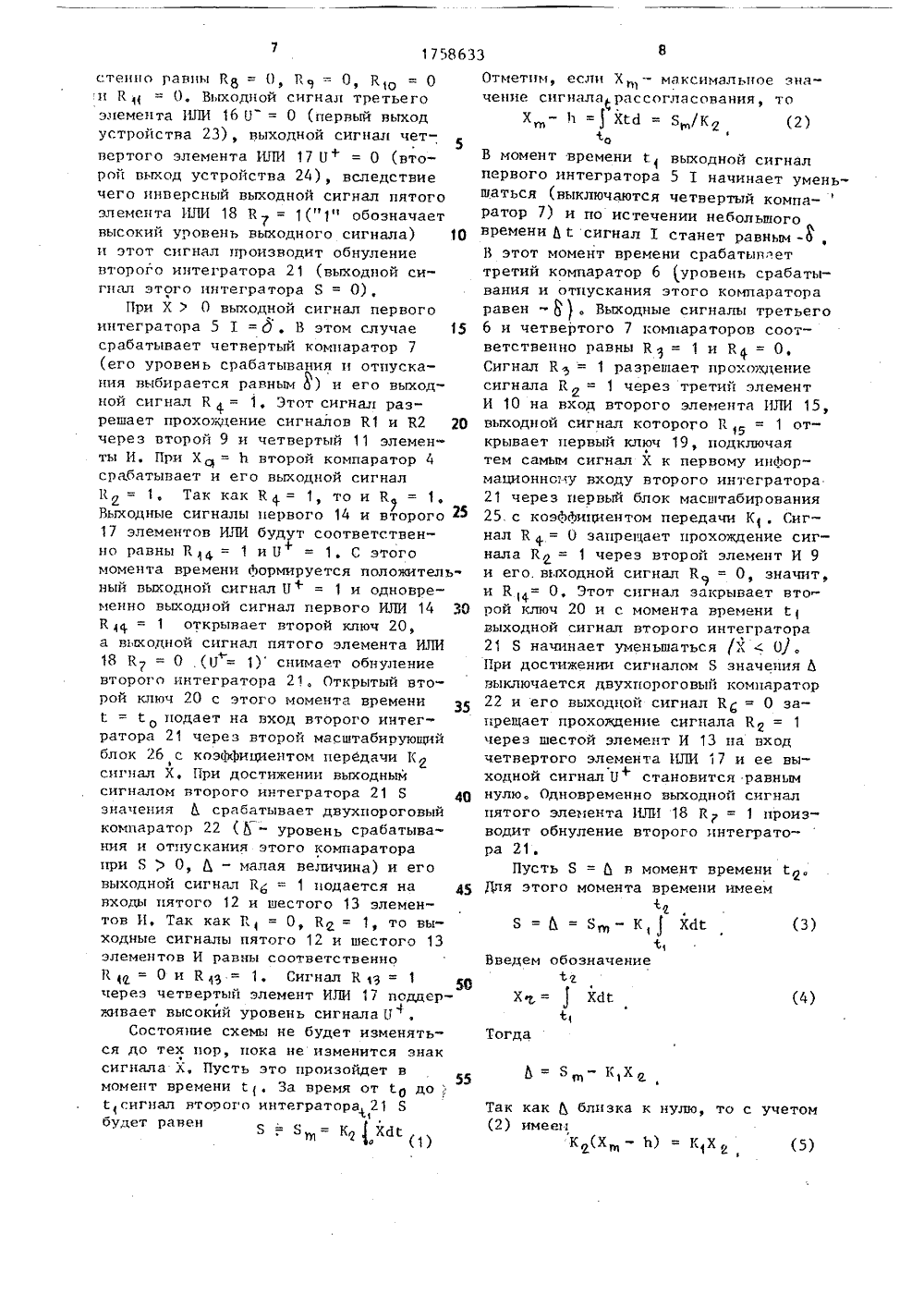

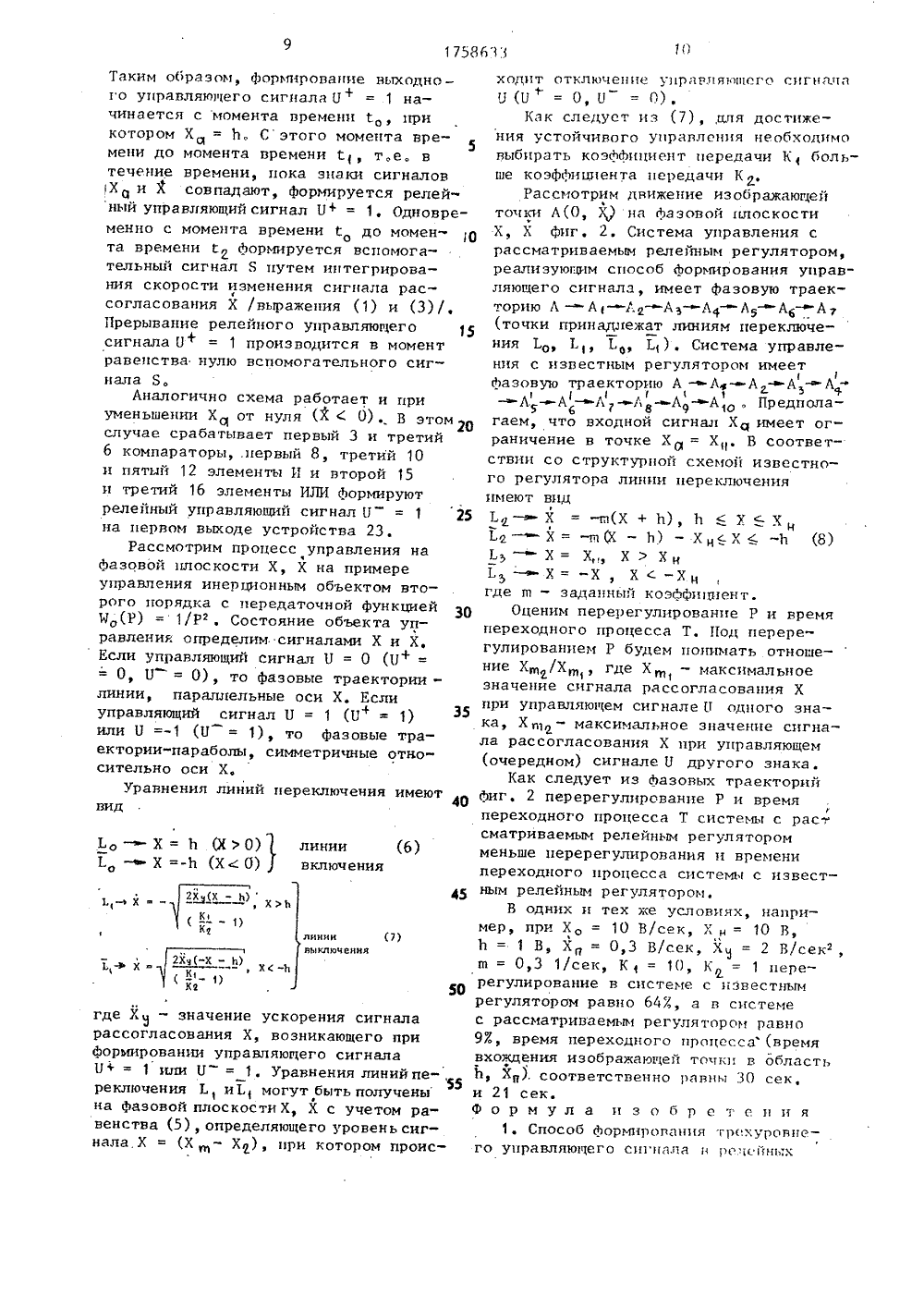

СОЮЗ СОВЕТСНИХСОЦЮЛИСТИЧЕСНИХ СПУБЛ 5) 5 С 05 В 11/14 ЕНИ регу уира 11 ля ско равл я Ва ну Образ осуще сигнал латы новно упрлвл 1 зобретени носится к техник ройство, огопороель, трех ф и суммиержащиц ивающее фильтр, говый1 о зи РуюсицНедит в слжевт а состоа тлк- входнозрлстаютпереревремя переходн гулцрование.роцессл ц аибо еще посо уров невого управлспособ, вклюа рассогпасован тся ля он ассогласова знако ляюще ир ля игн ГОСУДАРСТВЕННЫИ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР ОПИСАНИ(71) Головное конструкторское бюро Научно-производственного объединения Энергия"(56) Авторское свидетельство СССР1280567, кл. С 05 В 11/14, 1986, Авторское свидетельство СССР 1 н 805247, кл. С 05 В 13/02, 1981. (54) СНОСО Б ФОРМИРОВАНИЯ ТРЕХУРОВНЕГО УЛРАВЗМОЩЕГО СИГНАЛА В РЕЛЕЙНИХ СИСТЕМАХ УПРАВЛЕНИЯ ДИНАМИЧЕСКИМ ОБЪ ГКтОМ И РЕЛЕЙНЫЙ РЕГУЛЯТОР(57) Изобретение относится к технике автоматического управления . Способ автоматического управления, в частности, к технике 6 ормирования управляющих сигналов.Известен способ 6 ормирования трехуровневых управляющих сигналов в релейно-импульсных системах управления динамическим объектом, основанный натом, что в зависимости от огибки управления формируют импульсный и релейный управляющие сигналы путем создания скользящего режима.Недостаток этого способа состоитв сложности его реализации, а такжев том, что при ограличении входногосигнала рассогласования возрастают время переходного процесса и пере- Регулирование,Известен регурелейно-импульсный1 зуюций уклзанпый ст., 5 О 17586 оормирования управляющего сигнала ц релейный регулятор позволяют исключить влияние ограничения сигналалцруемоц координаты нл процессвления, уменьвьцть перерегулцрование и время переходного процесса.этого с момента изменения знакарости регулируемой координаты Формируют дополнительный релейый упюпий сигнал до момептл рлгенстлю вспомоаельного сигнала,ование вспомогательного сигналаствляют путем интегрированияа скорости регулируемой коордив течение времени децствия осго и дополнительного релецныхяюцих сигналов. 3 ил. инерционное звено, м мпульсный преобрлзова нный релейный элемент усилитель,таток этого регулято 1 жности его реализлцччто прц огранцченит игнала рассогллсовлця близким технцчсскцм у с 1 ормирсюлнця трех яющего сигнала явля ющцй. цзмерслп 1 с. с:цгн ия ц скс 1 роснц ц "мс и ия ц прц сон; 1; цп овл 1 пс.пчвоиоложен знаку сигнала рассогласования.Недостаток этого способа состоитв том, что при ограничении сигналарассогласования возрастают время пе 5реходного процесса и перерегулирование.Наиболее близким техническим решением к релейному регулятору являетсяустройство, содержащее первый и второй интеграторы, первый, второй и третий компараторы, при этом входы первого и второго компараторов являютсявходом устройства.Недостаток этого устройства состоит в том, что при ограничении сигналарассогласования возрастают время переходного процесса и перерегулирование,Цель изобретения - уменьшение пере 20регулирования и времени переходногопроцесса,Сущность изобретения состоит в том,что способ Формирования трехуровневого управляющего сигнала, включающий 25измерение сигналов рассогласованияи скорости изменения рассогласованияи при совпадении их знаков формирование релейного управляющего сигнала,знак которого противоположен знакусигнала рассогласования, предполагаетс момента начала формирования релейного управляющего сигнала формированиевспомогательного сигнала путем интсгрирования от нуля сигнала скоростиизменения рассогласования, при этом35формирование вспомогательного и релейного управляющего сигналов прерываетсяпри уменьшении абсолютного значениявспомогательного сигнала до нуля, акрутизну интегрирования К 1 при уменьпении абсолютного значения сигналарассогласования и крутизну интегрирования К при нарастании абсолютногозначения сигнала рассогласования выбирают одинакового знака из условияк, ъ к .В релейшй регулятор, содержащийпервый и второй интеграторы, первый,второй и третий комиараторы, при этомвходы первого и второго компараторов56являются входом устройства, введенышесть элементов И, пять элементовИЛИ, два ключа, двухпороговый компаратор, два блока масштабирования ичетвертый компаратор, при этом выходпервого компаратора соединен с первыми входами первого, четвертогон пятого элементов И, выход второго компаратора соединен с первыми входами второго, третьего и шестого элементов И, выход третьего компаратора соединен со вторыми входами первого и третьего элементов И, выход четвертого компаратора соединен со вторыми входами второго и четвертого элементов И, выход первого элемента И соединен с первыми входами первого и треть- его элементов ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выходы треть" его и четвертого элементов И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с управляющим входом первого ключа, информационный вход которого является вторым входом устройства, и соединен с информационными входами первого интегратора и второго ключа, выход первого ключа через первый блок масштабирования соединен с первым информационным входом второго интегратора, выход которого соединен с входом двухиорогового компаратора, соединенного своим выходом со вторыми входами пятого и шестого элементов И, выходы которых соединены соответственно с вторыми входами третьего и четвертого элементов ИЛИ, соединенных своими выходами соответственно с первым и втсрым входами пятого элемента ИЛИ, инверсный выход которого соединен с входом обнуления второго интегратора, второй информационный вход которого соедйнен через второй блок масштабг рования с выходом второго ключа, управляющий вход которого ;оединен с выходом иервогс элемента ИЛИ, вь:ход первого интегратора соединен со входами третьего и четвертого компараторов, а выход третьего элемента ИЗЯ является первым выходом устройства, выход четвертого элемента ЮЛ является вторым выходом устройства.На фиг. 1 представлена охема релейного регулятора, реализующего пособ формирования трехуровневого управляющего сигнала; на фиг, 2 фазовые траектории системы управления, использующей релейный регулятор Фиг. 1.Изобретение выполняется следуюпдм образом. Вход устройства 1 соединен со входом первого 3 и второго 4 компараторов, а второй вход устройства 2 соединен с информационным входом517586первого интегратора 5, первого ключа 19 и второго ключа 20Выход первого интегратора 5 соединен со входами третьего 6 и четвертого 7 компараторов, Выход первого кояпарато 5ра 3 соединен с первыми входами первого 8, четвертого 11 и пятого 12элементов И, выход второго компаратора 4 соединен с первыми входами10второго 9, третьего 10 и шестого 13элементов И, выход третьего компаратора 6 соединен со вторыми входамипервого 8 и третьего 10 элементов И,выход четвертого компаратора 7 соединен со вторыми входами второго 9 ичетвертого 11 элементов И. Выход первого элемента И 8 подключен к первымвходам первого 14 и третьего 16 элементов ИЛИ, выход второго элемента И 9 20подключен ко второму входу первогоэлемента ИЛИ 14 и первому входу четвертого элемента ИЛИ 17, выход третьего 10 и четвертого 11 элементов Исоединены соответственно с первым и 25вторым входами второго элемента ИЛИ15, выход которого подключен к управляющему входу первого ключа 19, выход которого через первый блок масштабирования 25 соедйнен с первым информационным .входом второго интегратора 21, соединенного своим выходом свходом двухпорогового компаратора 22,выход которого подключен ко вторымвходам пятого 12 и шестого 13 элементов И. Выход пятого элемента И соединен со вторым входом третьего элемента ИЛИ 16, выход шестого элементаИ 13 соединен со вторым входом четвертого элемента ИЛИ 17.Выход третьегоэлемента ИЛИ 16 соединен с первымвходом пятого элемента ИЛИ 18 и является первым выходом 23 устройства,выход четвертого элемента ИЛИ 17 соединен со вторым входом пятого элемента ИЛИ 17 и является вторым выходом 24 устройства, Инверсный выходпятого элемента ИЛИ 18 соединен совходом обнуления второго интегратора 21, второй информационный вход которого через второй блок масштабиро 50вания 26 подключен к выходу второгоключа 20, управляющий вход которогосоединен с выходом первого элементаИЛИ 14 55На фиг.2 Х - сигнал рассогласова(ния, Х - скорость изменения сигналарассогласования, ,о, .(, ., ,3361 1 ,- .пинии переключения(на фаэовой плоскости Х, Х.1 елейный регулятор работает следующим образом. Пусть ца вход релейного регулятора 1 поступает сигналХ - сигнал рассогласования и на второй вход 2 поступает сигнал Х - сигнал скорости изменения рассогласования. Считаем, что сигнал Х имеетограничение в некоторой точке Х(в этом состоит отличие Х, от сигналарассогласования Х)Предположим, что выходной сигналпервого интегратора 5 имеет ограничение, такое, что -8 с 1 с 3 где 39заданная величина. Рассмотрим работу(такого интегратора, Пусть Х ) О, Через некоторое время выходной сигнал 1станет равным о, В этом случае первыйинтегратор 5 будет сохранять свое со(стояние 1 = о до тех пор, пока Х ) О.Пусть в некоторый момент времени(Х = О, а затем этот сигнал началуменьшаться (Х ( 0), С этого моментавремени начнет уменьшаться и сигнал 1.Через некоторое времясигнал 1станет равным -8, т,е, изменение состояния первого интегратора 5 происходит после изменения знака сигнала(Х, при этом за время изменения состояния этого интегратора от 1 = о до 1=-О; сигнал рассогласования Х изменяется на величину ЬХ = 23, т,к, ЬХфо+ХсС = 2 о. Аналогичные ряссуж+одения можно провести и для случаяХ-О,Таким образом, изменение состоянияпервого интегратора 5 от 1 = о( до1 =-1 и наоборот происходит послеизменения знака сигнала .,. Зл времяэтого изменения сигнал рассогласования изменяется на величину 6 Х = 2 о.Если о выбрать достаточно малойвеличиной, то можно считать, что изменение состояния первого интегратора 5 происходит при измецеции знакасигнала Х,Пусть сигнал Хс( увели н(ляется отнуля (Х ) 0). При Хо ( Ь (1 - уровеньсрабатывания и отпускянпя гторогокомпаратора 4) выходные спгцллы первого 3 и второго 4 компяряторов соответственно рявнк Н = О, ц й=/ (0 ( 0 обозначает цп як ц и у р о ц е и ьвыходного сигнала), Гм г:огцц.е спгцлзд лпервого 8, второго 9, тр(.т; око 1 йи четвертого 11 элементовсоатпст(4) Тогда стелло равнлг Кв = О, Г г =- О, К = Ои К = О, Выходной сигнал третьегоэгемента ИЛИ 16 У = О (первый выходустройства 23), выходной сигнал четвертого элемента ИЛИ 17 11+ = О (второй выход устройства 24), вследствиечего инверсный выходной сигнал пятогоэлемента ИЛИ 18 К = 1("1 ф обозначает7высокий уровень выходного сигнала) 10и этот сигнал производит обнулениевторого интегратора 2 1 (выходной сигггал этого интегратора Я = О),При Х ) О выходной сигнал первогоинтегратора 5 1 = Д, В этом случае 15срабатывает четвертый компаратор 7(его уровень срабатывания и отпускания выбирается равным о) и его выходной сигнал К= 1, Этот сигнал разрешает прохождение сигналов К 1 и К 2 20через второй 9 и четвертый 11 элементы И, При Х= Ь второй компаратор 4срабатывает и его выходной сигналК = 1, Так как К= 1, то и К = 1,Выходные сигналы первого 14 и второго 2517 элементов ИЛИ будут соответственно равны Р= 1 и 11 = 1. С этогомомента времени формируется положительный выходной сигнал 11 ф = 1 и одновременно выходной сигнал первого ИЛИ 14 30К= 1 открывает второй ключ 20,а выходной сигнал пятого элемента ИЛИ18 К 7 = О (1 = 1) снимает обнулениевторого интегратора 21, Открытый второй ключ 20 с этого момента временио подает на вход второго интегратора 21 через второй масщтабирующийблок 26 с коэффициентом передачи Ксигнал Х. При достижении выходнымсигналом второго интегратора 21 Б ,10значениясрабатывает двухпороговыйкомпаратор 22 (гг - уровень срабатывания и отпускания этого компараторапри Я ) О, 6 - малая величина) и еговыходной сигнал К = 1 подается навходы пятого 12 и шестого 13 элементов И, Так как К = О, К = 1, то выходные сигналы пятого 12 и шестого 13элементов И равны соответственноК -- О и К = 1, Сигнал КЭ = 1через четвертый элемент ИЛИ 17 поддерживает высокий уровень сигнала 11Состояние схемы не будет изменяться до тех пор, пока не изменится знаксигнала л, Пусть это произойдет в55момент времени С, За время от Сб доссигггал второго интегратора 21 Б1будет равен 6 8 Кг КХс 1 Е Отметим, если Х.- максимальное знагчепце сигггаларассогласования, тоХ - г = Х 1 с 1 = Б/К (2)1(В момент временивыходной сигнал первого интегратора 5 1 начинает уменьшаться (выключаются четвертый компа-ратор 7) и по истечении небольшого времени Ь 1 сигнал 1 станет равным -3, В этот момент времени срабатыв .ет третий компаратор 6 уровень срабатывания и отпускания этого компаратора равен - ) . Выходные сигналы третьего 6 и четвертого 7 компараторов соответственно равны К= 1 и Кг = О, Сигнал К = 1 разрешает прохождение сигнала К = 1 через третий элемент2И 10 на вход второго элеггеггта ИЛИ 15, выходной сигнал которого Р = 1 от 5 крывает первый ключ 19, подключая тем самым сигнал Х к первому иггФормационному входу второго интегратора 21 через первый блок маснгтабирования 25. с коэФАициентом передачи К, Сигнал К= О запрецает прохождение сигнала К = 1 через второй элемент И 9 и его, вьгходной сигнал К = О, значит, и К = О, Этот сигнал закрывает вто" рой ключ 20 и с момента времени выходной сигнал второго интегратора 21 Б начинает уменьшаться гХ О/, При достижении сигналом Б значения Ь выключается двухпороговый компаратор 22 и его выходной сигнал КО заггрегцает прохождение сигнала К = 1 через шестой элемент И 13 на вход четвертого элемента ИЛИ 7 и ее выходной сигнал Ц становится равным нулю, Одновременно выходной сигнал пятого элемента ИЛИ 18 К = 1 ггроизводит обнуление второго интегратора 21.Пусть Я = 6 в момент времени Для этого момента времени имеем8 = б = Ь- К,Х 1 (3)СгВведем обозначениееХ=Ха Так какблизка к нулю, то с учетомТаким образом, формирование вьтходного управляющего сигнала У + = 1 начинается с момента времени Со, при котором Хц = Ь, С этого момента времени до момента времени С 1, т,е, в течение времени, пока знаки сигналов ХП и Х совпадают, формируется релейный управляющий сигнал Б+ = 1, Одновременно с момента времени С до момен- доо та времениформируется вспомогательный сигнал Б путем интегрирования скорости изменения сигнала расг согласования Х /выражения (1) и (3)/, 11 рерывание релейного управляющего сигнала О+ = 1 производится в момент равенства нулю вспомогательного сигнала БоАналогично схема работает и при уменьшении Хс 1 от нуля (1 ( О)В этому случае срабатывает первый 3 и третий 6 компараторы, .первый 8, третий 10 и пятый 12 элементы И и второй 15 и третий 16 элементы ИЛИ формируют релейный управляющий сигнал Б = 1 25 на первом выходе устройства 23Рассмотрим процесс управления на фазовой плоскости Х, Х на примере управления инерционным объектом второго порядка с передаточной функцией Ир(Р) = 1/Р 2 . Состояние объекта управления определим. сигналами Х и Х, Если управляющий сигнал Б = 0 (11 =О, 11 = О), то фазовые траекториилинии, параллельные оси Х. Если управляющий сигнал Б = 1 (11+1) или 11 =-1 (11 = 1), то фазовые траектории-параболы, симметричные относительно оси Х.Уравнения линий переключения имеют 4 О вид р -ф Х = Ь (Х) О)линии (6) Гр -е Х =-Ь (Х(0)включения 2 Х.(Х - Ь)кЭХЬ ( - - 1) К К, линнк (7)выключения 2 Хм(-Х - Ь)К ( - - 1) Хй50 где Х - значение ускорения сигнала рассогласования Х, возникающего при формировании управляющего сигнала Бф = 1 или 11 = 1Уравнения линийпе-,5 реключения 1,1 и 1,1 могут быть получены на фазовой плоскости Х, Х с учетом равенства (5), определяющего уровень сигнала Х = (Х,- Х), при котором происходит отключение упратляющег о сигнала1.) (и= О, 0 = О),Как следует из (7), для достижения устойчивого управления необходимовыбирать коэффициент передачи К 1 больше коэффип 71 ента передачи К,Рассмотрим движение изображающейточки Л(0, Я на фаэовой плоскостифХ, Х фиг, 2, Система управления срассматриваемым релейным регулятором,реализующим способ формирования управляющего сигнала, имеет фазовую траекторию Л Л 1 Ле- Л- Л- Лз А А 7(точки принадлежат линиям переключения 1.1 Т 1,1), Система управления с известным регулятором имеетбазовую траекторию А - Л,ю- А Л -ф А(, 1 г, Ьр е цп ола 5 6 7 Вгаем, что входной сигнал Х 1 имеет ограничение в точке Х = Х,1. В соответствии со структурной схемой известного регулятора линии переключенияимеют вид-ш(Х + 11), Ь сХ:,( -Ь) -х:;, -Ь" (8)1 - Х= Х ХХХ= -Х Х с-Х5 1где щ - заданный коэффициент.Оценим перерегулирование Р и времяпереходного процесса Т. Иод перерегулированием Р будем понимать отношеНИЕ Хю 1 /Х 1 ГдЕ Х - МаКСИМаЛЬНОЕО 1 1значение сигнала рассогласования Хпри управляющем сигнале 11 одного знаКа, Хю 1- МаКСИМаЛЬНОЕ ЗпаЧЕНИЕ СИГНала рассогласования Х при управляющем(очередном) сигнале 0 другого знака,Как следует из фазовых траекторийфиг. 2 перерегулирсванне Р и времяпереходного процесса Т системы с рассматриваемым релейным регуляторомменьше перерегулирования и временипереходного процесса системы с известным релейным регулятором.В одних и тех же условиях, например, при Хр = 10 В/сек, Х н = 10 В,Ь = 1 В, Хп = 0,3 В/сек, Х = 2 В/секш = 0,3 1/сек, К 1 = 10, К = 1 иеререгулирование в системе с известнымрегулятором равно 641, а в системес рассматриваемым регулятором равно97., время переходного процесса(времявхожцения изображающей точки в областьеЬ, Х 17). соответственно равны 30 сек,и 21 сек.Формула изобретения1. Способ формирования трехуровнего управляющего сигнала н ре.ейныхсистемах управления динамическим объектом, включающий измерение сигналов рассогласования и скорости изменения рассогласования и црц совпадении их знаков-Аормировацие релейного управ 5 ляющего сигнала, знак которого противоположен знаку сигнала рассогласования, о т л и ч а ю щ и й с я тем, что, с целью уменьшения перерегулиро вания и времени переходного процесса, с момента начала формирования релейного управляющего сигнала формируют вспомогательный сигнал путем интегрирования от нуля сигнала скорости изменения рассогласования, цри этом формирование вспомогательного и релейного управляющих сигналов прерывают при уменьшении абсолютного значения вспомогательного сигнала до нуля, а крутизну интегрирования Кпри уменьшении абсолютного значения сигнала рассогласования и крутизну интегрирования К,2 цри нарастании абсолютного значения сигнала рассогласова ния выбирают одинакового знака из условия 1 К,) ) К2, Релейный регулятор, содержащий первый и второй интеграторы, первый, второй и третий компараторы, при этом ЗО входы первого и второго компараторов являются входом регулятора, о т л и- Ч а ю щ и й с я тем, что, с целью уменьшения перерегулирования и времени переходного процесса, в него введены шесть элементов И, пять элементов ИЛИ, два ключа, двухпороговый компаратор, два блока масштабирования и четвертый компаратор, лри этом выход первого компаратора соединен спервыми входами первого, четвертогои пятого элементов И, выход второгокомцаратора соединен с первыми входами второго, третьего и шестогоэлементов И, выход третьего компара 45 тора соединен с вторыми входами первого и третьего элементов И, выход четвертого компаратора соединен с вторыми входами второго и четвертого элементов И, выход первого элемента И соединен с первыми входами первого и третьего элементов ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выходы третьего и четвертого элементов И соединены соответственно спервым и вторым входами второго элемента ИЛИ, выход которого соединен с управляющим входом первого ключа, информационный вход которого является вторым входом регулятора, и с информационными входами первого интегратора и второго ключа, выход первого ключа через первый блок масштабирования соединен с первым информационным входом второго интегратора, выход котсрого соединен с входом двух- порогового компаратора, соединенного своим выходом с вторыми входами пятого и шестого элементов И, выходы которых соединены соответственно с вторыми входами третьего и четвертого эле" ментов ИЛИ, соединенных своими выходами с первым и вторым входами пятого элемента ИЛИ, инверсный выход которого соединен с входом обнуления второго интегратора, второй информационный вход которого соединен через второй блок масштабирования с выходом второго ключа, управляющий вход кото" рого соединеч с выходом первого элемента ИЛИ, выход первого интегратора соединен с входами третьего и четвертого компараторов, выход третьего( элемента ИЛИ является первым выходом регулятора, а выиод четвертого элемента ШШ является его вторым выходом,Л1758 б 33 ХХа) Редактор Заказ 3000 Тиран Подписное3 НИИПИ Государственного комитета по изобрстениям и открытиям при ГКНТ СССР11303 5, Иосква, Ж, Раушская наб., д. 4/5 одстнеиио-издательский комбинат Пате Гагарина,1 Пр город,ОснО КИ СИН Ю 0 И реют Г 6 Во ,иг Составитель Г.Ледневегляник Техред ИЛоргентал Корректор О,Густи

СмотретьЗаявка

4699047, 18.04.1989

ГОЛОВНОЕ КОНСТРУКТОРСКОЕ БЮРО НАУЧНО-ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "ЭНЕРГИЯ"

ЛЕДЕНЕВ ГЕННАДИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G05B 11/14

Метки: динамическим, объектом, регулятор, релейный, релейных, сигнала, системах, трехуровнего, формирования

Опубликовано: 30.08.1992

Код ссылки

<a href="https://patents.su/8-1758633-sposob-formirovaniya-trekhurovnego-signala-v-relejjnykh-sistemakh-upravleniya-dinamicheskim-obektom-i-relejjnyjj-regulyator-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ формирования трехуровнего сигнала в релейных системах управления динамическим объектом и релейный регулятор для его осуществления</a>

Предыдущий патент: Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне

Следующий патент: Программный управляющий модуль с контролем

Случайный патент: Газоструйная горелка для разрушения бетона и железобетона