Формирователь сигналов произвольной формы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

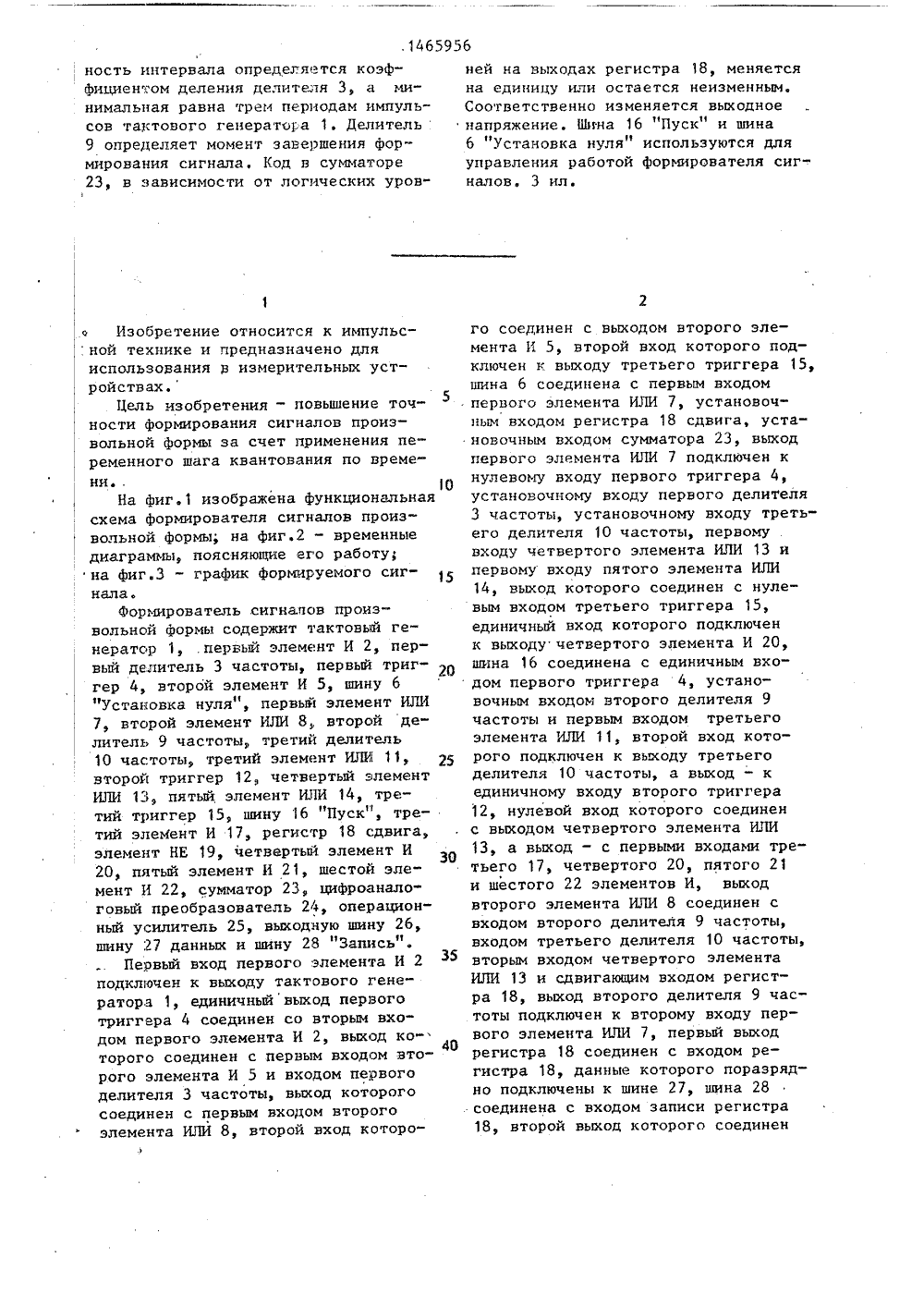

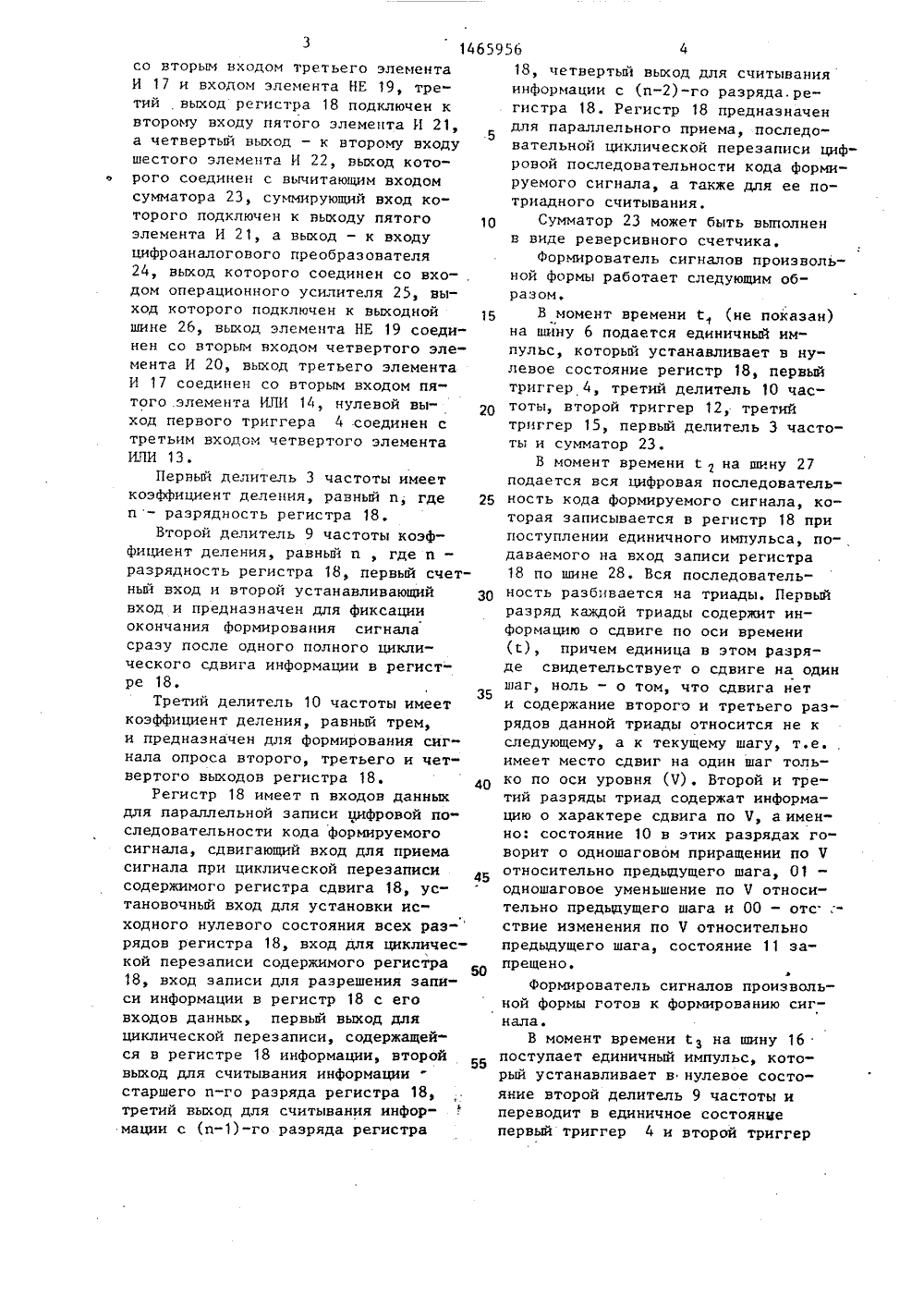

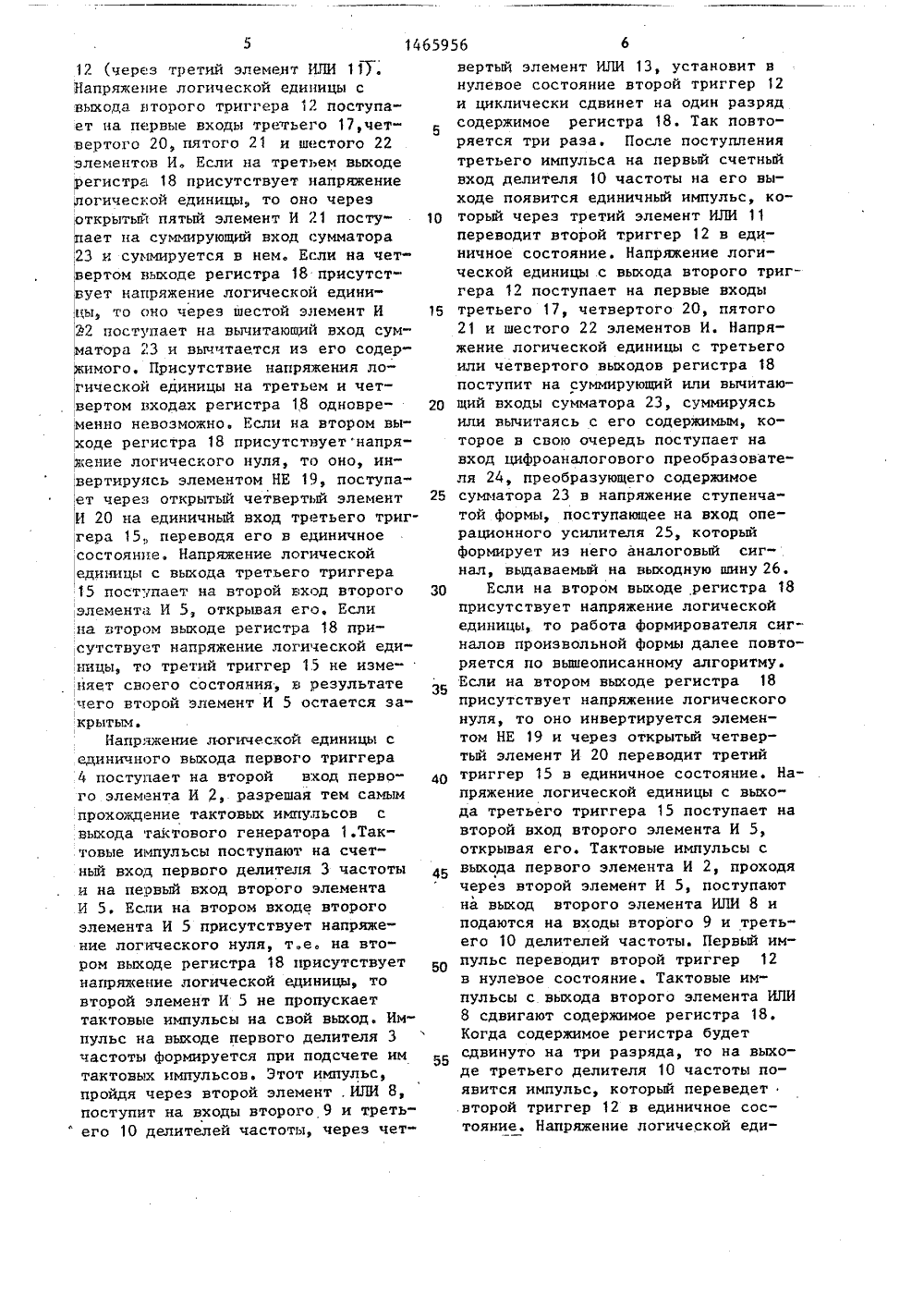

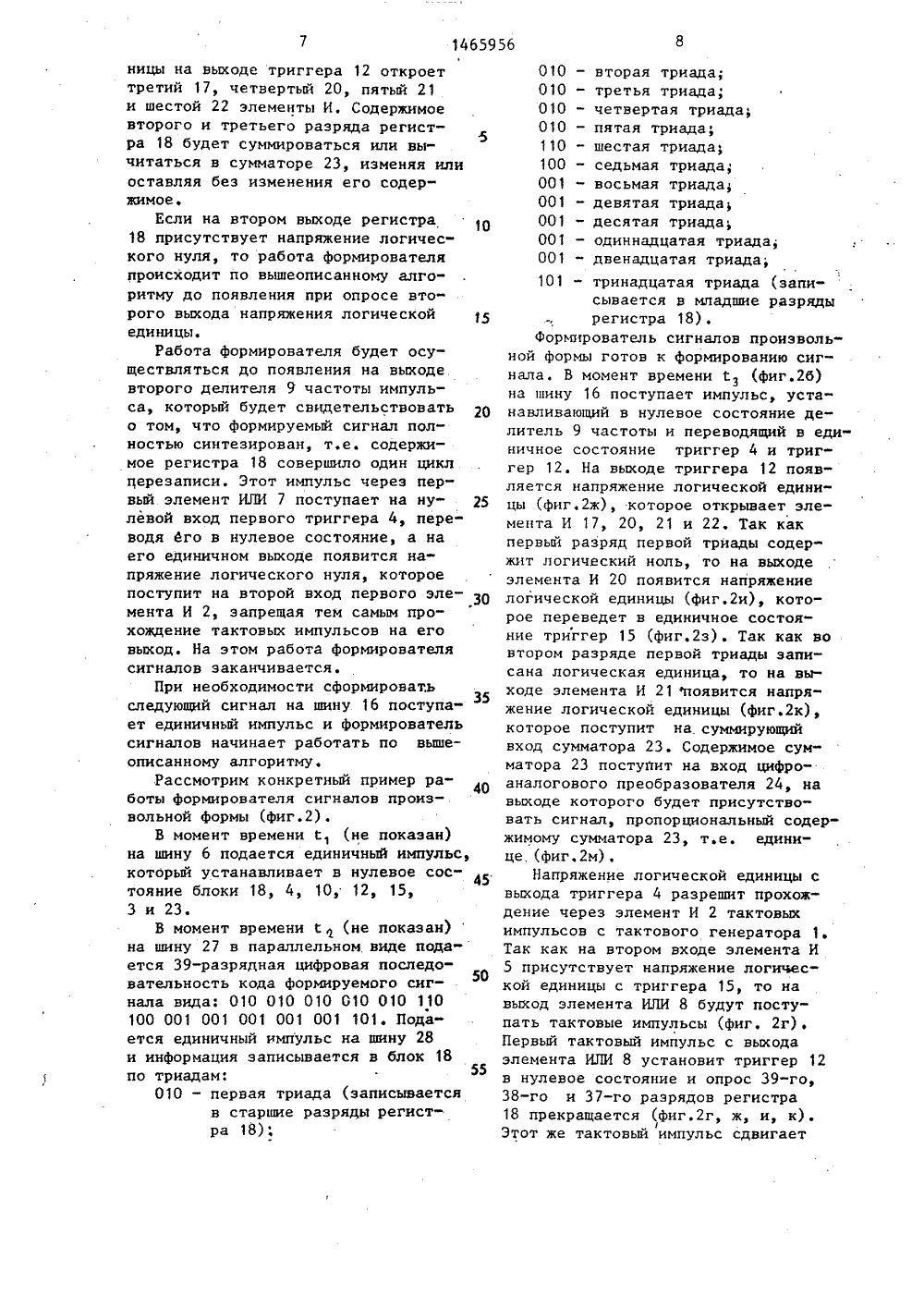

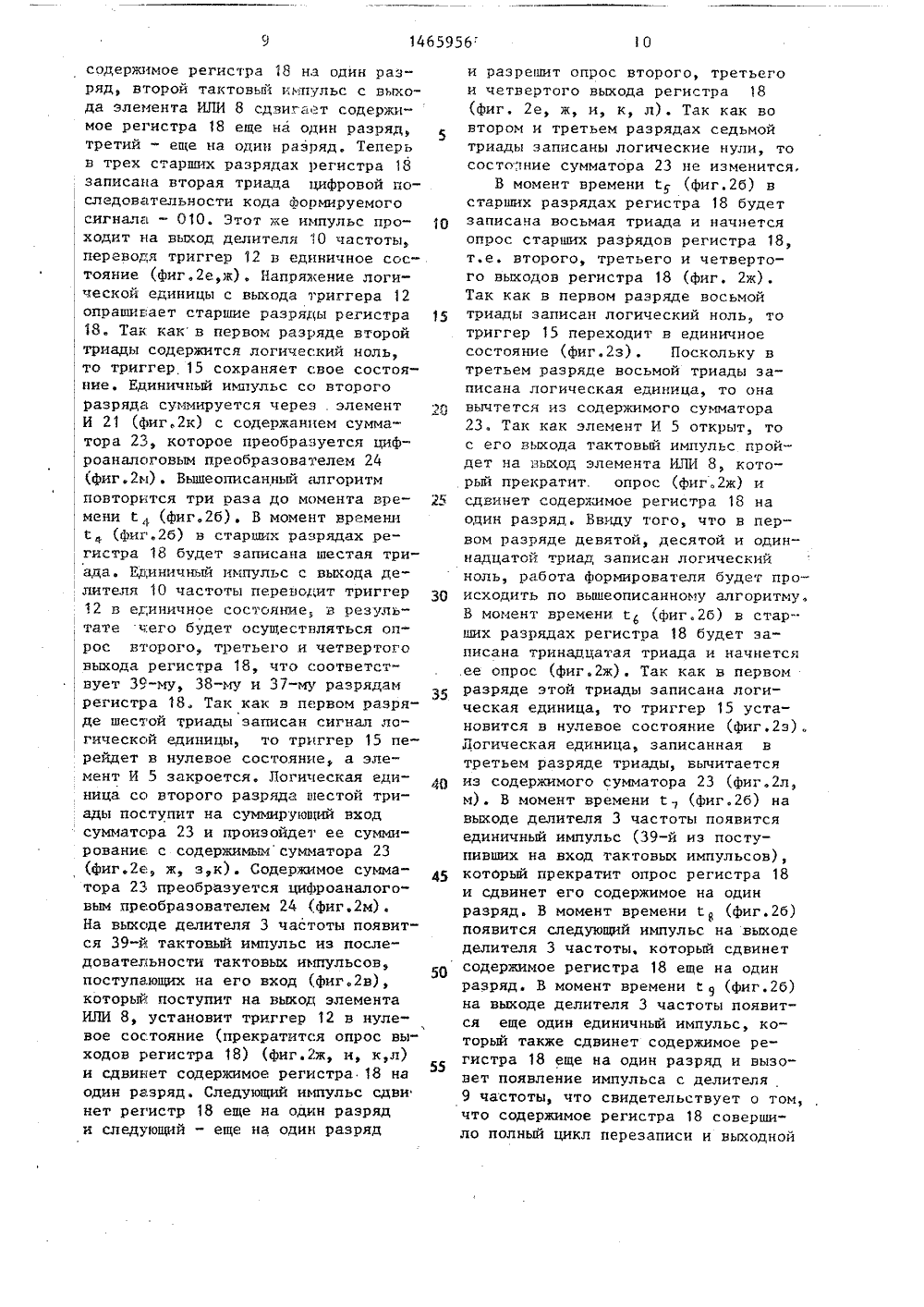

СОЮЗ СО 8 ЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 5 Н 4 Н 03 К ПИСАН БРЕТЕНИ СВИДЕТ ВТОРСН ЬСТВ ГОСУДАРСТВЕННЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССР В 1077045, кл. Н 03 К 4/06, 1984 .Палм, Уильямсон. Использование ЗУПВ и цифроаналогового преобразователя в генераторе сложных сигналов, - Электроника ,1978, У 1, с. 77-78.(54) ФОРМИРОВАТЕЛЬ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ(57) Изобретение относится к импульсной технике и может быть ис- пользовано в измерительных устройствах. Цель изобретения - повы-. шение точности формирования сигналов произвольной формы за счет применения переменного шага квантования по времени. Для достижения цели,901465956 в формирователь сигналов, содержа-.ший цифроаналоговый преобразователь24, операционный усилитель 25, тактовый генератор 1 и шину 27 данных,введены элементы И 2, 5, 17, 20, 2122, делители 3, 9, 10 частоты, триггеры 4, 12, 15, элементы ИЛИ 7, 8,11, 13, 14, регистр 18 сдвига, элемент НЕ 19, сумматор 23, Каждый интервал ступенчатой аппроксимацииформируемого сигнала кодируется тремя разрядами кода в регистре 18.Одиниз этих. разрядов кодирует величинушага квантования во времени, а двадругих - величину и знак приращениянапряжения на данном интервале, Информация о формируемом сигнале заносится в регистр 18 с шины 27 по импульсу на шине 28 "Запись". Затеминформация . последовательно выводит"ся из регистра 18. Делитель 10 обеспечивает сдвиг на три разряда в каж-,дом интервале. Максимальная длитель1465956 ность интервала определяется коэф"фициентом деления делителя 3, а минимальная равна трем периодам импульсов тактового генератора 1. Делитель9 определяет момент завершения формирования сигнала. 1(од в сумматоре23, в зависимости от логических уров" о Изобретение относится к импульс ной технике и предназначено дляиспользования в измерительных устройствах.Цель изобретения - повышение точности формирования сигналов произвольной формы за счет применения переменного шага квантования по времени.,1 ОНа фиг. 1 изображена функциональнаясхема формирователя сигналов произвольной формы; на фиг.2 - временныедиаграммы, поясняющие его работу;на Фиг.3 - график Формируемого сигнала,Формирователь сигналов произвольной Формы содержит тактовый генератор 1, .первый элемент И 2, первый делитель 3 частоты, первый триггер 4, второй элемент И 5, шину 6"Установка нуля", первый элемент ИЛИ7, второй элемент ИЛИ 8, второй делитель 9 частоты, третий делитель10 частоты, третий элемент ИЛИ 11,второй триггер 12, четвертый элементИЛИ 13, пятый элемент ИЛИ 14, третий триггер 15, шину 16 "Пуск", третий элемент И 17, регистр 18 сдвига,элемент НЕ 19, четвертый элемент И20, пятый элемент И 2 1, шестой элемент И 22, суыматор 23 цифроаналоговый преобразователь 24, операционный усилитель 25, выходную шину 26,шину 27 данных и шину 28 "Запись".Первый вход первого элемента И 235подключен к выходу тактового генератора 1, единичныйвыход первоготриггера 4 соединен со вторым входом первого элемента И 2, выход которого соединен с первым входом второго элемента И 5 и входом первогоделителя 3 частоты, выход которогосоединен с первым входом второгоэлемента ИЛИ 8 второй вход котороней на выходах регистра 18, меняетсяна единицу или остается неизменным,Соответственно изменяется выходноенапряжение. Шина 16 "Пуск" и шинаб "Установка нуля" используются дляуправления работой формирователя сигналов. 3 ил. го соединен с выходом второго элемента И 5, второй вход которого подключен к выходу третьего триггера 15,шика 6 соединена с первым входомпервого элемента ИЛИ 7, установоч"пым входом регистра 18 сдвига, установочным входом сумматора 23, выходпервого элемента ИЛИ 7 подключен кнулевому входу первого триггера 4,установочному входу первого делителя3 частоты, установочному входу третьего делителя 10 частоты, первомувходу четвертого элемента ИЛИ 13 ипервому входу пятого элемента ИЛИ14, выход которого соединен с нулевым входом третьего триггера 15,единичный вход которого подключенк выходу четвертого элемента И 20,шина 16 соединена с единичным входом первого триггера 4, установочным входом второго делителя 9частоты и первым входом третьегоэлемента ИЛИ 11, второй вход которого подключен к выходу третьегоделителя 10 частоты, а выход - кединичному входу второго триггера12, нулевой вход которого соединенс выходом четвертого элемента ИЛИ13, а выход - с первыми входами третьего 17, четвертого 20, пятого 21и шестого 22 элементов И, выходвторого элемента ИЛИ 8 соединен свходом второго делителя 9 частоты,входом третьего делителя 10 частоты,вторым входом четвертого элементаИЛИ 13 и сдвигающим входом регистра 18, выход второго делителя 9 частоты подключен к второму входу первого элемента ИЛИ 7, первый выходрегистра 18 соединен с входом регистра 18, данные которого поразрядно подключены к шине 27, шина 28соединена с входом записи регистра18, второй выход которого соединен14659 35 со вторым входом третьего элементаИ 17 и входом элемента НЕ 19, третий выход регистра 18 подключен квторому входу пятого элемента И 21,5а четвертый выход - к второму входушестого элемента И 22, выход которого соединен с нычитающим входомсумматора 23, суммирующий вход которого подключен к ныходу пятого 10элемента И 21, а выход - к входуцифроаналогового преобразователя24, выход которого соединен со вхо- .дом операционного усилителя 25, выход которого подключен к выходнойшине 26, выход элемента НЕ 19 соединен со вторым входом четвертого элемента И 20, выход третьего элементаИ 17 соединен со вторым входом пятого .элемента ИЛИ 14, нулевой выход первого триггера 4 соединен стретьим входом четвертого элементаИЛИ 13.Первый делитель 3 частоты имееткоэффициент деления, равный и, где 25и - разрядность регистра 18.Второй делитель 9 частоты коэффициент деления, равньп и , где и -разрядность регистра 18, первый счетный вход и второй устанавливающий З 0вход и предназначен для фиксацииокончания формирования сигналасразу после одного полного циклического сдвига информации в регистре 18,Третий делитель 10 частоты имееткоэффициент деления, равный трем,и предназначен для формирования сигнала опроса второго, третьего и четвертого выходов регистра 18.40Регистр 18 имеет и входов данныхдля параллельной записи цифровой последовательности кода формируемогосигнала, сдвигающий вход для приемасигнала при циклической перезаписисодержимого регистра сдвига 18, установочный вход для установки исходного нулевого состояния всех разрядов регистра 18, вход для циклической перезаписи содержимого регистра18, вход записи для разрешения записи информации в регистр 18 с еговходов данных, первый выход дляциклической перезаписи, содержащейся в регистре 18 информации, второйвыход для считывания информациистаршего и-го разряда регистра 18,третий выход для считывания информации с (и)-го разряда регистра 56 418, четвертый выход для считыванияинформации с (и)-го разряда.регистра 18. Регистр 18 предназначендля параллельного приема, последовательной циклической перезаписи цифроной последовательности кода формируемого сигнала, а также для ее потриадного считывания.Сумматор 23 может быть выполненв виде реверсивного счетчика.Формирователь сигналов произвольной формы работает следующим образом,В момент времени С (не показан)на шйну Ь подается единичный импульс, которьд устанавливает в нулевое состояние регистр 18, первыйтриггер 4, третий делитель 10 частоты, второй триггер 12, третийтриггер 15, первый делитель 3 частоты и сумматор 23,В момент времени Сна шину 27подается вся цифровая последовательность кода формируемого сигнала, которая записывается в регистр 18 припоступлении единичного импульса, по"даваемого на вход записи регистра18 по шине 28, Вся последовательность разбивается на триады. Первыйразряд каждой триады содержит информацию о сдвиге по оси времени(с), причем единица в этом разряде свидетельствует о сдвиге на одиншаг, ноль - о том, что сдвига нети содержание второго и третьего разрядов данной триады относится не кследующему, а к текущему шагу, т,е.имеет место сдвиг на один шаг только по оси уровня (Ч). Второй и третий разряды триад содержат информацию о характере сдвига по Ч, а именно: состояние 10 в этих разрядах говорит о одношаговом приращении по Чотносительно предыдущего шага, 01одношаговое уменьшение по Ч относительно предыдущего шага и 00 - отс.;ствие изменения по У относительнопредыдущего шага, состояние 11 запрещено.Формирователь сигналов произвольной формы готов к Формированию сигнала.В момент времени з на шину 16поступает единичный импульс, который устанавливает в нулевое состояние второй делитель 9 частоты ипереводит в единичное состоянцепервый триггер 4 и второй триггер14 б 5912 (через третий элемент ИЛИ 117.Напряжение логической единицы свыхода второго триггера 12 поступает на первые входы третьего 17,четвертого 20, пятого 21 и шестого 22элементов И. Если на третьем выходерегистра 18 присутствует напряжение логической единицы, то оно через ;открытый пятый элемент И 21 посту нает ка суммирующий вход сумматора 23 и суимируется в нем. Если на чет,вертом выходе регистра 18 присутствует напряжение логической единицы, то оно через шестой элемект И 1 б 32 поступает на вычитающий вход сумматора 23 и выччтается из его содеркимого. Присутствие напряжения логической единицы на третьем и четвертом входах регистра 18 одновре менно невозможно. Если на втором выходе регистра 18 присутствуетнапряжение логического нуля, то оно, инвертируясь элементом НЕ 19, поступа,ет через открытый четвертый элемент 25 И 20 на единичный вход третьего триггера 15 переводя его в единичное ,состояние. Напряжение логической ,единицы с выхода третьего триггера15 поступает на второй вход второго 30элемента И 5, открывая его. Еслина втором выходе регистра 18 присутствует напряжение логической едиьпщы, то третий триггер 15 не изменяет своего состояния, в результате чего второй элемент И 5 остается закрытьи.Напряжение логической единицы сединичного выхода первого триггера 4 поступает на второй вход первого элемента И 2, разрешая тем самым прохождение тактовых импульсов с выхода тактового генератора 1.Тактовые импульсы поступают на счетный вход первого делителя 3 частоты и ка первый вход второго элемента И 5. Если на втором входе второго элемента И 5 присутствует напряжение логического нуля, те. на втором выходе регистра 18 присутствует напряжение логической единицы, то второй элемент И 5 не пропускаеттактовые импульсы на свой выход. Им"пульс на выходе первого делителя 3 частоты формируется при подсчете им тактовых импульсов. Этот импульс, пройдя через второй элемент . ИЛИ 8, поступит на входы второго 9 и треть" его 10 делителей частоты, через чет 56 6вертый элемент ИЛИ 13, установит в нулевое состояние второй триггер 12 и циклически сдвинет на один разряд содержимое регистра 18. Так повторяется три раза. После поступления третьего импульса на первый счетный вход делителя 10 частоты на его выходе появится единичный импульс, который через третий элемент ИЛИ 11 переводит второй триггер 12 в единичное состояние. Напряжение логической единицы с выхода второго триггера 12 поступает на первые входы третьего 17, четвертого 20, пятого 21 и шестого 22 элементов И. Напряжение логической единицы с третьего или четвертого выходов регистра 18 поступит на суммирующий или вычитающий входы сумматора 23, суммируясь или вычитаясь с его содержимым, которое в свою очередь поступает на вход цифроаналогового преобразователя 24, преобразующего содержимое сумматора 23 в напряжение ступенча" той формы, поступающее на вход операционного усилителя 25, который формирует из него аналоговый сигнал, выдаваемый на выходную шину 26,Если на втором выходе регистра 18 присутствует напряжение логической единицы, то работа формирователя сигналов произвольной формы далее повторяется по вышеописанному алгоритму. Если на втором выходе регистра 18 присутствует напряжение логического нуля, то оно инвертируется элементом НЕ 19 и через открытый четвертый элемент И 20 переводит третий триггер 15 в единичное состояние. Напряжение логической единицы с выхода третьего триггера 15 поступает на второй вход второго элемента И 5, открывая его. Тактовые импульсы с выхода первого элемента И 2, проходя через второй элемент И 5, поступают на выход второго элемента ИЛИ 8 и подаются на входы второго 9 и третьего 10 делителей частоты. Первый импульс переводит второй триггер 12 в нулеВое состояние. Тактовые импульсы с выхода второго элемента ИЛИ 8 сдвигают содержимое регистра 18. Когда содержимое регистра будет сдвинуто на три разряда, то на выходе третьего делителя 10 частоты появится импульс, который переведет .второй триггер 12 в единичное состояние. Напряжение логической еди 1465956ницы на выходе триггера 12 откроеттретий 17, четвертый 20, пятый 21и шестой 22 элементы И. Содержимоевторого и третьего разряда регистра 18 будет суммироваться или вы 5читаться в сумматоре 23, изменяя илиоставляя без изменения его содержимое.Если на втором выходе регистра18 присутствует напряжение логического нуля, то работа формирователяпроисходит по вышеописанному алгоритму до появления при опросе второго выхода напряжения логическойединицы.Работа формирователя будет осуществляться до появления на выходевторого делителя 9 частоты импульса, который будет свидетельствоватьо том, что формируемый сигнал полностью синтезирован, т,е. содержимое регистра 18 совершило один циклцерезаписи. Этот импульс через первый элемент ИЛИ 7 поступает на нулевой вход первого триггера 4, переводя его в нулевое состояние, а наего единичном выходе появится на"пряжение логического нуля, котороепоступит на второй вход первого элемента И 2, запрещая тем самым прохождение тактовых импульсов на еговыход. На этом работа формирователясигналов заканчивается.При необходимости сформироватьследующий сигнал на шину 16 поступа 35ет единичный импульс и формировательсигналов начинает работать по вышеописанному алгоритму..Рассмотрим конкретный пример работы формирователя сигналов произ-.вольной формы (фиг.2).В момент времени 1 (не показан)на шину 6 подается единичный импульс,который устанавливает в нулевое сос .тояние блоки 18, 4, 10, 12, 15,3 и 23.В момент времени с(не показан)на шину 27 в параллельном виде подается 39-разрядная цифровая последо 50вательность кода формируемого сигнала вида: 010 010 010 010 010 110100 001 001 001 001 001 101. Подается единичный импульс на шину 28и информация записывается в блок 18по триадам:010 - первая триада (записываетсяв старшие разряды регистра 18); 010 - вторая триада;010 - третья триада,010 - четвертая триада,010 - пятая триада,110 " шестая триада;100 - седьмая триада;001 - восьмая триада,001 - девятая триада001 - десятая триада,001 - одиннадцатая триада;001 - двенадцатая триада;101 - тринадцатая триада (записывается в младшие разрядырегистра 18).Формирователь сигналов произвольной формы готов к формированию сигнала. В момент времени Сз (фиг.2 б)на шину 16 поступает импульс, устанавливающий в нулевое состояние делитель 9 частоты и переводящий в единичное состояние триггер 4 и триггер 12. На выходе триггера 12 появляется напряжение логической единицы (фиг.2 ж), которое открывает элемента И 17 20, 21 и 22. Так какпервый разряд первой триады содержит логический ноль, то на выходеэлемента И 20 появится напряжениелогической единицы (фиг.2 и), которое переведет в единичное состояние триггер 15 (фиг.2 з) . Так как вовтором разряде первой триады записана логическая единица, то на выходе элемента И 21 фпоявится напряжение логической единицы (фиг.2 к),которое поступит на. суммирующийвход сумматора 23, Содержимое сумматора 23 поступит на вход цифроаналогового преобразователя 24, навыходе которого будет присутствовать сигнал, пропорциональный содержимому сумматора 23, т.е. единице.(фиг.2 м) .Напряжение логической единицы свыхода триггера 4 разрешит прохождение через элемент И 2 тактовыхимпульсов с тактового генератора 1.Так как на втором входе элемента И5 присутствует напряжение логической единицы с триггера 15, то навыход элемента ИЛИ 8 будут поступать тактовые импульсы (фиг, 2 г) .Первый тактовый импульс с выходаэлемента ИЛИ 8 установит триггер 12в нулевое состояние и опрос 39-го,38-го и 37-го разрядов регистра18 прекращается (фиг.2 г, ж, и, к)./Этот же тактовый импульс сдвигаетсодержимое регистра 18 на один разряд, второй тактовый импульс с выхода элемента ИЛИ 8 сдвигает содержимое регистра 18 еще на один разряд, третий - еще на один разряд, ТепеРь в трех старших разрядах регистра 18 записана вторая триада цифровой но следовательности кода формируемого сигнала - 010. Этот же импульс про О ходит на Выход делителя 0 чястоты 1 переводя триггер 12 в единичное состояние (фиг.2 е,ж), Напряжение логической единицы с выхода триггера 12 опрашивает старшие разряды регистра 15 18. Так как в первом разряде второй триады содержится логический ноль, то триггер 15 сохраняет свое состояние. Единичный импульс со второго разряда суььлируется через . элемент И 21 (фиг.2 к) с содержанием сумматора 23, которое преобразуется цифроаналоговым преобразователем 24 (фиг,2 м). Вышеописанный алгоритм повторится три раза до момента вре мени , (фиг.2 б). В момент времени(фиг.26) в старших разрядах регистра 18 будет записана шестая три-ада. Единичжй импульс с выхода делителя 10 частоты переводит триггер 3 О 12 в единичное состояние, в резуль-тате .чего будет осуществляться опрос второго, третьего н четвертоговыхода регистра 18, что соответст"вует 39-муь 38-му и 37-му разрядам35регистра 18 Так как в первом разряде шестой триады записан сигнал логической единицы, то триггер 15 перейдет в нулевое состояние, а элемент И 5 закроется, Логическая еди О ница со второго разряда шестой триады поступит на суммирующий вход сумматора 23 и произойдет ее суммирование с содержимым сумматора 23 (фиг.2 е, ж, з,к). Содержимое сумматора 23 преобразуется цифроаналоговым преобразователем 24 (фиг,2 м). На выходе делителя 3 частоты появится 39-й тактовый импульс из последовательности тактовых импульсов, поступающих на его вход (фиг.2 в), который поступит на выход элемента ИЛИ 8, установит триггер 12 в нулевое состояние (прекратится опрос выходов регистра 18) (фиг.2 ж, и, к,л) и сдвинет содержимое регистра 18 на один разряд. Следующий импульс сдви нет регистр 18 еще на один разряд и следующий - еще на один разряд и Разрешит опрос второго, третьего и четвертого выхода регистра 18 (фиг, 2 е, ж, и, к, л). Так как во втором и третьем разрядах седьмой триады записаны логические нули, то состо,1 ние сумматора 23 не изменится,В момент времени С (фиг.26) в старших разрядах регистра 18 будет записана восьмая триада и начнется опрос старших разрядов регистра 18, т.е. второго, третьего и четвертого выходов регистра 18 (фиг, 2 ж), Так как в первом разряде восьмой триады записан логический ноль, то триггер 15 переходит в единичное состояние (фиг.2 з), Поскольку в третьем разряде восьмой триады записана логическая единица, то она вычтется из содержимого сумматора 3. Так как элемент И 5 открыт, то с его выхода тактовый импульс пройдет на выход элемента ИЛИ 8, который прекратит. опрос (фиг.2 ж) и сдвинет содержимое регистра 18 на оцин разряд. Ввиду того, что в первом разряде девятой, десятой и одиннадцатой триад записан логический ноль, работа формирователя будет происходить по вышеописанному алгоритму. В момент времени(фиг.26) в старших разрядах регистра 18 будет записана тринадцатая триада и начнется ее опрос (фиг.2 ж) . Так как в первом разряде этой триады записана логическая единица, то триггер 15 установится в нулевое состояние (фиг,2 э). Логическая единица, записанная в третьем разряде триады, вычитается из содержимого сумматора 23 (фиг,2 л, и) . В момент времени(фиг.26) на выходе делителя 3 частоты появится единичный импульс (39-й из поступивших на вход тактовых импульсов), который прекратит опрос регистра 18 и сдвинет его содержимое на один разряд. В момент времени(фиг.26) появится следующий импульс на выходе делителя 3 частоты. который сдвинет содержимое регистра 18 еще на один разряд. В момент времени(фиг.26) на выходе делителя 3 частоты появится еще один единичный импульс, который также сдвинет содержимое регистра 18 еще на один разряд и вызовет появление импульса с делителя 9 частоты, что свидетельствует о том, что содержимое регистра 18 совершило полный цикл перезаписи и выходнойсигнал сформирован. Триггер 4 также перейдет в нулевое состояние, напряжение логического нуля с его выхода (фиг.2 б) закроет элемент И 2, а напряжение логической единицы с его нулевого выхода запретит дальнейший опрос разрядов регистра 18. На этом работа формирователя сигналов по формированию сигнала по его цифровому коду заканчивается. Для вторичного и более формирования этого сигнала вышеописанный алгоритм пов-, торяется нужное количество раз при подаче сигнала на шину 16. Разрядность регистра 18 и коэффициенты деления делителей 3 и 9 частоты могут быть кратны числу три и должны быть равны или больше длины цифровой последовательности кода формируемого сигнала, Если длина последовательности меньше разрядности регистра 18, то она добавляется триадами вида 100, которые не влияют на форму импульса, а влияют только на момент его появления, Они добавляются впереди, если необходимо сформировать импульс с определенной временной задержкой.На фиг,З приведен еще один пример формирования сигнала, причем значения кодовых триад указаны под осью времени.Предлагаемый формирователь сигналов обеспечивает формирование сигнала произвольнои формы с переменным шагом квантования по времени. формула изобретения Формирователь сигналов произвольной формы, содержащий последовательно соединенные цифроаналоговый преобразователь, операционный усилитель и выходную шину, а также тактовый генератор и шину данньк, о тл и ч а ю щ и й с я тем, что, с целью повышения точности формирования сигналов произвольной формы за счет использования переменного шага квантования по времени, в неговведены первый элемент И, первый деяитель частоты, первый триггер, второй элемент И, шина "Установка нуля", первый элемент ИЛИ, второй элемент ИЛИ, второй делитель частоты, третий делитель частоты, третий элемент ИЛИ, второй триггер четвертый элемент ИЛИ, пятый эле.5 10 15 20 25 30 35 40 45 50 55 мент ШП 1, третий триггер, шина "Пуск", третий элемент И, регистр сдвига, элемент НЕ, четвертьй элемент И, пятый элемент И, шестой элемент И, сумматор данньк, шина "Запись", причем первый вход первогоэлемента И подключен к выходу тактового генератора, единичный выходпервого триггера соединен с вторымвходом первого элемента И, выходкоторого соединен с первым входомвторого элемента И и входом первого делителя частоты, выход которого соединен с первым входом второгоэлемента ИЛИ, второй вход которого соединен с выходом второго элемента И, второй вход которого подключен к выходу третьего триггера,шина "Установка нуля" соединена спервьм входом первого элемента ИЛИ,установочным входом регистра сдвига и установочным входом сумматора,вькод первого элемента ИЛИ подключен к нулевому входу первого триггера, установочному входу первого делителя частоты, установочному входу третьего делителя частоты, первому входу четвертого элемента ИЛИ и первому входу пятого элемента ИЛИ,вькод которого соединен с нулевымвходом третьего триггера, единичный вход которого подключен к выходу четвертого элемента И, шина "Пуск"соединена с единичным входом первого триггера, установочным входомвторого делителя частоты и первым входом третьего элемента ИЛИ, второйвход которого подключен к выходутретьего делителя частоты, а выход -к единичному входу второго триггера,нулевой вход которого соединен с выходом четвертого элемента ИЛИ, авькод - с первыми входами третьего,четвертого, пятого и шестого элементов И, выход второго элемента ИЛИсоединен с входом второго делителячастоты, входом третьего делителячастоты, вторым входом четвертогоэлемента ИЛИ и сдвигающим входомрегистра сдвига, выход второго делителя частоты подключен к второмувходу первого элемента ИЛИ, первыйвькод регистра сдвига соединен свходом регистра сдвига, входы данных которого поразрядно подключенык шине данных, шина Запись" соединена с входом записи регистра сдвига, второй выход которого соединен

СмотретьЗаявка

4294334, 04.08.1987

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БОРОДЕНКО ЕВГЕНИЙ ИВАНОВИЧ, ДУДАРЕВ ВАЛЕРИЙ АЛЕКСЕЕВИЧ, КУЗНЕЦОВ АЛЕКСАНДР ВЛАДИМИРОВИЧ, ЩЕГОЛЕВ ИГОРЬ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 4/02

Метки: произвольной, сигналов, формирователь, формы

Опубликовано: 15.03.1989

Код ссылки

<a href="https://patents.su/8-1465956-formirovatel-signalov-proizvolnojj-formy.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов произвольной формы</a>

Предыдущий патент: Генератор псевдослучайных последовательностей

Следующий патент: Генератор треугольного напряжения

Случайный патент: Газоразрядный антенный переключатель повышенного уровня мощности