Устройство для кодирования аналоговой информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1338074

Автор: Ходоровский

Текст

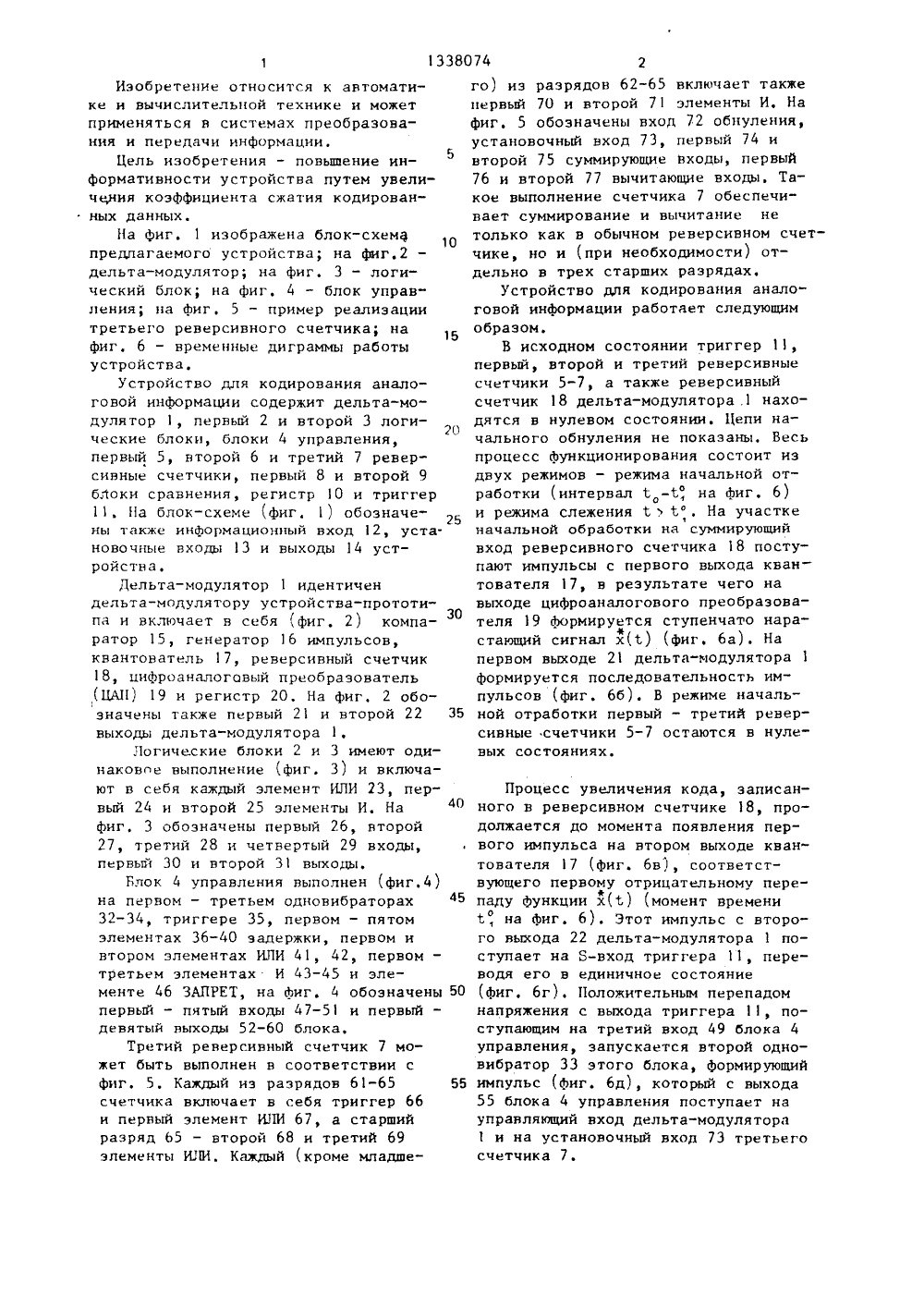

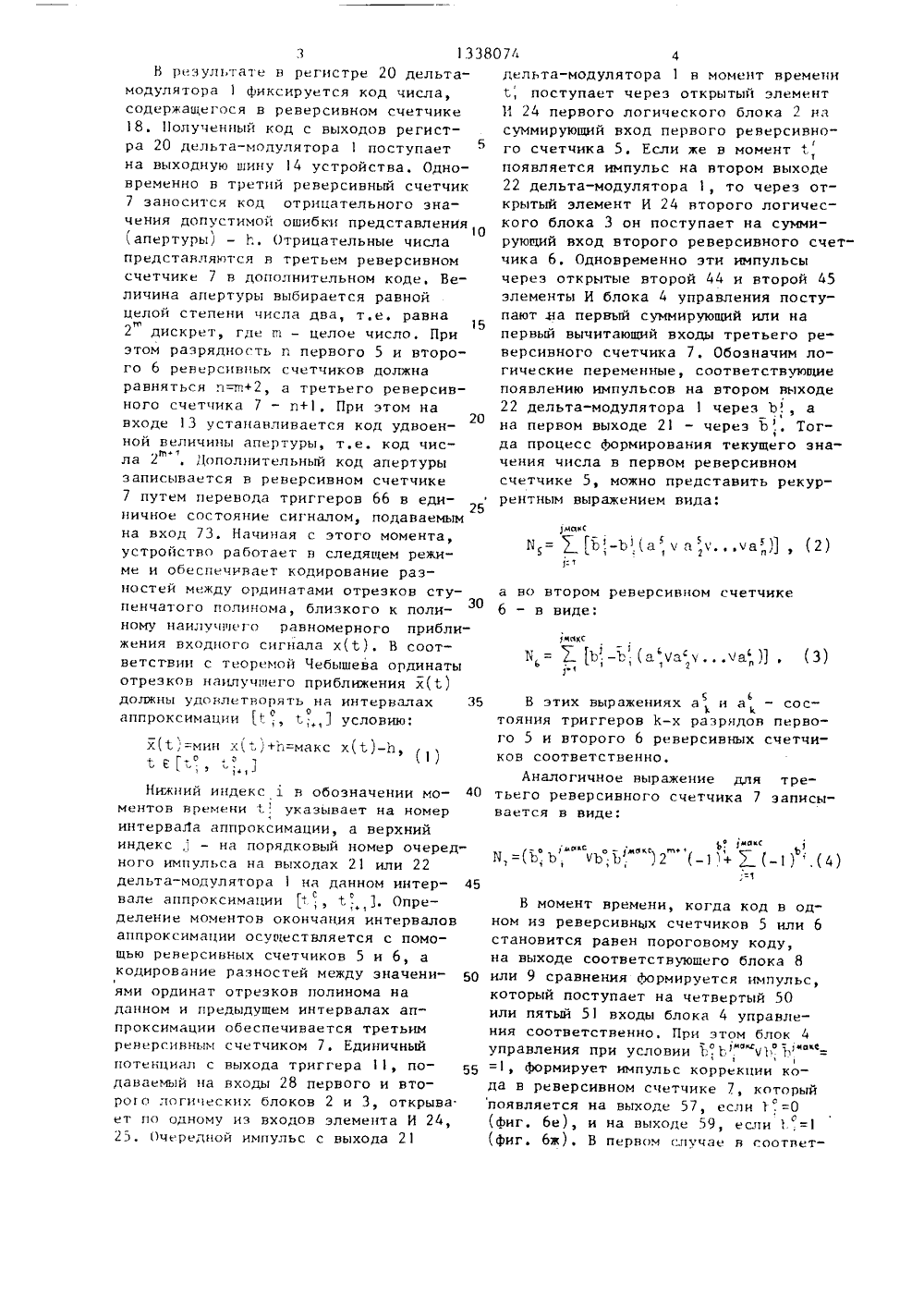

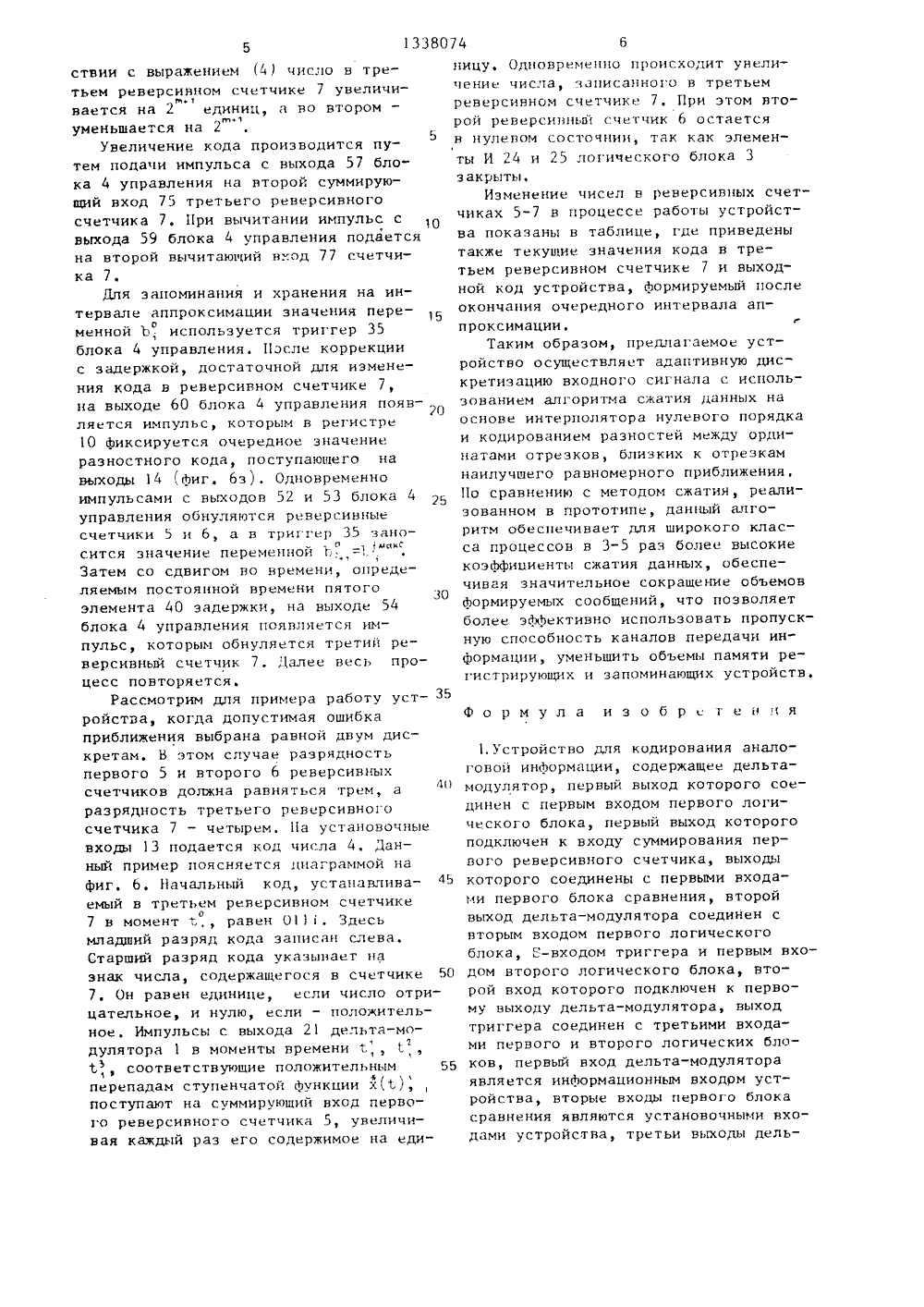

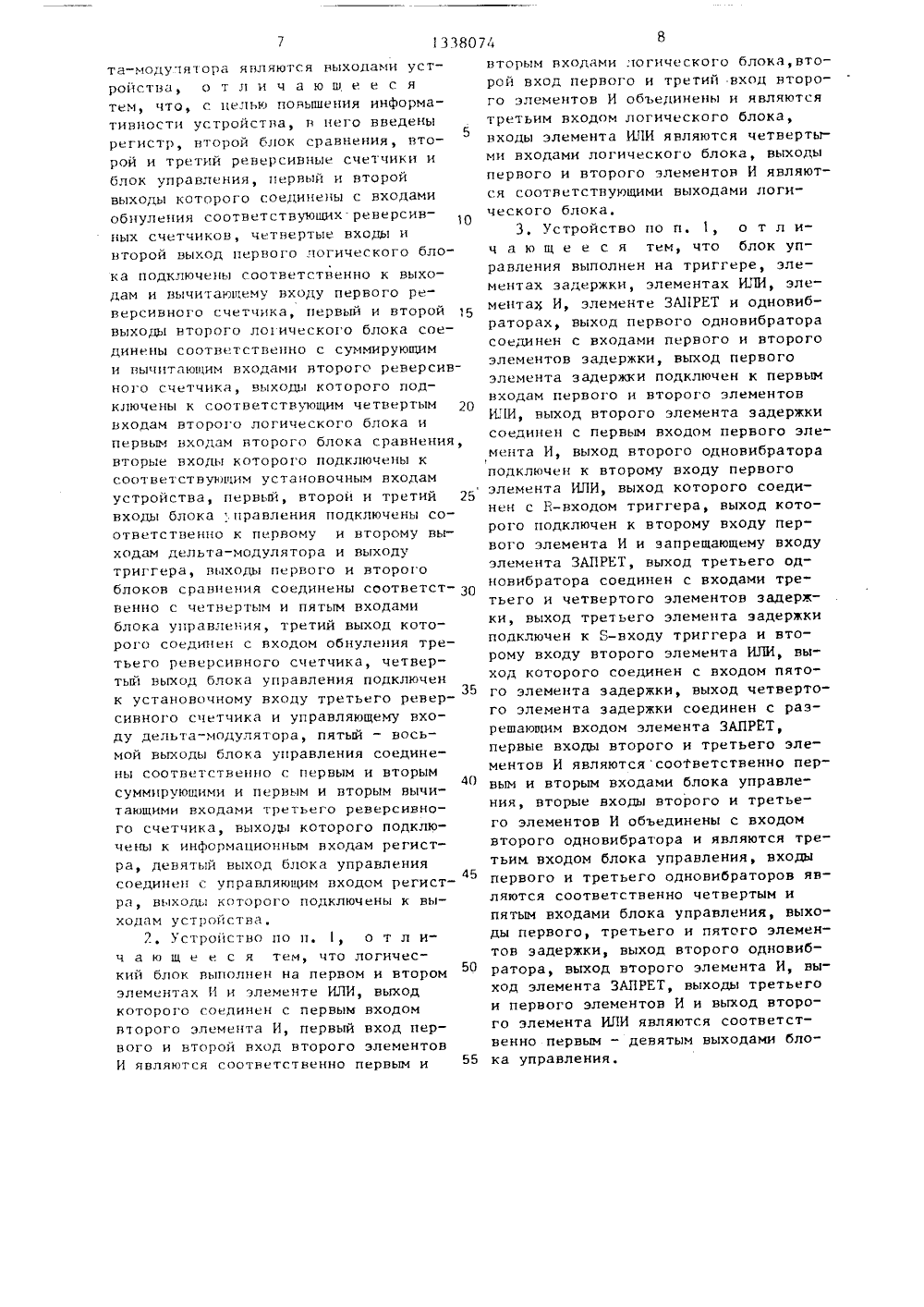

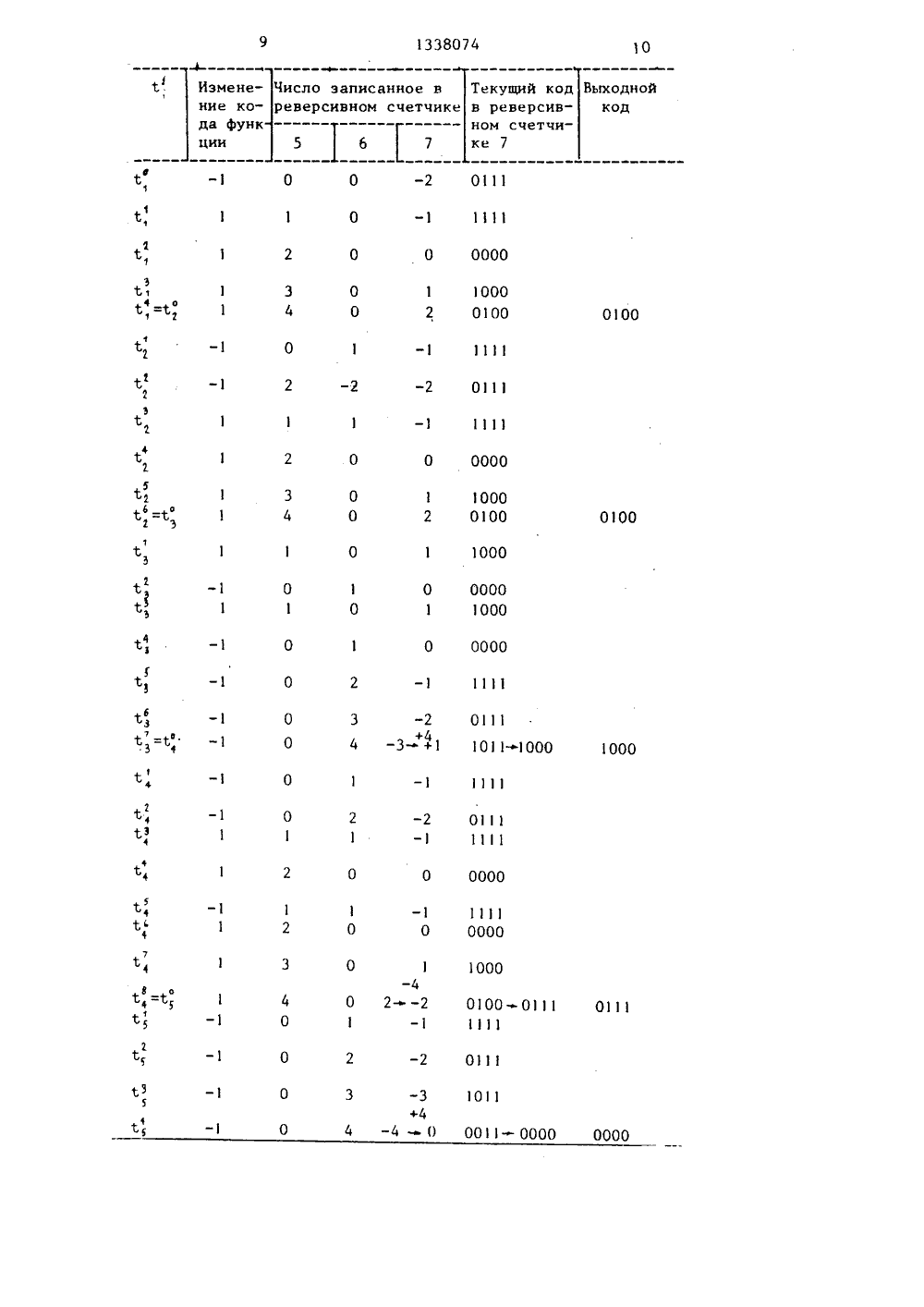

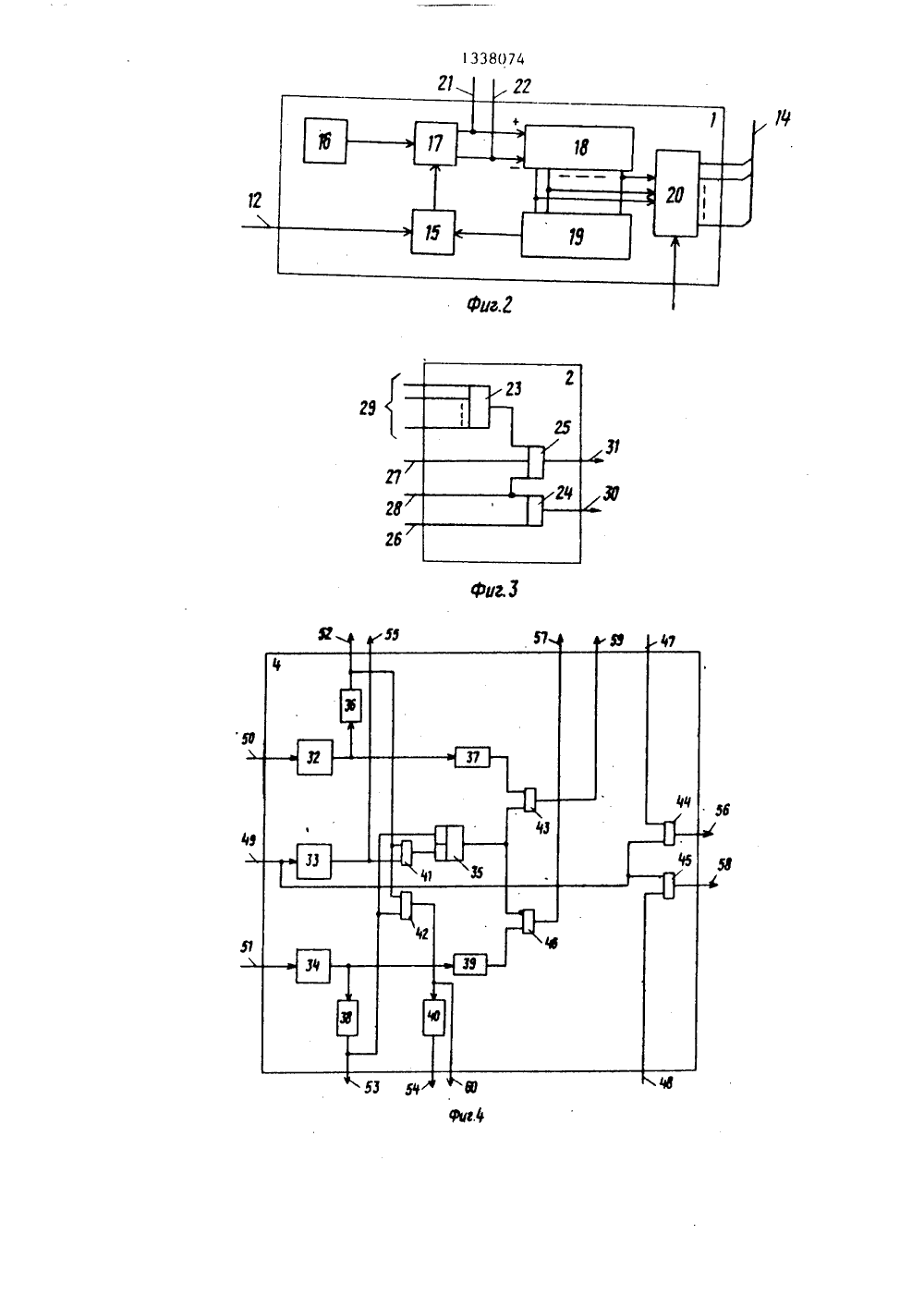

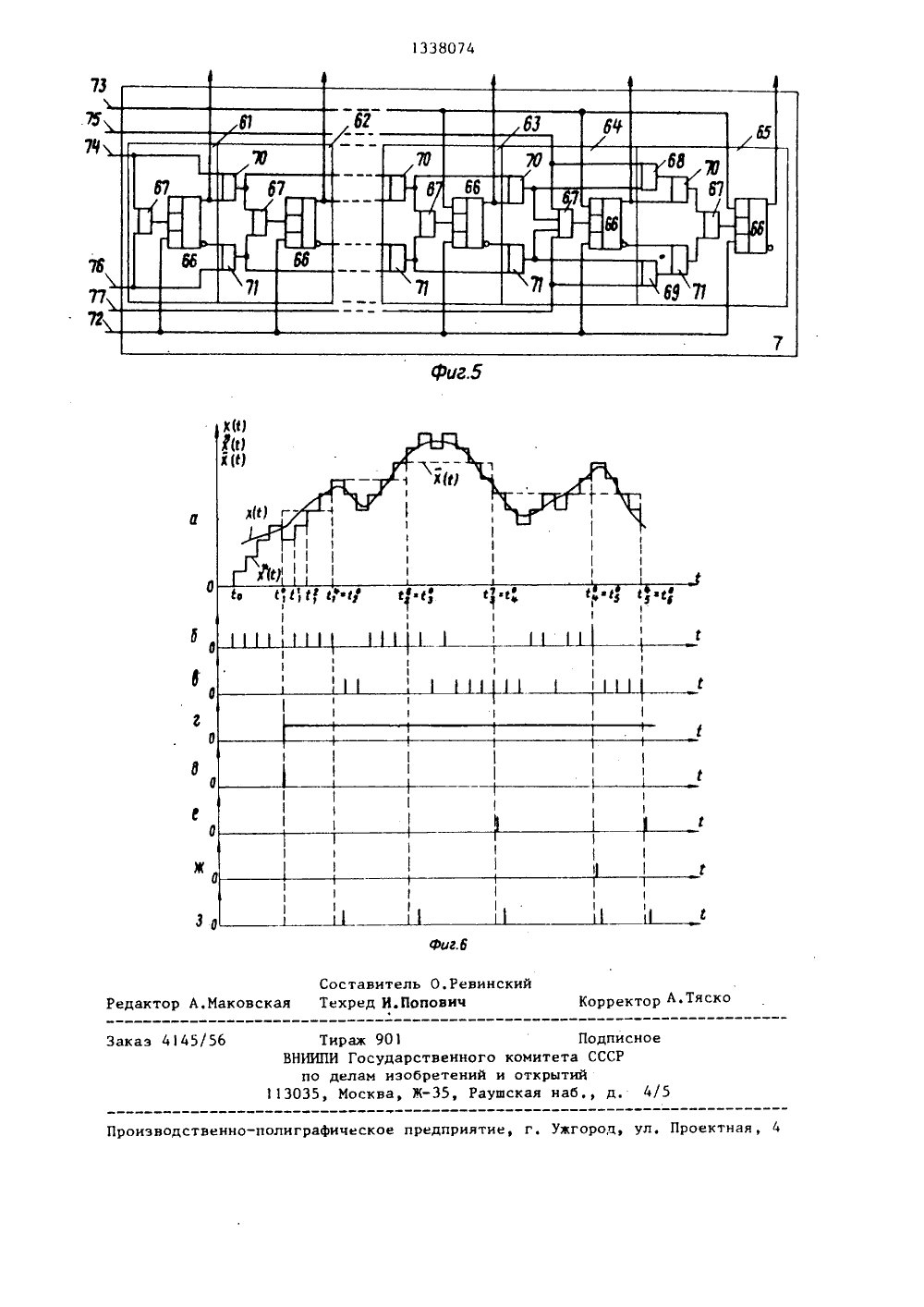

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 19) (1 3380 03 М 7/3 ПИСАНИЕ ИЗОБРЕТ кисти 974.ССР1982.АНИЯ АНАЛОк оптим высокий х. 2,з.п автомаЕгоГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ К А ВТОРСКОМУ СВИДЕТЕЛЬСГВ(57) Изобретение относится ктике и вычислительной техник использование в системах преобразования и передачи информации позволяетповысить информативность устройства.Устройство для кодирования аналоговойинформации содержит дельта-модулятор 1, логические блоки 2, 3, реверсивный счетчик 5, блок 8 сравнения итриггер 11. Благодаря введению реверсивных счетчиков 6, 7, блока 4 управления, блока 9 сравнения и регистра 10 в устройстве осуществляетсяадаптивная дискретизация входногосигнала, близкая альной, обеспечивающая более коэффициент сжатия данны ф-лы, 6 ил.Изобретение относится к автоматике и нычислительпой технике и можетприменяться в системах преобразования и передачи информации,Цель изобретения - повышение ин 5формативности устройства путем увеличения коэффициента сжатия кодированных данных.На фиг. 1 изображена блок-схемапредлагаемого устройства; на фиг,2дельта-модулятор; на фиг. 3 - логический блок; на фиг. 4 - блок управления; на фиг. 5 - пример реализациитретьего реверсивного счетчика; нафиг. 6 - временные диграммы работыустройства,Устройство для кодирования аналоговой информации содержит дельта-модулятор 1 первый 2 и второй 3 логиФ20ческие блоки, блоки 4 управления,первый 5, второй 6 и третий 7 реверсивные счетчики, первый 8 и второй 9бЛоки сравнения, регистр 1 О и триггер11. На блок-схеме (Фиг, 1) обозначены также информационный вход 12, уста.коночные входы 13 и выходы 14 устройства,Дельта-модулятор 1 идентичендельта-модулятору устройства-прототипа и включает в себя (фиг, 2) компа 30ратор 15, генератор 16 импульсов,квантователь 17, реверсивный счетчик18, цифроаналоговый преобразователь(ЦА 11) 19 и регистр 20, На фиг2 обозначены также первый 21 и второй 22 35выходы дельта-модулятора 1,Логические блоки 2 и 3 имеют одинаковое выполнение (Фиг. 3) и включают в себя каждый элемент ИЛИ 23, первый 24 и второй 25 элементы И. Нафиг, 3 обозначены первый 26, второй27, третий 28 и четвертый 29 входы,первый 30 и второй 31 выходы.Блок 4 управления выполнен (фиг.4)на первом - третьем одновибраторах32-34, триггере 35, первом - пятомэлементах 36-40 задержки, первом ивтором элементах ИЛИ 41, 42, первом -третьем элементах И 43-45 и элементе 46 ЗАПРЕТ, на Фиг. 4 обозначены 50перный - пятый входы 47-51 и первыйдевятый выходы 52-60 блока,Третий реверсивный счетчик 7 может быть выполнен в соответствии сфиг. 5. Каждый иэ разрядов 61-65 55счетчика включает в себя триггер 66и первый элемент ИЛИ 67, а старшийразряд 65 - второй 68 и третий 69элементы ИЛИ. Каждый (кроме младшего) из разрядов 62-65 включает также первый 70 и второй 71 элементы И, На фиг. 5 обозначены вход 72 обнуления, установочный нход 73, первый 74 и второй 75 суммирующие входы, первый 76 и второй 77 вычитающие входы, Такое выполнение счетчика 7 обеспечивает суммирование и вычитание не только как в обычном реверсивном счетчике, но и (при необходимости) отдельно в трех старших разрядах,Устройство для кодирования аналоговой информации работает следующим образом.В исходном состоянии триггер 11, первый, второй и третий реверсивные счетчики 5-7, а также реверсивный счетчик 18 дельта-модулятора 1 находятся в нулевом состоянии. Цепи начального обнуления не показаны, Весь процесс Функционирования состоит иэ двух режимов - режима начальной отработки (интервал С,-С, на Фиг. 6) и режима слежения СС, На участке начальной обработки на суммирующий вход реверсивного счетчика 18 поступают импульсы с первого выхода квантователя 17, в результате чего на выходе цифроаналогового преобразователя 19 Формируется ступенчато нара+стающий сигнал х(С) (фигба). На первом выходе 21 дельта-модулятора 1 формируется последовательность импульсов (фиг. бб). В режиме начальной отработки первый - третий реверсивные счетчики 5-7 остаются в нулевых состояниях. Процесс увеличения кода, записанного в реверсивном счетчике 18, продолжается до момента появления первого импульса на нтором выходе квантователя 17 (Фиг. бв), соответствующего первому отрицательному перепаду Функции х(С) (момент времени С, на Фиг. 6), Этот импульс с второго выхода 22 дельта-модулятора 1 поступает на Б-вход триггера 11, переводя его в единичное состояние (Фиг, бг), Положительным перепадом напряжения с выхода триггера 11, поступающим на третий вход 49 блока 4 управления, запускается второй одно- вибратор 33 этого блока, формирующий импульс (фиг. бд), который с выхода 55 блока 4 управления поступает на управляющий вход дельта-модулятора 1 и на установочный вход 73 третьего счетчика1338074 4дельта-модулятора 1 в момент времецнС, поступает через открытый элементИ 24 первого логического блока 2 насуммирующий вход первого реверсивного счетчика 5. Если же н моментпоявляется импульс на втором выходе22 дельта-модулятора 1, то через открытый элемент И 24 второго логического блока 3 он поступает на суммиОрующий вход второго реверсивного счетчика 6. Одновременно эти импульсычерез открытые второй 44 и второй 45элементы И блока 4 управления поступают ма первый суммирующий или на15первый вычитающий входы третьего реверсивного счетчика 7. Обозначим логические переменные, соответствующиепоявлению импульсов на нтором выходе22 дельта-модулятора 1 через Ь ана первом выходе 21 - через Ь Тогда процесс Формирования текущего значения числа в первом реверсивномсчетчике 5, можно представить рекуррентным выражением вида: В результате в регистре 20 дельта модулятора 1 фиксируется код числа, содержащегося в реверсивном счетчике 18. 11 олученцый код с выходов регистра 20 дельта-модулятора 1 поступает на выходную шину 14 устройства, Одно временно в третий реверсинный счетчи 7 заносится код отрицательного значения допустимой ошибки представлени (апертуры) - ",. Отрицательные числа представляются в третьем реверсивном счетчике 7 в дополнительном коде, Ве личина апертуры выбирается равной целой степени числа дна, те, равна 2 дискрет, где ш - целое число. При этом разрядность и первого 5 и второ го 6 реверсинцых счетчиков должна раннятьсн п=тп+2, а третьего реверсив ного счетчика 7 - и+1. При этом на входе 13 устанавливается код удвоенной величины апертуры, т,е, код чисуФ 1ла 2 , 11 ополцительный код апертуры записывается в реверсивном счетчике 7 путем перевода триггерон 66 в единичное состояние сигналом, подаваемым на вход 73. Начиная с этого момента, устройство работает в следящем режиме и обеспечивает кодирование разностей между ордицатами отрезков ступенчатого полицома, близкого к поли 30 ному наилучшего равномерного приближения входного сигнала х(С), В соответствии с теоремой Чебышева ординаты отрезков наилучшего приближения х(С) мсИС 35 В этих выражениях а и а - состояния триггеров Е-х разрядов перного 5 и второго 6 реверсивных счетчиков соответственно,Аналогичное выражение для тре тьего реверсивного счетчика 7 записывается н виде: Нккций индексв обозначении моментов времени С, указывает ца номер интерваЛа аппроксимации, а верхний индекс, - на порядковый номер очеред ного импульса на выходах 21 или 22 дельта-модулятора 1 на данном интервале аппроксимации С;, С., 3. Определение моментов окончания интервалов аппроксимации осуществляется с помощью реверсивных счетчиков 5 и б, а кодирование разностей между значени 1ями ординат отрезков полинома на данном и предыдущем интервалах аппроксимации обеспечивается третьим реверсивным счетчиком 7. Единичный потенциал с выхода триггера 11, подаваемый ца входы 28 первого и второо логических блоков 2 и 3, открыва. ет по одному из входов элемента И 24, 25, Очередной импульс с выхода 21 и,=(ь,. ь, дь;ь. ) 2 ( - 1)+( - 1) . (4),=45 должны удовлетворять на интервалахс 0аппроксимации (С С; 1 условию; х(С,=мин х(С)+п=макс х(С)-Ь, с " ";1 1 мднс1 =, 1 Ь-Ь (а у аунаД, (2) а но втором реверсивном счетчике6 - в виде: 1" = С Ь 1-ь (а час уна )3, (3)В момент времени, когда код в одном из реверсивных счетчиков 5 или 6 становится равен пороговому коду,на выходе соответствующего блока 8или 9 сравнения формируется импульс,который поступает на четвертый 50или пятый 51 входы блока 4 управления соответственно. При этом блок 4упр е я р, у овинЬ Н 1,О Р=1, формирует импульс коррекции кода в реверсивном счетчике 7, которыйпоявляется на выходе 57, если 1.=0ствии с выражением (4) число в третьем реверсивном счетчике 7 увеличив 1вается на 2 единиц, а во втором - уменьшается на 25Увеличение кода производится путем подачи импульса с выхода 57 блока 4 управления на второй суммирующий вход 75 третьего реверсивного счетчика 7, При вычитании импульс с выхода 59 блока 4 управления подается на второй вычитающий вход 77 счетчика 7.Для запоминания и хранения на интервале аппроксимации значения переоменной Ъ, используется триггер 35 блока 4 управления. После коррекции с задержкой, достаточной для изменения кода в реверсивном счетчике 7, на выходе 60 блока 4 управления появО ляется импульс, которым в регистре О фиксируется очередное значение раэностного кода, поступающего на выходы 14 ,фиг, 6 з). Одновременно импульсами с выходов 52 и 53 блока 4 управления обнуляются реверсивные счетчики 5 и 6, а в триггер 35 заносится значение переменной Ь, =1 Затем со сдвигом во времени, определяемым постоянной времени пятого30 элемента 40 задержки, на выходе 54 блока 4 управления появляется импульс, которым обнуляется третий реверсивный счетчик 7. Далее весь процесс повторяется.Рассмотрим для примера работу уст ройства, когда допустимая ошибка приближения выбрана равной двум дискретам. В этом случае разрядность первого 5 и второго 6 реверсивных счетчиков должна равняться трем, а разрядность третьего реверсивного счетчика 7 - четырем. На установочные входы 13 подается код числа 4. Данный пример поясняется диаграммой на фиг, 6. Начальный код, устанавливаемый в третьем реверсивном счетчикео7 в момент т равен О 11. Здесь младший разряд кода записан слева. Старший разряд кода указывает на знак числа, содержащегося в счетчике 50 7. Он равен единице, если число отрицательное, и нулю, если - положительноеИмпульсы с выхода 21 дельта-модулятора 1 в моменты времениьС соответствующие положительным 55 перепадам ступенчатой функции х(1), поступают на суммирующий вход первого реверсивного счетчика 5, увеличивая каждый раз его содержимое на единицу, Одновременно происходит увеличение числа, записанного в третьем реверсивном счетчике 7. При этом второй реверсивный счетчик 6 остается в нулевом состочнии, так как элементы И 24 и 25 логического блока 3закрыты,Изменение чисел в реверсивных счетчиках 5-7 в процессе работы устройства показаны в таблице, где приведены также текущие значения кода в третьем реверсивном счетчике 7 и выходной код устройства, формируемый после окончания очередного интервала аппроксимации.гТаким образом, предлагаемое устройство осуществляет адаптивную дискретизацию входного сигнала с использованием алгоритма сжатия данных на основе интерполятора нулевого порядка и кодированием разностей между ординатами отрезков, близких к отрезкам наилучшего равномерного приближенияПо сравнению с методом сжатия, реализованном в прототипе, данный алгоритм обеспечивает для широкого класса процессов в 3-5 раз более высокие коэффициенты сжатия данных, обеспечивая значительное сокращение объемов формируемых сообщений, что позволяет более эффективно использовать пропускную способность каналов передачи информации, уменьшить объемы памяти регистрирующих и запоминающих устройств,Формула и з о б р е г е и и я1,устройство для кодирования аналоговой информации, содержащее дельта- модулятор, первый выход которого соединен с первым входом первого логического блока, первый выход которого подключен к входу суммирования первого реверсивного счетчика, выходы которого соединены с первыми входами первого блока сравнения, второй выход дельта-модулятора соединен с вторым входом первого логического блока, Г-входом триггера и первым входом второго логического блока, второй вход которого подключен к первому выходу дельта-модулятора, выход триггера соединен с третьими входами первого и второго логических блоков, первый вход дельта-модулятора является информационным входрм устройства, вторые входы первого блока сравнения являются установочными входами устройства, третьи выходы дель 133807 чта-модучятора являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения информативности устройства, в него введены регистр, второй блок сравнения, второй и третий реверсивные счетчики и блок управления, первый и второй выходы которого соединены с входами обнуления соответствующих.реверсивных счетчиков, четвертые входы и второй выход первого логического блока подключены соответственно к выходам и нычитающему входу первого реверсивного счетчика, первый и второй 15 выходы второго логического блока соединены соответственно с суммирующими вычитающим входами второго реверсивного счетчика, выходы которого подключены к соответствующим четвертым 20входам второго логического блока ипервым входам второго блока сравнения,вторые входы которого подключены ксоответствующим установочным входамустройства, первый, второи и третий 25входы блока ,правления подключены соответственно к первому и второму выходам дельта-модулятора и выходутриггера, выходы первого и второгоблоков сравнения соединены соответст- Зрвенно с четвертым и пятым входамиблока управления, третий выход которого соединен с входом обнуления третьего реверсивного счетчика, четвертый выход блока управления подключен35к установочному входу третьего реверсивного счетчика и управляющему входу дельта-модулятора, пятый - восьмой выходы блока управления соединены соответственно с первым и вторым40суммирующими и первым и вторым вычитающими входами третьего реверсивного счетчика, выходы которого подключены к информационным входам регистра, девятый выход блока управления45соединен с управляющим входом регистра, выходы которого подключены к выходам устройства,2, Устройство по и1, о т л ич а ю щ е е с я тем, что логический блок выполнен на первом и второмэлементах И и элементе ИЛИ, выходкоторого соединен с первым входомвторого элемента И, первый вход первого и второй вход второго элементовИ являются соответственно первым и вторым входами логического блока,второй вход первого и третий вход второго элементов И объединень 1 и являютсятретьим входом логического блока,входы элемента ИЛИ являются четвертыми входами логического блока, выходыпервого и второго элементов И являются соответствующими выходами логического блока,3, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления выполнен на триггере, элементах задержки, элементах ИЛИ, элементах И, элементе ЗАПРЕТ и одновибраторах, выход первого одновибраторасоединен с входами первого и второгоэлементов задержки, выход первогоэлемента задержки подключен к первымвходам первого и второго элементовИЛИ, выход второго элемента задержкисоединен с первым входом первого элемента И, выход второго одновибратораподключен к второму входу первогоэлемента ИЛИ, выход которого соединен с Б-входом триггера, выход которого подключен к второму входу первого элемента И и запрещающему входуэлемента ЗАПРЕТ, выход третьего одновибратора соединен с входами третьего и четвертого элементов задержки, выход третьего элемента задержкиподключен к Б-входу триггера и второму входу второго элемента ИЛИ, выход которого соединен с входом пятого элемента задержки, выход четвертого элемента задержки соединен с разрешающим входом элемента ЗАПРЕТ,первые входы второго и третьего элементов И являются соответственно первым и вторым входами блока управления, вторые входы второго и третьего элементов И объединены с входомвторого одновибратора и являются третьим входом блока управления, входыпервого и третьего одновибраторов являются соответственно четвертым ипятым входами блока управления, выходы первого, третьего и пятого элементов задержки, выход второго одновибратора, выход второго элемента И, выход элемента ЗАПРЕТ, выходы третьегои первого элементов И и выход второго элемента ИЛИ являются соответственно первым - девятым выходами блока управления.ние кода функции 1 5 6 72 -2 0111 3 -3 1011 +4 4 -4 - О 0011 0000 0000 Число записанное вреверсивном счетчик Текущий кодв реверсивном счетчике 7аказ 4145/56 изводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 Тираж 901 ВНИИПИ Государственного по делам изобретений 13035, Москва, Ж, РауПодписное комитета СССР открытий ская наб д, 4/5

СмотретьЗаявка

4046773, 31.03.1986

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

ХОДОРОВСКИЙ АЛЕКСАНДР ЗИНОВЬЕВИЧ

МПК / Метки

МПК: H03M 7/38

Метки: аналоговой, информации, кодирования

Опубликовано: 15.09.1987

Код ссылки

<a href="https://patents.su/8-1338074-ustrojjstvo-dlya-kodirovaniya-analogovojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования аналоговой информации</a>

Предыдущий патент: Следящий аналого-цифровой преобразователь

Следующий патент: Кодек каскадного блочного кода

Случайный патент: Способ испытания изогнутыхрамных узлов