Устройство для моделирования сетевых графиков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1300481

Автор: Щетинин

Текст

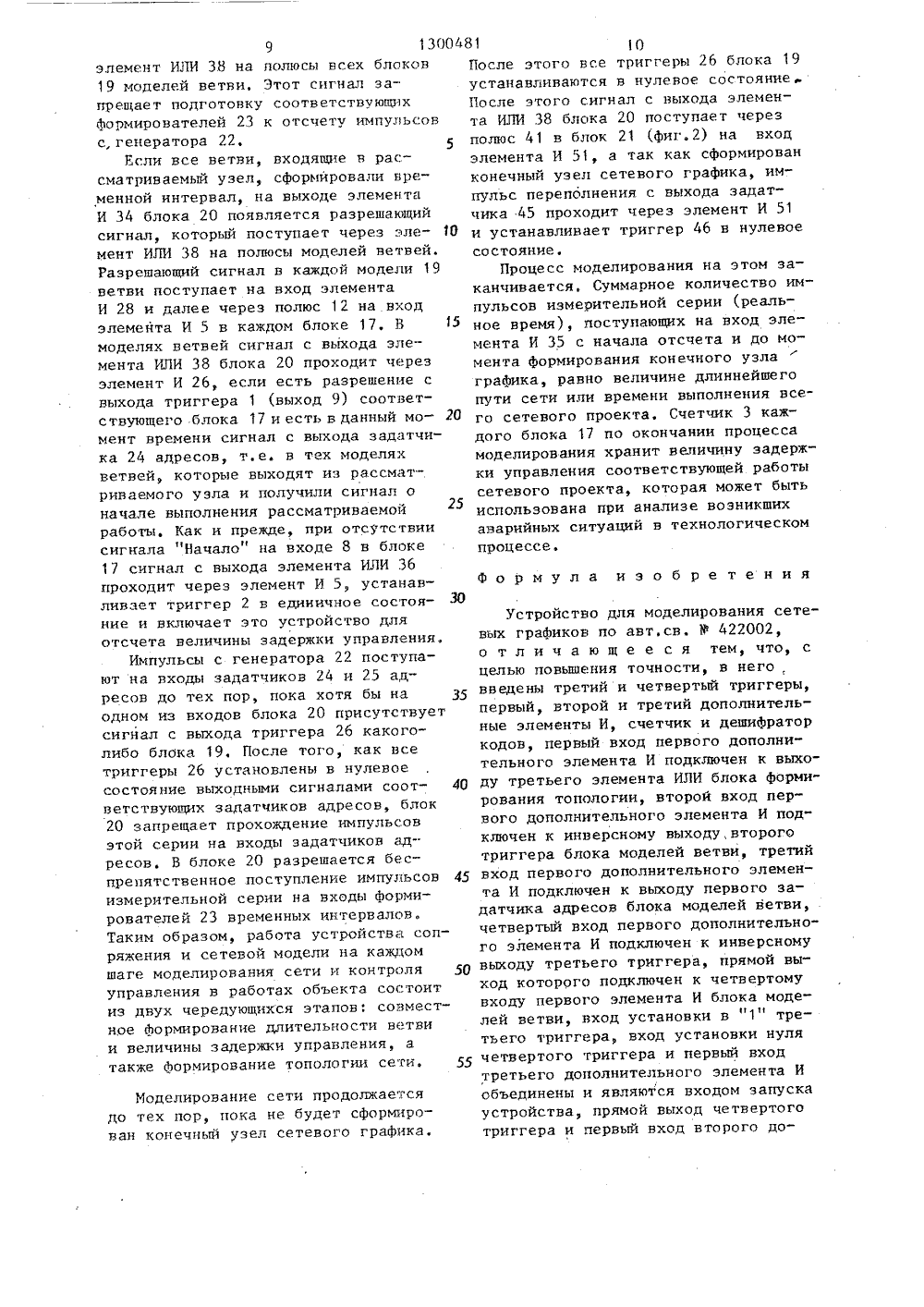

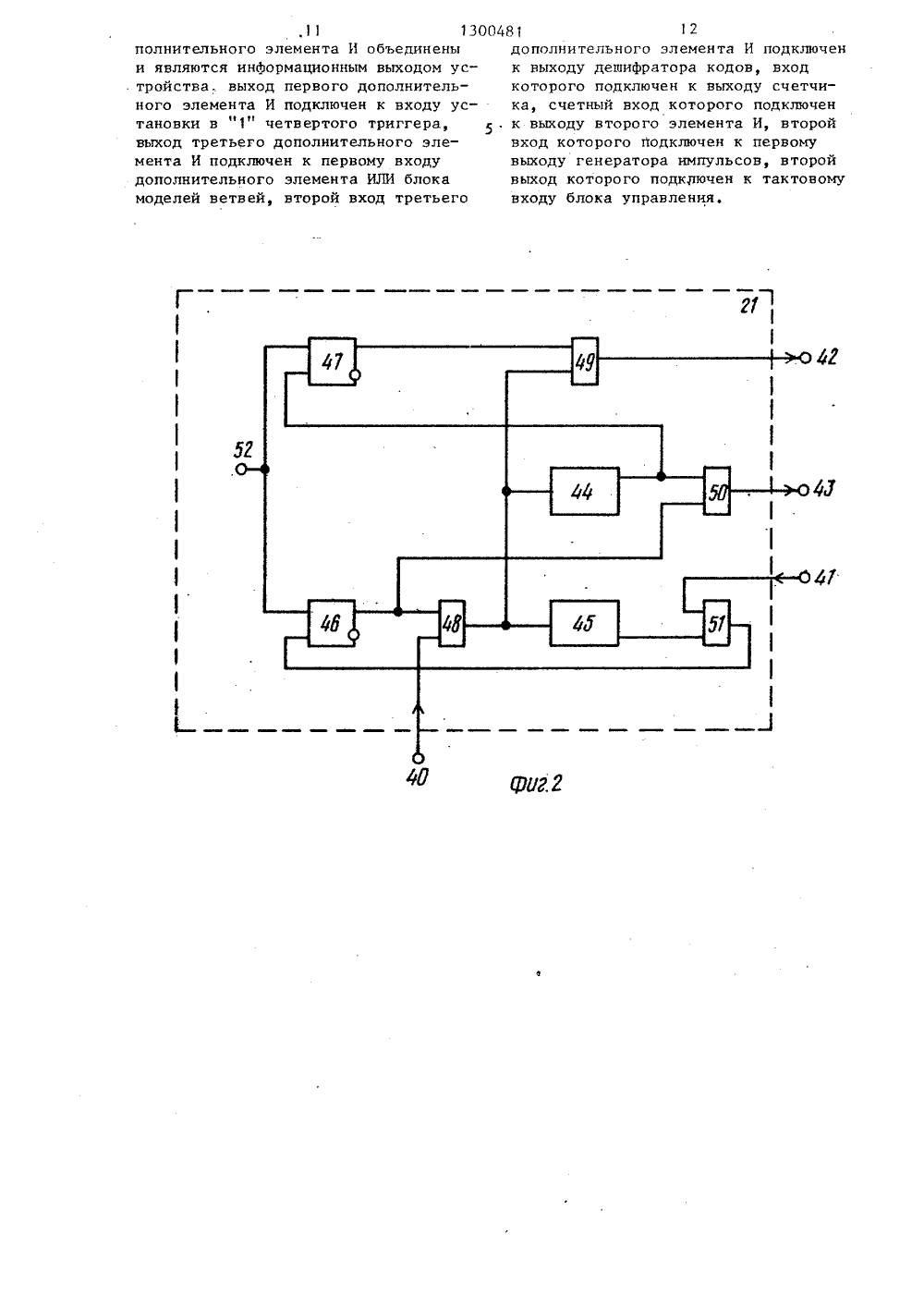

(ЮС 06 Р 13/00, С 06 С 7/4 ЕТЕН ВТОРСНОЧУ СВИДЕТЕЛЬСТВУ ОВА(57) Изобретение ольной технике ос мо вычи т быть ис я специал ых машин с делировани ользовано для соп ированных вычисли ель- Цель а ным объектом. тся повышение обретени ство СС 8, 1972 тво для лиро ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ПИСАНИЕ(71) Институт проблемв энергетике АН УССР(54) УСТРОЙСТВО ДЛЯСЕТЕВЫХ ГРАФИКОВ точности. Устройния содержит тре-о1300тий триггер 1, четвертый триггер 2, счетчик 3, дешифратор кодов 4, первый дополнительный элемент И 5, второй дополнительный элемент И 6 н третий дополнительный элемент И 7, вход 8 запуска устройства, выходы 9, 10 и 11 и входы 12, 13, 14 и 15 устройства. Использование новых элементов в устройстве обеспечивает повышение точности за счет обмена информацией между объектом и моделью сетевого графика в реальном масштабе времени для оперативного контроля и передачи управления по сетевому проекту, что позволяет существенно уменьшить время выполнения технологического процесса, Так, в частности, если сете 481вой проект моделируется параллельно с выполнением реального объекта, то в сетевой модели всегда имеется информация о планируемом состоянии объекта, которая сравнивается с реальным положением дел в проекте и обеспечивает оперативное управлениеатехнологическим процессом. При этом отпадает необходимость осуществлять расчет сетевого графика в контрольных точках моделируемой сети, находить множество операций, принадлежащих в данный момент времени критическому пути, а также вводить корректуру для работ, имеющих большие времена задержек. 3 ил.1Изобретение относится к вычислительной технике, а именно к устройству для сопряжения специализированных вычислительных машин с реальнымобъектом, и может быть использованопри построении специализированныхмашин для моделирования сетевых графиков и сопряжения их с объектом вреальном масштабе времени,Целью изобретения является повышение точности,На фиг,1 представлена структурнаясхема устройства для моделированиясетевых графиков; на Фиг.2 - блокуравления сетевой модели.; на фиг.3 -формирователь временного интервала.Устройство для сопряжения содержит третий триггер 1, четвертыи триггер 2, счетчик 3, дешифратор 4 кодов,первый-третий дополнительные элементы И 5-7На фиг,1 обозначены вход 8 запуска (или вход команды "Начало выполнения операции в объекте") устройства, выход 9 команды "Началоформирования ветвей, входящих в данный узел модели сети",;выход 10 команды "Окончание формирования ветвей,входящих в данный узел моделируемойсети", выход 11 команды "Задержканачала выполнения данной работыобъектом", вход 12 задания адреса начального узла сетевой модели, вход13 задания сигнала "Начало формиро 2вания временного интервала, пропор 11ционального длине ветви модели сетивход 14 задания сигнала "Окончаниеформирования временного интервала,пропорционального длине ветви моделисети", вход 15 тактовых импульсовустройства, известная модель 16 сети, блок 17 сопряжения объекта с сетевой моделью и объект 18,10Известная модель 16 сети содержитблок 19 моделей ветви, блок 20 формирования топологии, блок 21 управления,генератор 22 импульсов,Каждый из блоков 19 моделей ветви модели 16 сети содержит формиро- .ватель 23 временных интервалов, задатчики 24 начального и 25 конечного адресов узлов модели, триггеры 26и 27, элементы И 28 и 29, элементыИЛИ 30 и 31, элемент НЕ 32Блок 20 формирования топологиисодержит элементы И 33-35, элементыИЛИ 36-38 элемент НЕ 39,На фиг.2 обозначены входные 40и 41 и выходные 42 и 43 полюса блока 21 управления.Блок 21 управления состоит иззадатчиков 44 и 45 начального и ко нечного узлов сетевого графика соответственно (выполненных аналогичнозадатчикам 24 и 25 блока 19 моделейветвей), триггеров 46 и 47, элементов И 48-51, входа 52 запуска блока, 3 13 ОО 4Формирователь 23 временных интервалов содержит счетчик 53, элементИ 54 и триггер 55.В устройстве для сопряжения модели сети с объектом в качестве счет 5чика 3 может быть использован любойдвоичный счетчик с параллельным инверсным выходом, емкость которогоопределяется максимальной допустимойвеличиной задержки при передаче уп Оравления по сетевому графику.Дешифратор 4 кодов может быть выполнен в виде многовходового элемента И-НЕ, число входов которого определяется количеством разрядов 15счетчика 3. Дешифратор 4 предназначендля определения состояния счетчика 3,отличного от нулевого.Сетевой график диктует необходимость соблюдения определенной очередОности выполнения работ,Так, одни работы не могут быть начаты, пока не окончены другие работы.Минимальное время, за которое можетбыть выполнен комплекс работ, определяется совокупностью наиболее медленных работ Временная разновидность задачи расчета сетевого графика заключается в нахождении формы и.длины максимального пути между на Очальным и конечным событиями, так называемого критического (длиннейшего)пути. Методология сетевого планирования и управления использует целыйряд характеристик сети которые определяются через длины критическихпутей между различили событиями графика. Нахождение этих характеристики составляет содержание задачи.В данном случае сетевая модель 4 Оосуществляет моделирование объектав реальном масштабе времени. В объекте в это время осуществляется непос"редствеиное выполнение технологических операций. При этом каждая работа 45ч в объекте ие соединяется конструктивно с другими работами черезвершины Х,; и Х а ее начало выполнения зависит только от окончаниявыполнения работ, предшествующих потехнологическому процессу. Окончаниеработы ю, , в свою очередь, также13влияет на начало последующих работпо технологическому проекту,- 55Обеспечение обмена информациеймежду реальным объектом и модельюсети в реальном масштабе времени дляоперативного контроля и передачи уп 81 4равления по сетевому проекту позволяет существенно уменьшить время выполнения технологического процесса. Если сетевой проект моделируется параллельно с выполнением реального объекта, то в сетевой модели всегда имеется информация о планируемом состоянии объекта, которая сравнивается с реальным положением дел в проекте 1 и обеспечивает оперативное чправление технологическим процессом. При этом отпадает необходимость осуществлять расчет сетевого графика в контрольных точках моделируемой сети, находить множество операций, принадлежащих в данный момент времени критическому пути, и вводить корректуру для работ, имеющих большие времена задержек,Рассмотрим работу устройства при обеспечении обмена информацией между объектом и известной моделью сети в реальном масштабе времени для оперативного контроля перецачи управления по сетевому проекту.В модели сети в задатчики 21 и 22 адресов всех блоков моделей ветви Предварительно заносятся количества импульсов, дополняющие номера соответственно начальных и конечных узлов ветвей сетевого графика до полной емкости счетчиков. В формирователь 20 временных интервалов заносится количество импульсов, соотве- ствующее длительности моделируемой ветви, а триггеры 23 и 24 устанавливаются в нулевое состояние.В блоке 21 управления предварительно в задатчики 44 и 45 заносятся соответственно дополнительный код адреса начального и конечного узлов исследуемого сетевого графика, триггеры 46 и 47 устанавливаются в нулевое состояние. В устройстве для моделирования триггеры 1 и 2 и счетчик 3 предварительно устанавливаются в нулевое состояние.Для включения модели сети синхронно с работой объекта сигнал "Пуск" подается на полюс 52 блока 21 в момент, соответствующий,планируемому времени начала выполнения контролируемого проекта. Сигнал "Пуск" в блоке 21 управления поступает на входы триггеров 46 и 47 и устанавливает их в единичные состояния, Единичное состояние триггера 46 выдает13 ОО 4 Сигнал с выхода элемента ИЛИ 38 блока 20 Формирования топологии поступает на входы, элементов И 28 моделей 18 ветвей и через полюс 14- на входы элемента И 5 устройства 17 для сопряжения, Если работа, выходящая из начального узла сетевого проекта, еще не начата из-за отсутствия информации о начале выполнения соответствующих операций, та сигнал "Начало" из объекта через вход 8 не поступает на единичный вход триггера 1. Последний триггер 1 остается в нулевом состоянии и выдает запретчерез выход 9 на вход элемента И 28 соответствующей модели 19 ветви и разрешение на вход элемента И 5. В результате сигнал с выхода элемента ИЛИ 38 блока 20 не появляется на выходе элемента И 28 модели 19, а проходит через вход 14 и элемент И 5, на остальных входах которого присутствует разрешение с нулевого выхода 5разрешение на вход элемента И 48, и импульсы с выхода генератора 22 (топологическая серия) через входной полюс 40 и элемент И 48 проходят на входы задатчиков 44 и 45.5Кроме того, импульсы с выхода элемента И 48 проходят через элемент И 49, на втором входе которого присутствует разрешение с выхода триггера 47, на выходной полюс 42. Далее Ю через элемент ИЛИ 37 блока 20 формирования топологии они поступают на входы задатчиков 24 и 25 адресов блока 19 моделей ветвей. Эти импульсы будут поступать до тех пор, пока 15 на выходах эадатчиков адресов, в которых записан адрес начального узла сетевого графика, не появится сигнал переполнения. В этот же момент времени на выходе задатчика 44 на чального узла сетевого графика в блоке 21 (фиг.3) появляется сигнал переполнения, который проходит через элемент И 50, так как на втором входе элемента присутствует разрешение 25 с выхода триггера 46, на выходной полюс 43 и далее поступает на вход элемента ИЛИ 38 блока 20 Формирования топологии (фиг.1).Кроме того, сигнал переполнения с 30 выхода задатчика 44 (фиг.2) поступает на вход триггера 47 и устанавливает его в нулевое состояние. В результате прекращается подача импульсов на вход элемента ИЛИ 37 блока 20. 81 6триггера 1 и от соответствующей модели ветви 19 через вход 13 с нулевого вькода триггера 27 и через вход12 с выхода задатчика 24, Сигнал свыхода элемента И 5 поступает навход триггера. 2 и устанавливает егов единичное состояние, которое соответствует задержке управления о начале выполнения соответствующей работы в объекте,Для этих работ, выходящих из начального узла графа, сигнал задержкис прямого выхода триггера 2 устройства передается через выход 11 на место выполнения соответствующей работы.В случае, если работа, выходящаяиз начального узла сетевого проекта,получила информацию о выполнении соответствующей операции, то сигнал"Начало" уже передан из объекта всоответствующий блок 17 через вход 8,где он установил триггер 1 в единичное состояние. Единичное состояниетриггера 1 выдает запрет на вход эле.мента И 5 устройства и разрешение навход элемента И 28 соответствующеймодели 19 ветви. В результате появляется разрешающий сигнал на выходеэлемента И 28 модели 19, на остальных входах которой присутствует разрешение с нулевого выхода триггера27, задатчика 24 и через выход 9 сединичного выхода триггера 1 соответствующего устройства 17 для сопряжения. Сигнал с выхода элемента И 28проходит через элемент ИЛИ 31 и подготавливает Формирователь 23 временных интервалов соответствующей модели 19 ветви к отсчету импульсов измерительной серии,. поступающей из блока 20 формирования топологии. Такимобразом, в модели 16 сети будут подготовлены для моделирования длительностей те модели 1.9 ветвей, которыевыходят из начального узла сети и которые получили сигналы "Начало" черезблок 17 из объекта, где есть информация о начале выполнения соответствующих работ,После этого осуществляется моделирование длительностей моделей ветвей,имеющих включенные формирователи 23временных интервалов, а также длительности задержек для работ, выходящих из начального узла. сети и не выдавших сигналы "Начало", В этом случае все триггеры 26 моделей 19 ветвей находятся в нулевом состоянии,так как ни один формирователь 23 не510 15 20 25 30 35 40 45 50 55 7 13выработал сигнал переполнения, Элемент ИЛИ 36 блока 20, объединяющийединичны выходы триггеров 26 вырабатывает запрещающий сигнал на прохождение топологической серии генератора 22 через элемент И 33 и черезэлемент НЕ 39 - разрешающий сигнална вход элемента И 35. В результатеимпульсы измерительной серии генератора 22 проходят на входы формирователей 23 временных интервалов всехмоделей 19 ветвей, но отсчитываютизмерительную серию только формирователи, подготовленные сигналом свыхода элемента ИЛИ 31.В то же время независимо от элемента И 35 блока 20 импульсы непосредственно с генератора 22 черезвход 15 поступают на вход элементаИ 6 всех блоков 17, но отсчитываютуказанную серию в реальном временитолько те блоки 17, которые соответствуют работам, имеющим задержкув управлении, т,е. блоки 17, имеющие триггеры 2 в единичном состоянии.Счетчик 3 блока 17 отсчитывает величину реальной задержки управления дотех пор, пока на месте выполнения соответствующей работы не .будут приняты экстренные меры по устранениюимеющихся неполадок и не будет выработан сигнал "Начало" через вход 8на вход соответствующего блока 17,Последний сигнал в этом случае устанавливает триггер 1 в единичное сос. тояние, триггер 2 - в нулевое состояние, а также проходит через элементИ 7, так как на другом входе элемента присутствует разрешающий сигнал свыхода дешифратора 4 кодов, который.определяет состояние счетчика 3, отличное от нулевого,В результате на вход счетчика 3блока 17 больше не поступают импульсы измерительной серии, сигнал с выхода элемента И 7 через выход 10 иэлемент ИЛИ 31 подготавливает формирователь 23 временного интервала соответствующей модели 19 ветви к моделированию длительности выполненияработы,Формирователи 23 временных интервалов моделей 19 ветвей отсчитывают измерительную серию импульсов, соответствующую длительности данной вет ви, до тех пор, пока хотя би один из них не выработает сигнал, который установит в единичное состояние триг 00481 8 геры 26 и 27 своего блока 19 моделейветви. С единичного выхода триггера26 сигнал поступает в блок 20 формирования топологии на один из входовэлемента ИЛИ 36, к остальным входамкоторого подключены одноименные входы остальных моделей 19 ветвей, Пройдя через элемент ИЛИ 36, сигнал поступает на вход элемента НЕ 39, который вырабатывает запрет на одном извходов элемента И 35. В результатезапрещается поступление импульсов измерительной серии на входы всех бло 1ков 19 моделей ветви, хотя это не обязательно для устройства для сопряженияс сетевой моделью, так как топологи,ческая серия подается в ускоренном масштабе времени и коммутация блоков 19 моделей ветви выполнена до прихода следующего импульса измерительной серии. Сигнал с выхода элемента ИЛИ 36 также поступает на вход элемента И 33 и разрешает прохождение импульсов топологической серии с выхода генератора 22, которые проходят через элементы И 33, ИЛИ 37 и поступают на входы задатчиков 24 и 25 адресов всех блоков 19 моделей ветви. Задатчики 24 и 25 адресов начальных и конечных узлов отсчитывают импульсы до тех пор, пока задатчик 25 адресов блоков 19 моделей ветвей, где сформирован временной интервал формирователем 23, не выработает сигнал пере- - полнения. Сигнал с выхода задатчика 25 адресов, в котором записан адрес конечного узла ветви, устанавливает в нулевое состояние триггер 26, а также поступает на первый вход элемента И 29 и на вход элемента НЕ 32.Если ветвь, в которой появляется импульс на входе задатчика 23 адресов, закончила формирование временного интервала, то разрешающий сигнал с выхода триггера 27 проходит через элементы И 29 и ИЛИ 30 к одному из входов элемента И 34. В тех случаях, когда импульсы на выходе задатчика 25 адресов отсутствуют, на вход элемента И 34 разрешающий сигнал поступает с выхода элемента НЕ 32. Таким образом, запрет на входах элемента И 34 поступает только от тех моделей ветвей, которые входят в рассматриваемый узел, но не сформировали свою длительность, В этом случае запрещающий сигнал проходит на выход элемента И 34 и через9 13004элемент ИЛИ ЗЯ на полюсы всех блоков19 моделей ветви, Этот сигнал запрещает подготовку соответствующихформирователей 23 к отсчету импульсовс, генератора 22,5Если все ветви, входящие в рассматриваемый узел, сформировали временной интервал, на выходе элементаИ 34 блока 20 появляется разрешающийсигнал, который поступает через элемент ИЛИ 38 на полюсы моделей ветвей.Разрешающий сигнал в каждой модели 19ветви поступает на вход элементаИ 28 и далее через полюс 12 на входэлемента И 5 в каждом блоке 17, В 15моделях ветвей сигнал с выхода элемента ИЛИ 38 блока 20 проходит черезэлемент И 26, если есть разрешение свыхода триггера 1 (выход 9) соответствующего блока 17 и есть в данный момент времени сигнал с выхода задатчика 24 адресов, т.е. в тех моделяхветвей, которые выходят из рассматриваемого узла и получили сигнал оначале выполнения рассматриваемойработы, Как и прежде, при отсутствиисигнала "Иачало" на входе 8 в блоке17 сигнал с выхода элемента ИЛИ 36проходит через элемент И 5, устанавливает триггер 2 в единичное состояние и включает это устройство дляотсчета величины задержки управления,Импульсы с генератора 22 поступают на входы задатчиков 24 и 25 адресов до тех пор, пока хотя бы на 35одном из входов блока 20 присутствуетсигнал с выхода триггера 26 какоголибо блока 19, После того, как всетриггеры 26 установлены в нулевоесостояние выходными сигналами соответствующих задатчиков адресов, блок20 запрещает прохождение импульсовэтой серии на входы задатчиков адресов, В блоке 20 разрешается беспрепятственное поступление импульсов 45измерительной серии на входы формирователей 23 временных интервалов.Таким образом, работа устройства сопряжения и сетевой модели на каждомшаге моделирования сети и контроля 50управления в работах объекта состоитиэ двух чередующихся этапов: совместное формирование длительности ветвии величины задержки управления, атакже формирование топологии сети, 55 Устройство для моделирования сетевых графиков по авт,св, У 422002, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него, введены третий и четвертый триггеры, первый, второй и третий дополнительные элементы И, счетчик и дешифратор кодов, первый вход первого дополнительного элемента И подключен к выходу третьего элемента ИЛИ блока форми" рования топологии, второй вход первого дополнительного элемента И подключен к инверсному выходу, второго триггера блока моделей ветви, третий вход первого дополнительного элемента И подключен к выходу первого задатчика адресов блока моделей ветви, четвертый вход первого дополнительного элемента И подключен к инверсному выходу третьего триггера, прямой выход которого подключен к четвертому входу первого элемента И блока моделей ветви, вход установки в "1" третьего триггера, вход установки нуля четвертого триггера и первый вход третьего дополнительного элемента И объединены и являются входом запуска устройства прямой выход четвертого триггера и первый вход второго доМоделирование сети продолжается до тех пор, пока не будет сформирован конечный узел сетевого графика,81 10После этого все триггеры 26 блока 19 устанавливаются в нулевое состояниеПосле этого сигнал с выхода элемента ИЛИ 38 блока 20 поступает через полюс 41 в блок 21 (фиг.2) на вход элемента И 51, а так как сформирован конечный узел сетевого графика, импульс переполнения с выхода задатчика 45 проходит через элемент И 51 и устанавливает триггер 46 в нулевое состояние,Процесс моделирования на этом заканчивается, Суммарное количество импульсов измерительной серии (реальное время), поступающих на вход элемента И 35 с начала отсчета и до момента формирования конечного узла графика, равно величине длиннейшего пути сети или времени выполнения всего сетевого проекта. Счетчик 3 каждого блока 17 по окончании процесса моделирования хранит величину задержки управления соответствующей работы сетевого проекта, которая может быть использована при анализе возникших аварийных ситуаций в технологическом процессе. Формула и э о б р е т е н и я,11 13004 полнительного элемента И объединены и являются информационным выходом устройства,. выход первого дополнительного элемента И подключен к входу установки в "1" четвертого триггера, выход третьего дополнительного элемента И подключен к первому входу дополнительного элемента ИЛИ блока моделей ветвей, второй вход третьего 81 12дополнительного элемента И подключенк выходу дешифратора кодов, входкоторого подключен к выходу счетчика, счетный вход которого подключенк выходу второго элемента И, второйвход которого Подключен к первомувыходу генератора импульсов, второйвыход которого подключен к тактовомувходу блока управления.1300481 оставитель Т,Сапунехред А.Кравчук ектор А.Обручар актор Л.Веселовск Заказ 1150/4 Подписно го коми ний и о уда ам ушская а,Производственно-полиграфическое предприятие г.ужгород,ул. Проектная,ВНИИПИ по 13035, МТираж твенн обрет 35, Р ета СССРкрытийаб д, 4/5 1

СмотретьЗаявка

3852116, 05.02.1985

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ЩЕТИНИН АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 13/00, G06G 7/48

Метки: графиков, моделирования, сетевых

Опубликовано: 30.03.1987

Код ссылки

<a href="https://patents.su/8-1300481-ustrojjstvo-dlya-modelirovaniya-setevykh-grafikov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования сетевых графиков</a>

Предыдущий патент: Регулятор давления газа

Следующий патент: Многоканальное устройство для идентификации моделей

Случайный патент: Вычислительное устройство