Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1280385

Авторы: Золотовский, Коробков

Текст

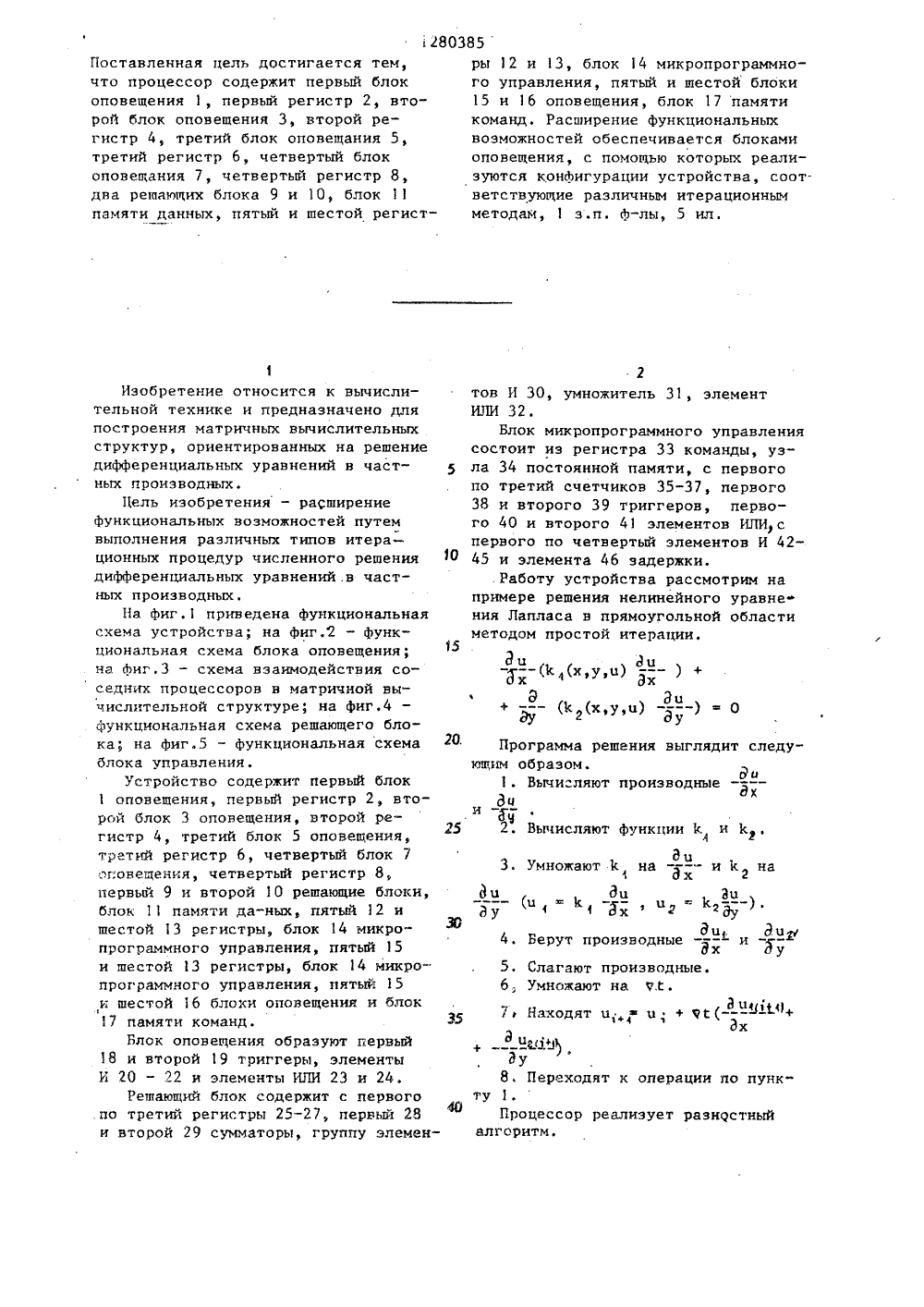

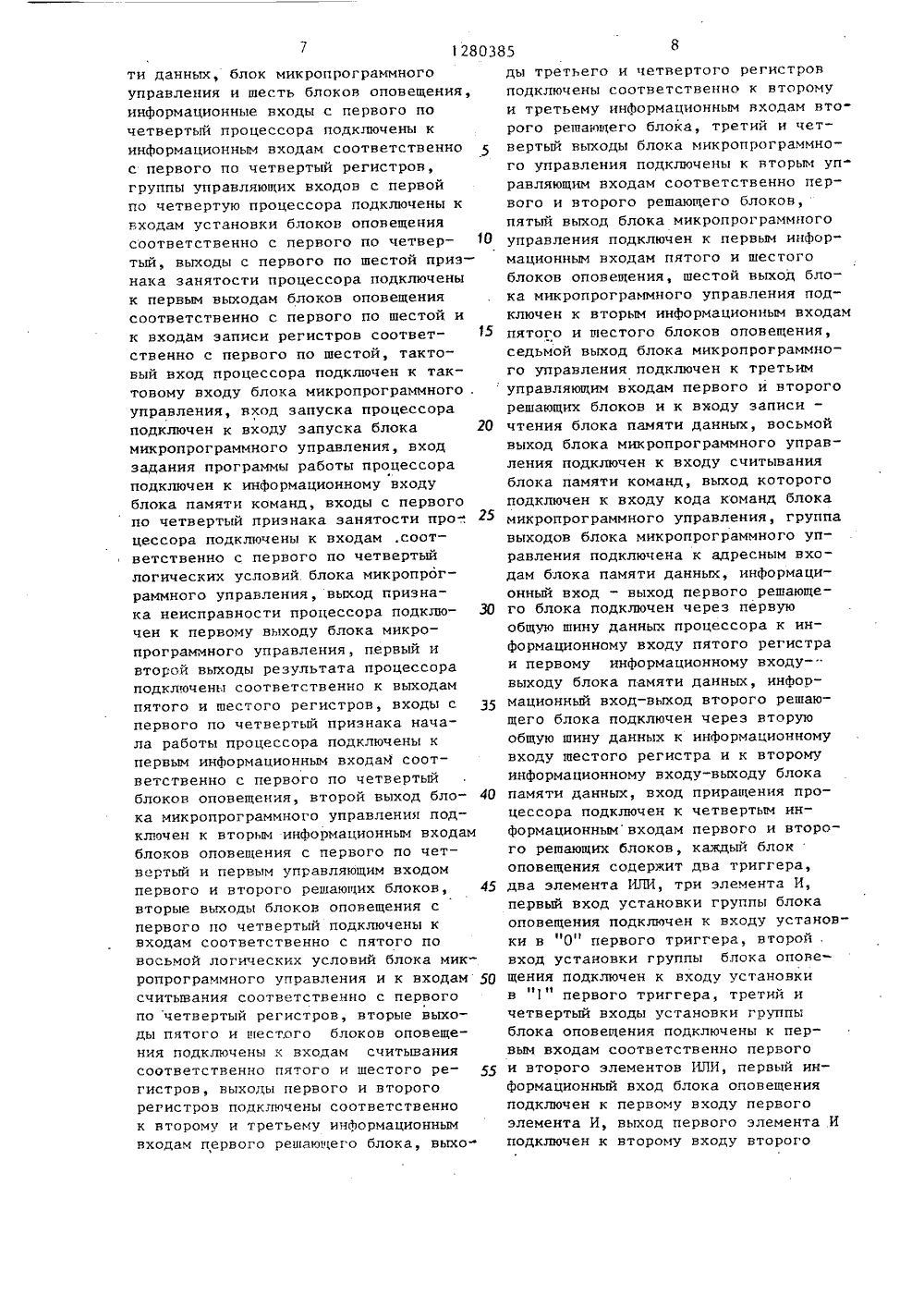

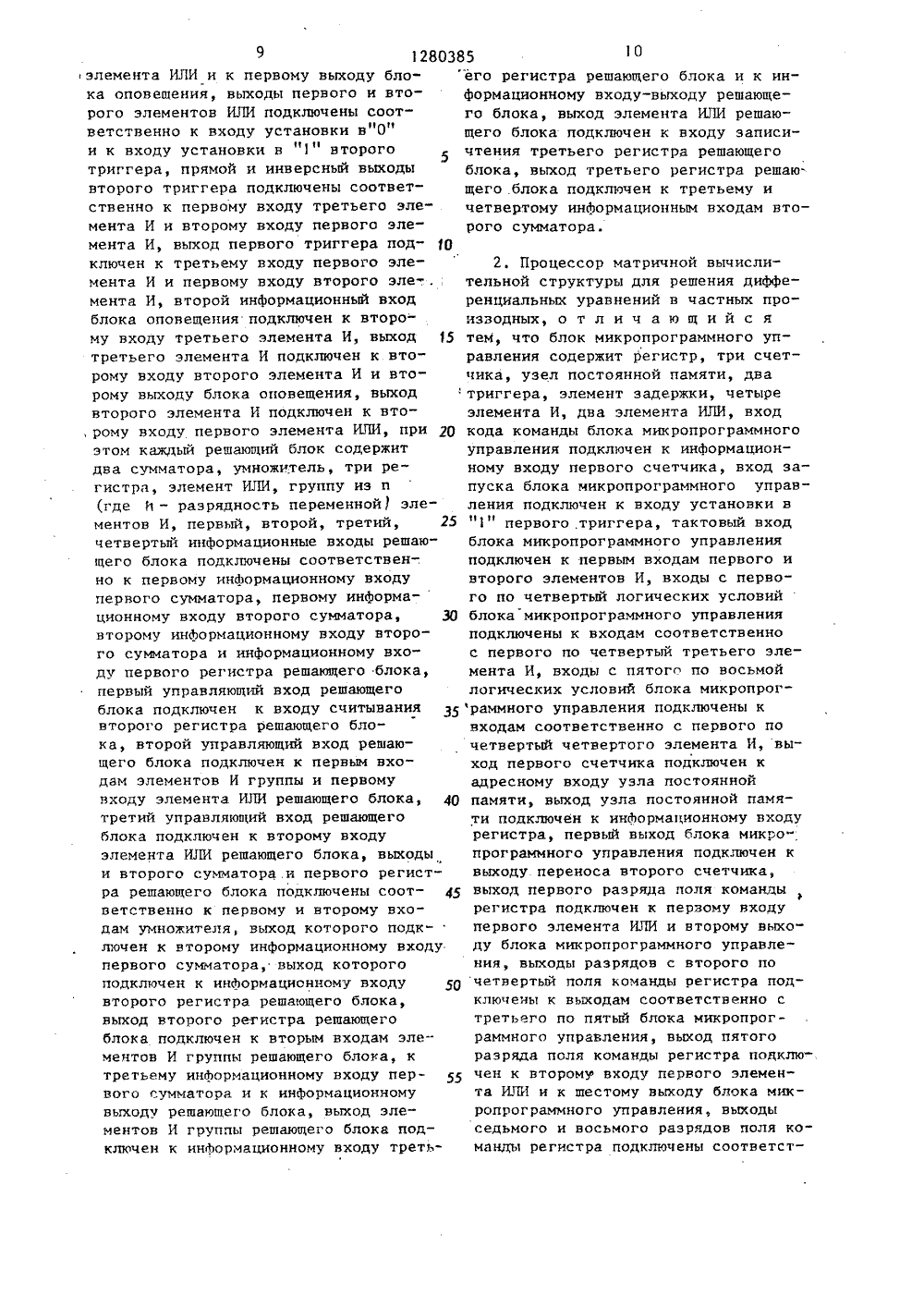

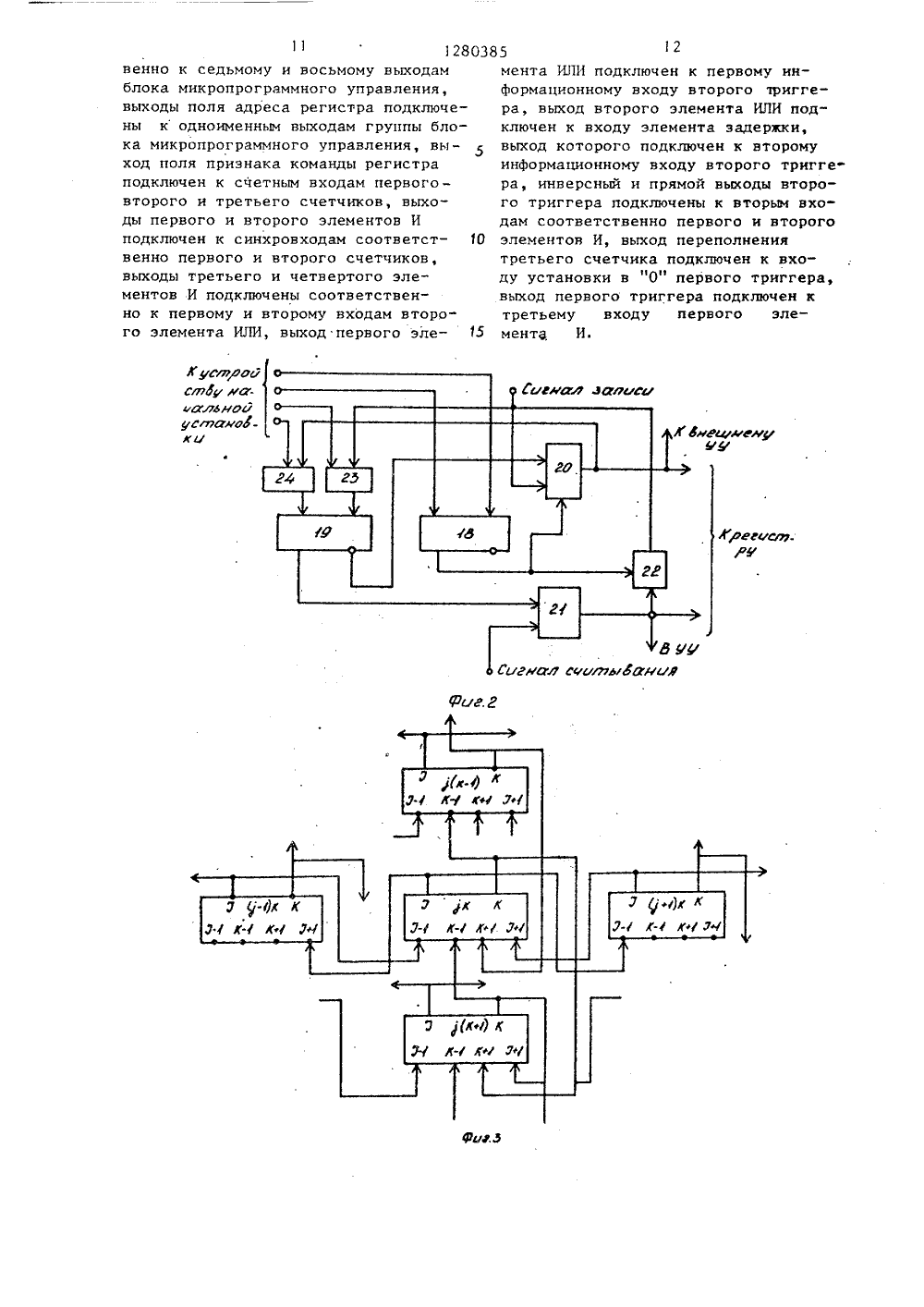

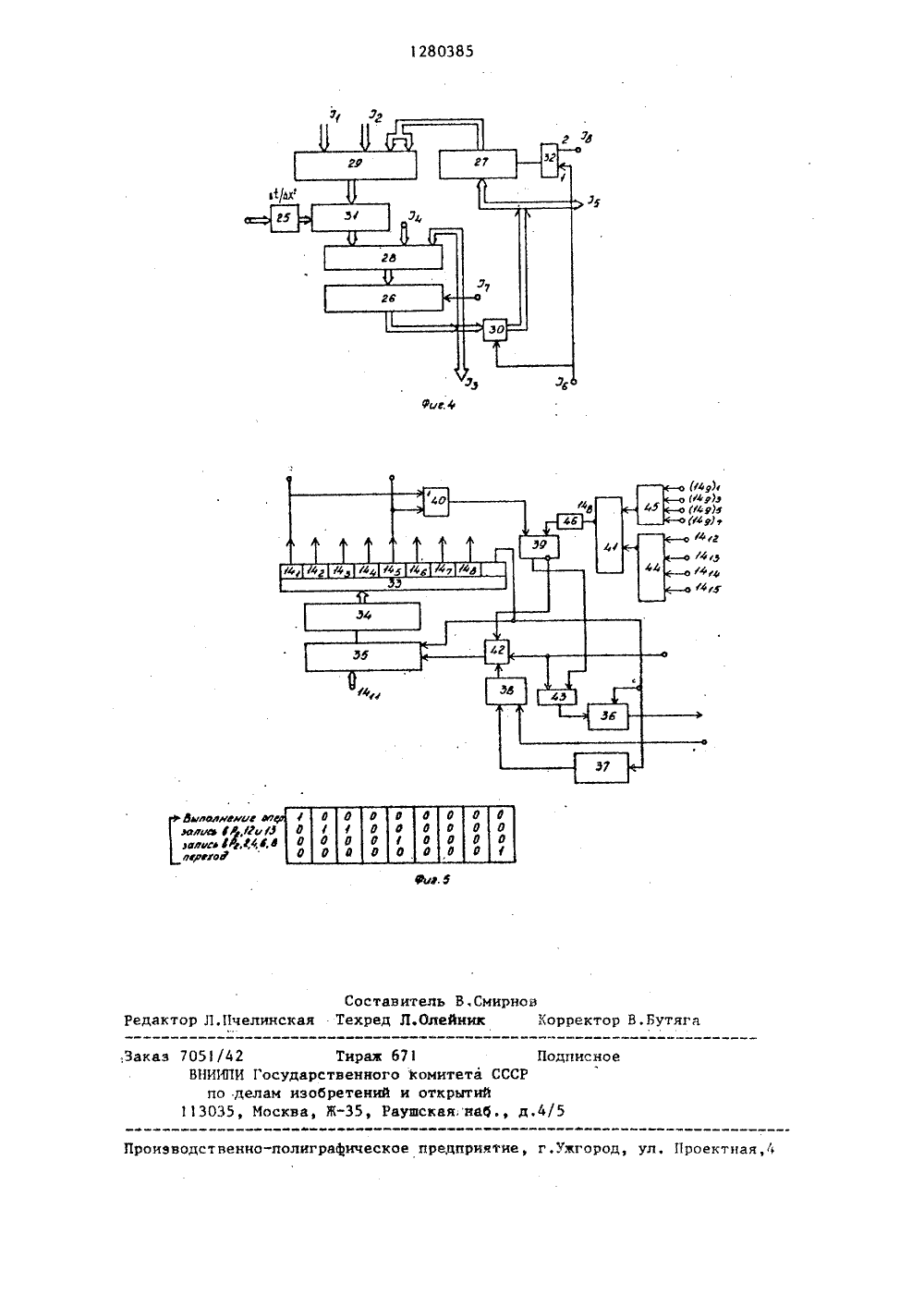

, ЯО. 128151) 4 С 06 Г 15/32Фе ПИСАНИЕ ИЗОБРЕТЕН 1 ЫХ исьийтевоз л ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Патент С 1)А Ф 3633002, кл. С 06 Р 15/32, 970.Авторское свидетельство СССР В 574733, кл. С 06 Л 1/02, 1977. (54) ПРОЦЕССОР МАТРИЧНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТ 1 ПРОИЗВОДНЫХ(57) Изобретение относится к выч лительной технике и предназначе для построения матричных вычисл ных структур, предназначенных д решения дифференциальных уравне частных производных. Цель изобр ния - расширение функциональных можностей за счет выполнения ра ного типа итерационных процедур ленного решения дифференциальны уравнений в частных производных12803Поставленная цель достигается тем, что процессор содержит первый блок оповещения 1, первый регистр 2, второй блок оповещения 3, второй регистр 4, третий блок оповещания 5, третий регистр 6, четвертый блок оповещания 7, четвертый регистр 8, два решающих блока 9 и 10, блок 11 памяти данных, пятый и шестой регист 85ры 12 и 13, блок 14 микропрограммного управления, пятый и шестой блоки 15 и 16 оповещения, блок 17 памяти команд. Расширение функциональных возможностей обеспечивается блокамиоповещения, с помощью которых реализуются конфигурации устройства, соответствующие различным итерационным методам, 1 з.п, Ф-лы, 5 ил.1Изобретение относится к вычислительной технике и предназначено для построения матричных вычислительных структур, ориентированных на решение дифференциальных уравнений в частных производных.Цель изобретения - расширение функциональных возможностей путем выполнения различных типов итерационных процедур численного решения дифференциальных уравнений .в частных производных.На фиг,1 приведена функциональная схема устройства; на фиг.2 - Функциональная схема блока оповещения; на Фиг.3 - схема взаимодействия соседних процессоров в матричной вычислительной структуре; на фиг.4 Функциональная схема решающего блока; на Фиг.5 - Функциональная схема блока управления.Устройство содержит первый блок 1 оповещения, первый регистр 2, второй блок 3 оповещения, второй регистр 4, третий блок 5 оповещения, третий регистр 6, четвертый блок 7 оповещения, четвертый регистр 8, первый 9 и второй 10 решающие блоки, блок 11 памяти да-ных, пятый 12 и шестой 13 регистры, блок 14 микропрограммного управления, пятый 15 и шестой 13 регистры, блок 14 микропрограммного управления, пятый 15 к шестой 16 блохи оповещения и блок17 памяти команд.Блок оповещения образуют первый 18 и второй 19 триггеры, элементы И 20 - 22 и элементы ИЛИ 23 и 24.Решающий блок содержит с первого по третий регистры 25-27, первый 28 и второй 29 сую 4 аторы, группу элеменгтов И 30, умножитель 31, элементИЛИ 32.Блок микропрограммного управлениясостоит из регистра 33 команды, узла 34 постоянной памяти, с первогопо третий счетчиков 35-37, первого38 и второго 39 триггеров, первого 40 и второго 41 элементов ИЛИ спервого по четвертый элементов И 42- 10 45 и элемента 46 задержки..Работу устройства рассмотрим напримере решения нелинейного уравнения Лапласа в прямоугольной областиметодом простой итерации.15оц Зц+(1 (х,у,ц) - ) Ол) 2 9 э Д Программа решения выглядит следующим образом.1. Вычисляют производные --ВцдхЧи -р5 2. Вычисляют функции М. и 1 с 2дц3. Умножают К на -- и 1 г надх 23 ц дц ац+ лдхду8. Переходят к операции по пункту 1.Процессор реализует разностныйалгоритм.3 1280385 4Производная аппроксимируется цент- попытке записи процессор, пытающий- ральной разностной производной ся произвести запись, приостанавливается до момента, пока такая запись станет возможной. Последние два сосд ц к ц 1 юл+дк- цм-л 1 кЮдх 2 чх О ц 11 д+1 к - цй-кдх 2 дх 3 ц ццк- ц кду 2 чу соответственно в решающих блоках 9и 10, После выполнения операции решающий блок 9 выдает результат в первую шину, а решающий блок 10 - вовторую шину данных и происходит за-.пись результата в блок 11 памяти данСчитывается следующая команда из блока памяти команд и начинает выполняться второй шаг - вычисление функций 1,и 1 .ИнАормация, необходимая для вычисления функций Е и Е поступает в решающие блоки 9 и 10 по шинам данных из блока 11 памяти,По окончании выполнения опЕраций происходит переход на следующую команду. При этом инАормация, хранимая в решающих блоках 9 и 10, умножается на величины, считываемые из блока 1 памяти. Таким образом в первом решающем блоке 9 Аормируется значение переменной ц, а во втором решающем блоке 1 О - значение переменной ц . После окончания операции значения ц, и ц ъ поступают в регистне происходит, процессор приостанавливает вьполнение программы при обращении к этому регистру и ждет поступления информации из соседнего процессора.Состояние означает, что запись производилась на предыдущих шагах, счиФыванин не происходило. При Величины с индексами, отличными от индекса 31, вычисляются в соседних процессорах.Передача информации происходит 1 О следующим образом.Данные, помещаемые в регистры 12 и 13, записываются в них в зависимости от состояния блоков оповещения. 15Триггер 19 (первый бит) есть собственно указатель блока оповещения,а триггер 8 (второй бит) - бит управления указателем блока оповещения. Если бит управления указателемнаходится в , то он разрешаетизменение указателя блока оповещенияв противном случае изменение запрещено. Установка триггера 19 (указателя) в "1" означает, что новая информация поступила, считывание разрешается, запись запрещается. Если указатель блока оповещения равен "0",информация не изменялась, записьразрешена, считывание запрещено. Наличие блоков оповещения позволяетэффективно организовать вычислительный процесс, Состояние 00" означаетчто ни считывание, ни запись невозможны, При обращении к регистру стаким указателем блок управления неполучает ответного сигнала и останавливается. Процессор отключается, Присостоянии "10" разрешается считывание, запись запрещена, указатель не 40изменяет своего состояния при считывании. Эта ситуация используется длязаписи граничного условия в соответ -ствующий регистр. В этом. случае зна-.чение регистра не изменяется за все 4время решения, что и необходимо дляграничного значения.Состояние "01" означает, что считывание инАормации произошло раньше, а новая информация не поступила. 50Так как в этом состоянии считывания тояния осуществляют синхронизацию работы двух процессоров в условиях ограниченного объема буферной памяти.При построении матричной структуры процессор с номером 1 К передает информацию из регистра 12 в регистр 2 процессора с номером (1-1)1 и в регистр 4 процессора (1+1)1, а иэ регистра 13 в регистр б процессора с номером 1 (К) и в регистр 8 процессора с номером 1 (1-1) и в ре- . гистр 8 процессора с номером 1(1+1).Предположим, что к первому шагу вся информация готова либо из начальных условий, либо вычислена. Тогда по сигналам с блока 14 управления информация из регистров 2 и 4 переносится в решающий блок 9, а из регистров б и 8 - в решающий блок 10 с установкой блоков оповещения в соответствующее состояние. Далее происходит запуск операции взятия производных1280385 матора 28 ирегистра 26Выполнение алгоритма обеспечивается следующей последовательностьюработы блока микропрограммного управления.1-й такт - считывание информациииз регистров 2,4 6 и 8. Сигнал появляется на выходе блока 4. Этот10 сигнал поступает на укаэанные регистры и одновременно устанавливаеттриггер 39 в единичное состояние.Открывается элемент И 43, и счетчик36 подсчитывает число пришедших15 синхроимпульсов. Одновременно навход элемента И 5 поступают сигналыс вьмодов блоков 1,3,5 и 7 оповещения. Если считывание разрешено, тона выходе элемента И 45 появляется сигнал, Который, проходя черезэлемент ИЛИ 41 и элемент 46 задержки, сбрасывает триггер 39 в нулевоесостояние. Наращивается счетчик 35 и .происходит переход на следующий такт,2-й такт - запись в регистры 12и 13.3-й такт - запись в регистры 2;4,6, и 8. Схема анализа возможности30записи работает аналогично анализупри считывании, причем проводитсяопрос не собственных регистров, арегистров соседних процессоров.4-й такт - сброс блока микропрограммного управления и переход на1ой цикл,Счетчик 7 итераций используетсядля организации останова решения. 40 Решающий элемент реализует сле дующий алгоритм:+л 0 -Лцц - 2 ц + ц (вычисление второй разностина сумматоре29); 50ЬС71 ц = ( Ч ц) х -- (определениеприращения наумножителе 31);ц = ц + ч 1 ц +Чтец (определение ночвого значения 55искомой переменной на накопнтеле,состоящем из сум-,ы 12 и 13 соответственно. После записи ц, и ц в указанные регистры ин" формации из них в зависимости от состояния блоков оповещения соответствующих процессоров переводится в состояние ожидания разрещения обмена. Так как все процессоры идентичны, то при простой итерации все они срабатывают одновременно и ожидание обмена отсутствует. После обмена устройство управления переходит на выполнение четвертого шага.В этом шаге считывается информация из регистров 2,4,6 и 8 и в решающем блоке 9 выполняется операция взятия производной - а в решаюдцдк фщем блоке 1 О формируется произволОлная в в , Затем полученные проиэдцводные взаимно пересылаются и в обоих решающих блоках происходит суммирование, В шестом шаге решающих бло" ков 9 и 1 О происходит умножение наВ седьмом шаге из блока 11 памяти данных считывается переменная ц, которая складывается с содержимым решающих блоков 9 и 10. Сформированная переменная ц в решающем блоке 9 поступает в регистр 12, эта же переменная, сформированная в решающем блоке 1 О, поступает в регистр 13, т,е. в двух разных решающих блоках формируется одна и та же переменная с целью устранения дополнительной пересылки иэ регистра с регистр и обеспечения возможности дополнительной проверки на работоспособность каждого решающего блока. После обмена информацией между процессорами описанные операции повторяются до тех пор, пока процесс не сойдется во всех процессорах. Проверка организуется программно. Формула изобретения 11. Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частньм производных, содержащий первый и второй решающие блоки первый регистр, информационный вьход первого решающего блока подключен к первому информационному входу второго решающего блока, информационный выход которого подключен к первому информационному входу первого решающего блока, с т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей за счет выполнения различных типов итерационньмпроцедур численного решения дифференциальных уравнений з частных производных, в него введены пять регистров, блок памяти команд, блок памя 1 280385ти данных, блок микропрограммногоуправления и шесть блоков оповещения,информационные входы с первого почетвертый процессора подключены кинформационным входам соответственнос первого по четвертый регистров,группы управляющих входов с первойпо четвертую процессора подключены кгходам установки блоков оповещениясоответственно с первого по четвертый, выходы с первого по шестой признака занятости процессора подключенык первым выходам блоков оповещениясоответственно с первого по шестой ик входам записи регистров соответственно с первого по шестой, тактовый вход процессора подключен к тактовому входу блока микропрограммного .управления, вход запуска процессораподключен к входу запуска блока 20микропрограммного управления, входзадания программы работы процессораподключен к информационному входублока памяти команд, входы с первогопо четвертый признака занятости процессора подключены к входам ,соответственно с первого по четвертыйлогических условий блока микропрограммного управления, выход признака неисправности процессора подключен к первому выходу блока микропрограммного управления, первый ивторой выходы результата процессораподключены соответственно к выходампятого и шестого регистров, входы с 35первого по четвертый признака начала работы процессора подключены кпервым информационным входаМ соответственно с первого по четвертыйблоков оповещения, второй выход блока микропрограммного управления подключен к вторым информационным входамблоков оповещения с первого по четвертый и первым управляющим входомпервого и второго решающих блоков, 45вторые выходы блоков оповещения спервого по четвертый подключены квходам соответственно с пятого повосьмой логических условий блока микропрограммного управления и к входам 50считывания соответственно с первогопо четвертый регистров, вторые выходы пятого и шестого блоков оповещения подключены к входам считываниясоответственно пятого и шестого регистров, выходы первого и второгорегистров подключены соответственнок второму и третьему информационнымвходам первого решающего блока, выходы третьего и четвертого регистровподключены соответственно к второмуи третьему информационным входам второго решающего блока, третий и четвертый выходы блока микропрограммного управления подключены к вторым управляющим входам соответственно первого и второго решающего блоков,пятый выход блока микропрограммногоуправления подключен к первым информационным входам пятого и шестогоблоков оповещения, шестой выход блока микропрограммного управления подключен к вторым информационным входампятого и шестого блоков оповещения,седьмой выход блока микропрограммного управления подключен к третьимуправляющим входам первого и второгорешающих блоков и к входу записи -чтения блока памяти данных, восьмойвыход блока микропрограммного управления подключен к входу считыванияблока памяти команд, выход которогоподключен к входу кода команд блокамикропрограммного управления, группавыходов блока микропрограммного управления подключена к адресным входам блока памяти данных, информационный вход - выход первого решающего блока подключен через первуюобщую шину данных процессора к информационному входу пятого регистраи первому информационному входу выходу блока памяти данных, информационный вход-выход второго решающего блока подключен через вторуюобщую шину данных к информационномувходу шестого регистра и к второмуинформационному входу-выходу блокапамяти данных, вход приращения процессора подключен к четвертым информационнымвходам первого и второго решающих блоков, каждый блокоповещения содержит два триггера,два элемента ИЛИ, три элемента И,первый вход установки группы блокаоповещения подключен к входу установки в "0" первого триггера, второй,вход установки группы блока оповещения подключен к входу установкив первого триггера, третий ичетвертый входы установки группыблока оповещения подключены к первым входам соответственно первогои второго элементов ИЛИ, первый информационный вход блока оповещенияподключен к первому входу первогоэлемента И, выход первого элемента Иподключен к второму входу второгоэлемента ИЛИ и к первому выходу блока оповещения, выходы первого и второго элементов ИЛИ подключены соответственно к входу установки в"0" и к входу установки в "1" второго5 триггера, прямой и инверсный выходы второго триггера подключены соответственно к первому входу третьего элемента И и второму входу первого элемента И, выход первого триггера под р ключен к третьему входу первого элемента И и первому входу второго эле- мента И, второй информационный вход блока оповещения подключен к второму входу третьего элемента И, выход 15 третьего элемента И подключен к второму входу второго элемента И и второму выходу блока оповещения, выход второго элемента И подключен к вто, рому входу первого элемента ИЛИ, при 20 этом каждый решающий блок содержит два сумматора, умножитель, три регистра, элемент ИЛИ, группу из и (где И - разрядность переменнойэлементов И, первый, второй, третий, 25 четвертый информационные входы решающего блока подключены соответствен-, но к первому информационному входу первого сумматора, первому информационному входу второго сумматора, 30 второму информационному входу второго сумматора и информационному входу первого регистра решающего блока, первый управляющий вход решающего блока подключен к входу считываниявторого регистра решающего блока, второй управляющий вход решающего блока подключен к первым входам элементов И группы и первомувходу элемента ИЛИ решающего блока, 4 Отретий управляющий вход решающегоблока подключен к второму входуэлемента ИЛИ решающего блока, выходыи второго суьиатора.и первого регистра решающего блока подключены соответственно к первому и второму входам умножителя, выход которого подключен к второму информационному входупервого сумматора, выход которогоподключен к информационному входувторого регистра решающего блока,выход второго регистра решающегоблока подключен к вторым входам элементов И группы решающего блока, ктретьему информационному входу первага сумматора и к информационномувыходу решающего блока, выход элементов И группы решающего блока подключен к информационному входу третьего регистра решающего блока и к информационному входу-выходу решающего блока, выход элемента ИЛИ решающего блока подключен к входу записичтения третьего регистра решающегоблока, выход третьего регистра решающего .блока подключен к третьему ичетвертому информационным входам второго сумматора. 2. Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных, о т л и ч а ю щ и й с я тем, что блок микропрограммного управления содержит регистр, три счетчика, узел постоянной памяти, два триггера, элемент задержки, четыре элемента И, два элемента ИЛИ, вход кода команды блока микропрограммного управления подключен к информационному входу первого счетчика, вход запуска блока микропрограммного управления подключен к входу установки в "1" первого, триггера, тактовый вход блока микропрограммного управления подключен к первым входам первого и второго элементов И, входы с первого по четвертый логических условий блока микропрограммного управления подключены к входам соответственно с первого по четвертый третьего элемента И, входы с пятогп по восьмой логических условий блока микропрограммного управления подключены к входам соответственно с первого по четвертый четвертого элемента И, выход первого счетчика подключен к адресному входу узла постоянной памяти, выход узла постоянной памяти подключен к информационному входу регистра, первый выход блока микро" программного управления подключен к выходу переноса второго счетчика, выход первого разряда поля команды регистра подключен к первому входу первого элемента ИЛИ и второму выходу блока микропрограммного управления, выходы разрядов с второго по четвертый поля команды регистра подключены к выходам соответственно с третьего по пятый блока микропрограммного управления, выход пятого разряда поля команды регистра подключен к второму входу первого элемента ИЛИ и к шестому выходу блока микропрограммного управления, выходы седьмого и восьмого разрядов поля команды регистра подключены соответственно к седьмому и восьмому выходам блока микропрограммного управления, выходы поля адреса регистра подключены к одноименным выходам группы блока микропрограммного управления, выход поля признака команды регистра подключен к счетным входам первого -второго и третьего счетчиков, выходы первого и второго элементов Иподключен к синхровходам соответственно первого и второго счетчиков,выходы третьего и четвертого элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход первого элеОЗ 85 2мента ИЛИ подключен к первому информационному входу второго триггера, выход второго элемента ИЛИ подключен к входу элемента задержки,выход которого подключен к второмуинформационному входу второго триггера, инверсный и прямой выходы второго триггера подключены к вторым входам соответственно первого и второго 10 элементов И, выход переполнениятретьего счетчика подключен к входу установки в "О" первого триггера,выход первого триггера подключен ктретьему входу первого эле мента И..,Зак ПодписноР ударстизобр 4 ва,роиэводстненно-полиграфическое предприятие л, Проектная,4 гор Вмадюмис юмюиь Щ/Лг О ювао Щ,84 С Ь сссссаУ 7051/42 ВНИИПИ Г по дел 113035, М

СмотретьЗаявка

3879724, 08.04.1985

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 17/13

Метки: вычислительной, дифференциальных, матричной, производных, процессор, решения, структуры, уравнений, частных

Опубликовано: 30.12.1986

Код ссылки

<a href="https://patents.su/8-1280385-processor-matrichnojj-vychislitelnojj-struktury-dlya-resheniya-differencialnykh-uravnenijj-v-chastnykh-proizvodnykh.html" target="_blank" rel="follow" title="База патентов СССР">Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных</a>

Предыдущий патент: Устройство для исследования графов

Следующий патент: Цифровой коррелятор

Случайный патент: Способ диагностики криовакуумных устройств