Генератор псевдослучайных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

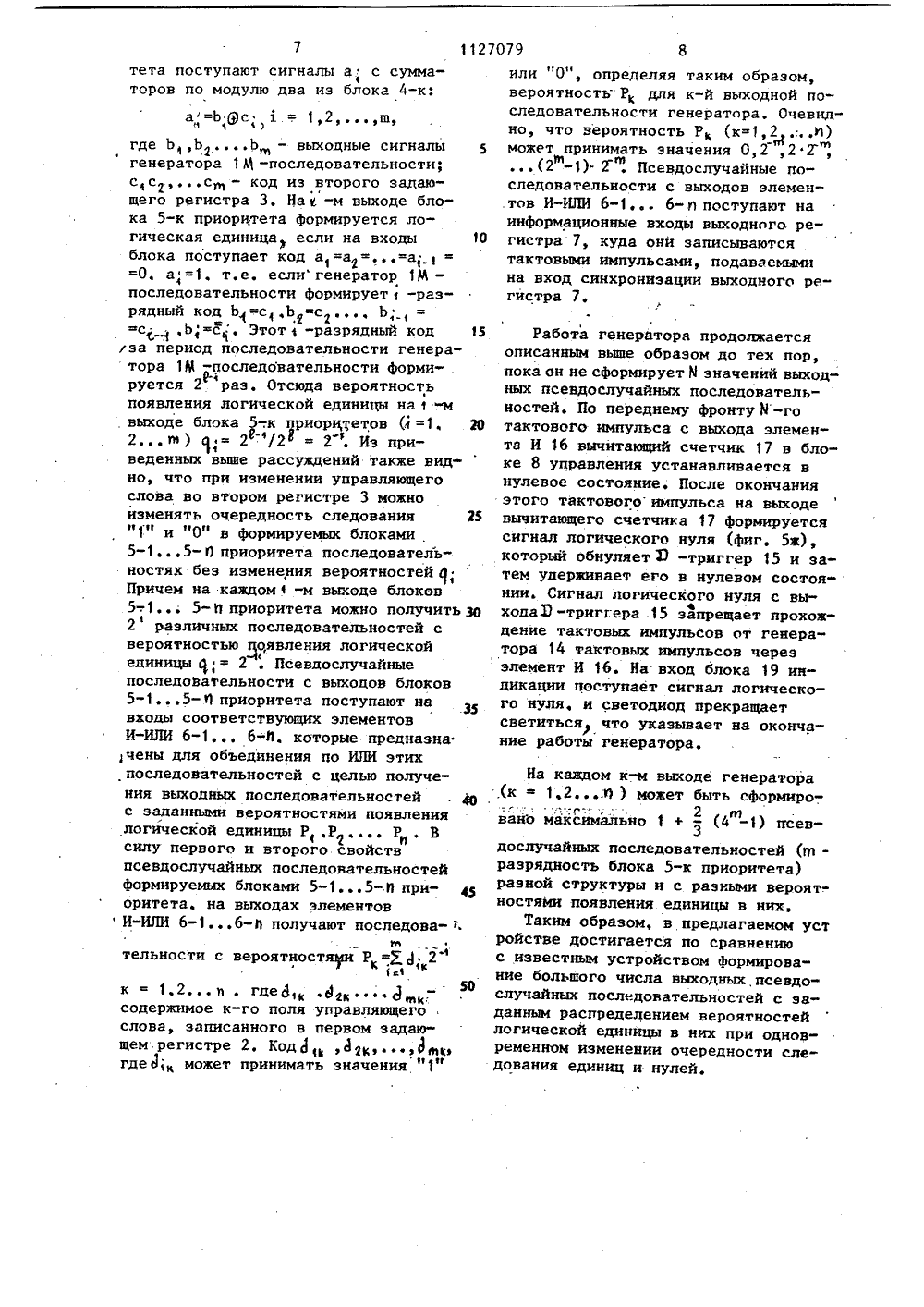

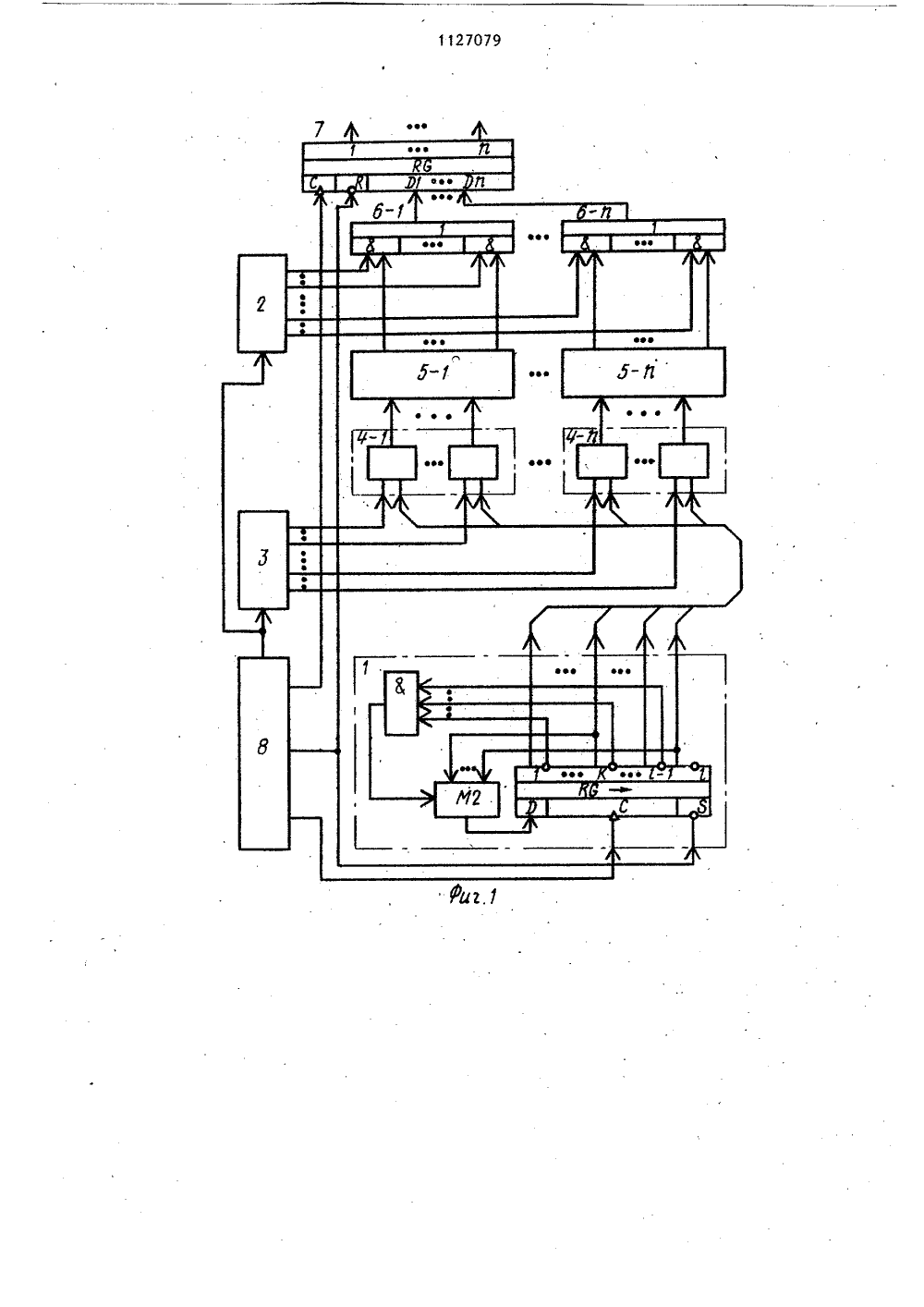

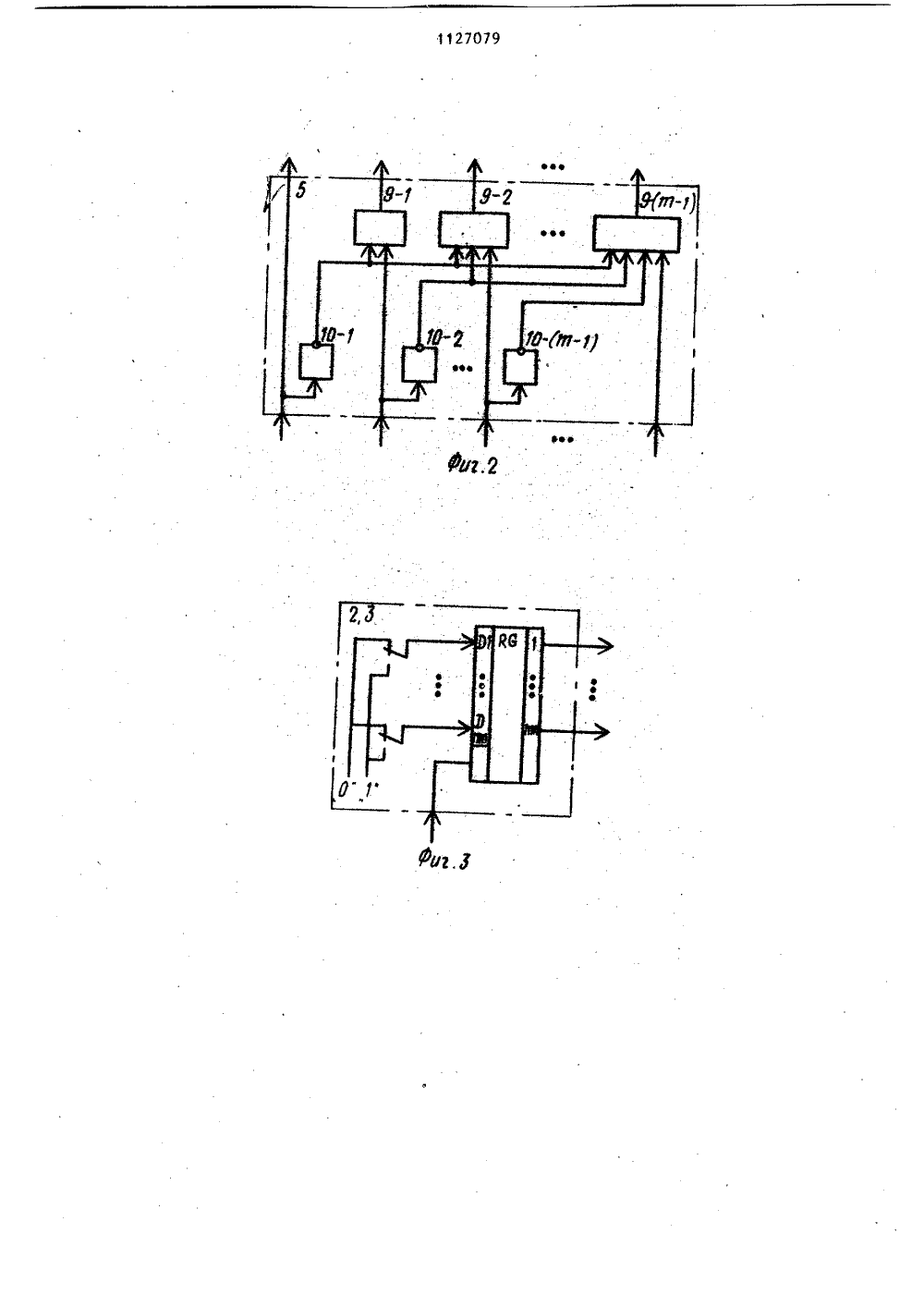

А СООЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ОЮ (И) за) Н 03 К 3/84 ПИСАНИЕ ИЗОБРЕТ ТВУ РСНОМУ СВИДЕ по п. 1, отем, что блтаэлемеЕ, причем вых 2. Генераточ ающий соритета содержиа) элементов(1=1 а -1)нен со входомИ 5 л 1 М 1) т л иок притов И,од 1 -гооедилемента лемента НЕ аждого-го ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(56) 1. Авторское свидетельство СССР У 767743, кл. С 06 Р 1/02, 1980.2. Авторское свидетельство СССР У 744525, кл. С 06 Р 1/02, 1980. (54)(57) 1. ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащий генератор М-последовательности, первый задающий регистр,о т л и ч аю ш и й с я тем, что, с целью расширения функциональных возможностей геяератора путем увеличения числа псевдослучайных последовательностей с заданным распределением вероятностей логической единицы в них, в него введены второй задающий регистр, И блоков сумматоров по модулю два, и блоков приоритета, й эле- . ментов И-ИЛИ, выходной регистр, блок управления, первый, второй и третий выходы которого соединены соответственно с входом синзронизации выходного регистра, входами установки выходного регистра и генератораф -последовательности, вхо-дом синхронизации генератораМ -последовательности, выходы которогосоединены с первыми входами ф блоков сумматоров по модулю два, выходы которых соединены с входамисоответствующих и блоков приоритета,выходы которых соединены с первьяивходами соответствующих й элементовИ-ИЛИ, выходы которых соединены синформационными входами выходногорегистра, выходы первого задающегорегистра соединены с вторыми входами и элементов И-ИЛИ, выходы второго задающего регистра соединены свторыми входами й блоков сумматоровпо модулю два, четвертый выход бло-,ка управления соединен с входамисинхронизации первого и второго задающих регистров.Изобретение относится к импуль, сной технике,Известен генератор псевдослучайных кодов, содержащий выходной регистр, регистр маски, блок памяти,преобразующий регистр, регистр сдвига с обратной связью и блок синхронизации, позволяющий формироватьпсевдослучайные сигналы с перестраиваемой вероятностью появления логического "0" ("1") на каждом еговыходе путем накопления в преобразующем регистре дизъюнкций логических произведений опорных циклических последовательностей блока памяти и псевдосучайных последовательностей регистра сдвига с обратнойсвязью Я .Недостатками этого генератораявляются низкое быстродействие, вызванное тем, что каждый элемент формируемой последовательности получается за несколько последовательныхциклов обращения к блоку памяти, атакже ограниченный диапазон вероятностей логического нО" ("1 н) в выходных последовательностях генератора. В данном генераторе возможно получение вероятностей появления логического "0" в формируемых последовательностях, равных 0,5 " или (1- 0,5 ), где к - число единиц в соответствующих опорных циклических последовательностях,Наиболее близким по техническомурешению к предлагаемому является генератор псевдослучайных двоичных последовательностей, содержащий ге нератор И -последовательности, задающий регистр, группу мультиплексоров, адресные входы которых соединены с выходами генератораМ -последовательности соответственно, а канальные входы группы мультиплексоров соединены с выходами задающего регистра соответственно 21.Однако такой генератор на каждом своем выходе может формировать псевдослучайную последовательность с заданным значением вероятности появления логической единицы (нуля) и не позволяет варьировать положением единицы (нуля) в формируемых последовательностях, т.е, изменять структуру выходных последовательностей. 1127079Целью изобретения является расширение функциональных возможностейгенератора путем увеличения числапсевдослучайных последовательностей 5 с заданным распределением вероятностей логической единицы в них.Поставленная цель достигаетсятем, что в генератор псевдослучайных последовательностей, содержащийгенераторФ -последовательности,1 первый задающий регистр, введенывторой задающий регистр, и блоковсумматоров по модулю два, и блоков приоритета, й элементов И-ИЛИ, 15 выходной регистр, блок управления,первый, второй и третий выходы которого соединены соответственно свходом синхронизапии выходного регистра, входами установки выходно го регистра и генератора М -последовательности, входом синхронизациигенератора М -последовательности,выходы которого соединены с первымивходами Н блоков сумматоров по модулю два, выходы которых соединены свходами соответствующих й блоковприоритета выходы которых соедиУиены с нервьпки входами соответствующих и элементов И-ИЛИ, выходы кото рых соединены с информационнымивходами выходного регистра, выходыпервого задающего регистра соединеныс вторыми входами и элементов И-ИЛИ,выходы второго задающего регистра З 5соединены с вторыми входами и блоков сумматоров по модулю два, четвертый выход блока управления соединен с входами синхронизации первого и второго задающих регистров, 40 Блок приоритета содержитП 1 -1элементов И, й 1-1 элементов НЕ, причем выход -го 6 =1 и -1) элемента НЕ соединен с входом каждого1-го элемента И Ф =1,М 1)45 На фиг. 1 приведена функциональная схема генератора псевдослучайных последовательностей; на фиг.2 -функциональная схема блока приоритета; на фиг. 3 - пример выполненияпервого и второго задающих регистров;на фиг, 4 - пример выполнения блока управления; на фиг. 5 - временныедиаграммы работы блока управления.Генератор псевдослучайных последовательностей (фиг. 1) содержит генератор 1 М -последовательности, первый 2 и второй 3 задающие регистры, И блоков 4-14- и сумматоров по11273модулю два,11 блоков 5-15- О приоритета, О элементов И-ИЛИ 6-16-И, выходной регистр 7, блок 8 управления, первый, второй и третий выходы которого соединены соответственно с 5 входом синхронизации выходного регистра 7, входами установки выходного регистра 7 и генератора 1 М -последовательности, входом синхронизации генератора 1 М -последовательнос ти, выходы которого соединены с первыми входами л блоков 4-14-п сумматоров по модулю два, выходы которых соединены с входами соответствующих блоков 5-1,5-априори-5 тета, выходы которых соединены с первыми входами соответствующих элементов И-ИЛИ 6-1 6-Н, выходы которых соединены с информационными входами выходного регистра 7, вы ходы первого задающегорегистра 2 соединены с вторыми входами п элементов И-ИЛИ 6-1 6-п, выходы второго задающего регистра 3 соединены с вторыми входами И блоков 25 4-1 4- 11 сумматоров по модулю два, четвертый выход блока 8 управления соединен с входами синхронизаций первого 2 и второго 3 задающих регистров. 30Блок 5; приоритета (фиг. 2) солержит %-1 элементов И 9-1 (м) . (л 1-1) элементов не 10-110- Ж). причем выхол 1-го (1=1 в) элемента НЕ соединен со входом каждого)( -го элемента И (1=,1).Задающие регистры 2 и 3 реализованы одинаково (фиг. 3)Каждый из , них содержит регистр и я п 1 переключателей с помощью которых на информационные входы регистра может быть подана логическая единица(ноль).Блок 8 управления (фиг, 4) содержит 88 -триггер 11, переключатель 45 12, элемент НЕ 13, генератор 14 тактовых импульсов,2 -триггер 15, элемент И 16, вычитаюший счетчик 17, переключатели 18-1 18-5, блок 19 индикации.50Генератор псевдослучайных последовательностей работает следующим образом.В исходном состоянии переключатель 12 блока 8 управления находится 55 в положении "Стоп" (см. фиг. 4). На выходе Я триггера 11 присутствует сигнал логического нуля (фиг. 5 а),079 4на выходе Я - логической единицй (фиг. 5 б), Сигнал с выхода Я триггера 11 поступает на входы синхронизации задающих регистров 2 и 3 и записывает в них управляющие слова, выбранные на переключателях. Управляющее слово первого задающего ре- гистра 2 задает вероятности появления логической единицы в каждой из и выходных псевдослучайных последовательностей, Управляющее. слово регистра 2 имеетд полей по гп разрядов в каждом, причем разряды из 1 -го поля (1=1,и) подключены к входам элемента 6-к и задают вероятность появления логической единицы в к-ой выходной последовательности генератора.Управляющее слово второго задающего регистра 3 содержит коды, определяющие структуру выходных последовательностей генератора. Айалогич. но управляющему слову регистра 2 управляющее слово регистра 3 имеет и полей по щ разрядов в каждом. Разряды регистра 3 из к-го поля (к= =1 П) подключены к входам сумматорсв по модулю два из группы 4-к и задают очередность следования "1" и "0", в к-й ьыходной последовательности генератора. Сигнал логического нуля с инверсного выхода 05 - триггера 11 в блоке 8 управления производит запись в вычитающий счетчик 17 с переключателей 18-1, 18- 2 18-8 двоичного кода длиныф формируемых генератором последовательностей. Сигнал логического нуля с инверсного выхода Ю -триггера 11 подается также на 3 -входО -триггера 15, который по положительному фронту тактового импульса генератора 14 тактовых импульсов (фиг.5 в) устанавливается в нулевое состояние (фиг.5 г)При этом сигнал логического нуля с выхода 2-триггера 15 запрещает прохождение тактовых импульсов от генератора 14 тактовых импульсов на счетный вход вычитающего счетчика 17 и вход синхронизации генератора 1 М -последовательности, а также через элемент И 16 (фиг. 5 д), элемент НЕ 13 (фиг, 5 е) на вход синхронизации выходного регистра 7. Сигнал логического нуля с инверсного выхода 8 б -триггера 11 блока 8 управления поступает также на входы установки выходного регистра 7 и генератора 1 А -последовательности иустанавливает их в исходные кодовыекомбинации. Выходной регистр 7, например, устанавливается в исходную композицию 000, а генератор 1 М-последовательности - в исходную комбинацию 111.Запуск генератора осуществляется путем установки переключателя 12 блока 8 управления в положение "Пуск". При этом на В -вход Ю -триггера 11 подается сигнал логического нуля через контакты переключателя 12,6 -триггер 11 устанавливается в нулевое состояние, На прямом выходе 88 -триггера 11 формируется сигнал логического нуля, который запрещает запись информации в первый 2 и второй 3 задающие регистры. На инверсном выходе кв-триггера 11 формируется сигнал.логической единицы, запрещающий запись исходных кодовыхкомбинаций в вычитающнй счетчик 17, выходной регистр 7 и генератор 1 ф последовательности. Сигнал логической единицы с инверсного выхода 8 -триггера 11 подается также наЭ- входО -триггера 15 в блоке 8 управления. По положительному фронту тактового импульса от генератора 14 тактовых импульсов Э-триггер 15 устанавливается в единичное состояние. Сигнал логической единицы с выхода 3-триггера 15 разрешает прохождение тактовых импульсов через элемент И 16 на счетный вход вычитающего счетчика 17, вход синхронизации генератора 1 М -последовательности, а также через элемент И 16 и элемент НЕ 13 на вход синхронизации выходного регистра 7. Сигнал логической единицы с выходами -триггера 15, поступая на вход блока индикации 19, вызывает свечение светодиода, что свидетельствует о формировании генератором выходных псевдослучайных последовательностей. Тактовые импульсы с выхода элемента И 16 блока8 управления, поступая на вход синхронизации генератора 1 М -последовательности, вызывают формирование наего выходах псевдослучайных кодов.С помощью элемента И 16 в последовательность псевдослучайных кодов генератора 1 М -последовательности включается нулевая комбинация, которая формируется между кодовыми комбинациями 0001 и 1000. Сформиро у хсу хЛх 25е.у =хлх л.4 х Ах ч 1-1лхтф р выходные сигналыблока 5-к приоритета;входные сигналы блока 5-к приоритета. х х х З 5 Из приведенных выше соотношенийлегко заметить следующие свойствапсевдослучайных последовательностей,формирующихся на выходах блоков5-15-п приоритета: в каждом такте работы генератора лишь один выходной сигнал блока 5-к приоритета(к ь 1,2 1 ) принимает значение 1;вероятность появления "1" на-мвыходе у блока 5-к приоритета а. =2Справедливость последнего свойст-.ва, в частности, можно показать следующим образом, Пусть- разрядностьгенератора 1 М -последовательности.Тогда эа период генератор 1 М -по- Ю следовательности сформирует 2 -беразрядных колов причем каждый 3 -)разрядный код встречается в последовательности кодов лишь один раз.Отсюда следует, что за период в про извольно выбранныхразрядах генератора 1 Щ-последовательности (1 с 3)каждый 1 -разрядный код встретитсяе 2 раз На входы блока 5-к приориванные генератором 1 М -последовательности псевдослучайные последовательности подаются на первые входыблоков 4-14-и сумматоров по моду лю два и повторяются на выходах техсумматоров по модулю два, на вторыевходы которых поступают сигналь 1 логического нуля от второго задающе Ого регистра 3, или инйертируются темисумматорами по модулю два, на вторые входы которых поступают сигналы логической единицы от второго задающего регистра 3. Преобразованныетаким образом псевдослучайные после довательности поступают на входы блоков 5-1 5- приоритета. Каждый иэблоков 5-к приоритета представляетсобой комбинационную логическую схемуреализующую следующую совокупностьпереключательных функций:тета поступают сигналы а с сумма 1торов по модулю два из блока 4-к О а=Ь Яс1 =. 1,2ш, где Ь,Ъ Ь - выходные сигналы генератора 1 Ц -последовательности; сс,сп, - код из второго задающего регистра 3. На-м выходе блока 5-к приоритета Формируется логическая единица если на входы блока поступает код а =а =а;= :О, а,=1. т.е. если генератор 1 М -Э последовательности Формирует-разрядный код Ъ 1=с 1,Ь=сЬ,= =с ,Ь; с. Этот-разрядный код 5 гза период последовательности генератора 19 -последовательности Форми.еруется 2 раэ. Отсюда вероятность появления логической единицы на"м выходе блока -,к приоритетов 6 =1. 20 2 и ) с = 2 "/2 = 2 . Из приведенных выше рассуждений также видно, что при изменении управляющего слова во втором регистре 3 можно изменять очередность следования 25 "1" и "О" в формируемых блоками 5-15- ц приоритета последовательностях без изменения вероятностейПричем на каждом-м выходе блоков 5-.1 5-приоритета можно получить з 02 различных последовательностей с вероятностью цоявления логическойе.единицы ;= 2 . Псевдослучайные последовательности с выходов блоков 5-15-приоритета поступают на входы соответствующих элементов И-ИЛИ 6-16-1, которые предназна чены для объединения по ИЛИ этих последовательностей с целью получения выходных последовательностей . 40с заданными вероятностями появлениялогической единицы Р .Р , Р , ВИсилу первого и второго свойств псевдослучайных последовательностей формируемьж блоками 5-15- И нри оритета, на выходах элементовИ-ИЛИ 6-16- получают последова- фЬътельности с вероятностями Р =2. 2Р к кк2игде 31 дксек: содержимое к-го поля управляющего слова, записанного в первом задающем регистре 2, Код 3 ,кео где 3; может принимать значения "1" или О", определяя таким образом, вероятность" Р для к-й выходной последовательности генератора, Очевидно, что вероятность Р (к=1,2 .И) может принимать значения О 2 22И Е3 Э Ф (2 -1) У , Псевдослучайные последовательности с выходов элементов И"ИЛИ 6-1 6-о поступают на информационные входы выходного регистра 7, куда они записываются тактовыми импульсами, подаваемыми на вход синхронизации вьжодного регистра 7. Работа генератора продолжается описанным выше образом до тех пор, пока он не сформирует М значений выходных псевдослучайных последовательностей. По переднему Фронту М-го тактового импульса с выхода элемента И 16 вычитающий счетчик 17 в блоке 8 управления устанавливается в нулевое состояние. После окончания этого тактовогоимпульса на выходе вычитающего счетчика 17 Формируется сигнал логического нуля (фиг, 5 ж), который обнуляет 2 -триггер 15 и затем удерживает его в нулевом состоянии. Сигнал логического нуля с выФхода 2 -триггера 15 запрещает прохождение тактовых импульсов от генератора 14 тактовых импульсов через элемент И 16. На вход блока 19 индикации поступает сигнал логического нуля, и светодиод прекращает светиться что указывает на окончание работы генератора.На каждом к-м выходе генератора .(к = 1,26 ) может быть сформиро, - .;г-.,2 ГИ вано максимально 1 + - (4 -1) псев 3дослучайных последовательностей (в- разрядность блока 5-к приоритета) разной структуры и с разными вероят-. ностями появления единицы в них.Таким образом, в предлагаемом уст ройстве достигается по сравнению с известным устройством Формирование большого числа выходных, псевдослучайньж последовательностей с заданным распределением вероятностей логической единйцы в них при одновременном изменении очередности следования единиц и нулей.1127079 орректор О., Билак селовск писное д. 4/5 Филиал ППП "Патент", г, Ужгород, ул, Проектная,Редактор Л, Заказ 8755/4 оставитель Ю. Бурмисехред Т.Иаточка Тираж 861 ВНИИПИ Государственного по делам изобретений и 13035, Москва, Ж, Раушкомитета открытий ская наб.

СмотретьЗаявка

3632589, 12.08.1983

ПРЕДПРИЯТИЕ ПЯ А-3756

БОГДАНОВ ВЯЧЕСЛАВ ВСЕВОЛОДОВИЧ, ЛУПИКОВ ВИКТОР СЕМЕНОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, последовательностей, псевдослучайных«

Опубликовано: 30.11.1984

Код ссылки

<a href="https://patents.su/8-1127079-generator-psevdosluchajjnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайных последовательностей</a>

Предыдущий патент: Импульсно-кодовый модулятор

Следующий патент: Генератор пилообразного напряжения

Случайный патент: Способ крепления датчиков с отверстия в корпусе в мягких тканях в эксперименте