Микропрограммное устройство для управления каналами эвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1068938

Авторы: Верига, Овсянников, Погодаев, Сиротко, Церлюкевич

Текст

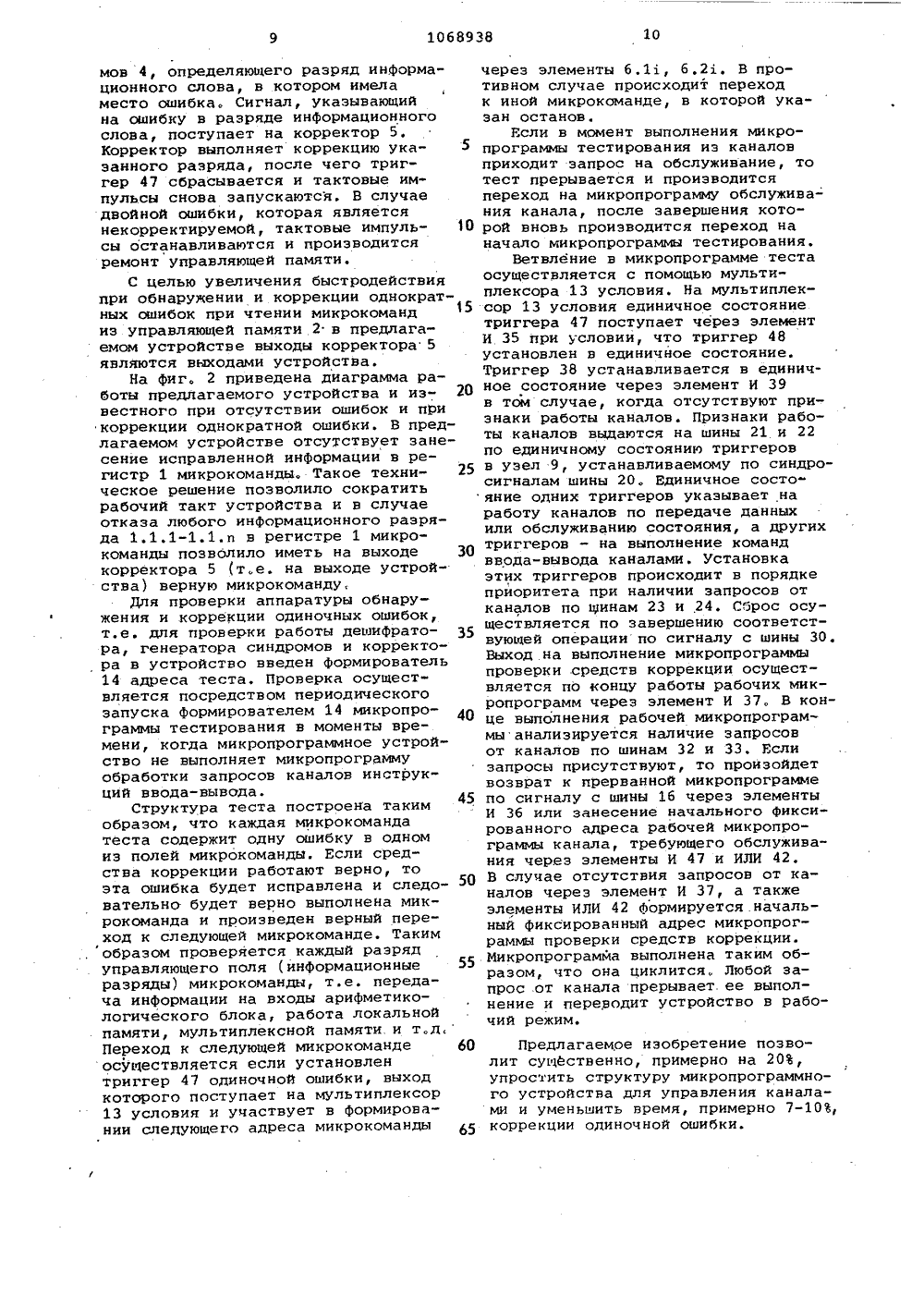

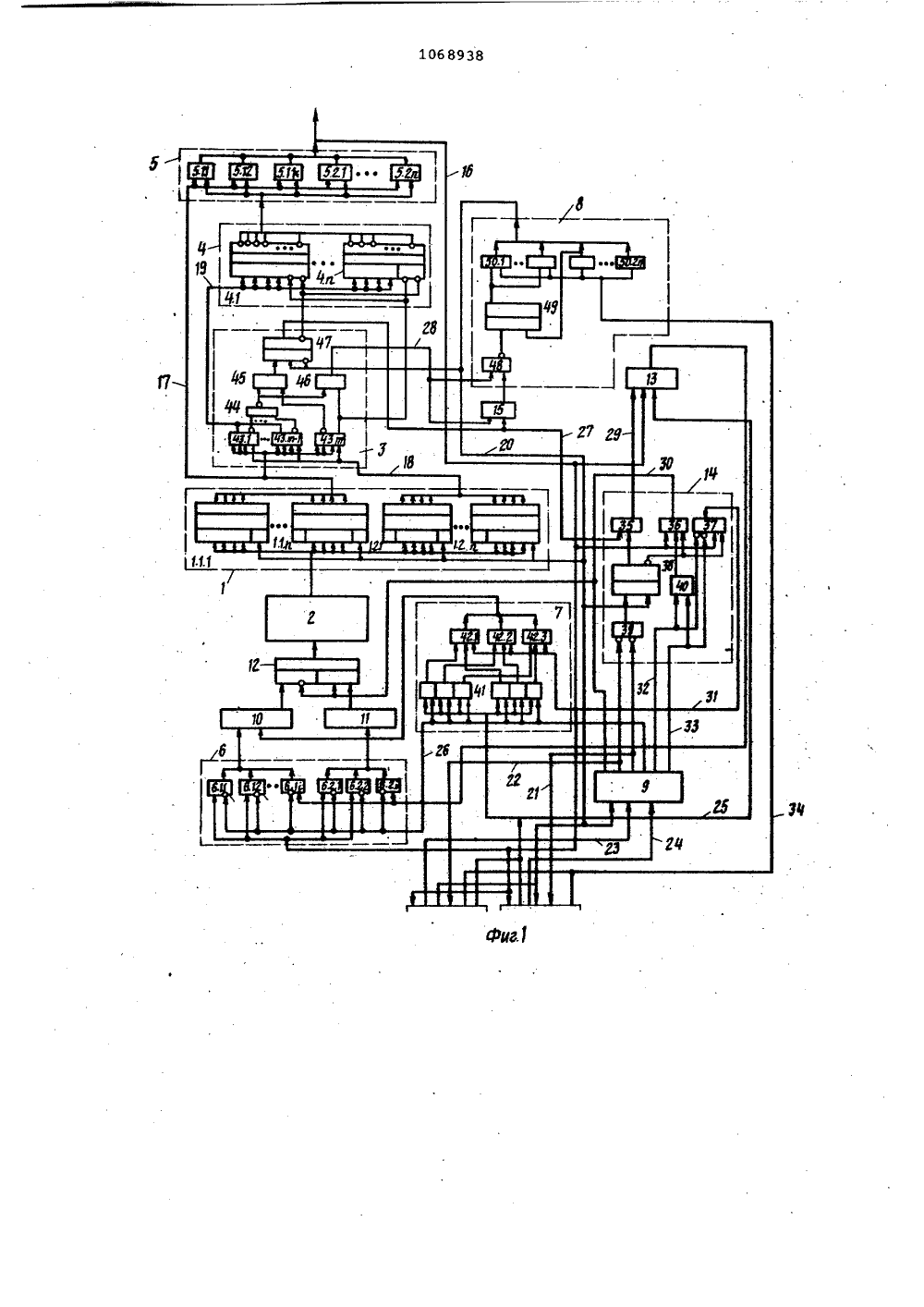

(19) (И) 9 22; 0 0 РЕТЕНИ ЕПЬСТВ иков фСт о СССР980 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИОПИСАНИЕ ИЗК АВТОРСКОМУ СВИДЕТ(56 ) 1. Процессор ЭВМ ЕС Под ред. А.М. Ларионова. М.тистика", 1975.2. Авторское свидетельствР 615478, кл. О 06 Р 9/22, 1(54 )( 57) 1. МИКРОПРОГРАММНОЕ УСТРОИСТВОДЛЯ УПРАВЛЕНИЯ КАНАЛАМИ ЭВМ, содержащее регистр микрокоманд, памятьмикропрограмм, генератор синдромов,блок дешифрации, корректор одиночной ошибки, блок формирования. естественного адреса, блок формированияфиксированного адреса, узел синхронизации, узел Фиксации запросЬв,регистр адреса, регистр возврата,элемент 2 И-ИЛИ и мультиплексор условия, выход которого подключен кпервому входу блока формирования естественного адреса, первый и второйвыходы которого подключены соответственно к первым входам регистраадреса и регистра возврата, выходыкоторых подключены соответственнок первому и второму входам элемента2 И-ИЛИ, выход которого подключенк входу памяти микропрограмм, выходкоторой подключен к первому входурегистра микрокоманд, первый выходкоторого через информационные шиныподключен к первым входам генератора синдромов и корректора одиночнойошибки, а второй выход через контрольные мины - к второму входу генератора синдромов, первый, второй итретий выходы которого подключенысоответственно к первому, второмуи третьему входам блока дешифрации,выход которого подключен к второму входу корректора одиночной ошибки, выход которого является выходной информационной шиной устройства и подключен к первому входу блокировки узла синхронизации и первому входу мультиплексора условия и второму входу блока формирования естественного адреса, третий вход которого и первый вход блока формирования фиксированного адреса подключены к первому выходу узла Фиксации запросов, первый и второй входы, второй и третий выходы которого подключены соответственно к выходным шинам запросов первого и второго каналов и . входным шинам признаков этих кана- ЕР лов, выходные шины условия первого и второго каналов подключены к вторым входам мультиплексора условия и блока Формирования Фиксированного ( адреса, выход которого подключен к второму входу регистра адреса, выход Д узла синхронизации подключен к второму входу регистра микрокоманд и .третьим входам генератора синдромов и узла фиксации запросов, вход синхроимпульсов узла синхронизацииподключен к выходным шинам синхронизации первого и второго каналов, о тл и ч а ю щ е е с я тем, что, с целью. увеличения быстродействия и упрощения устройства, оно содержит формирователь адреса теста и элемент ИЛИНЕ, выход которого подключен к второму входу блокировки узла синхронизации, а первый и второй входы элемента ИЛИ-НЕ подключены соответ- )Э ственно к четвертому и пятому выходам генератора синдромов, пятый выход которого подключен также .к первому входу Формирователя адреса теста, второй и третий входы которого подключены к выходным шинам признаков первого и второго каналов, ачетвертый,и пятый входа - к четвер10 б 8938 тому и пятому выходам узла фиксациизапросов, шестой и седьмой входыформирователя адреса теста подключены соответственно к выходу корректора одиночной ошибки и выходу узласинхронизации, первый и второй выходы Формирователя адреса теста подключены соответственно к третьимвходам мультиплексора условия и блока Формирования Фиксированного адреса, третий выход Формирователя адресата подключен к четвертому входуузла запросов и третьему и четверто-,му входам элемента 2 И-ИЛИ. 2. Устройство по п. 1, о т л ич а в щ е е с я тем, что формирователь адреса теста содержит триггер два элемента ИЛИ и три элемента И, выходы которых являются соответственно первым, вторым и третьим выходами формирователя, первый вход 1Изобретение относится к вычисли.тельной технике и может быть исполь-, зовано при организации процессоров каналов в ЗВМ общего и специального назначения, 5Известно микропрограммное устройство ЕС ЭВИ ряда 1, содержащее регистр микрокоманд, постоянную память, регистр адреса постоянной памяти и блок формирования адреса микрокоман ды, соединенные между собой, входами и выходами устройства с помощью адресных, управляющих и информационныхшин Ш .Недостатком данного устРойства 15 является сравнительно низкая надежность, так как в нем отсутствуют средства Для обнаружения кратных и коррекции однократных ошибок в информационных трактах.20Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее регистр микрокоманд, управляющую память, генератор синдромов, блок де шифрации, корректор одиночной ошибки, блок формирования естественного адреса, блок формирования фиксированного адреса, узел синхронизации, узел запросов, регистр адреса, ре- З 0 гистр возврата, элемент 2 И-ИЛЙ и мультиплексор условия, выход которого подклвчен к первому входу блока формирования естественного адреса, первый и второй выходы которого под- З 5 клвчены к первым входам регистра адреса и регистра возврата, выходы ,первого элемента И является первымвходом формирователя, и второй входсоединен с первым выходом триггера,первый вход которого является седьмым входом формирователя, а второйвход соединен с выходом первого элемента ИЛИ, входы которого являютсясоответственно вторым и третьим входами формирователя, четвертый и пятый входы которого соединены с первыми, вторыми входами второго элемента ИЛИ и первым и вторым инверсными входами третьего элемента И,третий и четвертый входы которогосоединены соответственно с вторымвыходом триггера и шестым входомформирователя, соединенным такжес первым входом второго элемента И,второй и третий входы которого .соединены соответственно с выходомвторого элемента ИЛИ и вторым выходом триггера. 2которых подключены к первым и вторым входам элемента 2 И-ИЛИ, выход котоРого подключен к входу управляющей памяти, выход которой подключен к первому входу регистра микрокоманд, первый выход которого через информационные шины подключен к первым входам генератора синдромов и корректора одиночной ошибки, а второй выход через контрольные шины - к второму входу генератора, первый, второй и третий выходы которого подключены к одноименным входам блока дешифрации, причем первый - через шины синд- . ромов, выход блока дешифрации подключен к второму входу корректора одиночной ошибки, выход которого через выводные информационные шины устройства подключен к первому входу узла синхронизации, к вторым входам мультиплексора условия и блока формирования естественного адреса, тре-. тий вход которого через шину фиксированного кода подключен к второму входу блока формирования фиксированного адреса и третьему выходу узла запросов, первые и вторые входы и. выходы которого подклвчены соответственно к шинам запросов первого и второго каналов и шинам признаков этих каналов, а шины условия каналов подключены к первым входам мультиплексора условия и блока формиро,вания фиксированного адреса, выход которого подключен к второму входу регистра адреса, выход узла синхронизации через управляющие шиныподключены к второму входу регистра микрокоманд и третьим входам генераторасиндромов и узла запросов, а второйвход узла синхронизации подключенк шинам синхронизации Г 21.Недостатками известного устрой-.ства являются сравнительно большоевремя коррекции однократных ошибок,избыточность аппаратуры, затрачиваемой на дубль аппаратуры проверкицепей обнаружения и коррекции ошибок.Кроме того, выход из строя любого 10информационного разряда регистрамикрокоманды вызывает отказ в работеустройства в целом.Целью изобретения является увеличение быстродействия и упрощение 15устройства (увеличение быстродействия достигается за счет уменьшения времени коррекции одиночныхошибок, упрощение устройства достигается тем, что в предлагаемом устройстве производится периодическийтестовый контроль аппаратуры, обнаружения ошибок, что позволило убрать аппаратуру проверки цепей обна,ружения и коррекции ошибок в микропрограммном устройстве,Поставленная цель достигается тем, что в микропрограммное устройство для управления каналами ЭВМ, содержащее регистр микрокоманд, па мять микропрограмм, генератор синдромов, блок дешифрации, корректор одиночной ошибки, блок формирбвания естественного адреса, блок формирования фиксированного адреса, узел 35 синхронизации, узел фиксации запросов, регистр адреса, регистр возврата, элемент 2 И-ИЛИ и мультиплексор условия, выход которого подключен к первому входу блока формирования 40 естественного адреса, первый и второй выходы которого подключены соответственно к первым входам Регистра адреса и регистра возврата, выходы котоРЫХ подключены соответст венно к первому и второму входам элемента 2 И-ИЛИ, выход которого под ключен к входу памяти микропрограмм, выход которой подключен к первому входу регистра микрокоманд, первый выход которого через информационные шины подключен к первым входам генератора синдромов и корректора оди- ночной ошибки, а второй выход через контрольные шины - к второму входу генератора синдромов, первый, вто рой и третий выходы которого подклю- чены соответственно к первому, второму и третьему входам блока дешифрации, выход которого подключен к второму входу корректора одиночной 60 ошибки, выход которого является выходной информационной шиной устрбйства и подключен к первому входу :-блокировки узла синхронизации и первому входу мультиплексора условия и второму входу блока формирования естественного адреса, третий вход которого и первый вход блока формирования фиксированного адреса подключены к первому выходу узла фиксации запросов, первый и второй входы, второй и третий выходы которого подключены соответственно к выходным шинам запросов первого и второго каналов и входным шинам признаков этих каналов, выходные шины условия первого и второго каналов подключены к вторым входам мультиплексора условия и блока формирования фиксированного адреса, выход которого подключен к второму входу регистра адреса, выход узла синхронизации подключен к второму входу регистра микроманд и третьим входам генератора синдромов и узла фиксации запросов, вход синхроимпульсов узла синхронизации подключен к выходным шинам синхронизации первого и второго каналов, введены формирователь адреса теста и элемент ИЛИ-НЕ, выход которого подключен к второму входу блокировки узла синхронизации, а первый и второй входы элемента ИЛИ-НЕ подключены соответственно к четвертому и пятому выходам генератора синдромов, пятый выход которого подключен также к первому входу формирователя адреса теста, второй и третий входы которого подключены к выходным шинам признаков первого и второго каналов., а четвертый и пятый входы - к четвертому и пятому выходам узла фиксации запросов, шестой и седьмой входы подключены соответственно к выходу корректора одиночной ошибки и выходу узла синхронизации, первый и второй выходы формирователя адреса теста подключены соответственно к третьим входам мультиплексора условия и блока формирования фиксированного адреса, третий выход формирования фиксатора подключен к четвертому входу узла запросов,и третьему и четвертому входам элемента 2 И-ИЛИ.Кроме того, формирователь адреса теста содержит триггер, два элемента ИЛИ и три элемента Ивыходы которых являются соответственно первым, вторым и третьим выходами формирователя, первый вход первого элемента И.является первым входом формирователя, а второй вход соединен с первым выходом триггера, первый вход которого является седьмым входом формирователя, а второй вход соединен с выходом первого элемента ИЛИ, входы которого являются соответственно вторым и третьим входами формирователя, четвертый и пятый входы которого соединены с первыми и вторыми входами второго элемента40 ИЛИ и первым н вторым инверснымивходами третвего элемента И, третийичетвертый входы которого соедине-ны соответственно с вторым выходомтриггера и шестым входом формирователя, соединенным также с первымвходом второго элемента И, второйи третий входы которого соединенысоответственно с выходом второгоэлемента ИЛИ и вторым выходом триггера.На фиг. 1 изображена структурамикропрограммного устройства; нафиг. 2 - временная диаграмма егоработы.Жкропрограммное устройство пред 15назначено для управления всеми процедурами в каналах ввода-вывода(в панельных процессорах). В качестве каналов могут служить блоковыеи байт-мультиплексные каналы ввода" 20вывода. Количество каналов можетбыть неограниченным и определяетсяпропускной способностью ЭВИ, в которой применено.микропрограммноеустройство. 25устройство содержит регистр 1мнкрокоманды, память 2 микропрограмм,. генератор 3 синдромов, блок 4 дешифрации, корректор 5 одиночной ошибки,блок 6 Формирования естественного 30адреса, блок 7 формирования фиксированного адреса, узел 8 синхронизации, узел 9 фиксации запросов,регистр 10 адреса, регистр 11 возврата, элемент 2 И-ИЛИ 12, мультиплексор 13 условия, формирователь 14адреса теста, элемент ИЛИ 15. Устройство также содержит выходную информационную шину 16, информационнуюшину 17, контрольную шину 18, шину 19 синдромов, управляюшую шину20, входную шину 21 и 22 признаковпервого и второго каналов, выходнуюшину 23 (24) запросов первого (второго) канала, выходную шину 25 условий каналов, шину 26 Фиксирован- .,45ного кода, шину 27 однократной ошибки, шину 28 двухкратной ошибки, шину 29 перехода, шину 30 .возврата,шину 31 начала теста, шину 32 инструкции, шину 33 микропрограммного 50прерывания и шину 34 синхронизации.Формирователь адреса содержитэлементы И 35-37, триггер 38, элементы ИЛИ 39 и 40. Длок формирования фиксированного адреса содержит 55элементы И 41, элементы ИЛИ 42.142.3. Генератор синдромов содержитсумматоры 43.1-43.щ по модулю два,элемент И-НЕ 44, элементы И 45 и 46,триггер 47, 60Узел синхронизации содержит элемент И 48, триггер 49 и элементыИ 50.1-50.2 п,Регистр 1 макрокоманды служитдля приема микроксианды из памяти 2 65 микропрограмм и хранения ее на время выполнения микрокоманды и разделен на две части - информационнуючасть 1,1.1-1,1.п и контрольную1 1,2 д, Регистр 1 выполнен наэлементах сдвига типа 533 ИР 16, Информационные входы элементов подключены к первому информационному входу регистра, а информационные выходы элементов регистра 1.1,.1-1,1ии 1.2.1-1.2.ш соответственно - к первому и второму выходам регистрамикрокоманд, Входы синхронизацииэлементов регистра подключены к второму управляющему входу регистра,Память 2 микропрограмм предназначена для хранения наборов микропрограмм, управляющих работой кана лов ввода-вывода, а также осуществляющих периодический контроль оборудования как каналов, так .и самогомикропрограммного устройства.Генератор 3 синдромов вырабатывает синдромы коррекции ошибки.Блок 4 дешифрации вырабатываеткорректирующий сигнал для исправления разряда микрокоманды по синдрому, получаемому от генератора синдромов, и выполнен на элементах4,1-4.п дешифратора 4 х 16 типа 133ИДЗ, информационные и управляющиевходы которых подключены к первым,вторым и третьим входам блока, авыходы - к выходу блока.Корректор 5 одиночной ошибкикорректирует сбойный разряд регистра микрокоманды согласно информации, получаемой от блока дешифрации.Корректор выполнен на, элементах5,1-5,2 п сложения по модулю 2 типа530 ИП 5, входы которых подключенык первйм и вторым информационнымвходам блока, а выводы -.к выходублока.Блок б формирования естественного адреса служит. для Формированияследующего адреса мнкрокоманды последовательно выполняемой микропрограммы. Блок 6 выполнен на элемен- .тах 2 И 6,1-6.11 и 6.2.1-6.2 х. Прямые и инверсные входы элементов6.1,1-6.1 и 6.2,1-6.2 подключенысоответственно к первому и второмувходам блока.Блок 7 формирования фиксированного адреса предназначен для Формирования начального адреса микропрограммы, нарушающей естественныйход адресации вследствие. каких-либопричин (,запросов на обслуживаниеот каналов, возникновения ошибкии т.д,),Узел 8 синхронизации служит длявыработки серии синхроимпульсов,управляющих работой микропрограммного устройства и каналов вводавывода (не показаны). Узел 9 Фиксации запросов фиксирует запросына обслуживание от каналов вводавывода по определенному приоритету,формирует признаки работающего канала и запросы на вход в соответствующую микропрограмму. Регистр 10.адреса служит для хранения адресауправляющей памяти, по которому происходит обращение к памяти, для управления работой каналов ввода-вывода,Регистр 11 возврата микропрограммслужит для запоминания адреса прерванной микропрограммы, которая является менее приоритетной по сравнениюс прерывающей ее микропрограммой.По концу работы прерывающей микропрограммы производится обращение куправляющей памяти по регистру 11и прерванная микропрограмма продолжается.Мультиплексор 13 условия участвует в формировании естественногоследующего адреса микропрограммыпосредством организации ветвленийв микропрограммах. Формирователь 14адреса теста вырабатывает начальныйадрес микропрограммы теста и организует ветвление в тесте в зависимостиот результатов тестирования.Работа микропрограммного устройства на примере подключения двух каналов. По адресу, хранящемуся в регистре 10 из памяти 2, считывается микрокоманда в регистр 1 микрокоманды. Иикрокоманда состоит из информационного и контрольного слов, которые размещаются на триггерных элементах сдвига 1.1.1-1,1.п и 1.2.1-1.2.п сбответственно. Информационное слово управляет всеми процедурами в каналах и разбито на ряд управляющих полей - поля управления арифметико-логическим блоком, обращениями к оперативной, локальной, мультиплексной памятям, установкой отдельных триггеров, формированием признаков, поле адреса следующей микрокоманды и т.д, Информационное слово поступает через элементы 51,1-5,1. сложения.по модулю два корректора 5.на выходную шину 16, а после адреса следующей микрокоманды - в блок 6 формирования естественного адреса и на мультиплексор 13 условия ветвлений через элементы 5,2.1-5.2.п сложения по модулю 2. Адрес следующей микрокоманды ФормируЕтся на элементах И 6.1,1-6 .1 и передается в регистр 10 адреса управляющей памяти. В случае, когда из каналов по шинам 23 и 24 в устройство поступает запрос на выполнение микропрограммы более приоритетной, чем выполняется в текущий момент, узел 9 вырабатывает на шину 26 Фиксированного кода сигнал,Г который запрещает занесение естественного адреса микрокоманды в регистр 10 и запускает блок 7 формирования Фиксированного адреса. Последний через элементы И 41, ИЛИ 5 42.1-42.3 формирует фиксированныйадрес прерывающей микропрограммы,код которой, вырабатываемыйнепосредственно каналом, поступает в регистр10 через шину 25 и блок 7. При этом 10 естественный адрес микрокомандыпрерванной микропрограммы запоми.нается в регистре 11 возврата микропрограмм В последней микрокомандепрерывающей микропрограммы по шине 15 30 производится обращение памяти 2по содержимому регистра 11 возврата микропрограмм и прерванная микропрограмма продолжается. Такая процедура выполняется всякий раз, ког да из каналов поступают более приоритетные запросы на выполнение микропрограмм, чем выполняются в данный момент времени.Правильность считывания микро команд из памяти 2 и занесения ихв регистр 1 микрокоманды контролируется по коду Хэмминга. Для этогокаждому информационному слову ставится в соответствие контрольноеслово группа контрольных разрядов),сформированное по определенным правилам из разрядов информационногослова.Совокупность этих двух словмо жет рассматриваться как новое слово,состоящее из информационных и контрольных частей. Если при считыванииили хранении информации в управляющей памяти или при занесении в ре гистр 1 микрокоманды произошло искажение разряда слова,то соответствие между информационной и контрольной частями нарушается, что исвидетельствует о наличии неисправ ности. Соответствие между информационной и контрольной частями определяется кодом Хэжинга, который.позволяет корректировать одиночныеи обнаруживать двойные ошибки. Дяяобнаружения ошибок информационноеи контрольное слово поступают вгенератор 3 синдромов на. элементы43,1-43.щ сложения по модулю 2 длявыработки синдромов. Нулевые синдромы указывают на отсутствие,ошибки, присутствие единиц - на Наличиеошибки. В случае одиночной ошибкичерез элементы И-НЕ 45 и 46 устанавливается в единичное состояние триггер 47, по которому в блоке 8 оста навливаются тактовые импульсы сэлементов И 50.1-50.2 п, которые управляют работой каналов и занесением новой информации в регистр 1.Единичное состояние трйггера. 47 разрешает работу дешифратора синдро 1068938 10мов 4, определяющего разряд информационного слова, в котором имеламесто ошибка, Сигнал, указывающийна ошибку в разряде информационногослова, поступает на корректор 5,Корректор выполняет коррекцию укаэанного разряда, после чего триггер 47 сбрасывается и тактовые импульсы снова запускаются. В случаедвойной ошибки, которая являетсянекорректируемой, тактовые импульсы останавливаются и производитсяремонт управляющей памяти.С целью увеличения быстродействияпри обнаружении и коррекции однократных ошибок при чтении микрокомандиэ управляющей памяти 2 в предлагаемом устройстве выходы корректора 5являются выходами устройства.На фиг. 2 приведена диаграмма работы предлагаемого устройства и известного при отсутствии ошибок и прикоррекции однократной ошибки. В предлагаемом устройстве отсутствует занесение исправленной информации в регистр 1 микрокоманды. Такое техническое решение позволило сократитьрабочий такт устройства и н случаеотказа любого информационного разряда 1.1.1-1.1.п в регистре 1 микрокоманды позволило иметь на выходе 30корректора 5 (т.е. на выходе устройства) верную микрокоманду,Для проверки аппаратуры обнаружения и коррекции одиночных ошибок,т.е. для проверки работы дешифратора, генератора синдромов и корректора в устройство введен формирователь14 адреса теста. Пронерка осуществляется посредством периодическогозапУска Формирователем 14 микропрограммы тестирования в моменты времени, когда микропрограммное устройство не выполняет микропрограммуобработки запросов каналов инструкций ввода-вывода.Структура теста построена такимобразом, что каждая микрокомандатеста содержит одну ошибку н одномиз полей микрокоманды. Если средства коррекции работают верно, тоэта ошибка будет испранлена и следовательно будет верно выполнена микрокоманда и произведен верный переход к следующей микрокоманде. Такимобразом проверяется каждый разрядуправляющего поля (информационные 55разряды) микрокоманды, т.е. передача информации на входы арифметикологического блока, работа локальнойпамяти, мультиплексной памяти и т.д,Переход к следующей микрокоманде 60осуществляется если установлентриггер 47 одиночной ошибки, выходкоторого поступает на мультиплексор13 условия и участвует в формировании следующего адреса микрокоманды через элементы 6.11, 6,2. В противном случае происходит переход к иной микрокоманде, н которой указан останов.Если в момент выполнения микропрограммы тестирования из каналов приходит запрос на обслуживание, то тест прерывается и производится переход на микропрограмму обслужива- ния канала, после завершения которой вновь производится переход на начало микропрограммы тестирования.Ветвление в микропрограмме теста осуществляется с помощью мультиплексора 13 условия. На мультиплексор 13 условия единичное состояние триггера 47 поступает через элемент И 35 при условии, что триггер 48 установлен в единичное состояние. Триггер 38 устанавливается в единичное состояние через элемент И 39 в том случае, когда отсутствуют признаки работы каналов. Признаки работы каналов выдаются на шины 21 и 22 по единичному состоянию триггеров в узел 9, устанавливаемому по синдросигналам шины 20. Единичное состояние одних триггеров указывает на работу каналов по передаче данных или обслуживанию состояния, а других триггеров - на выполнение команд ввода-вывода каналамиУстановка этих триггеров происходит в порядке приоритета при наличии запросов от каналов по цинам 23 и 24. Сброс осуществляется по завершению соответствующей операции по сигналу с шины 30, Выход на выполнение микропрограммы проверки средств коррекции осуществляется по концу работы рабочих микропрограмм через элемент И 37, В конце выполнения рабочей микропрограммы анализируется наличие запросов от каналов по шинам 32 и 33. Если запросы присутствуют, то произойдет возврат к прерванной микропрограмме по сигналу с шины 16 через элементы И 36 или занесение начального фиксированного адреса рабочей микропрограммы канала, требующего обслуживания через элементы И 47 и ИЛИ 42. В случае отсутствия запросон от каналов через элемент И 37, а также элементы ИЛИ 42 формируется начальный фиксированный адрес микропрограммы проверки средств коррекции. Микропрограмма выполнена таким образом, что она циклится. Любой запрос от канала прерывает. ее выполнение и переводит устройство в рабочий режим.Предлагаемое изобретение позволит существенно, примерно на 20, упростить структуру микропрограммного устройства для управления каналами и уменьшить время, примерно 7-10, коррекции одиночной ошибки.10 б 8938 Фет оаиоок Есть ойночная йиибко Ирес е региющМ . Закгсеюе Ф регистр 4 юмд си Коррекция дВьююмае иди ИфоквФ г.Г Редант о ак Подписномитета СССРткрытийая наб., д. 4/5 473/45 Тираж 703ВНИИПИ Государственного кпо делам изобретений и13035, Москва, Я, Раушс Филиал ППП "Патентф, г. Ужгород, ул. Проектная, 4 адрес 6 регистр Ю ймсеаге б регистр Люао сик 4 ююд Р Коррекция 6 керрекеоре оВЫЛОМЕНИЕ ЮИРО- коюИы Составитель И. Хазовач Техред М. Гергег.ьКорректор ИМУск

СмотретьЗаявка

3502478, 22.10.1982

ПРЕДПРИЯТИЕ ПЯ М-5339

ВЕРИГА МАРГАРИТА АНДРЕЕВНА, ОВСЯННИКОВ ВАЛЕРИЙ ИВАНОВИЧ, ПОГОДАЕВ ВАЛЕРИЙ ВИКТОРОВИЧ, СИРОТКО ЕЛЕНА АНАТОЛЬЕВНА, ЦЕРЛЮКЕВИЧ АЛЛА ИОСИФОВНА

МПК / Метки

МПК: G06F 9/22

Метки: каналами, микропрограммное, эвм

Опубликовано: 23.01.1984

Код ссылки

<a href="https://patents.su/8-1068938-mikroprogrammnoe-ustrojjstvo-dlya-upravleniya-kanalami-ehvm.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство для управления каналами эвм</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Устройство для формирования адреса данных

Случайный патент: Способ выявления иммунных антител