Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

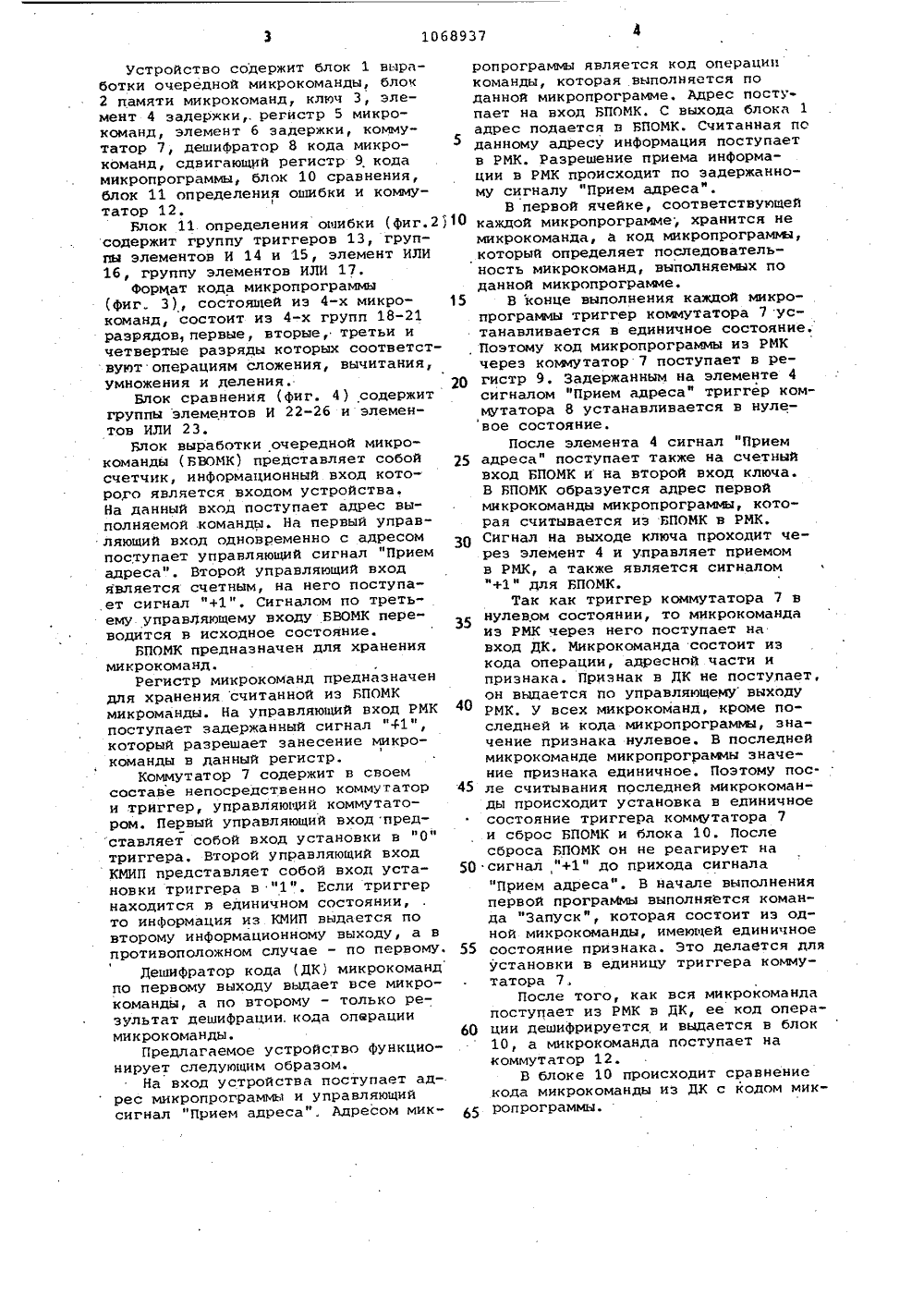

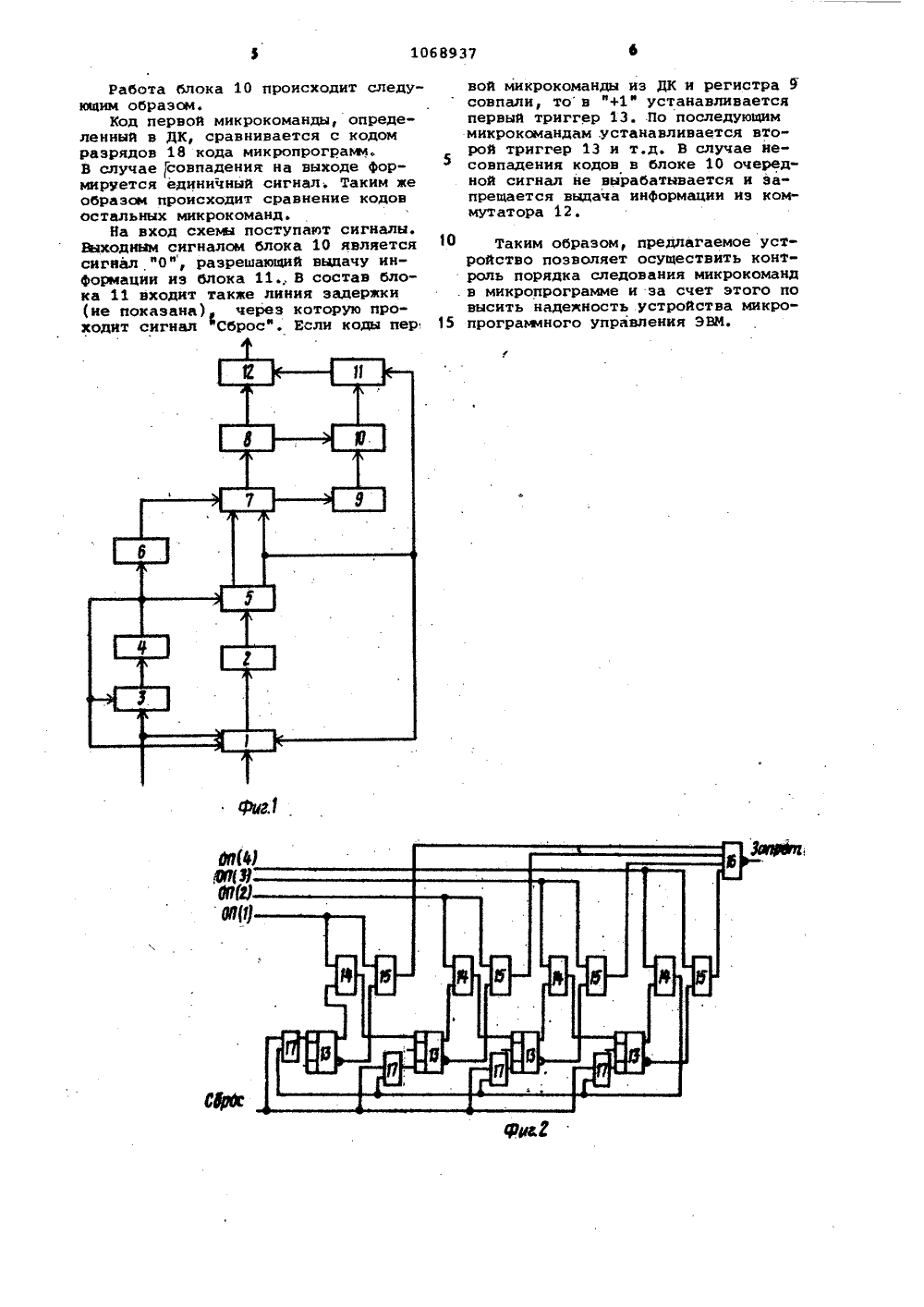

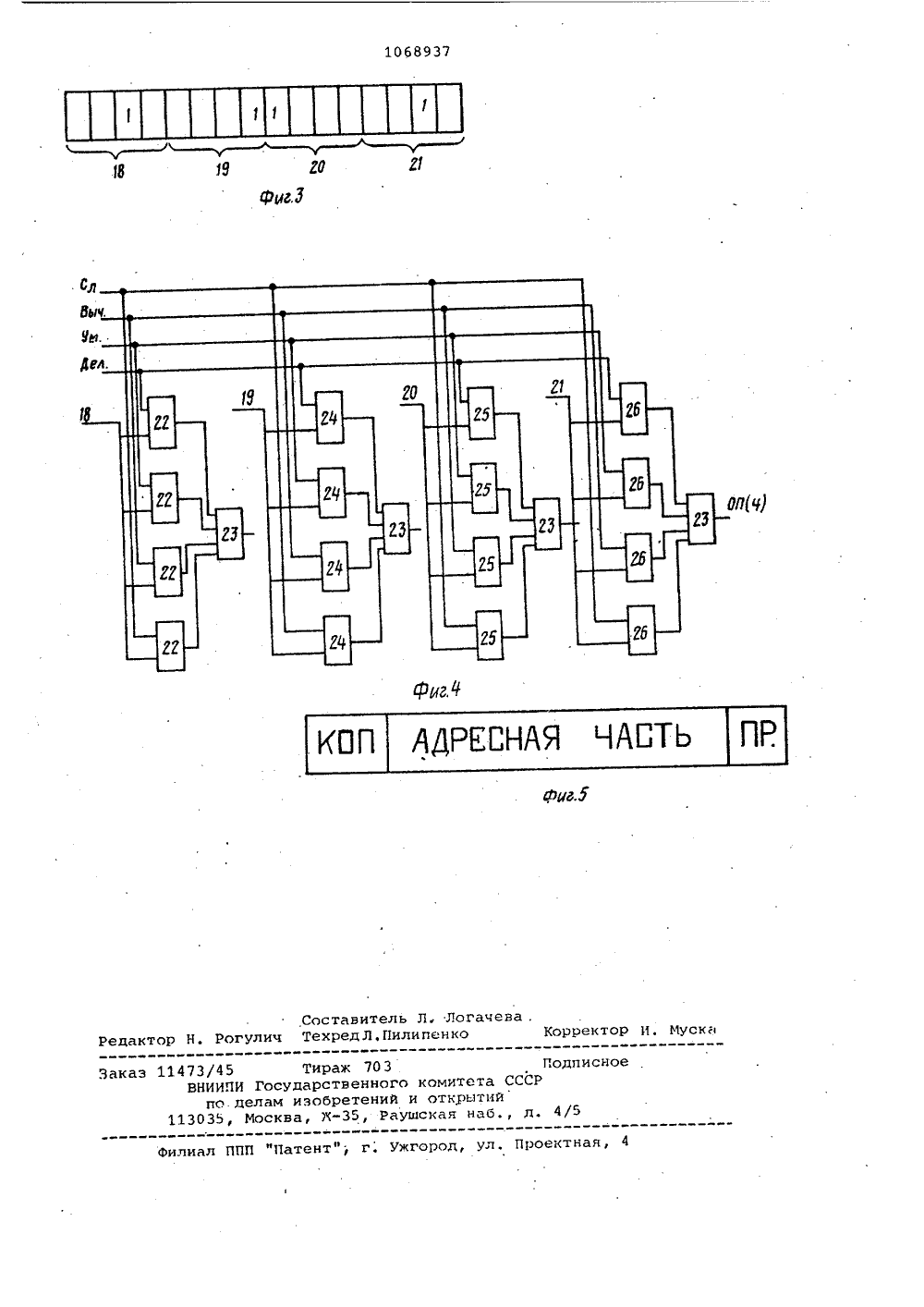

(19) (1 А з(511 а 0 ОПИСАН ИЗ НИЯ АВТОРСКОМ ТЕЛЬСТВУ м л ОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(56) 1. Авторское свидетельство С 9 543939, кл. 0 06 У 9/22, 1973.2, Авторское свидетельство СССР У 556439, кл. 0 06 Р 9/22, 1975 (прототип).(54)(57) 1. УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее блок выработки очередной микрокоманды, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, первый выход.дешифратора кода микро- команд соединен с информационным входом первого коммутатора, выход которого подключен к выходу устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности за счет контроля правильности порядка следования микрокоманд в микропрограмме, оно дополнительно содержит два элемента задержки, второй коммутатор, блок сравнения, блок определения ошибки и сдвигающий регистр кода микропрограммы, причем управляющий вход устройства соединен с первым входом ключа и первым уп-. равлянвим входом блока выработки очередной микрокоманды, второй управляющий вход которого соединен с управляющим входом регистра микрокоманд, с входом первого элемента задержки, с вторым входом ключа и с выходом ключа через второй элемент задержки, выход первого элемента задержки соединен с первым управляющим входом второго коммутатора, информационный и второй управляищий входы которого соединены соответственно с информационным и управляющим выходами регистра микрокоманд, первый выход второго коммутатора соединен с входом сдвигающего регистра кода микропрограммы, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с вторым выходом дешифратора кЬда микрокоманд, вход которого соединен с вторым выходом второго коммутатора, выход блока сравнения подключен к информационному входу блока определения ошибки, выход которого соединен с управляющим входом первого ковиутатора, а управляющий вход . - с управляющим выходом регистра. микро- команд и с третьим управляющим входом блока определения очередной микро- Е команды, информационный вход которого соединен с адресным входом устройства.2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок определения ошибки содержит две группы элементов И, группу элементов Я ИЛИ, группу триггеров и элемент ИЛИ причем информационный вход блока подключен к первым входам элементов И первой и второй групп, к вторым входам которых подключены. соответственно прямые и инверсные выходы триггеров группы, к входам сброса которых, кроме первого, подключены выходы элементов ИЛИ группы, кроме первого, выход которого соединен с единичным входом первого триггера группы, выходы элементов И первой группы, кроме последнего, подключены соответственно к единичным входа триггеров группы, кроме первого, выход последнего элемента И первой группы соединен с первыми входами элементов ИЛИ группы, вторые входы которых соединены с управляющим входом блока, выходы элементов И второй группы соединены с входами элемента ИЛИ, выход которого подк ючен к выходу блока.ния ошибок, на фиг. 3 - формат кодамикропрограммы; на фиг. 4 - схема блока сравнения на фиг. 5 - форматмикрокоманды. Изобретение относится к вычислительной технике и может быть исполь, зовано для расширения функциональ"ных возможностей и повышения надежности работы устройства УправленияЭ ВИ.5Известно микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса,блок формирования адреса, блок выработки микроопераций, блоки заданияконтрольного режима и блок контроля П,Недостатком этого устройстваявляется отсутствие контроля порядка правильности следования операций 15Наиболее близким к предлагаемомуявляется устройство, содержащее всвоем составе блок выработки очередной микрокоманды, блок памяти микрокоманд, регистр микрокоманд, дешифратор кода микрокоманд, коммутатор, причем выходы блока выработкиочередной микрокоманды соединеныс входами блока памяти микрокоманд,выходы дешифратора кода микрокоманд 25соединены с информационными входамикоммутатора.Для повышения надежности устройства н нем резервируются основныеблоки - регистр микрокоманд, блок 30памяти микрокоманд, дешифратор ивводится регистр контроля. В случаевыхода из строя одного из основных.блоков продолжают работать резервные,обеспечивая надежное функционирование всего устройства21,Однако н известном устройстве невозможен контроль за порядком следования микрокоманд н микропрограмме.При нарушении порядка следованиямикрокоманд, например по причинеслучайного сбоя оборудования устройства управления, ошибка обнаруженане будет, т.е. произойдет отказ устройства.целью изобретения является повышение надежности за счет контроляправильности порядка следования микрокоманд н микропрограмме.указанная цель достигается тем,что в устройство микропрограммногоуправления, содержащее блок выработки очередной микрокоманды, выход которого соединен с адресным входомблока памяти микрокоманд, выход которого соединен с информационнымвходом регистра микрокоманд, первыйвыход .дешифратора кода микрокомандсоединен с информационным входом первого коммутатора, выход которого подключен к выходу устройства, введены 60два элемента задержки, второй коммутатор, блок сравнения, блок опре-деления ошибки и двигающий регистркода микропрограммы, причем управляющий вход устройства содинен,с пер ным входом ключа и первым управляющим входом блока выработки очередной микрокоманды, второй управляющий вход которого соединен с управляющим входом регистра микрокоманд,с входом первого элемента задержки,с вторым входом ключа и с выходом ключа через второй элемент задержки,выход пврвого элемента задержки соединен с первым управляющим входом второго коммутатора, информационный и второй управляющий входы которогосоединены соответственно с информационным и управляющим выходами регистра микрокоманд, первый выходвторого коммутатора соединен с входом сдвигающего регистра кода микропрограммы, выход которого соединен с первым входом. блока сравнения,второй вход которого соединен с вторым выходом дешифратора кода микрокоманд, вход которого соединен свторым выходом второго коммутатора,выход блока сравнения подключен кинформационному входу блока опреде-.ления ошибки, выход которого соединен с управляющим входом первогокоммутатора, а упранляющий входс управляющим выходом регистра микрокоманд и с третьим управляющимвходом блока определения очередноймикрокоманды, информационный вход которого соединен с адресным входом УстРОЙства. Кроме того, блок Определения ошибки содержит две группы элементов И,группу элементов ИЛИ, группу триггеров и элемент ИЛИ, причем информационный вход блока подключен кпервым входам элементов И первойи второй групп, к вторым входам которых подключены соответственно прямые и инверсные выходы триггеров группы, к входам сброса которых, кроме первого, подключены выходы элементов ИЛИ группы, кроме первого,выход которого соединен с единичным входом первого триггера группы, выходы элементов И первой группы, кроме последнего, подключены соотнетстненно к единичным входам триггеров группы, кроме первого, выход последнего элемента И первой группы соединен с первыми входами элементон ИЛИ группы, вторые входы которых соединены с управляющим входом блока, выходы элементов И нторой группы соединены с входами элемента ИЛИ, выход которого подключен к выходу блока,На фиг., 1 представлена структурная схема устройства на фиг. 2 функциональная схема блока определе25 30 35 40 45 50 сигнал "+1" до прихода сигнала"Прием адресаф. В начале выполнения первой программы выполняется команда "Запускф, которая состоит из одной микрокоманды, имеющей единичное 55 состояние признака. Это делается дляустановки в единицу триггера коммутатора 7.После того, как вся микрокомандапоступает из РМК в ДК, ее код опера ции дешифрируется и выдается в блок10, а микрокоманда поступает на коммутатор 12.В блоке 10 происходит сравнениекода микрокоманды из ДХ с кодом мик Ропрограммы. Устройство содержит блок 1 выработки очередной микрокоманды, блок 2 памяти микрокоманд, ключ 3, элемент 4 задержки,. регйстр 5 микро- команд, элемент 6 задержки, коммутатор 7, дешифратор 8 кода микро- команд, сдвигающий регистр 9, кода микропрограммы, блок 10 сравнения, блок 11 определения ошибки и коммутатор 12.Блок 11.определения ошибки (фиг.2) содержит группу триггеров 13, группы элементов И 14 и 15, элемент ИЛИ 16, группу элементов ИЛИ 17.формат кода микропрограммы (фиг. 3), состоящей из 4-х микро- команд, состоит из 4-х групп 18-21 разрядов, первые, вторые, третьи и четвертые разряды которых соответствуют операциям сложения, вычитания, умножения и деления.Блок сравнения (фиг. 4) содержитгруппы элементов И 22-26 иэлементов ИЛИ 23.Блок выработки очередной микро- команды (БВОМК) представляет собой счетчик, информационный вход которого является входом устройства. На данный вход поступает адрес выполняемой .команды. На первый управляющий вход одновременно с адресом поступает управляющий сигнал "Прием адреса". Второй управляющий вход является счетным, на него поступа" ет сигнал "+1". Сигналом по третьему управЛяющему входу БВОМК переводится в исходное состояние.БПОМК предназначен для хранения микрокоманд.Регистр микрокоманд предназначен для хранения считанной из БПОМК микроманды. На управляющий вход РМК поступает задержанный сигнал "Ф 1", который разрешает занесение микро- команды в данный регистр.Коммутатор 7 содержит в своем составе непосредственно коммутатор и триггер, управляющий коммутатором. Первый управляющий вход представляет собой вход установки в "0" триггера, Второй управляющий вход КМИП представляет собой вход установки триггера в "1". Если триггер находится в единичном состоянии, то информация из КМИП выдается по второму информационному выходу, а в противоположном случае - по первому.Дешифратор кода (ДК) микрокоманд по первому выходу выдает все микро- команды, а по второму - только результат дешифрации. кода операции микрокоманды.Предлагаемое устройство функционирует следующим образом.На вход устройства поступает адрес микропрограммы и управляющий сигнал "Прием адреса". Адресом микропрограммы является код операциикоманды, которая выполняется поданной микропрограмме. Адрес поступает на вход БПОМК. С выхода блока 1адрес подается в БПОМК. Считанная по5 данному дресу информация поступаетв РМК. Разрешение приема информации в РМК происходит по задержанному сигналу "Прием адреса".В первой ячейке, соответствующей0 каждой микропрограмме; хранится немикрокоманда, а код микропрограмм,который определяет последовательность микрокоманд, выполняемых поданной микропрограмме.15 В конце выполнения каждой микропрограммы триггер коммутатора 7 устанавливается в единичное состояние.. Поэтому код микропрограммы из РМКчерез коммутатор 7 поступает в регистр 9. Задержанным на элементе 4сигналом яПрием адреса" триггер коммутатора 8 устанавливается в нулевое состояние,После элемента 4 сигнал фПрием адреса" поступает также на счетныйвход БПОМК и на второй вход ключа.В БПОМК образуется адрес первоймикрокоманды микропрограммы, которая считывается из БПОМК в РМК. Сигнал на выходе ключа проходит через элемент 4 и управляет приемом в РМК, а также является сигналом "+1 ф для БПОМК.Так как триггер коммутатора 7 в нулевом состоянии, то микрокоманда из РМК через него поступает на вход ДК. Микрокоманда состоит из кода операции, адресной части и признака. Признак в ДК не поступает, он выдается по управляющему выходу РМК. У всех микрокоманд, кроме последней и кода микропрограммы, значение признака нулевое. В последней микрокоманде микропрограммы значение признака единичное. Поэтому после считывания последней микрокоманды происходит установка в единичное состояние триггера коммутатора 7 и сброс БПОМК и блока 10. После сброса БПОМК он не реагирует наРабота блока 10 происходит следующим образом.Код первой микрокоманды, определенный в ДК, сравнивается с кодом разрядов 18 кода микропрограмм. В случае совпадения на выходе формируется единичный сигнал, Таким же образом происходит сравнение кодов остальных микрокоманд.На вход схеж поступают сигналы, Выходным сигналом блока 10 является сигнал "0", разрешающий выдачу информации из блока 11., В состав блока 11 входит также линия задержки (ие показана) через которую проходит сигнал Сбросф. Если коды пер вой микрокоманды из ДК н регистра 9совпали, то в "+1 ф устанавливаетсяпервый триггер 13. По последующиммикроксмандам .устанавливается второй триггер 13 и т.д. В случае несовпадения кодов в блоке 10 очередной сигнал не вырабатывается и запрещается выдача информации иэ коммутатора 12. Таким образом, предлагаемое устройство позволяет осуществить контроль порядка следования микрокоманд. в микропрограмме и за счет этого повысить надежность устройства микро программного управления ЭВИ.1068937 Составитель Л, Логацевактор Н. Рогулич ТехредЛ,Пилипенко К Муски Подписно лиал ППП "Патентф, г. Ужгород, ул, Проектная, 4 1473/45 Тирак 703ВНИИПИ Государственногпо делам изобретений 113035, Москва, Я, Ра комитета СССР открытий скаЯ нзб, де 4/

СмотретьЗаявка

3426706, 21.04.1982

ЛЕНИНГРАДСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. ЛЕНСОВЕТА

СЫПЧЕНКО РУСЛАН ПАВЛОВИЧ, НИКИТИН ВЛАДИМИР БОРИСОВИЧ, ГЛУШАНКОВ ЕВГЕНИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.01.1984

Код ссылки

<a href="https://patents.su/5-1068937-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Генератор случайного процесса

Следующий патент: Микропрограммное устройство для управления каналами эвм

Случайный патент: Питатель к конусному молотильному аппарату