Устройство для моделирования систем обработки данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

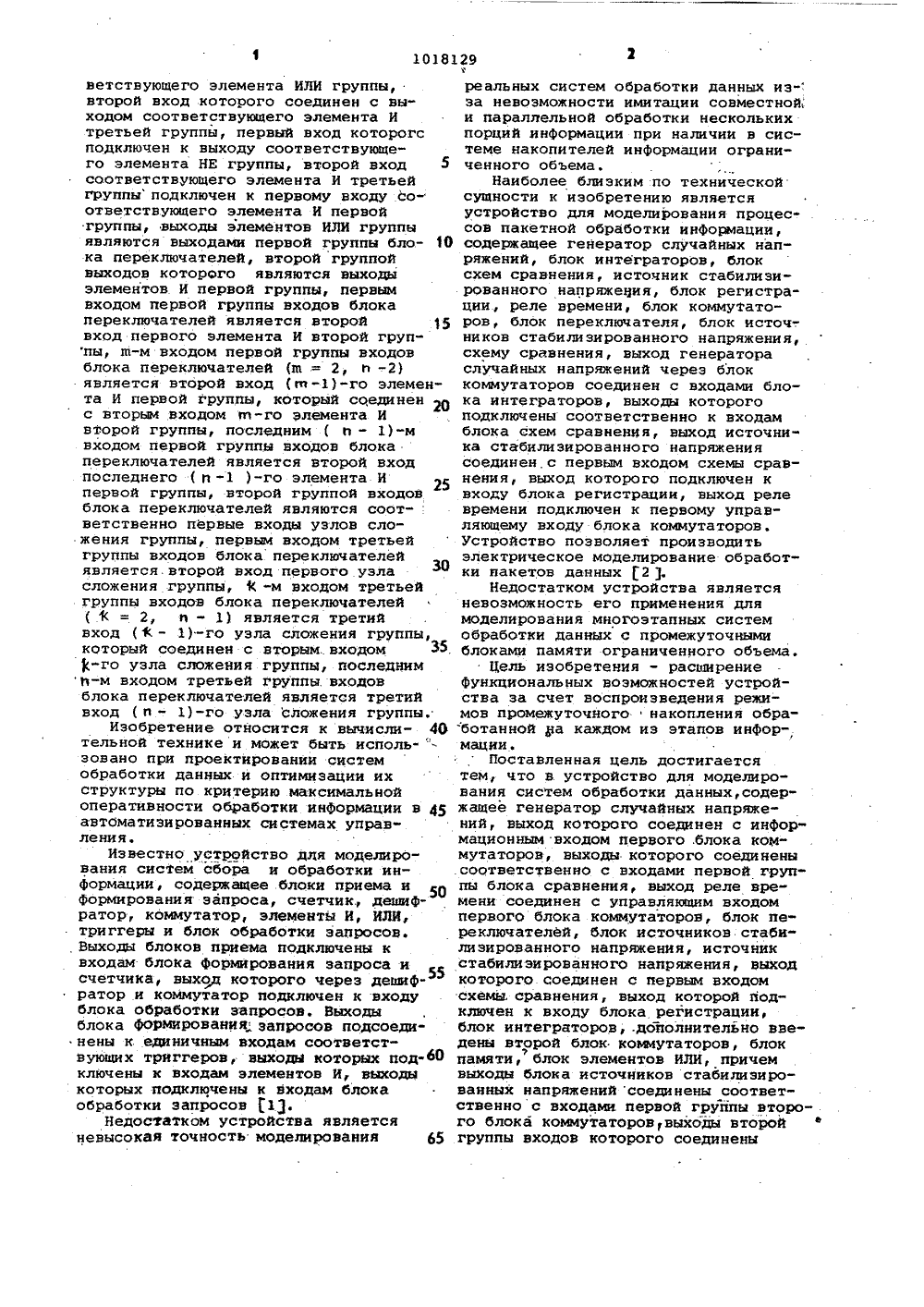

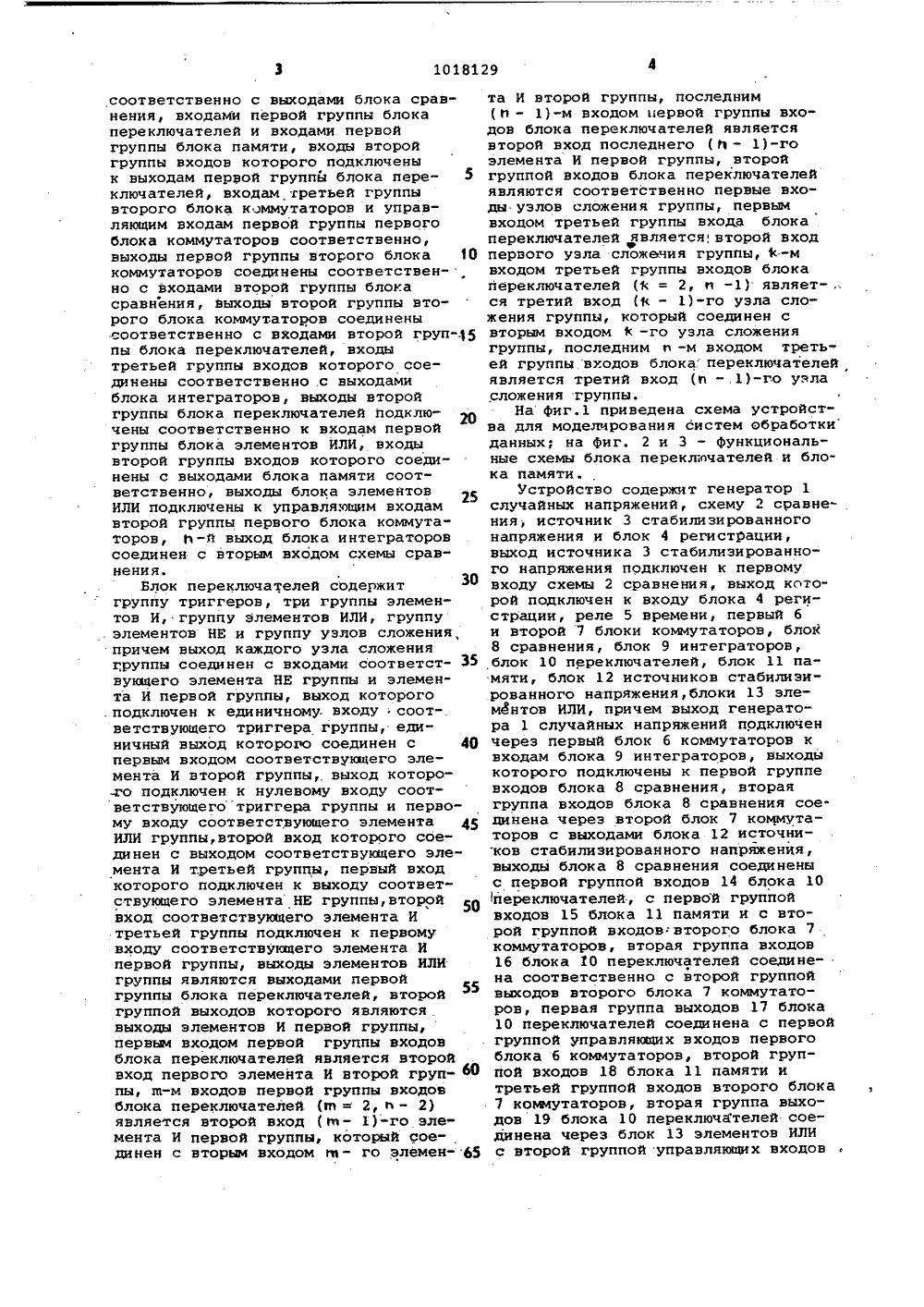

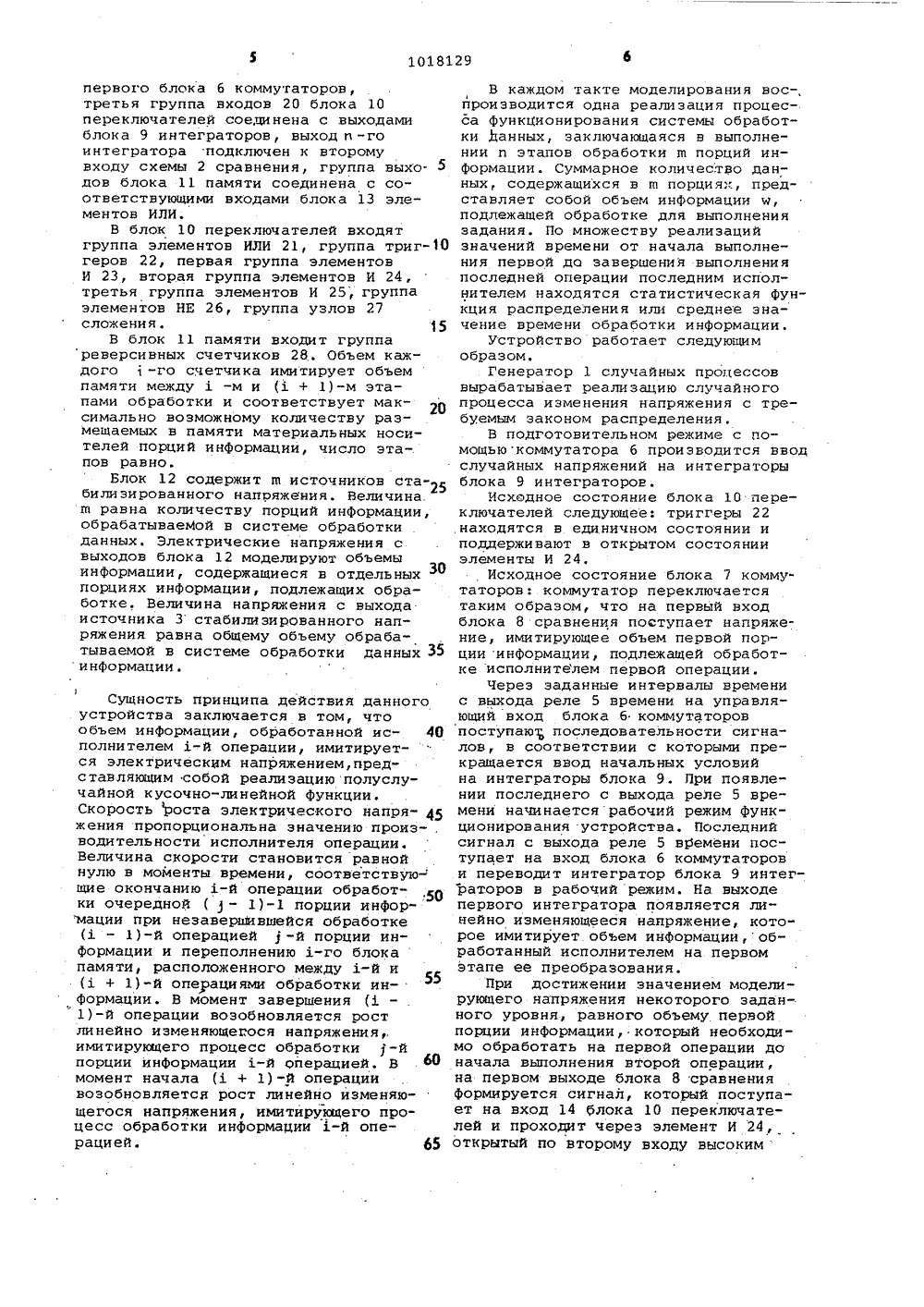

СОЮЗ СОВЕТСКИХасиаааисюиРЕСПУБЛИК 67 48 САЙКЕ Б ЬСТВУ Ленина ио Знаменинодорожно блок выхо : кома ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТШИЙ И ОТКРЫТИЙ(71) Московский орденаордена Трудового Красногинститут инженеров жеиез готранспорта(56) 2. Авторскоесвидетельство СССРВ 631925, кл. 6 06 Р 15/20, 1975,2. Авторское свидетельство СССРпо заявке 9 3305662/24,.кл.кл. 6 06 О 7/48, 1981 (прототип).(54)(57)1 УСТРОЙСТВО ДЛЯ МОДЕЛИРОВ 3 НИЯ СИСТЕМ ОБРАБОТКИ ДАННЫХ, содержащее генератор случайных напряжеакй, выход которого соединен с ин- .Формационным входом первого блокакоммутаторов, выходы которого соединены соответственно с аходамк первой Группы блока сравнения, выходреле времени соединен с управляющимвходом первого блока коммутаторов,блок переключателей,. блок источниковстабилизированного напряжения, источникстабилизированного напряже"ниа, выход которого соедйнен с первьж входом схемы сравнения, выходкоторой подключен к аХоду блока регистрации, блок ийтеграторов,. о т.л и ч а ю щ е е с я тем, что, сцелью расширения Функциональных воэмэжностей за счет воспроизведения рв-.,жимоа промежуточного йакопления об-работанной на каждом из этапов инФормации, оно дополнительно содержит второй блок комыутаторов, блокпамяти, блок элементов ИЛИ, причемвыходы блока источников стабилизированных напряжений соединены соответственно с входами первой группывторого блока коммутаторов, входывторой группы входов которого соединены соответственно с выходами блока 0.1018129 сравнения, входами первой группы блока переключателей и входами первой группы блока памяти, входы второй группы которого подключены к выходам первой группы блока переключателей, входам третьей группы второго блока коммутаторов и управляющим входам первой группы первого а коммутаторов соответственно, ды первой группы второго блока утаторов соединены соответственно с входами второй группы блока сравнения, выходы второй группы второго блока коммутаторов соединены соответственно с входами второй группы блока переключателей, входы третьей группы входов которого сое-,аинены соответственно с выходами блока интеграторов, выходы второй группы блока переключателей подключены соответственно к входам первой группы блока элементов ИЛИ, входы второй группы входов которого сое- р динены с выходамк блока памяти соответственно, выходы блока элементов ИЛИ подключены х управляющим входам второй группы первого блока коммутаторов, и-й выход блока интеграторов соединен с вторым входом схемы сравнения.2, Устройство по п. 1, о т л и % а ю щ е е с я тем, что блок переключателей содержит группу триггеров, три группы элементов И, группу элементов ИЛИ, группу элементов НЕ и группу узлов сложения, причем выход каждого узла сложения группы соединен с входамк соответствующего элемента НЕ группы к элемента И первой группы, выход которого подключен к единичному входу соответстаукщеготриггера группы, единичный выход кОтоцого соединен с первым входомсоответствующего элемента И второй группы, выход которого подключен к нулевому входу соответствующего триггера группы и первому входусоот 10181 ветствующего элемента ИЛИ группы, второй вход которого соединен с выходом соответствующего элемента И третьей группы, первый вход которогс подключен к выходу соответствующего элемента НЕ группы, второй вход 5 соответствующего элемента И третьей группыподключен к первому входу соответствующего элемента И первой группы, выходы элемЕнтов ИЛИ группы являются выходами первой группы бло" 10 ка переключателей, второй группой выходов которого являются выходы элементов И первой группы, первым входом первой группы входов блока переключателей является второй )5 вход первого элемента И второй группы, в-м входом первой группы входов блока переключателей (щ = 2, ь -2) является второй вход (п -1)-го элемента И первой группы, который соединен 2 О с вторым входом п 1-го Элемента И второй группы, последним ( и - 1)-м входом первой группы входов блока переключателей является второй вход последнего ( и -1 )"го элемента И первой группы, второй группой входов блока переключателей являются соответственно первые входы узлов сложения группы, первым входом третьей группы входов блока переключателей является. второй вход первого. узла сложения группы, М -м входом третьей группы входов блока переключателей (= 2, п - 1) является третий вход ( Ф - 1)-го узла сложения группы, который соединен с вторимвходом З 5 -го узла сложения группы, последним ь-м входом третьей группы. входов блока переключателей является третий вход ( и - 1)-го узла сложения группы.Изобретение относятся к вычисли тельной технике и может быть использовано при проектировании систем обработки данных и оптимизации их структуры по критерию максимальной оперативности обработки информации в 45 автоматизированных системах управления.Известно устройство для моделирования систем сбора и обработки инФормации, содержащее блоки приема и Формирования запроса, счетчик., дешифратор, коммутатор, элементы И, ИЛИ триггеры и блок обработки запросов. Выходы блоков приема подключены к входам блока Формирования запроса и счетчика, выход которого через дещифратор и коммутатор подключен к входу блока обработки запросов, Выходы блока ФОРмиРования запросов подсоединены к. единичным входам соответствующих триггеров, выходы которых подО ключены к входам элементов И, выходЫ которых подключены к входам блока обработки запросов ) 1.Недостатком устройства является невысокая точность моделирования 29Ъреальных систем обработки данных из-" за невозможности имитации совместной, и параллельной обработки нескольких порций информации при наличии в системе накопителей информации ограниченного объема.Наиболее близким:по технической сущности к изобретению является устройство для моделирования процессов пакетной обработки информации, содержащее генератор случайных напряжений, блок интеграторов, блок схем сравнения, источник стабилизированного напряжения, блок регистрации., реле времени, блок коммутато" ров, блок переключателя, блок источ-. ников стабилизированного напряжения, схему сравнения, выход генератора случайных напряжений через блок коммутаторов соединен с входами блока интеграторов, выходы которого подключены соответственно к входам блока схем сравнения, выход источника стабилизированного напряжения соединен с первым входом схемы сравнения, выход которого подключен к входу блока регистрации, выход реле времени подключен к первому управляющему входу блока коммутаторов. Устройство позволяет производить электрическое моделирование обработки пакетов данных 2 .Недостатком устройства является невозможность его применения для моделирования многоэтапных систем обработки данных с промежуточными блоками памяти ограниченного объема.Цель изобретения - расщирение Функциональных возможностей устройства за счет воспроизведения режимов промежуточного накопления обработанной на каждом из этапов информацииПоставленная цель достигается тем, что в устройство для моделирования систем обработки данных,содержащее генератор случайных напряжений, выход которого соединен с информационным входом первого .блока коммутаторов, выходы которого соединены соответственно с входами первой группы блока сравнения, выход реле времени соединен с управляющим входом первого блока коыаутаторов, блок переключателей, блок источников стабилизированного напряжения, источник стабилизированного напряжения, выход которого соединен с первым входом схемы сравнения, выход которой подключен к входу блока регистрации, блок интеграторов, .дополнительно введены второй блок коммутаторов, блок памяти, блок элементов ИЛИ, причем выходы блока источников стабилизированных напряжений соединены соответственно с входами первой группы второго блока коммутаторов, выходы второй группы входов которого соединенысоответственно с выходами блока сравнения, входами первой группы блока переключателей и входами первой группы блока памяти, входы второй группы входов которого подключены к выходам первой группы блока пере ключателей, входам третьей группы второго блока коммутаторов и управляющим входам первой группы первого блока коммутаторов соответственно, выходы первой группы второго блока 10 коммутаторов соецинены соответственно с входами второй группы блока сравнения, выходы второй группы второго блока коммутаторов соединены .соответственно с входами второй груп"45 пы блока переключателей, входы третьей группы входов которого соединены соответственно с выходами блока интеграторов, выходы второй группы блока переключателей подключены соответственно к входам первой группы блока элементов ИЛИ, входы второй группы входов которого соединены с выходами блока памяти соответственно, выходы блока элементов ИЛИ подключены к управляющим входам второй группы первого блока коммутаторов, Ь-й выход блока интеграторов соединен с вторым входом схемы срав" нения.Блок переключателей сЬдержит группу триггеров, три группы элементов И, группу элементов ИЛИ, группу . элементов НЕ и группу узлов сложения, причем выход каждого узла сложения группы соединен с входами соответст вукщего элемента НЕ группы и элемента И первой группы, выход которого .подключен к единичному, входу соответствующего триггера группы, единичный выход которого соединен с 40 первым входом соответствующего элемента И второй группы, выход которо-го подключен к нулевому входу соответствующего триггера группы и первому входу соответствующего элемента 45 ИЛИ группы, второй вход которого соединен с выходом соответствукщего элемента И третьей группы, первый вход которого подключен к выходу соответствующего элемента НЕ группы, второй вход соответствующего элемента И третьей группы подключен к первому входу соответствующего элемента И первой группы, выходы элементов ИЛИ группы являются выходами первой группы блока переключателей, второй группой выходов которого являются выходы элементов И первой группы, первым входом первой группы входов блока переключателей является второй вход первого элемента И второй груп ф пы, щ-м входов первой группы входов блока переключателей (е = 2, ь - 2) является второй вход (в - 1)-го элемента И первой группы, который сое" динен с вторым входом е- го элемен та И второй группы, последним ( п - 1)-м входом первой группы входов блока переключателей является второй вход последнего ( И - 1)-го элемента И первой группы, второй группой входов блока переключателей являются соответственно первые входы узлов сложения группы, первым входом третьей группы входа блока переключателей является, второй входэпервого узла сложечия группы, В -м входом третьей группы входов блока переключателей (Я = 2, и -1) являет-,. ся третий вход (й - 1)-го узла сло" жения группы, который соединен с вторым входом 1 -го узла сложения группы, последним о -м входом третьей группы входов блока.переключателей является третий вход (п в .1)-го узла сложения группы.На фиг.1 приведена схема устройства для моделчрования систем обработки данных; на фиг. 2 и 3 - функциональные схемы блока переключателей и блока памятиУстройство содержит генератор 1 случайных напряжений, схему 2 сравнения, источник 3 стабилизированного напряжения и блок 4 регистРации, выход источника 3 стабилизированного напряжения подключен к первому входу схемы 2 сравнения, выход которой подключен к входу блока 4 регистрации, реле 5 времени, первый 6 и второй 7 блоки коммутаторов, блок 8 сравнения, блок 9 интеграторов, блок 10 переключателей, блок 11 памяти, блок 12 источников стабилизированного напряжения, блоки 13 элементов ИЛИ, причем выход генератора 1 случайных напряжений подключен через первый блок 6 коммутаторов к входам блока 9 интеграторов, выходы которого подключены к первой группе входов блока 8 сравнения, вторая группа входов блока 8 сравнения сое" динена через второй блок 7 коммутаторов с выходами блока 12 источников стабилизированного напряжения, выходы блока 8 сравнения соединены с первой группой входов 14 блока 10 переключателей, с первой группой входов 15 блока 11 памяти и с второй группой входов:второго блока 7 коммутаторов, вторая группа входов 16 блока 10 переключателей соедине" на соответственно с второй группой выходов второго блока 7 коммутаторов, первая группа выходов 17 блока 10 переключателей соединена с первой группой управляющих входов первого блока б коммутаторов, второй группой входов 18 блока 11 памяти и третьей группой входов второго блока 7 коммутаторов, вторая группа выходов 19 блока 10 переключателей соединена через блок 13 элементов ИЛИ с второй группой управляющих входовпервого блока б коммутаторов,третья группа входов 20 блока 10переключателей соединена с выходамиблока 9 интеграторов, выход п -гоинтегратора подключен к второмувходу схемы 2 сравнения, группа выхо. 5дов блока 11 памяти соединена с соответствующими входами блока 13 элементов ИЛИ.В блок 10 переключателей входятгруппа элементов ИЛИ 21, группа триггеров 22, первая группа элементовИ 23, вторая группа элементов И 24,третья группа элементов И 25, группаэлементов НЕ 26, группа узлов 27сложения. 15В блок 11 памяти входит группареверсивных счетчиков 28 Объем каждого-го счетчика имитирует объемпамяти между 1 -м и (1 + 1)-м этапами обработки и соответствует максимально возможному количеству размещаемых в памяти материальных носителей порций информации, число этапов равно.Блок 12 содержит щ источников ста билизированного напряжения. Величина.т равна количеству порций информации,обрабатываеМой в системе обработкиданных. Электрические напряжения свыходов блока 12 моделируют объемыинформации, содержащиеся в отдельных Зпорциях информации, подлежащих обработке. Величина напряжения с выходаисточника 3 стабилизированного напряжения равна общему объему обрабатываемой в системе обработки данных З 5информации. Сущность принципа действия данного устройства заключается в том, что объем информации, обработанной ис полнителем 1-й операции, имитируется электрическим напряжением, пред" ставляюшим собой реализацию полуслучайной кусочно-линейной функции.Скорость роста электрического напря жения пропорциональна значению произ- . водительности исполнителя операции. Величина скорости становится равной нулю в моменты времени, соответствую- щие окончанию 1-й операции обработки очередной ( ) - 1)-1 порции инфор" мации при незавершившейся обработке (1 - 1)-й операцией-й порции информации и переполнению 1-го блока памяти, расположенного между 1-й и (1 + 1)-й операциями обработки информации. В момент завершения (1 - .1)-й операции возобновляется рост линейно изменяющегося напряжения,.имитирующего процесс обработки 1 -й порции информации 1-й операцией. В 60 момент начала (1 + 1)-й операции возобновляется рост линейно изменяющегося напряжения, имитирующего процесс обработки информации д-й операцией. 65 В каждом такте моделирования вос-, производится одна реализация процесса функционирования системы обработки данных, заключающаяся в выполнении и этапов обработки ш порций информации. Суммарное количество данных, содержащихся в ш порциях, представляет собой объем информации ж, подлежащей обработке для выполнения задания. По множеству реализаций значений времени от начала выполнения первой до завершения выполнения последней операции последним исполнителем находятся статистическая функция распределения или среднее значение времени обработки информации,Устройство работает следующим образом.Генератор 1 случайных процессов вырабатывает реализацию случайногопроцесса изменения напряжения с требуемым законом распределения.В подготовительном режиме с помощью коммутатора б производится вводслучайных напряжений на интеграторыблока 9 интеграторов. Исходное состояние блока 10 переключателей следующее: триггеры 22находятся в единичном состоянии иподдерживают в открытом состоянииэлементы И 24,Исходное состояние блока 7 комму.таторов; коммутатор переключается таким образом, что на первый вход блока 8 сравнения поступает напряжение, имитирующее объем первой порции информации, подлежащей обработке исполнителем первой операции.Через заданные интервалы временис выхода реле 5 времени на управляющий вход блока б коммутаторов поступают, последовательности сигналов, в соответствии с которыми прекращается ввод начальных условий на интеграторы блока 9. При появлении последнего с выхода реле 5 времени начинается рабочий режим функционирования устройства. Последний сигнал с выхода реле 5 вемени поступает на вход блока б коммутаторови переводит интегратор блока 9 интеграторов в рабочий режим. На выходе первого интегратора появляется линейно изменяющееся напряжение, которое имитирует объем информации, обработанный исполнителем на первом этапе ее преобразования.При достижении значением моделирующего напряжения некоторого заданного уровня, равного объему первой порции информации, который необходимо обработать на первой операциИ до начала выполнения второй операции, на первом выходе блока 8 сравнения формируется сигнал, который поступает на вход 14 блока 10 переключателей и проходит через элемент И 24, открытый по второму входу высокимнапряжением с единичного выхода триггера 22. На выходе 17 блока 10 переключателей появляется сигнал начала работы второго интегратора. При этомтриггер 22 блока 10 переключателейсбрасывается. На выходе интегратора9 блока 9 интеграторов появляетсялйнейно изменяющееся напряжение,моделирующее объем информации, обработанный, исполнителем на втором этапе ее преобразования. При этом интегратор 9 блока 9 интеграторов продол 3жает работу.Сигнал с первого выхода блока 8 сравнения, имитирующий окончание исполнителем первой операции обработки .первой порции информации, переключает коммутатор 7 таким образом, что на первый вход блока 8 сравнения от него поступает напряжение,моделирующее суммарный объем (ы,+ ы)0первой и второй порций информацйи,обрабатываемых на первом этапе пре"образования информации .Кроме того, сигнал с первого выхода блоха 8 сравнения поступает на вход .15 блока 1,1 памяти, являющийся суммйрующнм входом счетчика 28., В счетчик 28 заносится единица, что имитирует.объем информации (в порциях инФормации), хранящейся в нако-: пителе между первым и вторым этапами ее преобразования.Сигнал с выхода 17 блока 10 переключателей, имитируюший начало обработки второй операцией первой порции инФормации переводит коммутатор 35 7 таким образом, что на, вход 16 блока 10 переключателей поступает. напряжение ж, имитирующее объем второй порций информации, подлежащей обработке на первом этапе ее 40 преобразования, при этом на второй вход блока 8 сравнения поступаетнапряжение, имитирующее объем первой порции информации, подлежащей обработке на втором этапе ее преобразования. Кроме того, сигнал с выхода 17 блока 10 переключателей поступает на вычитающий вход счетчика 28 блока 11 памяти В счетчике 28. ус-.танавливается О, что соответствует отсутствию, информации, хранящейся в накопителе между 1 и 2-й операциями.Появление на выходах блока Э одновременно двух линейно изменяющихся напряжений имитирует процесс совместного выполнения двух этапов технологи ческого процесса обработки информации в системе обработки данных, при-. чем на первом этапе обрабатывается вторая порция информации, а на втором - первая. 60На входы узла 27 сложения блока 10 переключателей подаются напряже" ния с выходов интеграторов Э и 9блока 9 интеграторов и от блока 12 источников напряжения через коммута тор 7 напряжения, моделирующие объем ю 2 втоРой порции информации, подлежащей обработке в системе обработки данных.Напряжение с выхода узла 27 сложения блока 10 переключателей представляет собой разность значений суммы напряжения ю , напряжения с выхода интегратора 9 блока 9 интег 2раторов и напряжения с выхода интегратора 9 блока 9 интеграторов. Эта разность напряжений положительна, пока объем информации, ожидающий начала выполнения второй операции, не превышает значения ыПоложительное напряжение с выхода узла 27 сложения поддерживает в открытом состоянии элемент И 23 н, пройдя через элемент НЕ 26, запи,рает элемент И 25 блока 10 переключателей.В дальнейшем процесс. Функционирования устройства зависит от последовательности поступления сигналов окончания отдельных операций обработки различных порций информации.Если сигнал (с второго выхода блока 8 сравнения) окончания второй операцией обработкипервой порции информации появляется раньше сигнала (с первого выхода блока 8 сравнения) окончания первой оиерацией обработки второй порции информации, то он проходит через элемент И,23 блока. 10 переключателей, открытый по второму входу положительным напряжением с .выхода узла 27 сложения. При этом триггер 22 переводится в единичное состояние, а на выходе 19 блока 10 переключателей форми.- руется сигнал Конец работы интегратора 9 ф. Интегратор 92 блока 9 интеграторов прекращает формирование линейно изменяющегося напряжения. Прекращение работы интегратора 92 соответствует прекращению выполнения второй операции по окончании обработки первой порции информации при незавершившейся первой операцией . обработки второй порции информации.Сигнал окончания второй операцией обработки первой порции информации с второго выхода блока 8 сравнения проходит на суммирующий вход счетчика 282 блока 11 памяти и записывает в нем единицу. Кроме того, он проходит через элемент И 242 блока 10 переключателей, открытый по второму входу высоким напряжением с единичного выхода триггера 22. На выходе 17 блока 10 переключателей появляется сигнал начала работы 3-го интегратора. При этом триггер 22 блока 10 переключателей сбрасывается. Сигнал с выхода 17 блока 10 переключателей вычитает единицу из .содержимого счетчика 28 блока 11 памяти. Содержимое счетчика 28 имитирует объем инфор"мации (в материальных носителях пор"ций инФормации), хранящийся в накопиСигнал с выхода 17 блока 10 пе 1реключателей (имитирующий начало обработки второй операцией второйпоРции информации) переключает комму татор 7 таким образом, что на вход16 блока 10 переключателей поступает напряжение, соответствующее объему ы третьей порции информации,подлежащей обработке на втором этапеее преобразования, при этом на третий вход блока 8 сравнения поступаетнапряжение ы, имитирующее объемпервой порции информации, подлежащейобработке на третьем этапе ее преобразования,Если сигнал окончания первой операцией обработки второй порции информации (с первого выхода блока 8 сравнения) появляется раньше сигнала окончания второй операции обработки первой порции информации (с второго выхода блока 8 сравнения), то он не проходит через элемент И 24 , закры" тый по второму входу низким напряже 60 65 теле перед началом выполнения на третьем этапе обработки.Сигнал окончания обработки первой операцией второй порции информации, пришедшей после сигнала окончания второй операцией обработки первой порции информации с первого выхода блока 8 сравнения, прибавляет к содержимому счетчика 28 блока 11 памя-(01ти единицу. Кроме того, пройдя через элемент И 24, открытый по второму входу высоким напряжением с единичного выхода триггера 22,формирует на выходе 17 блока 10 йереключате лей сигнал Начало работы интегратора 9. В интеграторе 92 блока 9 интеграторов возобновляется рабочий режим. Сигнал с выхода 17 блока 10 переключателей вычитает единицу из, 20 содержимого счетчика 28 блока 11 памяти.Сигнал с второго выхода блока 8 сравнения (имитирующий окончание обработки первой порции инфоРмации 25 исполнителем второй операции) переключает коммутатор блока 7 таким образом, что от него на второй вход блока 8 сравнения поступает напряжение, моделирующее суммарный объем (ч + ю ) первой и второй порций информации, обрабатываемых на втором этапе преобразования информации, Кроме того, сигнал с второго выхода блока 8 сравнения поступает на суммируощий вход счетчика 282 блока 11 памяти. В счетчике прибавляется единица. Содержимое счетчика имитирует объем информации (в порциях), хранящийся в накопителе между вторым и третьим этапами ее обработки. 40 нием с единичного выхода триггера 22 блока 10 переключателейСигнал окончания второй операцией обработки первой информации (с второго выхода блока 8 схем сравнения) не проходит через элемент И 23-, закрырый по второму входу низким напряжением с выхода узла 27 сложения бло- . ка 10 переключателей. При этом сигнал Конец работы интегратора 92 на выходе 19 блока 10 переключателей не появляется. Однако сигнал " второго выхода блока 8 сравнения проходит . через элемент И 25, открытый по второму входу высоким напряжением с выхода элемента НЕ 26, на вход которого поступает низкое напряжение с выхода узла 27 сложения блОка 10 переключателей и проходит через элемент ИЛИ 21. На выходе 17 блока 10 переключателей появляется сигнал Начало работы интегратора 92. Он подтверждает рабочий режим интегратора 92 блока 9 интеграторов и производйт в схеме описанные действия,Сигналы с первого выхода блока 8 сравнения прибавляют к содержимому счетчика 28 единицу. При значительной производительности исполнителя первой операции может произойти переполнение счетчика 28 блока 11 памяти, что имитирует переполнение блока памяти между первым и вторым этапами ее преобразования. Сигнал переполнения счетчика 28 с первого выхода блока 11 памяти поступает через блок 24 элементов ИЛИ на первый вход второй группы входов ком,мутатора 6 и прекращает рабочий режим интегратора 9 блока 9 интеграторов. Возобновление рабочего режима интегратора 9 происходит по сигналу, который появляется по сигналу Начало работы интегратора 9с выхода 17 блока 10 переключателей.2Аналогичным образом осуществляется дальнейшее функционирование устройства по переключению в рабочий режим всех интеграторов. При этом с помощью блока 10 переключателей имитируются события прекращения выполнения (1 + 1)-й операции по окончании обработки ( л - 1)-й порции информации при незавершившейся 1-й операции обработки ) "й порции информа ции (по сигналу с выхода 19, ); возобновления выполнения (1 + 1)-1 операции после завершения 1-й операцией обработки л-й порции информации (по сигналу с выхода 17); возобновление выполнения 1"й операции при частичном освобождении 1-го накопителя инфорьиции в связи с началом (1+1)-й операцией обработки очередной порции информации, взятой из накопителя (по сигналу с выхода 17).С помощью блока 11 памяти имитируется прекращение выполнения 1-й,1 (п - 1), операции при переполнении 1-,го накопителя информации.В конце концов иа выходе каждого из интеграторов появляется напряжение, предатавлякщее собой реализацию кусочно-линейной функции, имити рующей объем информации, обработанной на каждом из этапов ее лреобразозания Напряжение с выхода и блока 9 30 интеграторов, представляющее собой реализацию кусочно-линейной Функции, имитирующей объем информации, появляющейся на выходе системы обработки.данных, поступает на второй вход 15 схемы 2 сравнения, на первый вход которой с выхода источника 3 стаби-. лизированного напряжения подается напряжение, равное по величине объему инФормации, подлежащей обработке в системе обработки данных каждым исполнителем.При достижении линейно"изменяющимся напряжением, поступающим от блока 9, этого значения с выхода. схемы 2 сравнения поступает сигнал окончания обработки информации и фиксируется в блоке 4 регистрации.Устройство позволяет моделировать процессы совместной и параллельной обработки нескольких порций информации системой обработки данных при наличии в ней промежуточнык буферных каскадов памяти ограниченного объема. Благодаря этому возрастают достоверность и качество результатов моделирования реальных схем обработ.ки данных в АСУ.1018129 остав ехред ель Е. Фукалов. Пекарь . Корректор С. Шекм Закаэ 3546/ Тираж 70 босударственногелам иэобретениква, 3-35, Рауюс ю Фе ФЮ ю е е аЬю ю ю юрректная, 4 лиал ППП фПатентф, г. Мкгород л едактор Л, Алексеев ВНИИПИ по д 113035, МомвтеЮ откр ая на Подписное а СССРытий

СмотретьЗаявка

3379819, 11.01.1982

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

ДРУЖИНИН ГЕОРГИЙ ВАСИЛЬЕВИЧ, СЕРГЕЕВА ИРИНА ВАСИЛЬЕВНА, КРЫЛОВ ВЛАДИМИР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: данных, моделирования, систем

Опубликовано: 15.05.1983

Код ссылки

<a href="https://patents.su/8-1018129-ustrojjstvo-dlya-modelirovaniya-sistem-obrabotki-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования систем обработки данных</a>

Предыдущий патент: Параболический интерполятор

Следующий патент: Устройство для моделирования процессов движения поездов

Случайный патент: Устройство для образования рисунка на ткани