Устройство для умножения чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

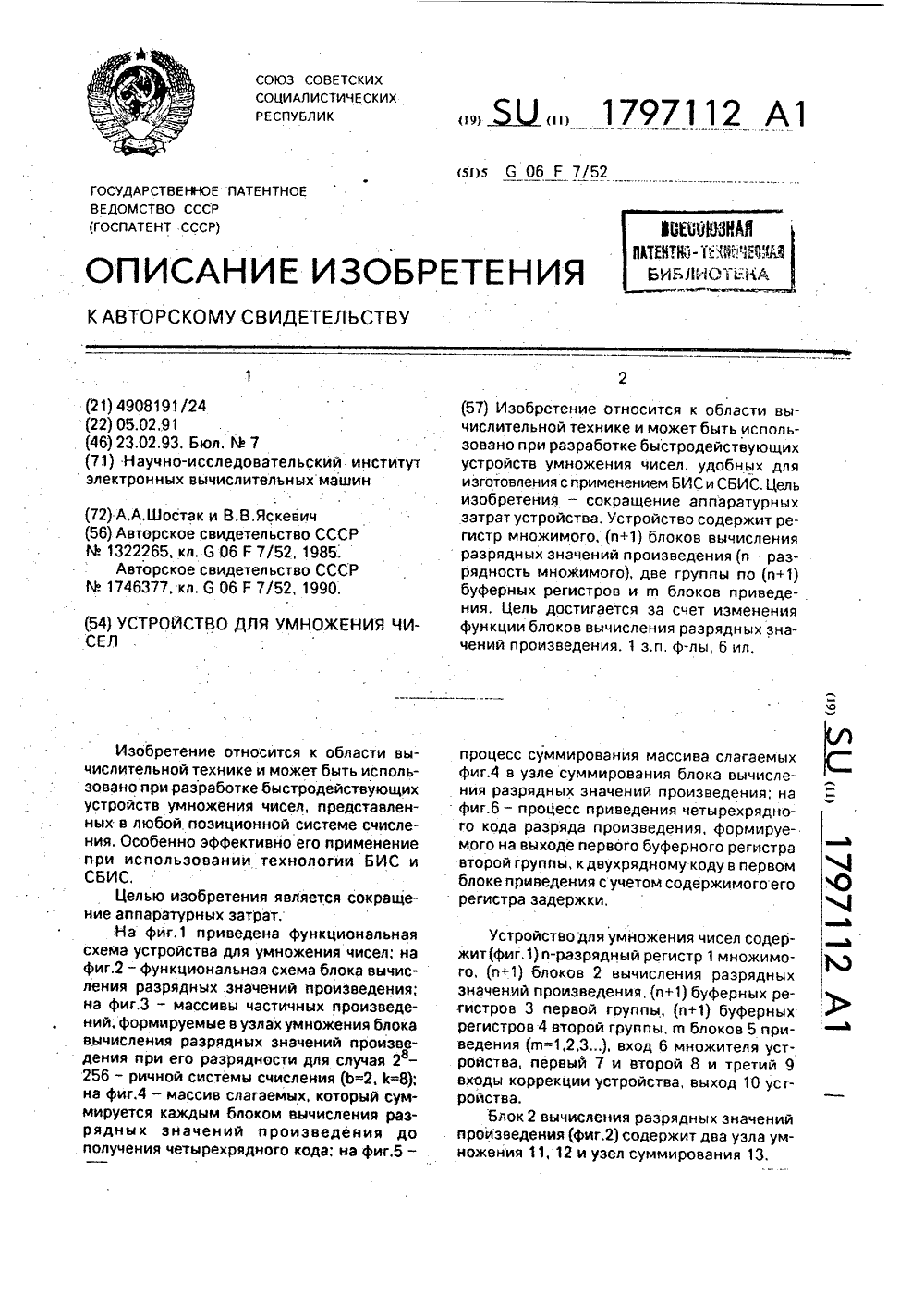

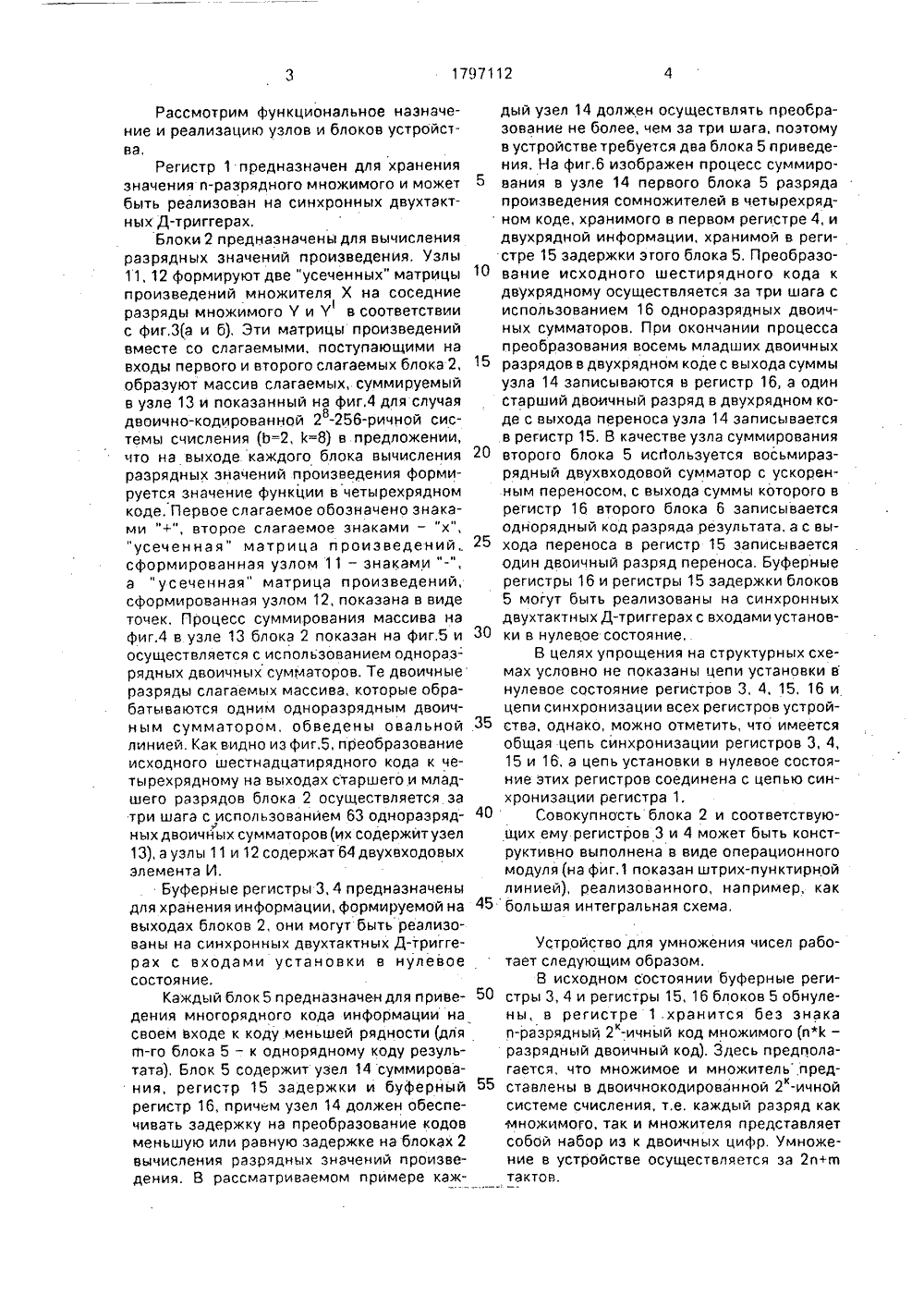

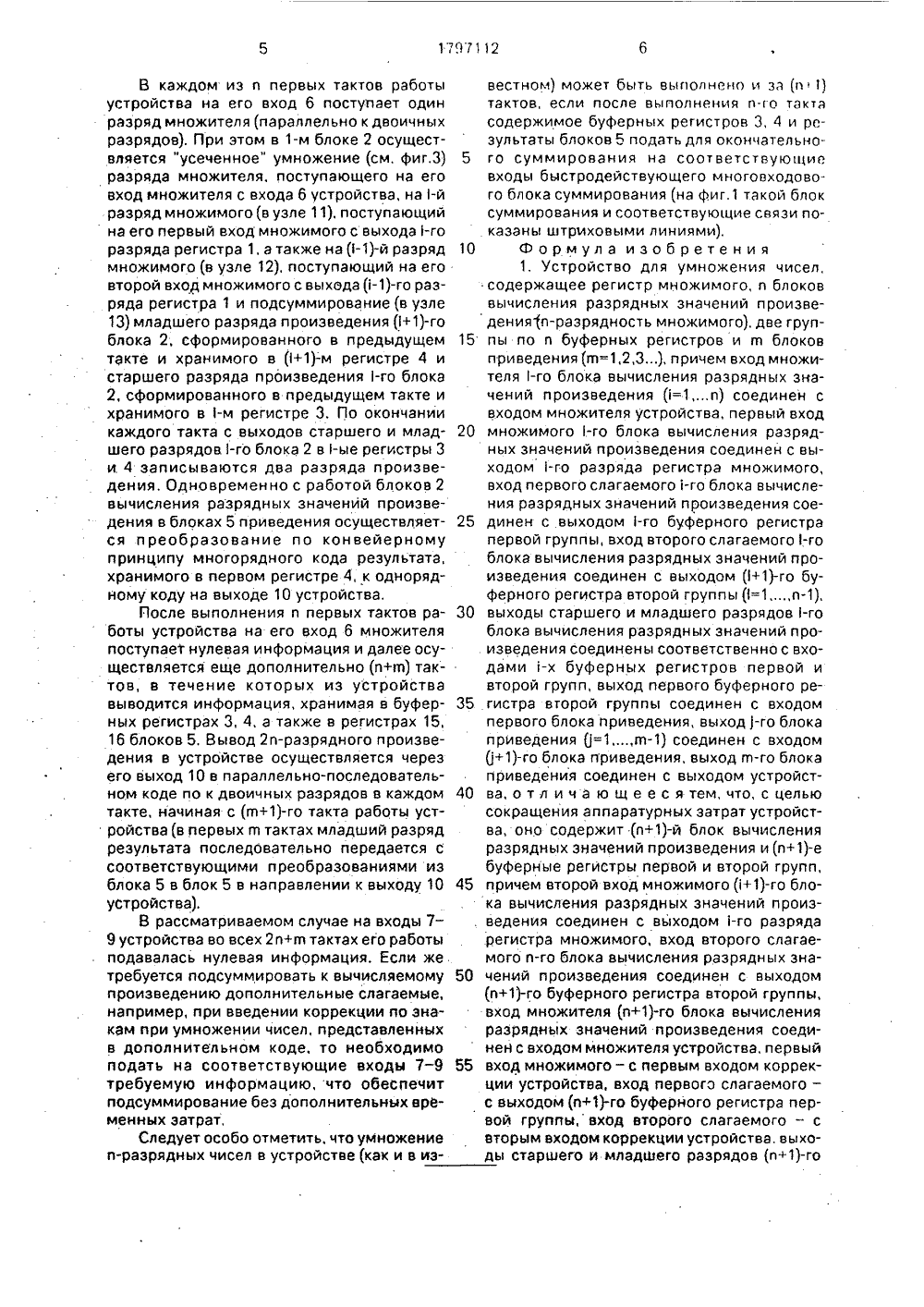

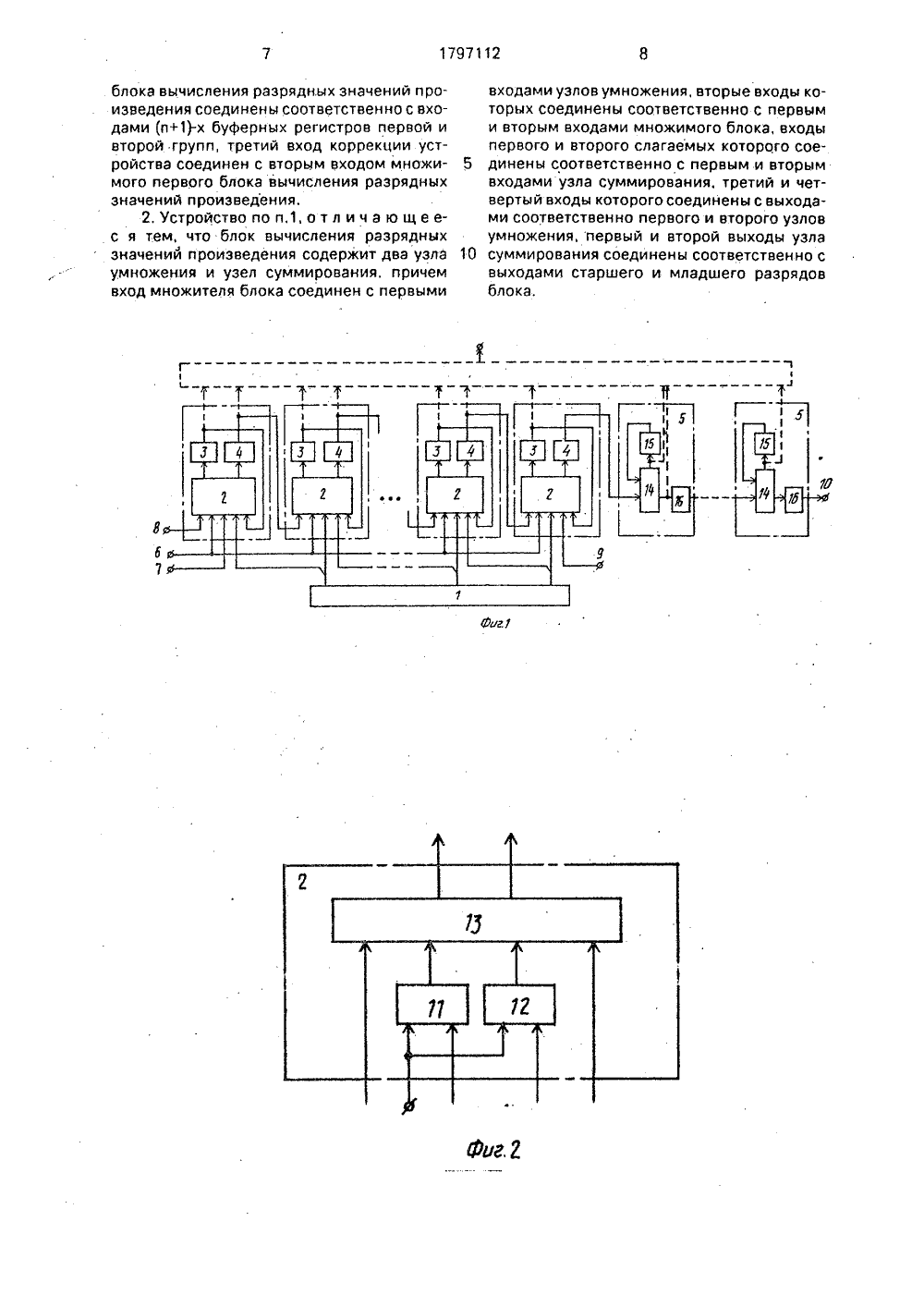

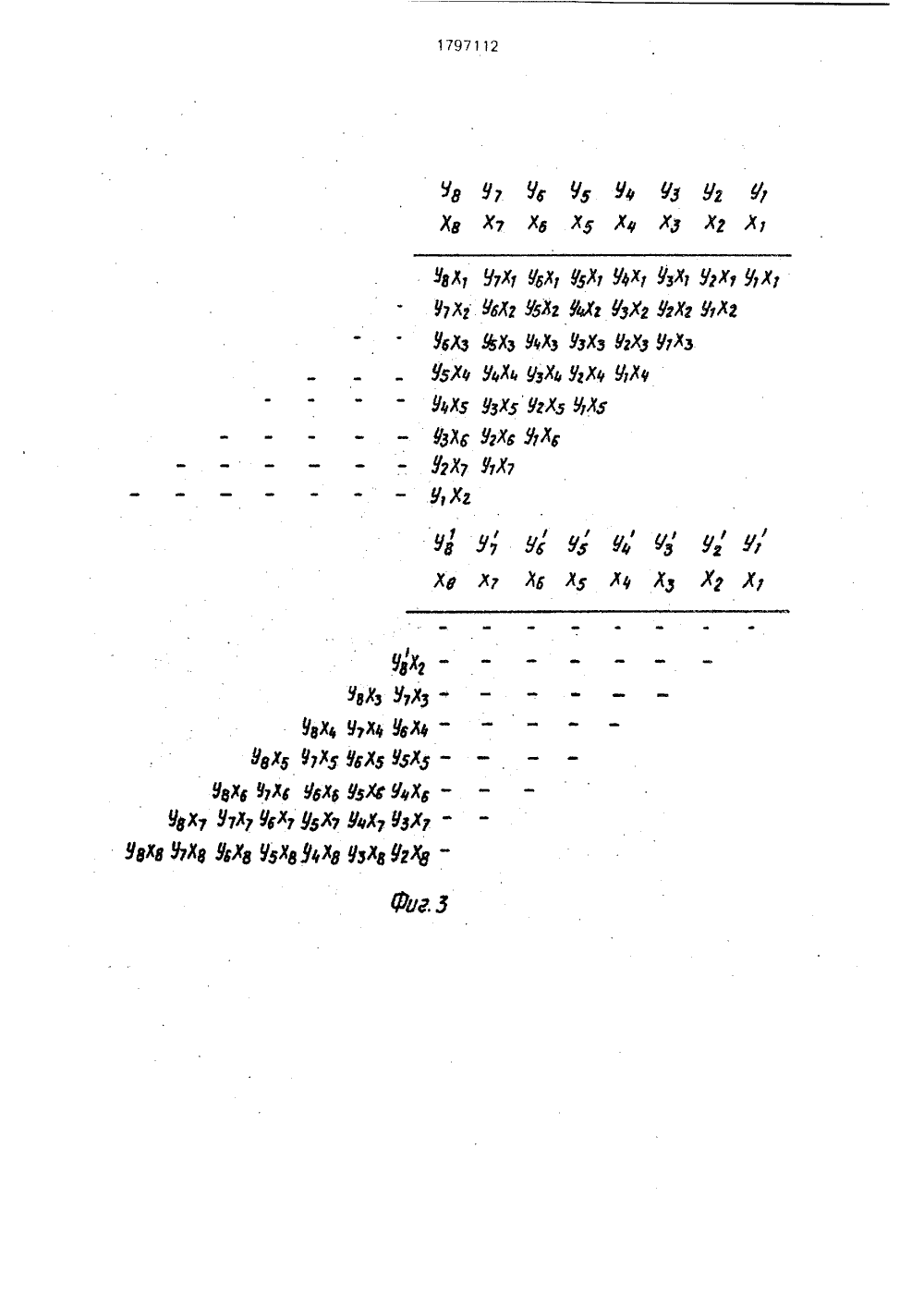

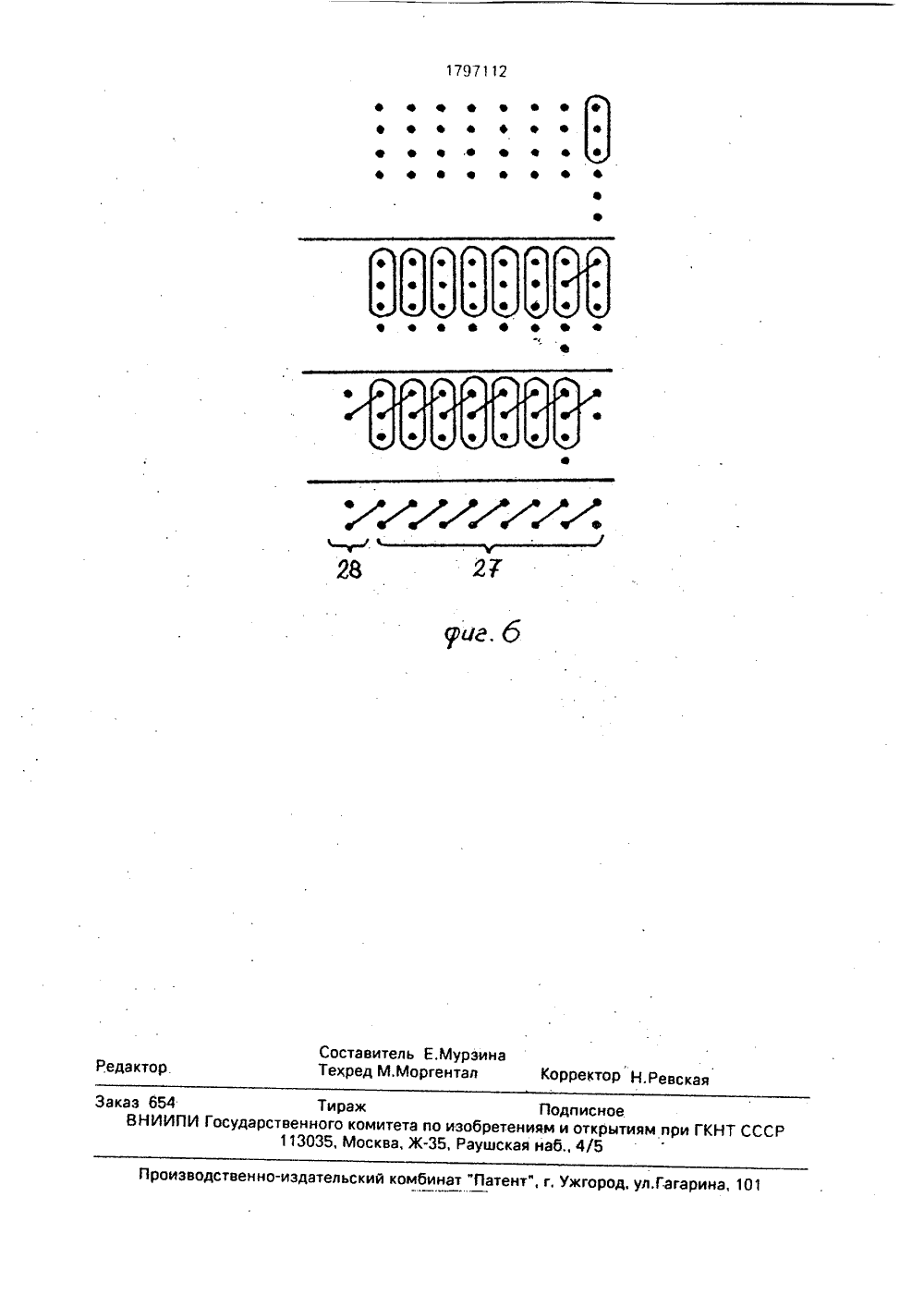

ЮЗ СОВЕТСКИХЦИАЛИСТИЧЕСКИСПУБЛИК 1797 9) .ъЖ. Р 7/52 ТЕНТНОЕ ГОСУДАРСТВЕННОЕ ВЕДОМСТВО СССР ГОСПАТЕНТ СССР РЕТЕН 2(71) Научно-исследовательский институтэлектронных вычислительных машин Изобретение относится к области в числительной технике и может быть испол зовано при разработке быстродействующ. устройств умножения чисел, представленных в любой позиционной системе счисления. Особенно эффективно его применение при использовании технологии БИС и СБИС.Целью изобретения является сокращение аппаратурных затрат,На фиг.1 приведена функциональная схема устройства для умножения чисел; на фиг.2 - функциональная схема блока вычисления разрядных значений произведения; на фиг,3 - массивы частичных произведений, формируемые в узлах умножения блока вычисления разрядных значений произведения при его разрядности для случая 2 -8 256 - ричной системы счисления (Ь=2, 1=8); на фиг.4 - массив слагаемых, который суммируется каждым блоком вычисления разрядных значений произведения до получения четырехрядного кода; на фиг.5 -(57) Изобретение относится к области вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения чисел, удобных для изготовления с применением БИС и СБИС. Цель изобретения - сокращение аппаратурнь 1 х затрат устройства, Устройство содержит регистр множимого, (и+1) блоков вычисления разрядных значений произведения (и - разрядность множимого), две группы по (и+1) буферных регистров и в блоков приведения. Цель достигается за счет изменения функции блоков вычисления разрядных значений произведения. 1 з,п, ф-лы, 6 ил,процесс суммирования массива слагаемых фиг.4 в узле суммирования блока вычисления разрядных значений произведения; на фиг.6 - процесс приведения четырехрядного кода разряда произведения, формируемого на выходе первого буферного регистра второй группы, к двухрядному коду в первом блоке приведения с учетом содержимого его регистра задержки. Устройстводля умножения чисел содержит(фиг,1) и-разрядный регистр 1 множимого, (и+1) блоков 2 вычисления разрядных значений произведения, (и+1) буферных регистров 3 первой гоуппы, (и+1) буферных регистров 4 второй группы, гп блоков 5 приведения (в=1,2,3), вход 6 множителя устройства, первый 7 и второй 8 и третий 9 входы коррекции устройства, выход 10 устройства.Блок 2 вычисления разрядных значений произведения (фиг.2) содержит два узла умножения 11, 12 и узел суммирования 13.Рассмотрим функциональное назначение и реализацию узлов и блоков устройства,Регистр 1 предназначен для хранениязначения и-разрядного множимого и может 5быть реализован на синхронных двухтактных Д-триггерах,Блоки 2 предназначены для вычисленияразрядных значений произведения, Узлы11, 12 формируют две "усеченных" матрицы 10произведений множителя Х на соседниеразряды множимого У и У в соответствии1с фиг.З(а и б), Эти матрицы произведенийвместе со слагаемыми, поступающими навходы первого и второго слагаемых блока 2, 15образуют массив слагаемых, суммируемыйв узле 13 и показанный на фиг,4 для случаядвоично-кодированной 2 -256-ричной системы счисления (Ь=2, 1=8) в предложении,что на выходе каждого блока вычисления 20разрядных значений произведения формируется значение функции в четырехрядномкоде, Первое слагаемое обозначено знаками "+", второе слагаемое знаками - "х","усеченная" матрица произведений 25сформированная узлом 11 - энаками "-",а "усеченная" матрица произведений,сформированная узлом 12, показана в видеточек. Процесс суммирования массива нафиг.4 в узле 13 блока 2 показан на фиг,5 и 30осуществляется с использованием однораз-рядных двоичных сумматоров. Те двоичныеразряды слагаемых массива, которые обрабатываются одним одноразрядным двоичнь 1 м сумматором, обведены овальной 35линией. Как видно иэ. фиг,5, преобразованиеисходного шестнадцатирядного кода к четырехрядному на выходах старшего и младшего разрядов блока 2 осуществляется затри шага с использованием 63 одноразряднь 1 х двоичных сумматоров (их содержит узел13), а узлы 11 и 12 содержат 64 двухвходовыхэлемента И.Буферные регистры 3,4 предназначеныдля хранения информации, формируемой на 45выходах блоков 2, они могут быть реализованы на синхронных двухтактных Д-триггерах с входами установки в нулевоесостояние.Каждый блок 5 предназначен для приведения многорядного кода информации насвоем входе к коду меньшей рядности (дляв-го блока 5 - к однорядному коду результата), Блок 5 содержит узел 14 суммирования, регистр 15 задержки и буферный 55регистр 16, причем узел 14 должен обеспечивать задержку на преобразование кодов меньшую или равную задержке на блоках 2вычисления разрядных значений произведения. В рассматриваемом примере каждый узел 14 должен осуществлять преобразование не более, чем за три шага, поэтому в устройстве требуется два блока 5 приведения. На фиг,б изображен процесс суммирования в узле 14 первого блока 5 разряда произведения сомножителей в четырехрядном коде, хранимого в первом регистре 4, и двухрядной информации, хранимой в регистре 15 задержки этого блока 5. Преобразование исходного шестирядного кода к двухрядному осуществляется за три шага с использованием 16 одноразрядных двоичных сумматоров, При окончании процесса преобразования восемь младших двоичных разрядов в двухрядном коде с выхода суммы узла 14 записываются а регистр 16, а один старший двоичный разряд в двухрядном коде с выхода переноса узла 14 записывается в регистр 15, В качестве узла суммирования второго блока 5 используется восьмиразрядный двухвходовой сумматор с ускоренным переносом, с выхода суммы которого в регистр 16 второго блока б записывается однорядный код разряда результата, а с выхода переноса в регистр 15 записывается один двоичный разряд переноса, Буферные регистры 16 и регистры 15 задержки блоков 5 могут быть реализованы на синхронных двухтактных Д-триггерах с входами установки в нулевое состояние.В целях упрощения на структурных схемах условно не показаны цепи установки в нулевое состояние регистров 3, 4, 15, 16 и цепи синхронизации всех регистров устройства, однако, можно отметить, что имеется общая цепь синхронизации регистров 3, 4, 15 и 16, а цепь установки в нулевое состояние этих регистров соединена с цепью синхронизации регистра 1,Совокупность блока 2 и соответствующих ему регистров 3 и 4 может быть конструктивно выполнена в виде операционного модуля (на фиг.1 показан штрих-пунктирной линией), реализованного, например, как большая интегральная схема. Устройство для умножения чисел работает следующим образом.В исходном состоянии буферные регистры 3, 4 и регистры 15, 16 блоков 5 обнулены, в регистре 1.хранится без знака р-разрядный 2"-ичный код множимого (пЕ - разрядный двоичный код), Здесь предполагается, что множимое и множитель представлены в двоичнокодированной 2"-ичной системе счисления, т,е. каждый разряд какмножимого, так и множителя представляетсобой набор из к двоичных цифр, Умножение е устройстве осуществляется эа 2 п+ттактов.10 15 20 25 30 35 40 45 50 55 В каждом из и первых тактов работы устройства на его вход 6 поступает один разряд множителя (параллельно к двоичных разрядов). При этом в 1-м блоке 2 осуществляется "усеченное" умножение (см. фиг.3) разряда множителя, поступающего нэ его вход множителя с входа 6 устройства, на 1-й разряд множимого (в узле 11), поступающий на его первый вход множимого с выхода 1-го разряда регистра 1, а также на (1-1)-й разряд множимого (в узле 12), поступающий на его второй вход множимого с выхода (1-1)-го разряда регистра 1 и подсуммирование (в узле 13) младшего разряда произведения (1+1)-го блока 2; сформированного в предыдущем такте и хранимого в (1+1)-м регистре 4 и старшего разряда произведения 1-го блока 2, сформированного в предыдущем такте и хранимого в 1-м регистре 3. По окончании каждого такта с выходов старшего и младшего разрядов 1-го блока 2 в 1-ые регистры 3 и 4 записываются два разряда произведения. Одновременно с работой блоков 2 вычисления разрядных значений произведения в блоках 5 приведения осуществляется преобразование по конвейерному принципу многорядного кода результата, хранимого в первом регистре 4, к однорядному коду на выходе 10 устройства,После выполнения и первых тактов работы устройства нэ его вход 6 множителя пОступаеТ нулевая информация и далее осуществляется еще дополнительно (и+ги) тактов, в течение которых из устройства выводится информация, хранимая в буферных регистрах 3, 4, а также в регистрах 15, 16 блоков 5. Вывод 2 и-разрядного произведения в устройстве осуществляется через его выход 10 в параллельно-последовательном коде по к двоичных разрядов в каждом такте, начиная с (гл+1)-го такта работы устройства (в первых и тактах младший разряд результата последовательно передается с соответствующими преобразованиями из блока 5 в блок 5 в направлении к выходу 10 устройства),В рассматриваемом случае на входы 7 - 9 устройства во всех 2 и+ги тактах его работы подавалась нулевая информация, Если же требуется подсуммировать к вычисляемому произведению дополнительные слагаемые, например, при введении коррекции по знакам при умножении чисел, представленных в дополнительном коде, то необходимо подать на соответствующие входы 7-9 требуемую информацию, что обеспечит подсуммирование без дополнительных временных затрат,Следует особо отметить, что умножение и-разрядных чисел в устройстве (как и в известном) может быть выполнено и за (и1) тактов, если после выполнения и-го такта содержимое буферных регистров 3, 4 и результаты блоков 5 подать для окончательного суммирования на соответствующие входы быстродействующего многовходового блока суммирования (на фиг,1 такой блок суммирования и соответствующие связи показаны штриховыми линиями). Формула изобретения 1, Устройство для умножения чисел, содержащее регистр множимого, и блоков вычисления разрядных значений произведениями-разрядность множимого), две группы по и буферных регистров и в блоков приведения (ги=1,2,3), причем вход множителя 1-го блока вычисления разрядных значений произведения (1=1,и) соединен с входом множителя устройства, первый вход множимого 1-го блока вычисления разрядных значений произведения соединен с выходом 1-го разряда регистра множимого, вход первого слагаемого 1-го блока вычисления разрядных значений произведения соединен с выходом 1-го буферного регистра первой группы, вход второго слагаемого 1-го блока вычисления разрядных значений произведения соединен с выходом (1+1)-го буферного регистра второй группы (1=1.и), выходы старшего и младшего разрядов 1-го блока вычисления разрядных значений произведения соединены соответственно с входами 1-х буферных регистров первой и второй групп, выход первого буферного регистра второй группы соединен с входом первого блока приведения, выход)-го блока приведения =1в) соединен с входом 0+1)-го блока приведения, выход п-го блока приведения соединен с выходом устройства, о т л и ч э ю щ е е с я тем, что, с целью сокращения аппаратурных затрат устройства, оно содержит (и+1)-й блок вычисления разрядных значений произведения и (и+1)-е буферные регистры первой и второй групп, причем второй вход множимого (1+1)-го блока вычисления разрядных значений произведения соединен с выходом 1-го разряда регистра множимого, вход второго слагаемого и-го блока вычисления разрядных значений произведения соединен с выходом (и+1)-го буферного регистра второй группы, вход множителя (и+1)-го блока вычисления разрядных значений произведения соединен с входом множителя устройства, первый вход множимого - с первым входом коррекции устройства, вход первого слагаемого - с выходом (и+1)-го буферного регистра первой группы,вход второго слагаемого - с вторым входом коррекции устройства, выходы старшего и младшего разрядов (и+1)-го1797112 Фиг 1 блока вычисления разрядн.ых значений произведения соединены соответственно с входами (и+1)-х буферных регистров первой и второй групп, третий вход коррекции устройства соединен с вторым входом множи мого первого блока вычисления разрядных значений произведения.2, Устройство по п,1, о т л и ч а ю щ е ес я тем, что блок вычисления разрядных значений произведения содержит два узла 10 умножения и узел суммирования. причем вход множителя блока соединен с первыми входами узлов умножения, вторые входы которых соединены соответственно с первым и вторым входами множимого блока, входы первого и второго слагаемых которого соединены соответственно с первым и вторым входами узла суммирования, третий и четвертый входы которого соединены с выходами соответственно первого и второго узлов умножения, первый и второй выходы узла суммирования соединены соответственно с выходами старшего и младшего разрядов блока,1797112В УР Ь ЬЬ УЯ б ХВ ХУ Хб Х ХУ ХР Хг Я УУВЯу УуХу УаМ УЮТ УФХу УЗМу УРХО ЯХгМУХу УЮТУ УЗЛА УОХЯ УЗЫ УМ УЯйУФЯз ЖХз У 4 Хз УЗХз ЬХЯ ЮзМН ЙЙ ЧзХь Ъ ЧРММ УзаЬХ ЬМеЪ 6 Чаи ЬЯ 6ЬУХгУг Уу Ук Ь Чц з Уя й Яу Ху Мю Лу Я Х Хр ЯрУ 2 ОХЗ АХ) ЧЕХА Чую УВЯЛ УЭХВ УуХ,5 У 6 Ф УФ 5 УФХб УРХ 6 ЙХ 6 УзХВ УЮХВ УВХу У 7 Ху УРч УБХу УчХу УЗРИ УВХВ %48 УЕВ УЗХВ ЭФХВ УЗХа У 2 Ь11 КоРРектоР М.Ревская оставитель Е,Мурзина хред М.Моргентал актор. каз 654 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5 роизводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 10 Б 00 3

СмотретьЗаявка

4908191, 05.02.1991

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

ШОСТАК АЛЕКСАНДР АНТОНОВИЧ, ЯСКЕВИЧ ВАЛЕНТИН ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 7/52

Опубликовано: 23.02.1993

Код ссылки

<a href="https://patents.su/7-1797112-ustrojjstvo-dlya-umnozheniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел</a>

Предыдущий патент: Устройство для подсчета числа единиц

Следующий патент: Умножитель частоты

Случайный патент: Устройство для автоматической сортировки ферритовых сердечников по добротности и эффективной магнитной проницаемости