Цифровой асинхронный регенератор дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1788582

Автор: Романов

Текст

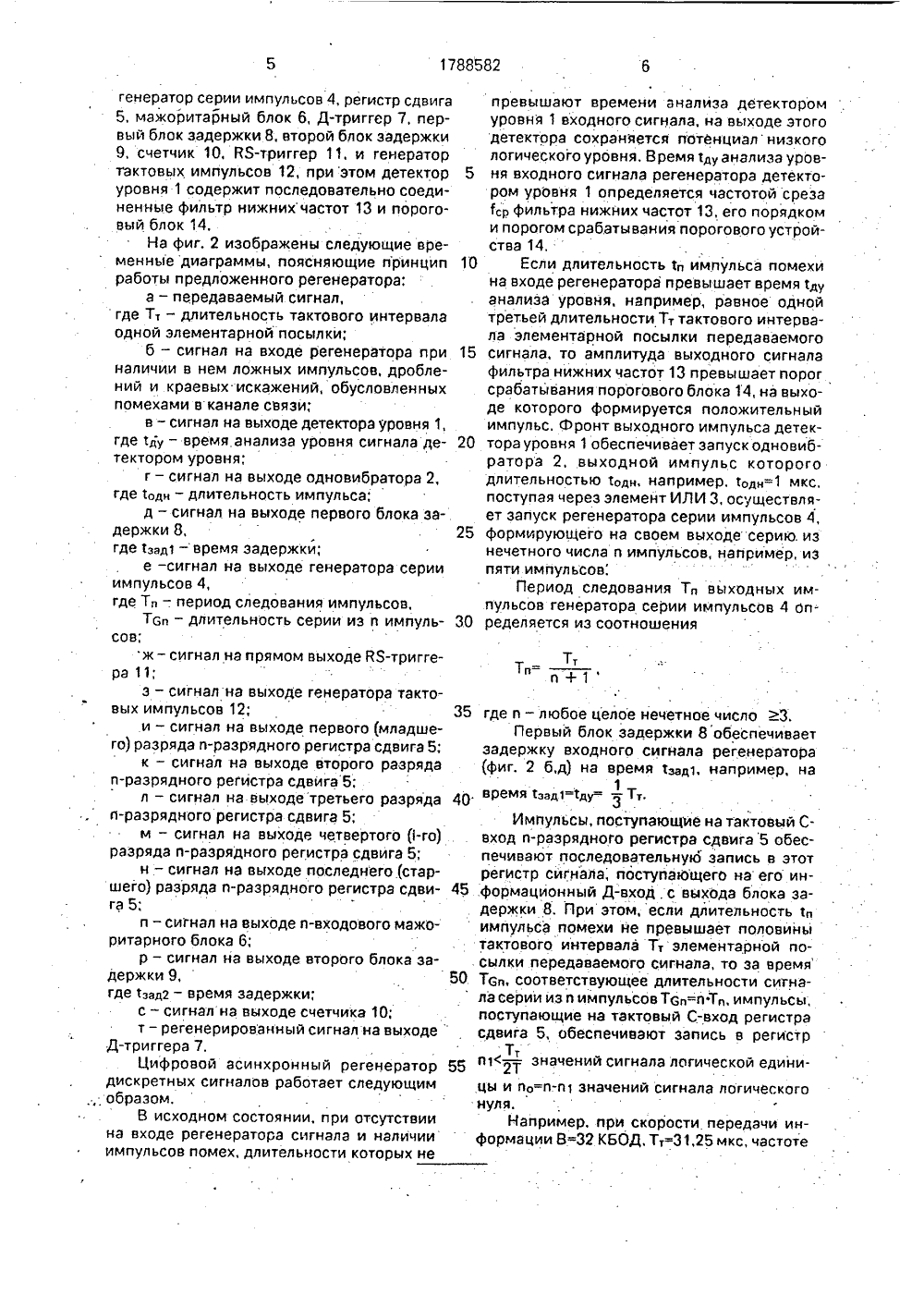

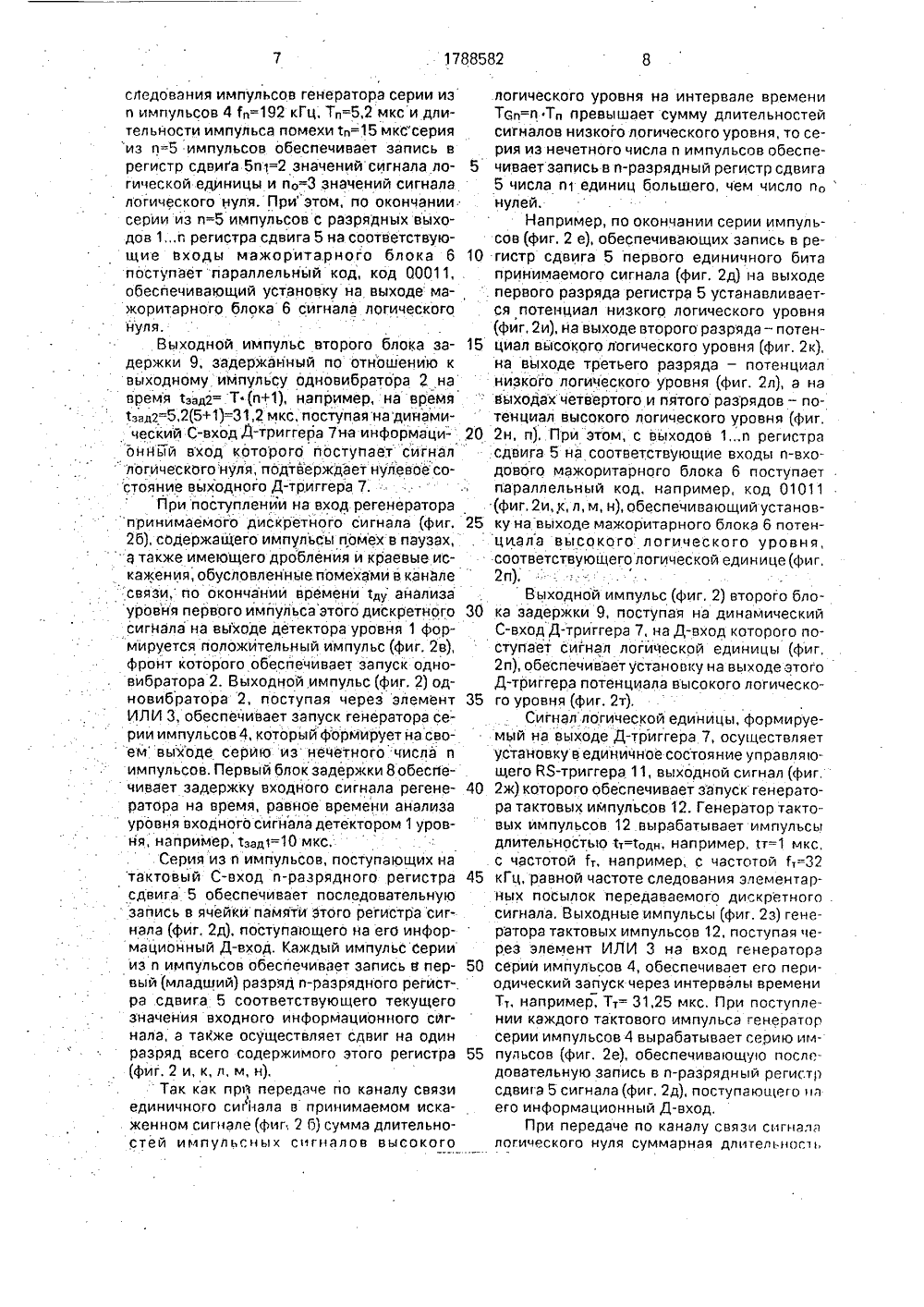

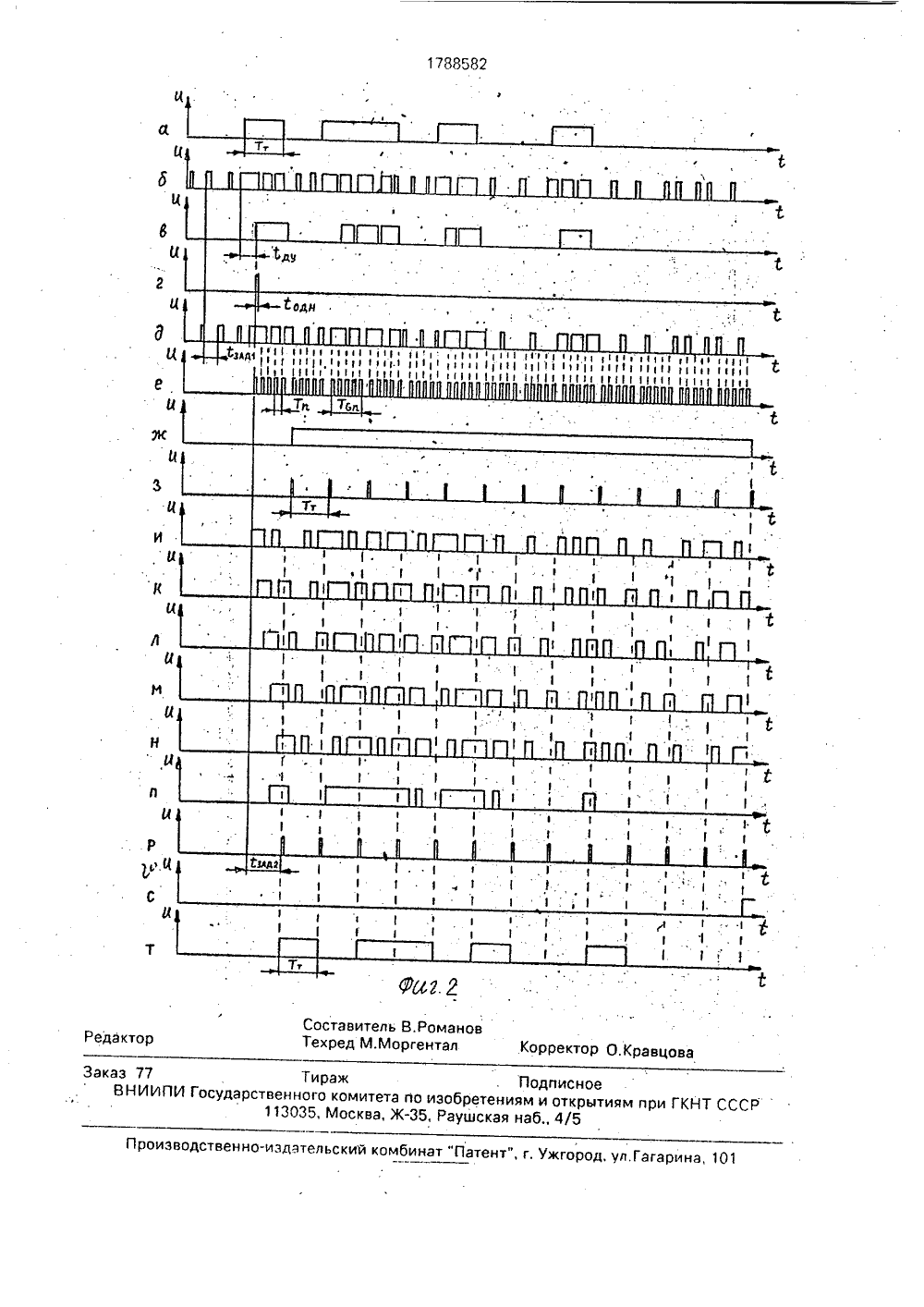

СОЮЗ СОВЕТСКИХСОцИАЛИСТИчеСКИРЕСПУБЛИК 8582 09) (13) ЙЙ 2 д 3,433ДЩа ЯЯ 1 ЦБЛБЛИОТЕИА АНИЕ ИЗОБРЕТЕН К АВ 10 РСКО ВИДЕТЕЛ ЬСТ 2 ОО ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(71) Научно-исследовательский институт автоматизированных систем и комплексовсвязи "Нептун"(56) Авторское свидетельство СССРМ 1241486, кл, Н 04 В 1/10, 1985.(54) ЦИФРОВОЙ АСИНХРОННЫЙ РЕГЕНЕРАТОР ДИСКРЕТНЫХ СИГНАЛОВ(57) Использование: регенерация дискретных сигналов, передаваемых по физическимлиниям связи. Сущность изобретения: регенератор содержит детектор уровня 1, одно- а 5 Н 04 В 1/10,Н 041 2 вибратор 2, элемент ИЛИ 3. генератор серии импульсов 4,регистр сдвига 5, мажоритарный блок 6, Д-триггер 7, блоки задержки 8, 9, счетчик 10, ЙЯ-триггер 11, генератортактовых импульсов 17. 1-2-3-4-5- 6-7, 1-8, 8-5, 11-12-3, 11-2, 11-10, 3-9-10, 9-7, 10-11, 7-10, 7-11, Повйшение помехоустойчивости достигается за счет того, что в каждом цикле анализа входного сигнала длительность из "и" импульсов, поступающих на тактовый вход, обеспечивает полную смену его содержимого, исключая возможность накопления лбгических сигйалов от импульсов помех. Устройство по и. 2 формулы отлйчается выполнением детектора уровня 1. 1 з,п. ф-лы, 2 ил.Изобретение относится к технике передачи сигналов и может использоваться в устройствах телеуправления, телеконтроля и цифровой связи, работающих в асинхронном режиме, для регенерации дискретных сигналов, передаваемых по физическим линиям или радиолиниям с высоким уровйем помех,Известен цифровой асинхронный регенератор импульсных сигналов, содержащий 10 генератор импульсов, первый и второй элементы И, реверсивный счетчик, элемент НЕ, делитель частоты спеременным коэффициентом деления, дешифратор и выходной 15 триггер Недостатком этого цифрового асинхронного регенератора является искажение длительностей элементарных посылок принимаемых дискретных сигналов, которое 20 выражается в уменьшении длительностей импульсов и увеличении длительностей пауз в выходном регенерировайнОм сигнале и имеет место как при поступлении на вход регенератора посылок без искажений, так 25 при поступлении посылок уже имеющих искажения.Цифровой асинхронный регенератор диСкретных сигналов обеспечивает исключение искажений длительностей принимаемых посылок сйгнала. 30 По технической сущности это устройство наиболее близко к заявляемому и принято за прототип, Этот цифровой асинхронный регенератор дискретных сиг 35 налов содержит выходной триггер, генератор импульсов, делитель частоты, четыре элемента И, реверсивный счетчик, дешифратор, инвертор, детектор уровня, ЙЯ-триггер управления, одновибратор, дополнительный инвертор, два элемента 40 ИЛИ и датчик тактовых импульсов. Детектор уровня состоит из ЙЯ-триггера, элемента И и интегратора,Недостатком прототипа является нйзкая помехоустойчивосгь, обусловленная 45 тем, что, при равновероятности появления врезок в принимаемых импульсных сигйалах и импульсов помех в паузах, отсутствие принудительного сброса реверсивного 50 счетчика обеспечивает возможность накопления в нем числа, определяемого импульсами помех, достаточного для формирования сигнала на первом выхоДе дешифратора, что определяет возможность ложной установки выходного триггера вединичное состояние при отсутствии передаваемого сигнЪля, Кроме того, низкая помехоустойчивость э гого устройства обусловлена также тем что выходной сигнал РЯ-триггера в де гектопе уровня, разрешающий работу устройства, формируется при поступлении на Я-вход этого триггера любого из импульсов помех независимо от длительности, что при отсутствии передачи дискретной информации и наличии импульсных помех в канале связи обеспечивает практически постоянное присутствие на выходе детектора уровня сигнала, разрешающего работу регенератора,Целью изобретения является повышение помехоустойчивости.Реализация поставленной цели достигается тем, что в цифровой асинхронный регенератор дискретных сигналов, содержащий детектор уровня, генератор тактовых импульсов, счетчик, Д-триггер, выход котОрого является выходом регенератора, входом которого является вход детектора уровня, и последовательно соединенные ЯЯ-триггер, одновибратор и элемент ИЛИ введены два блока задержки, мажоритарный блок, генератор серии импульсов и регистр сдвига, информационный и тактовый входы и выходы которого соединены соответственно с выходом первого блока задержки, вход которого подключен ко входу детектора уровня, с выходом генератора серии импульсов; ко входу которого подключен выход элемента ИЛИ, и со входом мажоритарного блока, выход которого подключен к информационному входу Д-триггера, динамический вход которого соединен с выходом второго блока задержки, ко входу которого подключен выход элемента ИЛИ, и с тактовым входом счетчика, управляющий и установочный входы и выход которого соединены соответственно с инверсным выходом ВЯ-триггера, с выходом Д-триггера и с Й-входом ВЯ-триггера, Я-вход и прямой выход которого соединены соответственно с выходом Д-триггера и со входом генератора тактовых импульсов, выход которого подключен ко второму входу элемента ИЛИ, при этом выход детектора соединен с пусковым входом одновибратора,Реализация поставленной цели достигается также тем, что детектор уровня содержит последовательно соединенные фильтр нижних частот и пороговый блок, выход которого является выходом детектора уровня, входом которого является вход фильтря нижних частот.На фиг. 1 изображена структурная элек. трическая схема предложенного генерято ра; на фиг, 2 - временные диаграммы, поясняющие работу предложенного р. гене ратора,Цифровой асинхронный регенеряо дискретных сигналов содержит дет".к. уровня 1, одновибратор 2, элемент Ин .3генератор серии импульсов 4, регистр сдвига5, мажоритарный блок 6, Д-триггер 7, первый блок задержки 8, второй блок задержки9, счетчик 10, ВЯ-триггер 11, и генератортактовых импульсов 12, при этом детекторуровня 1 содержит последовательно соединенные фильтр нижних частот 13 и пороговый блок 14.На фиг. 2 изображены следующие временные диаграммы, поясняющие принципработы предложенного регенератора:а - передаваемый сигнал,где Т - длительность тактового интервалаодной элементарной посылки;б - сигнал на входе регенератора приналичии в нем ложных импульсов, дроблений и краевых искажений, обусловленныхпомехами в канале связи;в - сигнал на выходе детектора уровня 1,где ду - время анализа уровня сигнала детектором уровня;г - сигнал на выходе одновибратора 2,где ьодн - длительность импульса;д - сигнал на выходе первого блока задержки 8,где 1 зэд 1- время задержкй;е -сигнал на выходе генератора серииимпульсов 4,где Тл - период следования импульсов,Тс - длительность серии из и импульсов;ж - сигнал на прямом выходе ЙЯ-триггера 11;з - сигнална выходе генератора тактовых импульсов 12;и - сигнал на выходе первого (младшего) разряда и-разрядного регистра сдвига 5;к - сигнал на выходе второго разрядаи-разрядного регистра сдвига 5;л - сигнал на выходетретьего разрядаи-разрядного регистра сдвига 5;м - сигнал на выходе четвертого (1-го)разряда и-разрядного регистра сдвига 5;н - сигнал на выходе последнего старшего) разряда и-разрядного регистра сдвига 5;и - сигнал на выходе и-входового мажоритарного блока б;р - сигнал на выходе второго блока задержки 9,где тзадг - время задержки;с - сигнал на выходе счетчика 10;т - регенерированный сигнал на выходеД-триггера 7,Цифровой асинхронный регенератордискретных сигналов работает следующимобразом,В исходном состоянии, при отсутствиина входе регенератора сигнала и наличииимпульсов помех, длительности которых неТти+135 где и - любое целое нечетное число 3.Первый блок задержки 8 обеспечиваетзадержку входного сигнала регенератора (фиг. 2 б,д) на время Ьад 1, например, на140. время Ьад 1=тду= - Т,.3Импульсы, поступающйе на тактовый Свход и-разрядного регистра сдвига 5 обеспечивают последовательную запись в этот регистр сигнала, поступающего на его ин формационный Д-вход. с выхода блока задержки 8, При этом, если длительность ь импульса помехи не превышает половины тактового интервала Тт элементарной посылки передаваемого сигнала, то за время 50 Та, соответствующее длительности сигна ла серии из и импульсов Та=п Тп, импульсы,поступающие на тактовый С-вход регистра сдвига 5, обеспечивают запись в регистрТтп - значений сигнала логической едини 2 Тцы и по=п-п 1 значений сигнала логического нуля.Например, при скорости передачи информации В=32 КБОД, Тт=31,25 мкс, частоте 5 10 15 20 25 30 превышают времени анализа детектором уровня 1 входного сигнала, на выходе этого детектора сохраняется потенциал низкого логического уровня, Время тду анализа уровня входного сигнала регенератора детектором уровня 1 определяется частотой среза 1 р фильтра нижних частот 13, его порядком и порогом срабатывания порогового устройства 14.Если длительность 1 п импульса помехи на входе регенератора превышает время 1 ду анализа уровня, например, равное одной третьей длительности Тт тактового интервала элементарной посылки передаваемого сигнала, то амплитуда выходного сигнала фильтра нижних частот 13 превышает порог срабатйвания порогового блока 14, на выходе которого формируется положительный импульс. Фронт выходного импульса детектора уровня 1 обеспечивает запуск одновибратора 2. выходной импульс которого длительностью тодн, например. тодди=1 мкс, поступая через элемейт ИЛИ 3, осуществляет запуск регенератора серии импульсов 4, формирующего на своем выходе серию. из нечетного числа и импульсов, например, из пяти импульсов,Период следования Тл выходных импульсов генератора серии импульсов 4 определяется из соотношенияследования импульсов генератора серии из и импульсов 4 оп=192 кГц, Тп=5,2 мкс и длительности импульса помехи Ь=15 мкс"серия из и=5 импульсов обеспечивает запись в регистр сдвига 5 и 1=2 значений сигнала логической единицы и по=3 значений сигналалогического нуля. При этом, по окончании серии из п=5 импульсов с разрядных выходов 1,и регистра сдвига 5 на соответствующие входы мажоритарного блока 6 поступает параллельный код, код 00011, обеспечивающий установку на выходе макоритарного блока 6 сигнала логического нуля.Выходной импульс второго блока задержки 9, задержанный по отношению к выходному импульсу одновибратора 2 на время Ьдг= Т (и+1), например, нэ время 1 зад 2=5,2(5+1)=31,2 мкс, поступая надийамический С-вход Д-триггера 7 на информационный вход которого поступает сигналлогическогонуля, подтверждает нулевое состояние выходного Д-триггера 7.При поступлении на вход регенераторапринимаемого дискретного сигнала (фиг, 2 б), содержащего импульсы помех в паузах, э также имеющего дробления и краевые искажения, обусловленные помехами в канале связи, по окончании времени тду анализа уровня первого импульсаэтого дискретного сигнала на выходе детектора уровня 1 формируется положительный импульс (фиг, 2 в), фронт которого обеспечивает запуск одновибратора 2. Выходной импульс (фиг. 2) одновибратора 2, поступая через элемент ИЛИ 3, обеспечивает запуск генератора серии импульсов 4, который формирует на своем выходе серию из нечетного числэ и импульсов. Первый блок задержки 8 обеспечивает задержку входного сигнала регенератора на время, равное времени анализа уровня входного сигнала детектором 1 уровня, например, тзад 1=10 мкс.Серия из и импульсов, поступающих натактовый С-вход и-разрядного регистра сдвига 5 обеспечивает последовательную запись в ячейки памяти этого регистра сигнала (фиг, 2 д), поступающего на его информационный Д-вход. Каждый импульс Серии из и импульсов обеспечивает запись в первый(млэдший) разряд и-разрядного регистра сдвига 5 соответствующего текущего значения входного информационного сигнала, а также осуществляет сдвиг на один разряд всего содержимого этого регистра (фиг. 2 и, к, л, м, н),Так как при передаче по каналу связиединичного сигнэлэ в принимаемом искаженном сигнале (фиг; 2 б) сумма длительностей импульсных сигналов высокогонулей 10 гистр сдвига 5 первого единичного бита 15 20 2 н, п), При этом, с выходов 1.и регистра.сдвига 5 на соответствующие входы и-входовьго мажоритарного блока 6 поступает 25 ку навыходе мажоритарного блока 6 потенциала высокого логического уровня, соответствующего логической един и це (фиг,2 п) 30 35 40 45 50 55 логического уровня на интервале времени Тап=п Т, превышает сумму длительностей сигналов низкого логического уровня, то серия из нечетного числа и импульсов обеспечивает запись в и-разрядный регистр сдвига 5 числа и 1 единиц большего, чем число и,Например, по окончании серии импульсов (фиг, 2 е), обеспечивающих запись в репринимаемого сигнала (фиг, 2 д) на выходе первого разряда регистра 5 устэнавливается потенциал низкого логического уровня (фиг,2 и), на выходе второго разряда - потенциал высокого логического уровня (фиг. 2 к), на выходе третьего разряда - потенциал низкого логического уровня (фиг. 2 л), э на выходах четвертого и пятого разрядов - потенциал высокого логического уровня (фиг. параллельный код, например, код 01011 (фиг,2 и, к, л, м, н), обеспечивающий установВыходной импульс (фиг, 2) второго блока задержки 9, поступая на динамический С-вход Д-триггера 7, на Д-вход которого поступает сигнал логической единицы (фиг, 2 п), обеспечивает установку на выходе этого Д-триггера потенциала высокого логического уровня (фиг. 2 т). Сигнал логической единицы, формируемый на выходе Д-триггера 7, осуществляет установку в единичное состояние управляющего ЙЯ-триггера, 11, выходной сигнал (фиг, 2 ж) которого обеспечивает запуск генератора тактовых импульсов 12. Генератор тактовых импульсов 12 вырабатывает импульсы длительностью тт=тодн, например, от=1 мкс, с частотой 7 т, например, с частотой от=32 кГц, равной частоте следования элементарных посылок передаваемого дискретного сигнала, Выходные импульсы (фиг. 2 з) генератора тактовых импульсов 12, поступая через элемент ИЛИ 3 на вход генератора серии импульсов 4, обеспечивает его периодический запуск через интервалы времени Тт, например, Тт= 31,25 мкс. При поступлении каждого тактового импульса генератор серии импульсов 4 вырабатывает серию импульсов (фиг. 2 е), обеспечивающую посл- довательную запись в и-разрядный регистр сдвига 5 сигнала(фиг. 2 д), поступающего на его информационный Д-вход.При передаче по каналу связи сигнала логического нуля суммарная длительноеь5 10 15 20 25 30 35 40 50 ратора серии импульсов 4, При отсутствии 55 сигналов низкого логического уровня во входном сигнале регенератора, содержа-. щем импульсные помехи, превышает суммарную длительность сигналов высокого логического уровня, обусловленных помехами в канале связи, вследствие чего, по окончании соответствующей серии из п импульсов, число нулей в выходном параллельном коде регистра сдвига 5 превышает число единиц.При этом, с выходов 1.п регистра сдвига 5 на соответствующие входы и-входового мажоритарного блока 6 поступает параллельный код, например, код 10100(фиг. 2 и, к, л, м, н),обеспечивающий установку на выходе мажоритарного блока 6 потенциала низкого логического уровня (фиг. 2 п), а соответствующий выходной импульс (фиг. 2 р) второго блока задержки 9 обеспечивает установку потенциала логического нуля (фиг, 2 т) на выходе Д-триггера 7,Таким образом, по окончании каждой серии из и-импульсов в и-разрядном регистре сдвига 5 фиксируется код, число единиц в котором определяется суммарной длительностью сигналов высокого логического уровня, а число нулей - суммарной длительностью сигналов низкого логического уровня в искаженном входном сигнале регенератора, Если числоединиц в соответствующем параллельном коде, характеризующем входной сигнал регенератора, превышает число нулей п 1 по, на выходе п-входового мажоритарного блока 6 устэнавливается сигнал. логической единицы, а если число нулей в этом коде превышает число единиц п 1 по, то на выходе мажоритарного блока 6 устанавливается сигнал логического нуля. Выходные импульсы (фиг. 2 р) второго блока задержки 9 обеспечивают фиксацию значений выходного сигнала мажоритарного блока 6 в Д-триггере 7, на выходе которого формируется цифровой регенерированный сигнал (фи, 2 т), не имеющий краевых искажений, дроблений и ложных импульсов. По окончании передачи дискретногосигнала на вход регенераторэ. поступают только импульсы, обусловленные помехами в канале связи. При этом, выходные импульсы генератора тактовых импульсов 12, поступая через элемент ИЛИ 3, продолжают осуществлять периодический запуск геневходного сигнала по окончании каждой серии из и импульсов нэ выходе мажоритарного блока 6 устанавливается потенциал низкого логического уровня, обеспечивающий наличие потенциала низкого логического уровня на выходе Д-триггера 7,Выходной сигнал Д-триггера 7 низкогологического уровня разрешает работу счетчика 7, осуществляющего подсчет числа тактовых импул ьсов, соответствующихтактовым интервалам, в течение которых навыходе Д-триггера 7 непрерывно сохраняется сигнал логического нуля, При поступлении на счетный С-вход счетчика 10 числа Мтактовых импульсов, например, М=8, соответствующих, следующим подряд, сигналам:логического нуля, на единицутревышающе-го максимально возможное число И, например, К=7, следующих подряд, тактовыхинтервалов логического нуля. в передэваЕмом сигнале, на выходе счетчика 10 формируется положительный импульс (фиг, 2 с),обеспечивающий сброс в исходное состояние управляющего ЙЯ-триггера 11, Приэтом, на инверсном выходеупраВляющегоВЯ-тригера 11 устанавливается потенциалвысокого логического уровня, запрещающий подсчет счетчиком 10 тактовых импул ьсов и разрешающий работу одновибратора2, подготавливая тем самым регенератор крегенерации нового принимаемого дискретного сигнала.Эффективность предлагаемого изобретения состоит в том, что путем введения вцифровой асинхронный регенератор дискретных сигналов, содержащий детекторуровня, генератор тактовых импульсов,счетчик, Д-триггер, ВЯ-триггер, одновибратор и элемент ИЛИ, двух блоков задержки,мажоритарного блока, генератора серии импульсов и регистра сдвига достигается увеличение помехоустойчивости регенератора.Увеличение помехоустойчивостирегенератора при наличии на его входе потока импульсов помех обеспечивается тем,что в каждом цикле анализа входного сигнала серия из п-импульсов, поступающая натактовый С-вход и-разрядного регистрасдвига обеспечивает полную смену его содержимого, исключая возможность накопления в регистре логических сигналов отимпульсов помех, а, следовательно и возможность формирования ложных сигналовна выходе регенератора,Кроме того, увеличение помехоустойчивости регенератора обусловлено также выполнением детектора уровня в видепоследовательно соединенных фильтранижних частот и порогового блока, обеспечивающих уменьшение вероятности ложных запусков регенерэтора импульсамипомех и его переключенйя в режим анализавходного сигнала при отсутствии факта пе 1788582редачи дискретного сигнала по каналу свя- тельно соединенные ЙЗ-триггер, одновибзи. ратор и элемент ИЛИ, о т л и ч а ю щ и й с яТочность воспроизведения в выходном тем; что, с целью повышения помехоустойсигнале регенератора временных интерва- чивости, введены два блока задержки, маловпередаваемогодискретногосигналаоп жоритарный блок, генератор серии ределяется только точностью соответствия импульсов и регистр сдвига, информациончастоты генератора тактовых импульсов ный и тактовый входы и выходы которого тактовой частоте передаваемого дискретно- соединены соответственно с выходом перга сигнала и может быть, при использовании вого блока задержки; вход которого подклюкварцевой стабилизации, очень высокой. 10 чен к входу детектора уровня, с выходомОбладая более высокой помехоустойчи- генератора серии импульсов, к входу котовостью и обеспечивая высокую точность рого подключен выход элемента ИЛИ, и с воспроизведения временных интервалов входами мажоритарного блока; выход кото- передаваемого дйскретного сигнала, пред- рого подключен к информационному входу ложенный регенератор, содержащий 12 15 Д-триггера,динамический вход которого соблоков и элементов, является значительно единен с выходом второго блока задержки. более простым по сравнению с прототипом к входукоторого подключенвыход элемента по авт.св, %1241486, содержащим 20 бло- ИЛИ, ис тактовым входомсчетчика, управков.и элементов,ляющий и установочный входы и выход коБолее высокая помехоустойчивость 20 торого соединены соответственно с предложенйого ретенератора, по сравне- инверсным выходом ЯЯ-триггера, с выходом нию с прототипом и базовым объектом,при Д-триггера иВ-входом ЯЯ-триггера, 8-вход использовании этого регенераторав прием- и прямой выход которого соединены соотных устройствах телеуправления и телекон- ветственно с выходом Д-триггера и с выхотроля, обеспечивает увеличение 25 домтенератора тактовых импульсов, выход надежности дистанционного, управлений и которого подключен к второму входу элеконтроля, а при использовании в приемныхмента ИЛИ, при этом выход детектора уров- . устройствах цифровой связи - увеличейие ня соединен с пусковым входом дальности связи,одновибратора.ф о р м у л а и з о б р е т е н и я 30 2, Регенератор дискретных сигналов по 1, Цифровой асинхронный регейератор п.1, о т л и ч а ющ и й с я тем, что детектор дискретных сигналов, содержащий детек- уровня -содержит последовательно соедитор уровня, генератор тактовых импульсов,ненные фильтр нижнйх частот и пороговый счетчик, Д-триггер, выход которого является . блок, выход которого "является выходом девыходомрегенератора, входом которого яв тектора уровня, входом которого является ляется вход детектора уровйя, и последова- вход фильтра нижнйх частот,17 Я 8582 д и дакто ова р ректор Заказ 77 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раущская наб., 4/5 изводственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 10 Лй оставитель В.Роман ехред М.Моргентал

СмотретьЗаявка

4866668, 09.07.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ АВТОМАТИЗИРОВАННЫХ СИСТЕМ И КОМПЛЕКСОВ СВЯЗИ "НЕПТУН"

РОМАНОВ ВИКТОР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04B 1/10, H04L 25/30

Метки: асинхронный, дискретных, регенератор, сигналов, цифровой

Опубликовано: 15.01.1993

Код ссылки

<a href="https://patents.su/7-1788582-cifrovojj-asinkhronnyjj-regenerator-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой асинхронный регенератор дискретных сигналов</a>

Предыдущий патент: Радиоприемное устройство

Следующий патент: Устройство компенсации гармонических помех в радиоприемниках амплитудно-модулированных сигналов

Случайный патент: Способ получения синтетического шлака