Устройство для суммирования длительностей импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1430970

Авторы: Белан, Кожемяко, Короновский

Текст

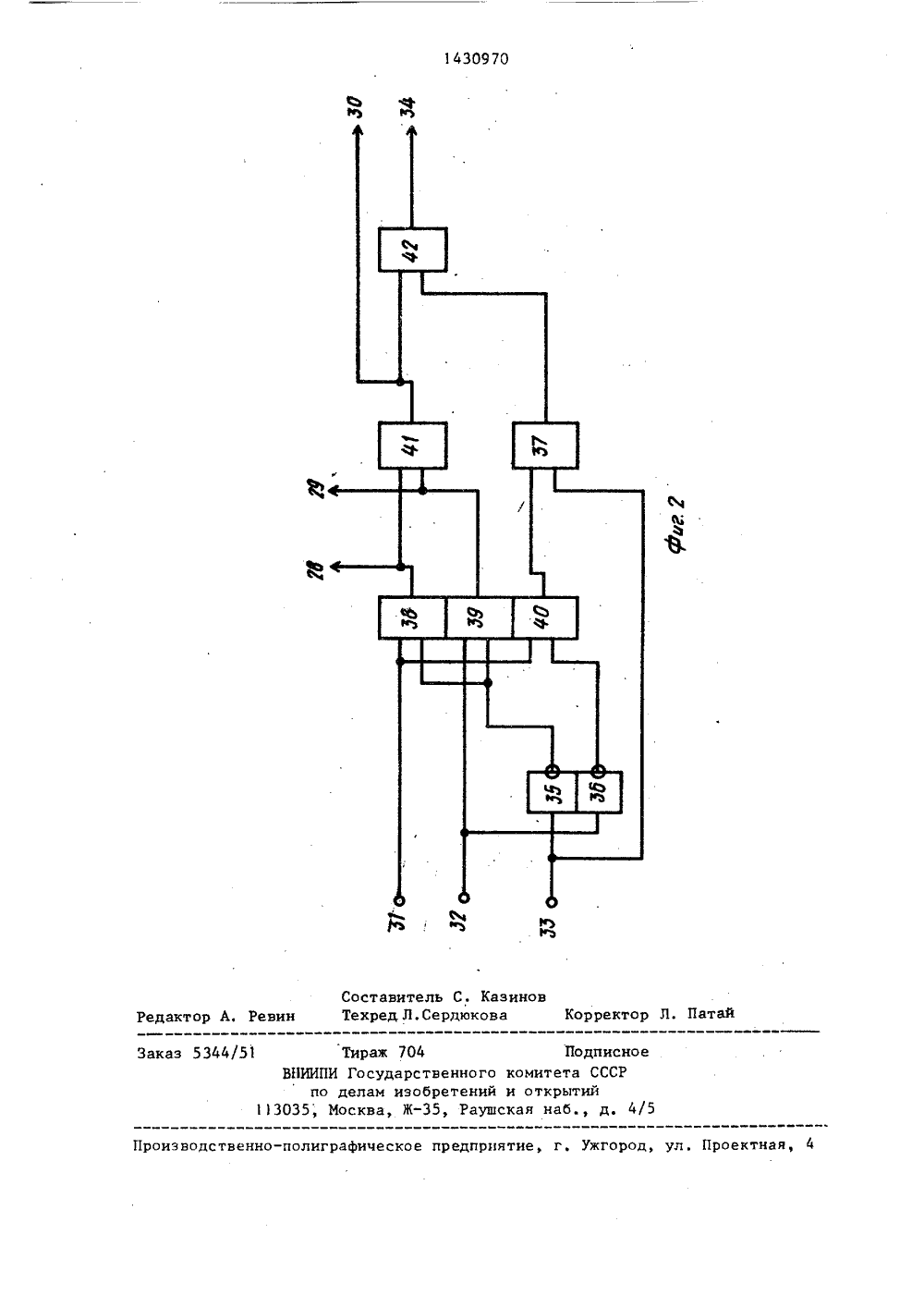

(21 (22 4190070/24-230.01.8715.10,88.Винницкий Бюл. Р 38политехнический ин(71) ститу (72) А.И. (53) (56) тель а ыч ислиая техУСТРОЙНОС ТЕЙ Изобре и вычибыть исретения ТВО ДЛЯ СУММИРОИМПУЛЬСОВение относитсяслительной техникользовано в ЦВМявляется повышерасширение обл втом е жетиз о,б л ние быстсти прика но одействи СУДАРСТВЕННЫЙ НОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ МУ СВИДЕТЕЛЬСТВ В.П. Кожемяко, С.Н. БелКороновский и Л,В, Бела681.335(088.8)Майоров С.А. и др. Узлыой техники - Вычислитель1976,.У 6, с. 83-89.торское свидетельство С330, кл. С Об 6 7/14, 1 менения эа счет параллельного суммирования или вычитания длительностей импульсов. Устройство содержит К бло. ков суммирования, каждый из которых содержит п бистабильных элементов, группы элементов ИЛИ, группы элементов И, . формирователи импульсов, элементы запрета,шины сложения, вычитания,переноса,заема. Кроме того, устройство содержит блок формирования длительностей импульсов, импульсные входы, вход управления режимами сложения и вычитания, а первый блок суммирования дополнительно содержит группы элементов И, элемент И-НЕ и два элемента НЕ. Информация н устройстве пред- ф ставляется в единично-нормальном коде. Сложение и вычитание длительностей импульсов может производиться С к параллельно, так и последователь 1 з,п. ф-лы, 2 ил.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в ЦВИ.Цель изобретения - повышение быст 5родействия и расширение области применения устройства за счет параллельного суммирования или вычитания длительностей импульсов.На фиг. 1 изображена блок-схемапредлагаемого устройства; на Фиг,2схема блока Формирования длительностей импульсов,Устройство содержит К блоков11-11, суммирования, каждый из которых содержит и бистабильных элементов 2, 2-2 с входами 3 и 4 установки в "1" и "0" соответственно,первую группу элементов ИЛИ 5, вторуюгруппу элементов ИЛИ 6, первую группу элементов И 7, вторую группу эле 1ментов И 8, два формирователя 9 импульсов, первый ,1 О и второй 11 злементы запрета, дину 12 сложения, дину13 вычитания, шину 14 переноса, шину 2515 заема, блок 16 Формирования длительностей импульсов, первый 17 и второй 18 импульсные входыи вход 19 управления режимами сложения и вычитания, 30В первый блок 1 суммирования до"полнительно входят третья группа элементов И 20, четвертая группа из элементов й 21-24, элемент И-НЕ 25 идва элемента НЕ 26 и 27. Блок 16 Фор- З 5,мирования длительностей импульсов,содержит с первого по третий выходы28-30, сигнальные входы 31 и 32, управляющий вход 33, четвертый выход34, элементы НЕ 35 и 36, элементы И 4037-40 и элементы ИЛИ 41 и 42.Устройство работает следующим образом.Каждый блок 1,. -1содержит четноеколичество бистабильных элементов,те. и 21 (1=11 Ц.Информация в устройстве представляется в единично-нормальном коде.Сложение и вычитание длительностейимпульсов может производиться как параллельно, так и последовательно.Для последовательного сложениядлительностей импульсов на вход 19устройства подается логический "0",а на первый 17 либо второй 18 входыустройства подают первый импульс, поступающий на первый 31 или второй 32входы блока 16 формирования длительностей импульсов и проходящий на его выход 34, поступающий оттуда на шину 12 сложения, при этом сигнал с выхода элемента 10 запрета через элемент ИЛИ 5 поступает на вход 3 установки в единичное состояние бистабильного элемента 21, вызывая его установку в состояние логической "1", которая появляется на единичном выходе, давая разрешение на переключение следующего бистабильного элемента и т.д.Последний бистабильный элемент .2, при установке в состояние логической "1" дает разрешение на формирование импульса переноса с выхода схемы второго Формирователя 9 импульсов, этим же импульсом все бистабипьные элементы, кроме первого в первой группе, устанавливаются в состояние логического "0" воздействием на входы 4 установки в нулевое состояние через элементы ИЛИ 6, при этом длительность ", , импульса определяется максимальным временем переключения бистабильных элементов 2-2. Первый, бистабильный элемент 2, не устанавли вается в состояние логического "0", только в том случае, когда входной импульс продолжает присутствовать на одном из двух входов 17 или 18 устройства и по окончании времени установки в состояние логической "1 " . последнего бистабильиого элемента 2 первой группы, через время ь ср, к первый бистабильный элемент 2 следующей группы перейдет в состояние логической "1", а первый бистабильный элемент 2 первой группы останется в состоянии логической "1 " лишь только в том случае, если С ргде Е - длительность импульса на входе 17 или 8 устройства;л"ср.ср - среднее время срабатывания одного бистабильного элемента.Первый бистабильный элемент 2 первой группы остается в состоянии логической "1", так как с выхода 30 блока 16 на вход первого элемента НЕ 26 поступает сигнал логической "1", который преобразуется в логический0 и поступает на первый вход треть е го элемента И 2 3 , на выходе которого также будет и рисут ст в ова ть логич е ский "О ", по с туп аюший че реэ второй элемент ИЛИ 6 на нулевой вход первого б ис т абиль но го элемента 2который, в свою очередь, не переходит в состояние логического 10". Для последовательного вычитания длительностей импульсов в устройство5 заносят импульс уменьшаемый, Процесс записи импульса уменьшаемого аналогичен вышеописанному режиму последовательного сложения.При поступлении информации на шину 1 3 вычитания сигнал с выхода элемента 11 запрета поступает на элементы И 8 и появляется на выходах тех элементов И 8, на вторые входы которых с нулевых выходов бистабильных элементов поступает сигнал логической "1", т.е. эти бистабильнь:е элементы находятся в состоянии логического "0".Допустим, в декаде в состоянии логической 1 находится 1 бистабильньм 2 элементов 2, -2 следовательно, в состоянии логического "0" находится и - х бистабильных элементов 2; -2. С нулевого выхода (1+1)-го бистабильного элемента 2,+ через элемент И 8 25 сигнал логической "1 " поступает через элемент ИЛИ 6 на вход 4 установки в нулевое состояние бистабильного элемента 21, вызывая его установку в состояние логического "О", т.е, на его нулевом выходе появляется логическая "1", давая разрешение на переключение следующего бистабильного элемента 2; 1, и т.д. При этом на единичном выходе 1-го бистабильного элемента 2 появляется логический 0" и т.д.Первый бистабильный элемент 2 при установке в состояние логического "0" разрешает Формирование импульса пе О реноса с выхода схемы первого формирователя импульсов, этим же импульсом все бистабильные элементы 2,-2 устанавливаются в состояние логической 1 воздействием на входы 3 уста новки в единичное состояние через элементы ИЛИ 6, при этом длительность импульса определяется максимальным временем переключения.Последний бистабильный элемент 2устанавливается в состояние логической "1" лишь в том случае, если с шины 13 вычитания в этот момент не подается единичный сигнал, На вьмоде второго элемента НЕ 27 присутствует сигнал логической "1", который через четвертый элемент И 24 и элемент ИЛИ 5 поступает на единичный вход 3 последнего бистабильного элемента 2. Через шину 15 заема в нулевое состояние переходит старший бистабильный элемент второй группы, находящийся в состоянии логической "1".Для одновременного сложения двух длительностей импульсов на вход 19 устройства подается логический "О", а на первый 17 и второй 8 входы - суммируемйе импульсы. Все они поступают на входы 31-33 блока 16. В результате на выходе 34 блока 16 будет присутствовать импульс с длительностью, равной наибольшей длительности одного из суммируемых импульсов.Таким образом, устройство может суммировать длительности импульсов, совпадающие по передним фронтам, а суммирование происходит за время, равное времени импульса с большей длительностью.Если на первые два входа 17 и 18 устройства одновременно подаются суммируемые импульсы, то первых два бистабильных элемента 2, и 2 первой группы одновременно устанавливаотся в единичное состояние за счет того, что с двух выходов 28 и 29 блока 16 на входы элемента И 21 подаются логические "1", а с выхода элемента И 21 через элементы ИЛИ 5 единичный сигнал поступает на единичные входы 3 первых двух бистабильных элементов 2, и 2, вызывая их установку в состояние логической "1 ", которая появляется на единичных выходах, давая разрешение на переключение следующих двух бистабильных элементов 2и 2. Единичный сигнал с выхода элемента И 7, первый вход которого подключен к единичному выходу бистабильного элемента 2 поступает на третий вход второго элемента И 20, сигнал с выхода которого через элементы ИЛИ 5 поступает на единичные входы 3 бистабильных элементов 2 и 2 , тем самым вызывая их установку в состояние логической "1" и т.д.Последний бистабильный элемент 2 при установке в состояние логической "1" дает разрешение на формирование импульса переноса с выхода второго Формирователя 9 импульсов. Этим же импульсом все бистабильные элементы устанавливаются в состояние логического "О" воздействием на входы 4 установки в нулевое состояние через элементы ИЛИ 6, при этом длительность импульса определяется максимальнымТ 61 1, при 11 = 1 40 0 при 1 О где й - время присутствия импульсавычитаемого, 45й 1 " время присутствия имцульсауменьшаемого,Таким образом, время присутствия вычитаемого импульса не выходит за рамки времени присутствия уменьшаемо го импульса.Блок 16 на выходе 34 формирует импульс, длительность которого соответствует времени Ей - С присутст 1вия только уменьшаемогб импульса. Время присутствия одновременно двух импульсов не учитывается. Если импульсы по передним фронтам не совпадают,временем переключения бистабильныхэлементов,Если на первых двух входах 17 и18 устройства продолжают присутство-:5вать два импульса, то в состояниелогической "1" переходит бистабильный элемент следующей группы, а впервой группе остаются в том же единичном состоянии первые бистабильныеэлементы 21 и 2так как с выходов28-30 блока 16 на входы элементаИ-НЕ 25 и элемента НЕ 26 подаютсясигналы логической "1". На выходахэлементов НЕ 26 и И-НЕ 25 появляютсялогические "0", поступающие черезэлементы И 23 и 22 и элементы ИЛИ бна нулевые входы 4 первых двух бистабильных элементов 2 и 2, тем самымне вызывая их переключенйя. В дальнейшем процесс сложения происходитаналогичным образом.С момента времени, когда импульсс меньшей длительностью заканчивается, сложение происходит так же, каки сложение при последовательном суммировании до окончания импульса сбольшей длительностью.,. Дпя параллельного вычитания двухдлительностей импульсов на вход 19устройства подают сигнал логической"1", а на первый 17 и второй 8 входы устройства соответственно подаютимпульс .уменьшаемого и импульс вычитаемого, причем моменты присутствияобоих импульсов должны соответствовать условиям то на выходе блока 16 будет присутствовать два импульса с длительностями,соответственно равными длительностиот переднего фронта уменьшаемого импульса до переднего фронта вычитаемого импульса и от заднего фронта вычитаемого импульса до заднего фронтауменьшаемого импульса, т.е. блок 16вырезает длительность импульса (двухимпульсов), полученного в результатевычитанияПолученный импульс поступает на шину сложения и в, дальнейшемпроцесс записи происходит аналогично.процессу последовательного суммирования, описанного вышее.Таким образом, устройство можетпоследовательно и параллельно суммировать и вычитать длительности импульсов.Блок 1 б формирования импульса сложения и вычитания работает следующимобразом,В режимах сложения на вход 33 по-.дается логический "0", а на входы 31и 32 подаются логические "1 ", посту-,пающие через элементы И 38 и 39 (засчет присутствия на выходе элементаНЕ логического "0") на входы элемента ИЛИ 41 и на выходы 28 и 29 . С выхода элемента ИЛИ 41 единичный сигнал поступает на выход 30 и черезэлемент ИЛИ 42 - на выход 34 блока16. Если присутствует один импульсна одном из двух входов блока 16,то на выходе элемента ИЛИ 41 такжебудет присутствовать логическая "1 ".В режиме параллельного вычитанияна вход 32 блока 16 подается логическая "1 ", поступающая также навход элемента И 37. С выхода элемента НЕ 35 на вторые выходы первогои второго элементов И 38 и 39 поступает логический "0". Следовательно,на выходе элемента ИЛИ 41 и выходах28 и 29 присутствует логический "0".Если на выходе 30 присутствует импульс, а на входе 31 импульс не присутствует, то на первый вход элемента И 40 с первого выхода 30 блока 16и на второй вход с выхода второгоэлемента НК 36 поступает логическая"1 ". С выхода элемента И 40 черезэлемент И 37 и второй элемент ИЛИ42 единичный сигнал поступает на выход 34 блока 1 6. Если импульсы присутствуют на первых двух входах 31 и32 блока 16, то на выходе элементаИ 40 будет присутствовать логическийО, который также поступает на вы=ход 34 блока 16.Формула изобретенияУстройство для суммирования длительностей импульсов, содержащее К блоков суммирования, каждый из которых содержит и бистабильных элемен О тов, два элемента запрета, два формирователя импульсов две группы по и, элементов И и две группы по п элементов ИЛИ, причем в каждом -м (1 1, К) блоке суммирования единичный выход 15 "го (д = 1,и) бистабильного элемента подключен к первому входу 1.-го элемента И первой группы, соединенного выходом с первым входом (д+1)-го элемента ИЛИ первой группы, выход ко торого подключен к входу установки в "1" (+1)-го бистабильного элемента, соединенного нулевым выходом с первым входом (д+1)-го элемента И второй . группы, подключенного выходом к пер вому входу 1.-го элемента ИЛИ второй группы, выход которого соединен с входом установки в "0" 1.-го бистабильного элемента, причем выход первого элемента ИЛИ первой группы.под ключен к входу установки в "1 " первого бистабильного элемента, соединенного нулевым выходом с первым входом первого элемента И второй группы, подключенного выходом к входу первого формирователя импульсов, причем вторые входы элементов И первой группы и первый вход первого элемента ИЛИ первой группы соединены с выходом первого элемента запрета, подключенного первым входом к вторым входам с третьего по и-й элементов ИЛИ второй группы и выходу второго формирователя импульсов, соединенного. входом с выходом и-го элемента И первой45 группы, а вторые входы элементов И второй группы и второй вход и-го элемента ИЛИ второй группы подключены к выходу второго элемента запрета, соединенного первым входом с выходом рервого формирователя импульсов и вторыми входами с первого по (и)-й элементов ИЛИ первой группы, причем в каждом -м блоке суммирования, за исключением первого блока, выход первого формирователя импульсов подклю 55 чен к второму входу и-го элемента ИЛИ первой группы, выход второго формиоователя импульсов соединен с вторыми входами первого и второго элементов ИЛИ второй группы, вторые входы первого и второго элементов запрета 1-го блока суммирования подключены к выходам второго и первого формирователей импульсов (1-1)-го блокасуммирования соответственно, а вторыевходы первого и второго элементов запрета первого блока суммирования соединены с шинами сложения и вычитанияустройства соответственно, о т л ич а ю щ е е с я тем, что, с цельюповышения быстродействия и расширенияобласти применения за счет параллельного суммирования или вычитания длительностей импульсов, в него введенблок формирования длительностей импульсов, а первый блок суммирования,дополнительно содержит третью группу из (и - 2)/2 элементов И, четвертую группу из четырех элементов И,два элемента НЕ и элемент И-НЕ, приэтом блок формирования длительностейимпульсов подключен первым и вторымсигнальными входами к первому и второму импульсным входам устройства,управляющим входом - к входу управления режимами сложения и вычитанияустройства, первым и вторым выходамисоответственно к первым и вторымвходам элементов И третьей группы,первому и второму входам первого элемента И четвертой группы и первому ивторому входам элемента И-НЕ, третьимвыходом - к входу первого элементаНЕ, а четвертым выходом - к второмувходу первого элемента запрета первого блока суммирования, причем в первом блоке суммирования выход первогоэлемента И четвертой группы соединенс третьими входами первого. и второгоэлементов ИЛИ первой группы, второйэлемент И четвертой группы подключенвыходом к второму входу второго элемента ИЛИ второй группы, первым входом - к выходу элемента И-НЕ, а вторым входом - к выходу второго формирователя импульсов и первому входутретьего элемента И четвертой группы,соединенного вторым входом с выходомпервого элемента НЕ, а выходом - свторым входом первого элемента ИЛИвторой группы, при этом четвертыйэлемент И четвертой группы подключенвыходом к второму входу и-го элемента ИЛИ первой группы, первым входомк выходу первого формирователя импульсов, а вторым входом - к выходувторого элемента НЕ, соединенного входом с шиной вычитания устройства, при этом каждый 1-й 11 ( (и)щэлемент И третьей группы подключен третьим входом к выходу (2 - 1)-го5 элемента И первой группы, а выходомк третьему входу 2(1+1)-го элемента ИЛИ первой группы.2. Устройство по п, 1, о т л и - ч а ю щ е е с я тем, что блок формирования длительностей импульсов содержит четыре элемента И, два элемента ИЛИ и два элемента НЕ, причем первый элемент НЕ подключен входом к управляющему входу блока формирования длительностей импульсов и первому входу первого элемента И, а выходомк первым входам второго и третьего элементов И, причем второй элемент И 2 О соединен вторым входом с первым сигнальным входом блока формирования длительностей импульсов и первым входом четвертого элемента И, а выходом - с первым выходом блока формирования длительностей импульсов ипервым входом первого элемента ИЛИ,подклЬченного вторым входом к выходутретьего элемента И и второму выходублока формирования длительностей импульсов, а выходом - к первому входувторого элемента ИЛИ, соединенноговторым входом с выходов первого элемента И, второй вход которого подключен к выходу четвертого элемента И,соединенного вторым входом с выходомвторого элемента НЕ, подключенноговходом к второму входу третьего элемента И и второму сигнальному входублока формирования длительностей импульсов, а выходы первого и второгоэлементов ИЛИ соединены соответственно с третьим и четвертым выходамиблока формирования длительностей импульсов.1430970 е Ь Составитель С. Ка Техред Л. Сердюков ов Корректор Л. Патай Ревин дак Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 аз 5344/51ВНИИ1)3035 Тираж 704 ПИ Государственного по делам изобретений Москва, Ж-Э 5, РаушПодписноекомитета СССРи открытийкая наб, д. 4/

СмотретьЗаявка

4190070, 30.01.1987

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОЖЕМЯКО ВЛАДИМИР ПРОКОФЬЕВИЧ, БЕЛАН СТЕПАН НИКОЛАЕВИЧ, КОРОНОВСКИЙ АЛИМ ИВАНОВИЧ, БЕЛАН ЛАРИСА ВАЛЕНТИНОВНА

МПК / Метки

МПК: G06G 7/14

Метки: длительностей, импульсов, суммирования

Опубликовано: 15.10.1988

Код ссылки

<a href="https://patents.su/7-1430970-ustrojjstvo-dlya-summirovaniya-dlitelnostejj-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования длительностей импульсов</a>

Предыдущий патент: Устройство для управления транспортным средством

Следующий патент: Устройство для формирования двухфазных гармонических напряжений

Случайный патент: Смесь для устройства дорожных оснований