Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1381503

Автор: Соловей

Текст

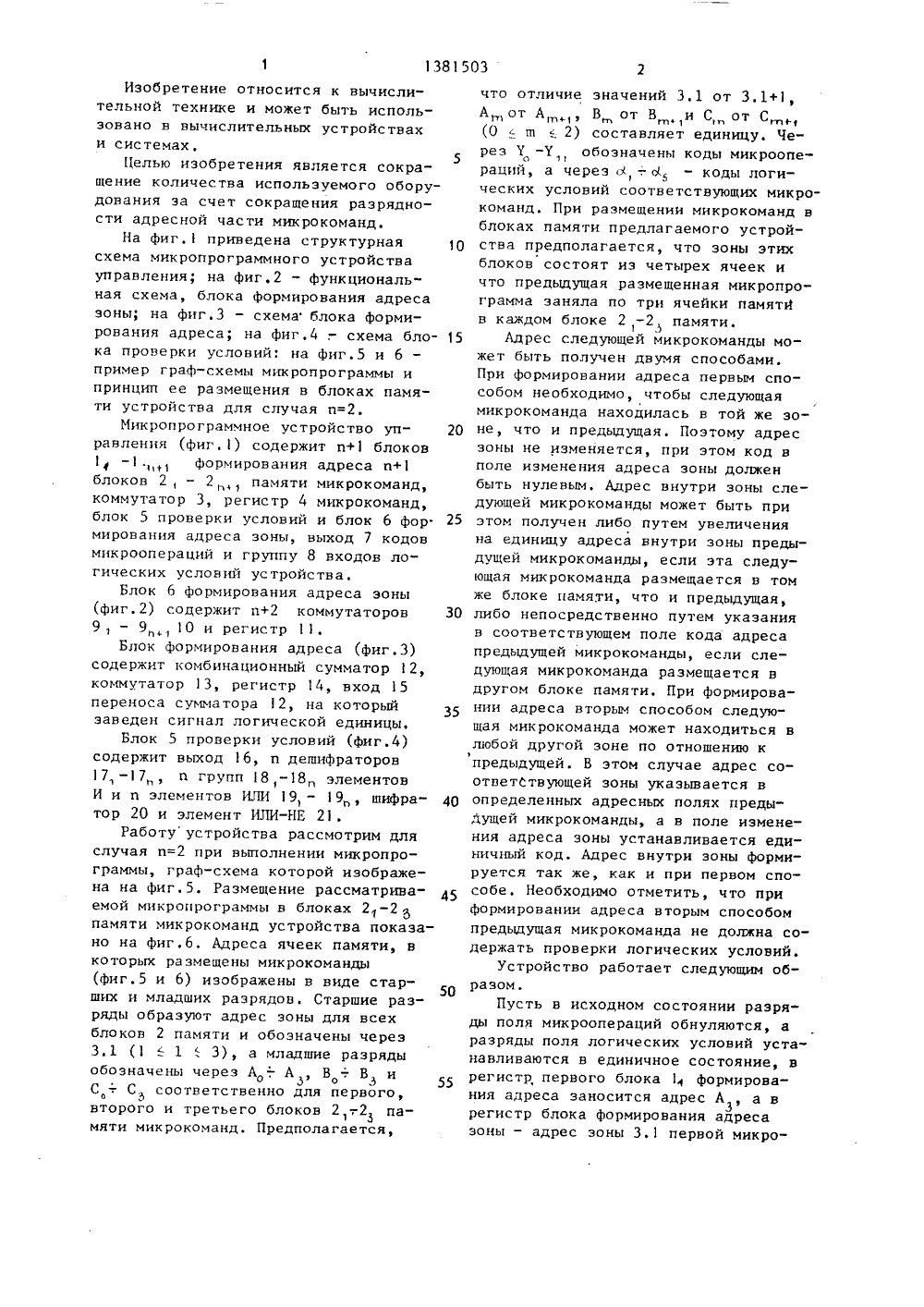

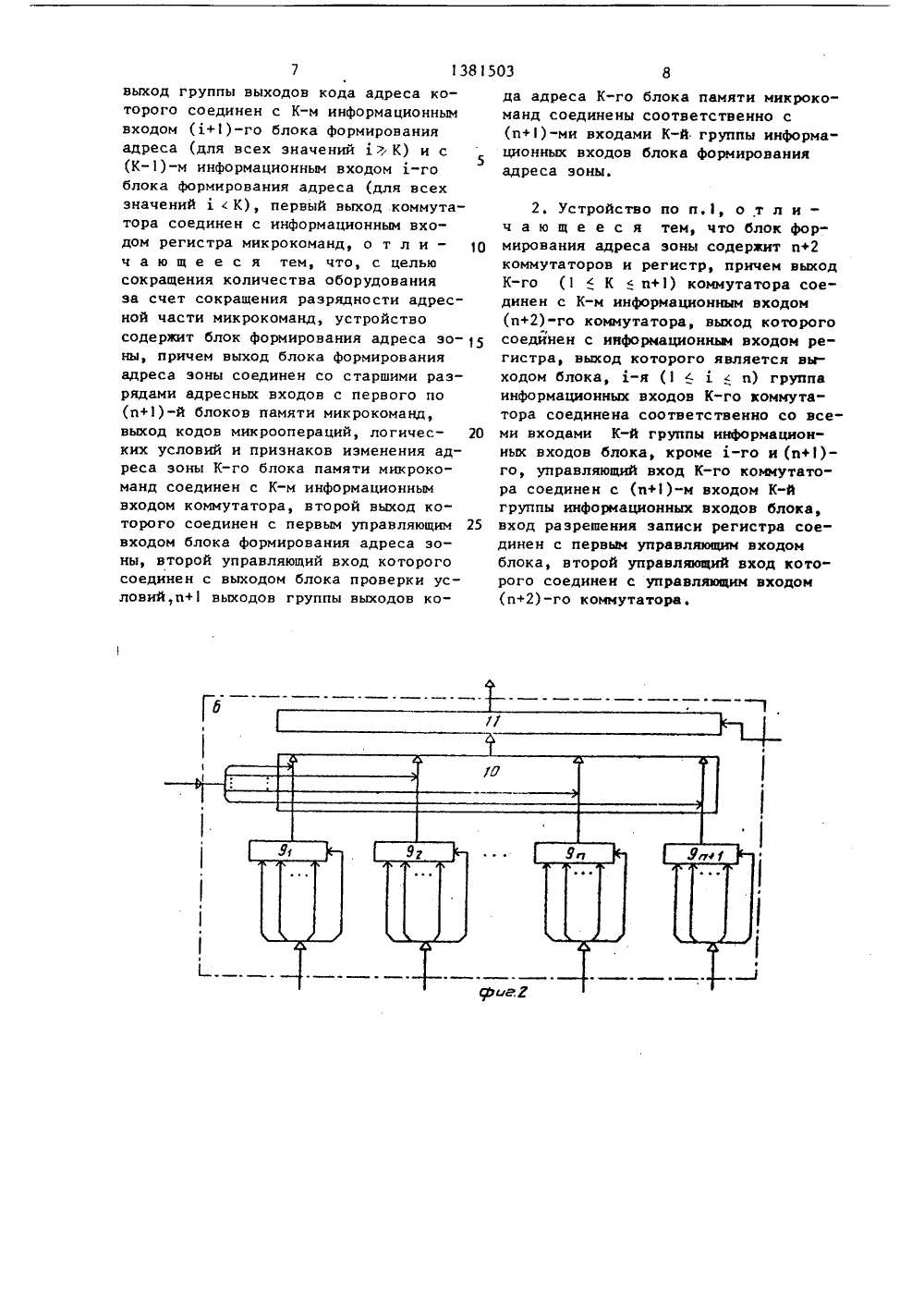

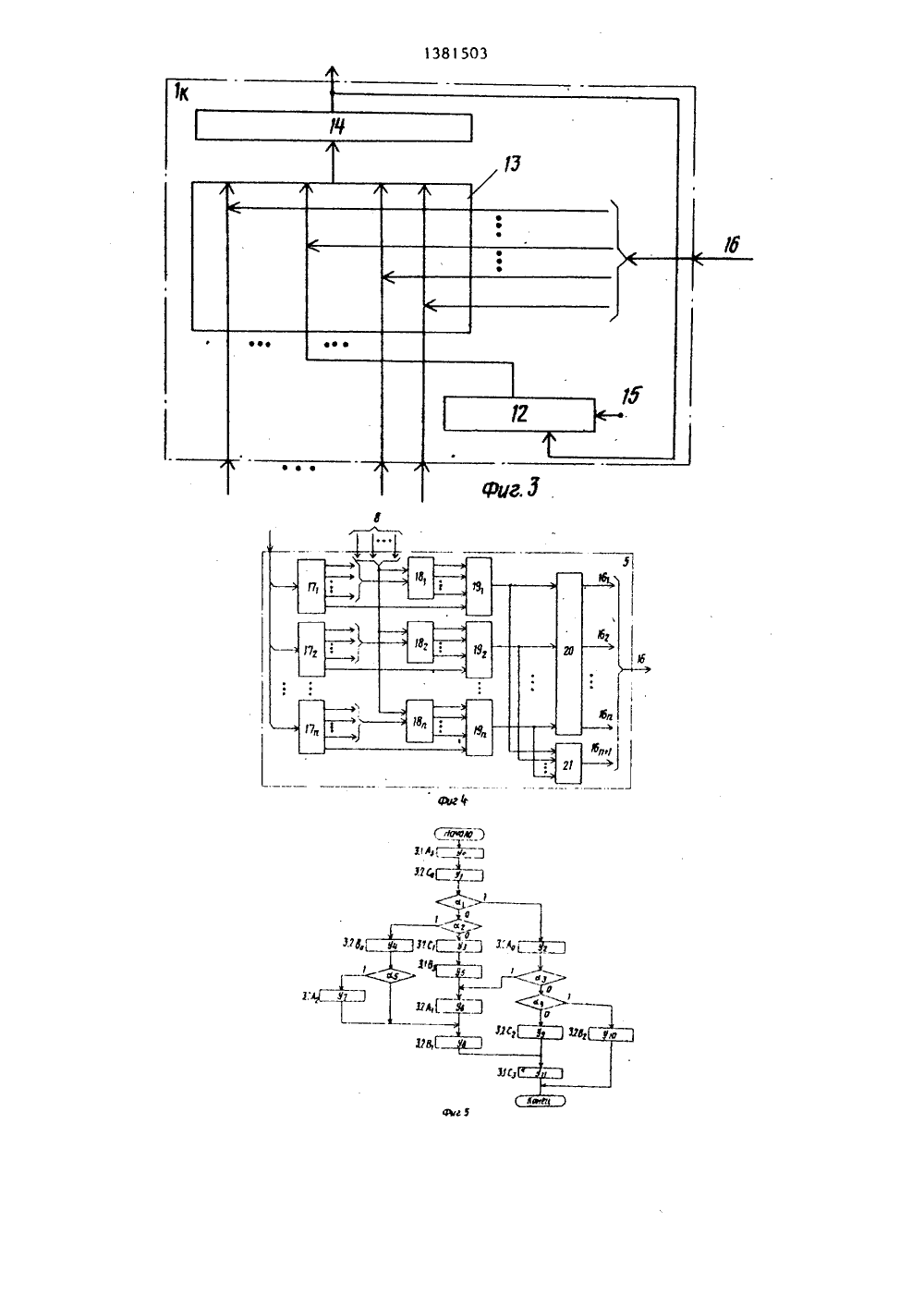

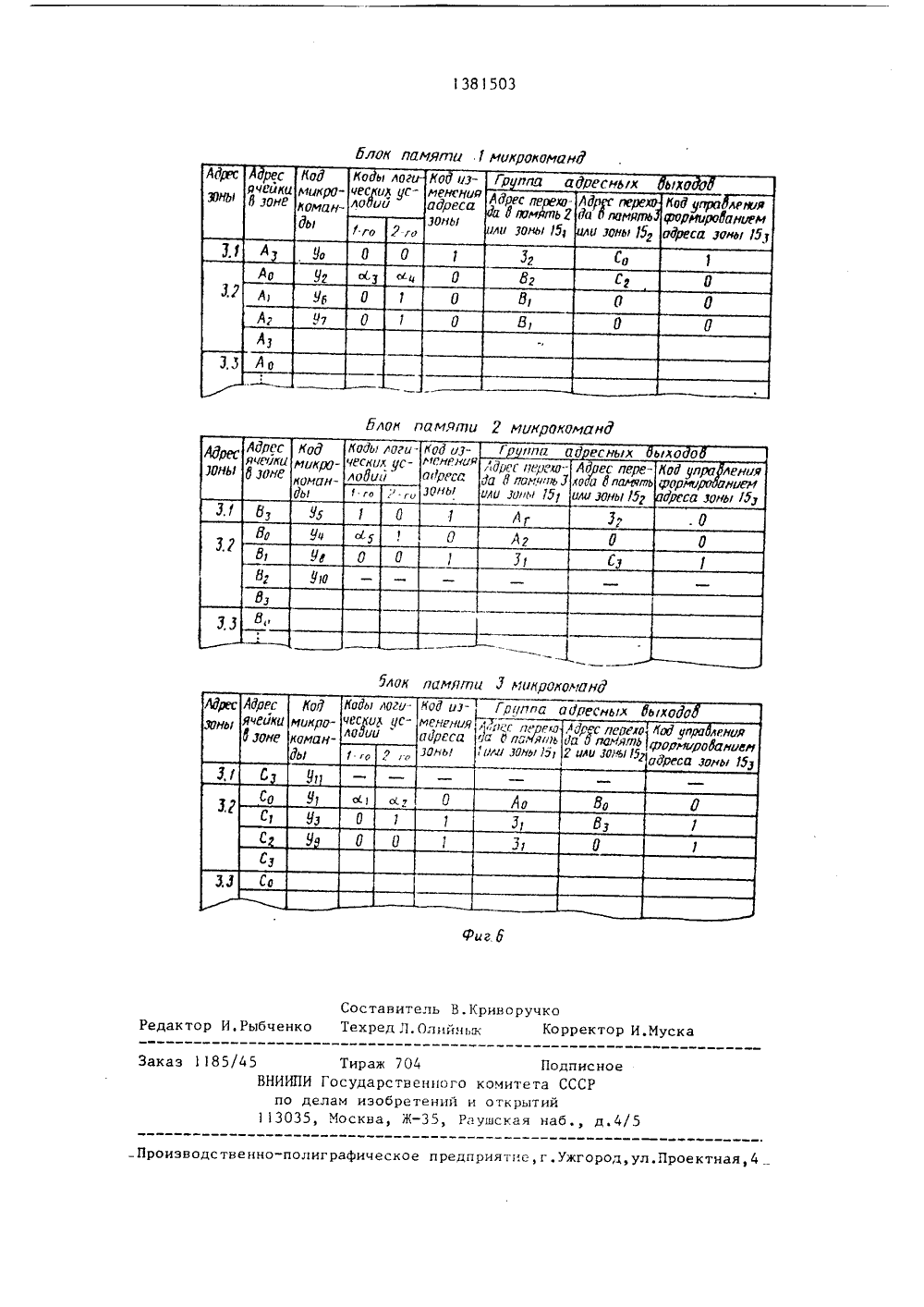

.,Ъ 74 УЩОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ическии инсти льство СССР 9/22, 1983, ство СССР 9/22, 1984. и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ(57) Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системахЦелью изобретенияявляется сокращение оборудования засчет сокращения разрядности адреснойчасти микрокоманд. Устройство содержит и+1 блоков 1 формирования адреса и+1 блоков 2 памяти микрокоманд,.коммутатор 3, регистр 4 микрокоманд,блок 5 проверки условий, блок 6 формирования адреса эоны. Указанная совокупность признаков позволяет достигнуть цели изобретения. 1 з.п.ф-лы40 45 5055 Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствахи системах,Целью изобретения является сокращение количества используемого оборудования за счет сокращения разрядности адресной части микрокоманд.На фиг. приведена структурнаясхема микропрограммного устройствауправления; на фиг,2 - функциональная схема, блока формирования адресаэоны; на фиг.З - схема блока формирования адреса; на фиг,4 ; схема блока проверки условий: на фиг.5 и 6пример граф-схемы микропрограммы ипринцип ее размещения в блоках памяти устройства для случая п=2.Микропрограммное устройство управления (фиг.1) содержит и+1 блоков1 - 1.формирования адреса и+1блоков 2, - 2 , памяти микрокоманд,коммутатор 3, регистр 4 микрокоманд,блок 5 проверки условий и блок 6 фор.мирования адреса зоны, выход 7 кодовмикроопераций и группу 8 входов логических условий устройства.Блок 6 формирования адреса эоны(фиг.2) содержит п+2 коммутаторов9, - 9, 10 и регистр 11.Блок формирования адреса (фиг,З)содержит комбинационный сумматор 12,коммутатор 13, регистр 14, вход 15переноса сумматора 12, на которыйзаведен сигнал логической единицы,Блок 5 проверки условий (фиг.4)содержит выход 16, и дешифраторов17 -17 и групп 18,-18 элементовИ и и элементов ИЛИ 19, - 19, шифратор 20 и элемент ИЛИ-НЕ 21.Работу устройства рассмотрим дляслучая п=2 при выполнении микропрограммы, граф-схема которой изображена на фиг.5. Размещение рассматриваемой микропрограммы в блоках 2-2 Впамяти микрокоманд устройства показано на фиг,6. Адреса ячеек памяти, вкоторых размещены микрокоманды(фиг.5 и 6) изображены в виде старших и младших разрядов, Старшие разряды образуют адрес зоны для всехблоков 2 памяти и обозначены через31 (1 " 1 . 3), а младшие разрядыобозначены через Ао-; А , Вот Вз иС, - С. соответственно для первого,второго и третьего блоков 2 т 2 па 1 3мяти микрокоманд. Предполагается,5 10 15 20 25 30 35 что отличие значений 3.1 от 3.1+1,(О . ш с 2) составляет единицу. Через У -У обозначены коды микроопераций, а через д., в . с - коды логических условий соответствующих микро- команд. При размещении микрокоманд в блоках памяти предлагаемого устройства предполагается, что зоны этих блоков состоят из четырех ячеек и что предыдущая размещенная микропрограмма заняла по три ячейки памяти в каждом блоке 2,-2 памяти.Адрес следующей микрокоманды может быть получен двумя способами. При формировании адреса первым способом необходимо, чтобы следующая микрокоманда находилась в той же зоне, что и предыдущая. Поэтому адрес зоны не изменяется, при этом код в поле изменения адреса зоны должен быть нулевым. Адрес внутри зоны следующей микрокоманды может быть при этом получен либо путем увеличения на единицу адреса внутри зоны предыдущей микрокоманды, если эта следующая микрокоманда размещается в том же блоке памяти, что и предыдущая, либо непосредственно путем указания в соответствующем поле кода адреса предыдущей микрокоманды, если следующая микрокоманда размещается в другом блоке памяти. При формировании адреса вторым способом следующая микрокоманда может находиться в любой другой зоне по отношению к 1 предыдущей. В этом случае адрес соответСтвующей зоны указывается вопределенных адресных полях предыдущей микрокоманды, а в поле изменения адреса зоны устанавливается единичный код. Адрес внутри зоны формируется так же, как и при первом способе, Необходимо отметить, что приформировании адреса вторым способом предыдущая микрокоманда не должна содержать проверки логических условий,Устройство работает следующим образом,Пусть в исходном состоянии разряды поля микроопераций обнуляются, а разряды поля логических условий устанавливаются в единичное состояние, в регистр первого блока 1 формирования адреса заносится адрес А , а в регистр блока формирования адреса зоны - адрес эоны 3,1 первой микрокоманды выполняемой микропрограммы (цепи занесения начальных адресов и установки в нулевое и единичное состояния соответствующих разрядов регистра 4 микрокоманд, а также цепи5 синхронизации не показаны). Так как на вход первого дешифратора 17 блока 5 проверки условий поступает единичный код, то на его дополнительном выходе устанавливается сигнал "1", который поступает через первый элемент ИЛИ 19, на первый вход шифратора 20. Поскольку этот вход имеет наивысший приоритет, то на первом выходе 16, блока 5 проверки условий устанавливается сигнал "1", на остальных выходах 16 - 16 устанавливаются сигналы О. Поэтому коммутатор 3 настраивается на выборку информации 20 с выхода первого блока 2 памяти иэ которого считывается микрокоманда по адресу 3,1 А ; коммутатор 1 О блока3формирования адреса зоны настраивается на выборку информации с выхода 25 первого коммутатора 19 , на первый вход которого с второго выхода группы выходов кода адреса первого блока 2 памяти поступает адрес С а на второй вход с первого выхода группы выходов кода адреса первого блока 2памяти - адрес новой зоны 3.2, который и передается на выход коммутатора 9 т.к, на его управляющий вход с третьего выхода группы выхо 35 дов кода адреса первого блока 2 памяти поступает сигнал "1" (на фиг.б в поле кода управления формированием адреса зоны считываемой микрокоманды установлен единичный код); коммута торы первого, второго и третьего блоков 1 - 1 формирования адреса на 3.страиваются на выборку информации соответственно с выхода сумматора . первого блока формирования адреса и 45 с первого и второго выходов группы выходов кода адреса первого блока 2, памяти. По синхросигналу, завершающему первый такт работы устройства, в регистр 4 записываются код микро- операций У и нулевые коды первого и второго логических условий (на. фиг.б обозначены как "0"), в регистры первого, второго и третьего блоков 1-1 З формирования адреса - со ответственно А 3.2 и С, так как на вход разрешения записи регистра блока 6 с второго выхода коммутатора 3 поступает сигнал "1" (на фиг.б в считываемой микрокоманде код изменения адреса зоны установлен н единичное состояние), то в регистр 11 записывается новый адрес зоны 3.2.Одновременно с выполнением микро- операций У из блоков 2 -2 памятио3 происходит чтение информации соответственно по адресам 3,2 А , 3.2 3.2ои 3.2 С, Но так как на входы первого и второго дешифраторов 17 и 17 блока 5 проверки условий поступают нулевые коды, то на выходе 16 блока 5 устанавливается сигнал ,а наи , 3 остальных выходах 16, - 16 - сигналы0 . Следовательно , коммутатор 3 нас траивае тс я на выборку информации с выхода третьего блока 2 З памяти , коммутатор 1 О блока формирования адреса зоны - с выхода третьего коммутатора 9 зно так к ак с второго выхода к оммутатора 3 на вход разрешения записи регистра 1 1 поступает сигнал " 0 " ( на фиг . б в считываемой микрокоманде У 1 код изменения адреса зоны установлен в нулевое состояние) , то по синх росигналу в этом регистре информация не меняе тся . Коммутаторы и е р во го , второго и третьего блоков 1 -. Фо р 3 мирования адреса настраиваются на выборку инфбрмации соответственно с первого и второго выходов группы выходов кода адреса третьего блока 2 памяти и сумматора третье 3го блока формирования адреса, Итак, по синхросигналу, завершающему второй такт работы устройства, в регистр 4 записываются код микроопераций У и коды ЙД соответственнопервого и второго логических условий, в регистре 11 блока формирования адреса эоны остается прежней адрес зоны 3.2, в регистры первого, второго и третьего блоков 1 - 1 формирования адреса записываются соответственно адреса А, В и С,.Одновременно с выполнением микро- операций У происходит чтение возможных следующих микрокоманд из блоков 2,-2 памяти соответственно по адресам 3.2 А , 3,2 В, и 3.2 С, . В зависимости от выполнения или не выполнения условий сА и д при выполне 1нии текущей микрокоманды на выходах 16-16, блока проверки условий устанавливаются следующие сигналы. Если первое логическое условие с выполняется, то на первом выходе 16, бло 138503ка проверки условий появляется сигнал "1", а на остальных выходах 6 16- сигналы "0", Поэтому по синхросигналу, завершающему третий такт работы устроиства, в регистр 4 запич5Юсываются код микроопераций Уи коды с 1. с соответственно первого и вто 5рого логических условий, в регистры первого, второго и третьего блоков- 1 формирования адреса записывают 3ся соответственно адреса А, В 2 и С1 ф а в регистре 11 блока формирования адреса эоны остается прежний адрес зоны 3.2, так как в считьваемой микрокоманде код изменения адреса зоны установлен в нулевое состояние (фиг.6). Если первое логическое условие д.,не выполняется, а выполняется второе логическое условие о , то на 20 выходе второго элемента ИЛИ 19 уста 2 навливается сигнал. Так как на первом более приоритетном входе шифратора 20 присутствует сигнал "0", на втором выходе 6блока проверки условий устанавливается сигнал "1", а на остальных его выходах 16 и 16 - сигнал "0". Поэтому по синхросигналу, завершающему третий такт работы устройства, в регистр 4 записьваются код микроопераций У , код1 д,. первого логического условия и еди 5ничный код второго логического условия на фиг,6 представлен как ), в регистры первого, второго и третьего блоков 1 - 1. формирования адреса353записываются соответственно адреса А, В и О, в регистре 11 блока формирования адреса зоны остается прежний адрес 30 ны 3,2 так как и В этОЙ 40 считываемой микрокоманде код изменения адреса зоны установлен в нулевое состояние. Если же и второе логичес" кое условие о не выполняется, то на выходах первого и второго элемен тов 19, 19 блока проверки условий устанавливаются сигналы "0". Следовательно, сигнал "1" устанавливается на выходе 16блока проверки условий, на остальных выходах 16 -16которого устанавливаются сигналы 0. По синхросигналу, завершающему третий такт работы устройства, в регистр 4 эаписьваются коды микроопераций Уз, нулевой код первого логического условия и единичный код второго логического условия, в регистры первого, второго и третьего блоков 1 1 З формирования адреса записываются соответственно адреса 3. 1, В 3 и Св регистрблока формирования адреса зоны записывается новый адрес эоны 3.1, поскольку в считываемой микрокоманде код изменения адреса зоны установлен в единичное состояние и в первом адресном поле указан адрес эоны 3.1. В данном случае в следующем такте работы устройства одновременно с выполнением микроопераций У из второго блока 2.2 памяти считьвается следующая микрокоманда по адресу 3.1 В . Далее устройство работает аналогйчно.При нулевом коде управления формированием адреса зоны значение адреса новой зоны следующей микрокоманды записывается во втором поле адресной части микрокоманд, первое поле при этом может исполЬзоваться как младшие разряды адреса этой следующей микрокоманды (например, на.фиг.5 и 6 пятая микрокоманда). При единичном коде управления формированием адреса зоны значение адреса новой зоны следующей микрокоманды записывается в первом поле адресной части микрокоманды, второе поле при этом может использоваться как младшие разряды адреса этой следующей микрокоманды (например, на фиг.5, 6 нулевая, третья и восьмая микрокоманды).ф о р м у л а и з о б р е т е н и я1. Микропрограммное устройство управления, содержащее и+1 (где и - количество одновременно проверяемых в микрокоманде логических условий) блоков формирования адреса, и+ блоков памяти мнкрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микроопераций регистра микрокоманд является одноименным выходом устройства, группа выходов логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, выход блока проверки условий соединен с управляющими входами с первого по (и+1)-й блоков формирования адреса и коммутатора, выход К-го (1 ( К ( п+) блока формирования адреса соединен с младшими разрядами адресных входов К-го блока памяти микрокоманд, 1-Й (Ып)выход группы выходов кода адреса которого соединен с К-м информационным входом (д+1)-го блока формирования адреса (для всех значений д ) К) и с (К)-м информационным входом "го5 блока формирования адреса (для всех значений д ( К), первый выход коммутатора соединен с информационным входом регистра микрокоманд, о т л и - 1 О ч а ю щ е е с я тем, что, с целью сокращения количества оборудования за счет сокращения разрядности адресной части микрокоманд, устройство содержит блок формирования адреса эо ны, причем выход блока формирования адреса эоны соединен со старшими разрядами адресных входов с первого по (и+1)-й блоков памяти микрокоманд, выход кодов микроопераций, логичес ких условий и признаков изменения адреса зоны К-го блока памяти микрокоманд соединен с К-м информационным входом коммутатора, второй выход которого соединен с первым управляющим 25 входом блока формирования адреса зоны, второй управляющий вход которого соединен с выходом блока проверки условий,п+ выходов группы выходов кода адреса К-го блока памяти микрокоманд соединены соответственно с(и+1)-ми входами К-й группы информационных входов блока формированияадреса эоны. 2, Устройство по п,1, о т л и - ч а ю щ е е с я тем, что блок формирования адреса эоны содержит и+2 коммутаторов и регистр, причем выход К-го (1Ки+1) коммутатора соединен с К-м информационным входом (и+2)-го коммутатора, выход которого соедйнен с информационньи входом регистра, выход которого является выходом блока, д-я (1 ( ь ( и) группа информационных входов К"го коммутатора соединена соответственно со всеми входами К-й группы информационньм входов блока, кроме д-го и (и+1)- го, управляющий вход К-го коммутатора соединен с (и+1)-м входом К-й группы информационных входов блока, вход разрешения записи регистра соединен с первым управляющим входом блока, второй управляющий вход которого соединен с управляющим входом (и+2)-го коммутатора.1381503 блок памятц 1 мцироко блок па мяли 2 мцкрокомаид лок памяти У микрокодафиг оСоставитель В.Криворучко Редактор И.Рыбченко Техред Л.Олийнык Корректор И.Муска Заказ 1185/45 Тираж 704 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий13035, Москва, Ж, Раушская наб., д.4/5 Производственно-полиграфическое предприятие,г.ужгород,ул.Проектная,4.

СмотретьЗаявка

3975580, 08.10.1985

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

СОЛОВЕЙ АЛЕКСАНДР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/7-1381503-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Цифровой умножитель частоты

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ изготовления гидрофобных цементов