Аналого-цифровая вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

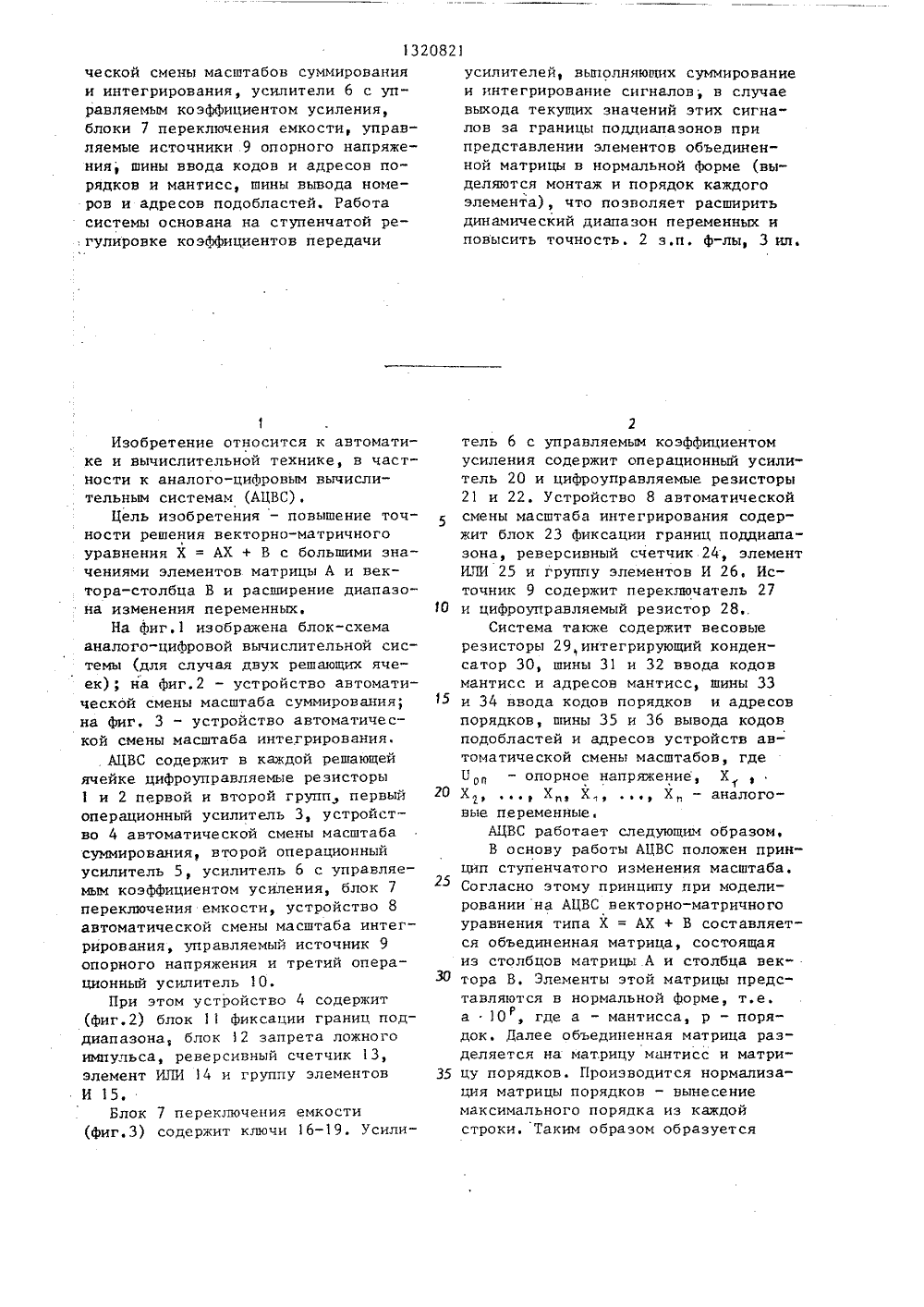

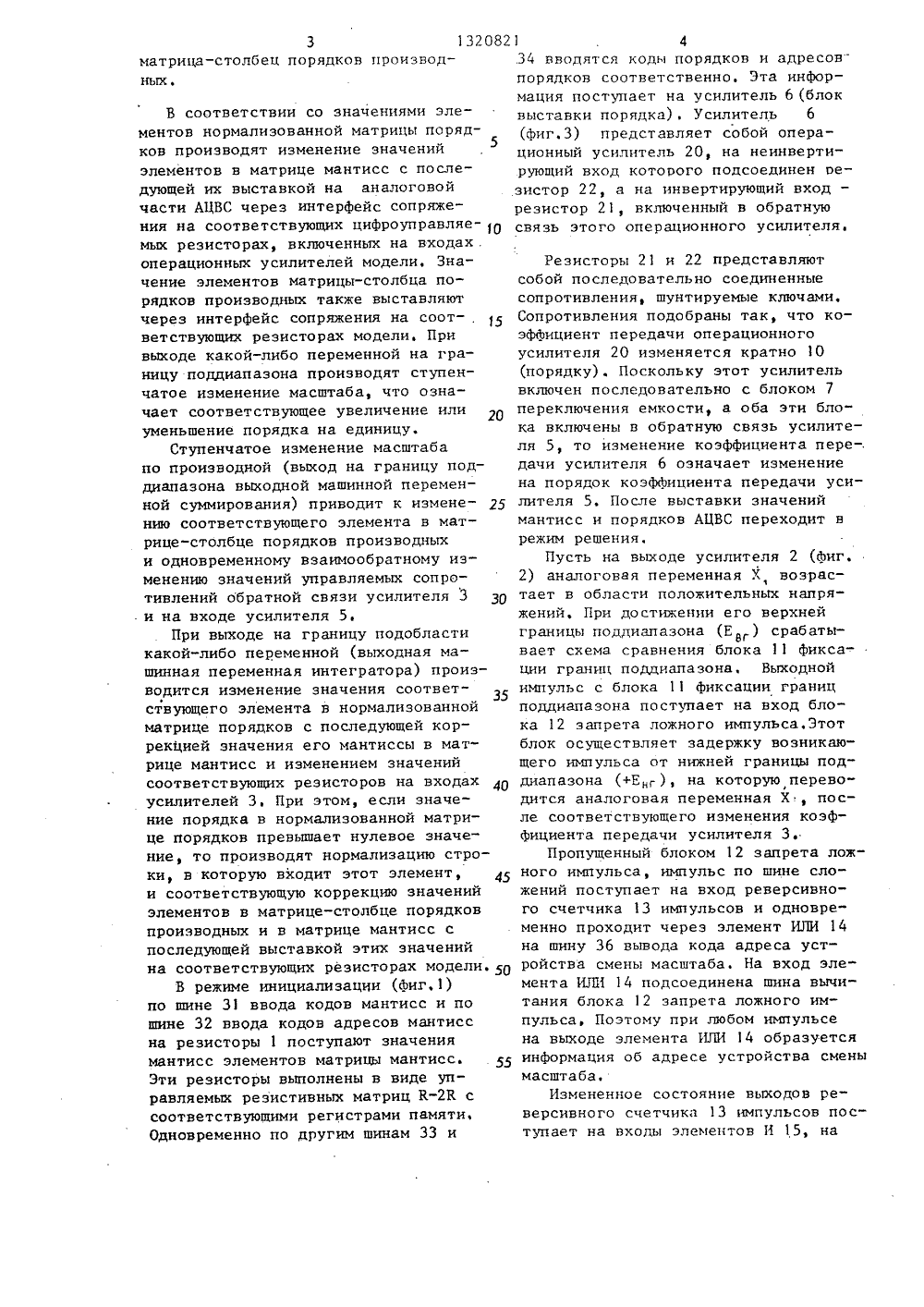

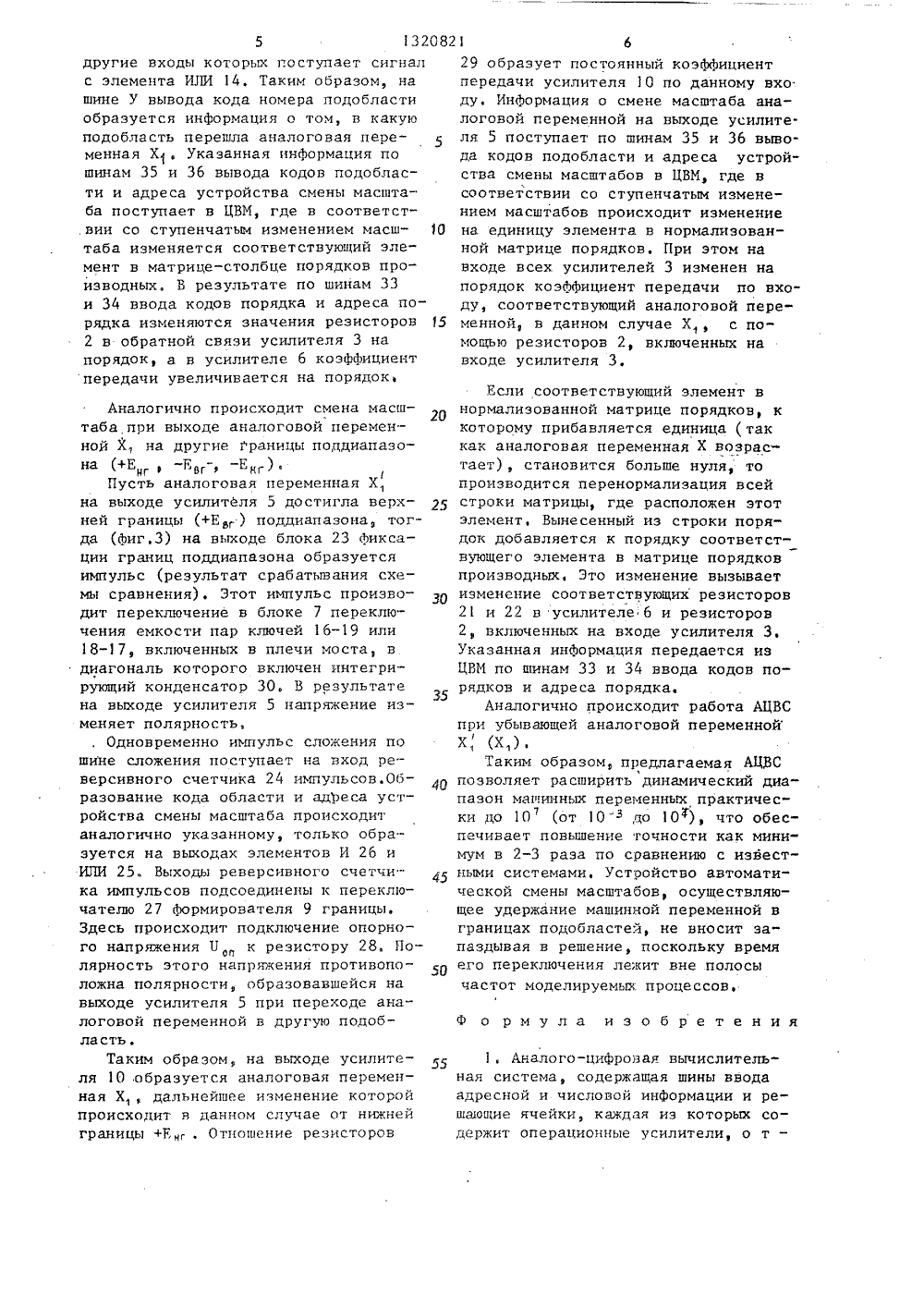

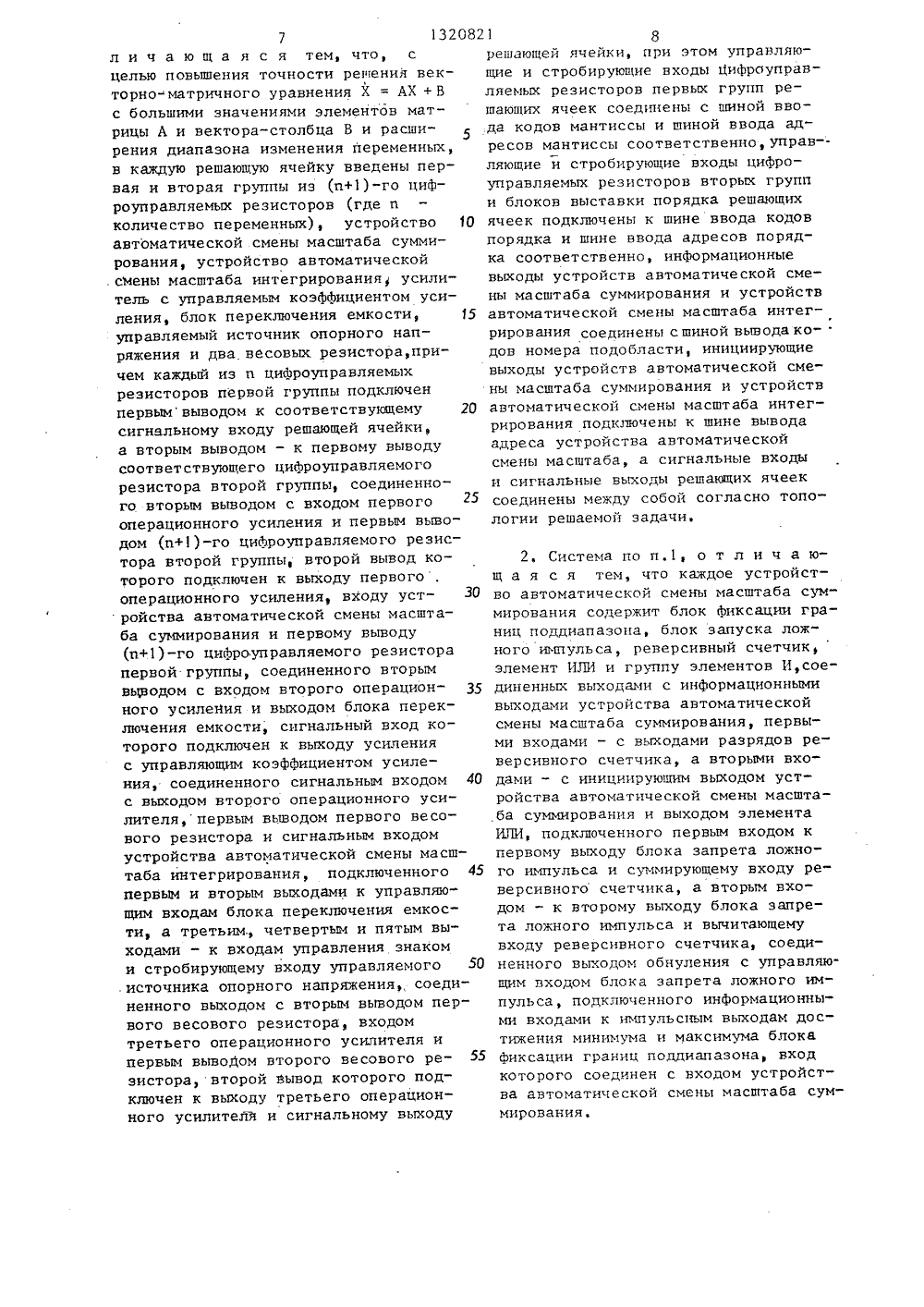

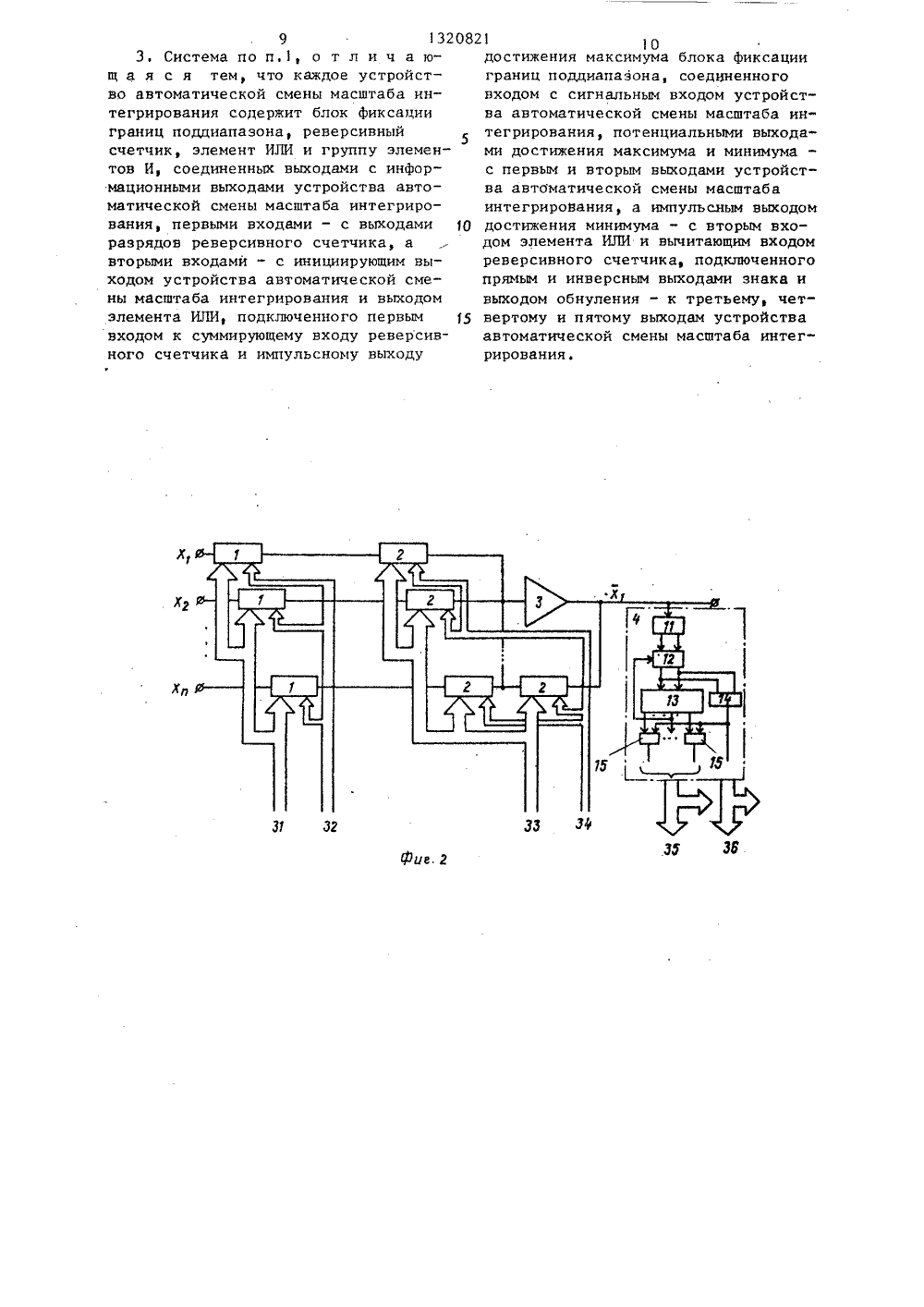

(57)автомЦельти ре тся к облас ьной техник тики и вычислите зобретения - пов ения векторно-ма Х = АХ + В с бол ппение точносричного уравшими значенияни и вектора - диапазона из алого-циЬрова содержит ци1 и 2 первых ментов м рицы А ирение столбца менения и расшеременльная вычисли ист зист емые роуправи вторыхли 3,5,онные усилите,8 автоматиоп групп,О, устр гг хр иства ззг зз жззз Фис. уГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВТОРСКОМУ СВИДТЕЛЬСТ(21) 3879688/24-24 (22) 02 ь 04 с 85 (46) 30.06 е 87.Бюл. В 24. (72) Е,И,Баду, В.В.Дубаренко и В.М.Перепеч (53) 682,335 (088.8) (56) Авторское свидетельство СССР 9 801005, кл. С 06 С 7/38, 1 972,Силаев Е.В, и др. Создание аналого-цифрового комплекса на базе СМи АВКдля проектирования цийровых систем управления. Харьковский политехнический институт, Харьков, 1983, Рукопись депонирована в УкрНИНТИ, В 640-Уп-Д 83. Деп, от 29.06,83,сг гп 801320821 А 11320821ческой смены масштабов суммирования и интегрирования, усилители б с управляемым коэффициентом усиления,блоки 7 переключения емкости, управляемые источники 9 опорного напряжения, шины ввода кодов и адресов порядков и мантисс, шины вывода номеров и адресов подобластей. Работа системы основана на ступенчатой регулировке коэффициентов передачи усилителей, выполняющих суммированиеи интегрирование сигналов, в случаевыхода текущих значений этих сигналов за границы поддиапазонов припредставлении элементов объединенной матрицы в нормальной форме (выделяются монтаж и порядок каждогоэлемента), что позволяет расширитьдинамический диапазон переменных иповысить точность. 2 з.п, ф-лы, 3 ил.1Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровым вычислительным системам (АЦВС),Цель изобретения - повышение точности решения векторно-матричногоуравнения Х = АХ + В с большими значениями элементов матрицы А и вектора-столбца В и расширение диапазона изменения переменных.На фиг.1 изображена блок-схемааналого-цифровой вычислительной системы (для случая двух решающих ячеек); на фиг.2 - устройство автоматической смены масштаба суммирования;на фиг. 3 - устройство автоматической смены масштаба интегрирования.. АЦВС содержит в каждой решающейячейке цифроуправляемые резисторы1 и 2 первой и второй групп первыйоперационный усилитель 3, устройст -во 4 автоматической смены масштабасуммирования, второй операционныйусилитель 5, усилитель 6 с управляемым коэффициентом усиления, блок 7переключения емкости, устройство 8автоматической смены масштаба интегрирования, управляемый источник 9опорного напряжения и третий операционный усилитель 10.При этом устройство 4 содержит(фиг.3) содержит ключи 16-19. Усили 2тель 6 с управляемым коэффициентомусиления содержит операционный усилитель 20 и цифроуправляемые резисторы21 и 22. Устройство 8 автоматической5 смены масштаба интегрирования содержит блок 23 фиксации границ поддиапаэона, реверсивный счетчик 24, элементИЛИ 25 и группу элементов И 26, Источник 9 содержит переключатель 2710 и цифроуправляемый резистор 28.Система также содержит весовыерезисторы 29 интегрирующий конденсатор 30, шины 31 и 32 ввода кодовмантисс и адресов мантисс, шины 33и 34 ввода кодов порядков и адресовпорядков, шины 35 и 36 вывода кодовподобластей и адресов устройств автоматической смены масштабов, где11 р - опорное напряжение, Х 1.Хгю Хпе Х. , Х - аналоговые переменные,АЦВС работает следующим образом.В основу работы АЦВС положен принцип ступенчатого изменения масштаба,Согласно этому принципу при моделировании на АЦВС векторно-матричногоуравнения типа Х = АХ + В составляется объединенная матрица, состоящаяиз столбцов матрицы А и столбца век 30 тора В, Элементы этой матрицы представляются в нормальной форме, т.е.а 10 , где а - мантисса, р - порядок. Далее объединенная матрица разделяется на матрицу мантисс и матри 35 цу порядков. Производится нормализация матрицы порядков - вынесениемаксимального порядка из каждойстроки, Таким образом образуется3 132082 матрица-столбец порядков производВ соответствии со значениями элементов нормализованной матрицы порядков производят изменение значенийэлементов в матрице мантисс с последующей их выставкой на аналоговойчасти АЦВС через интерфейс сопряжения на соответствующих цифроуправляемых резисторах, включенных на входахоперационных усилителей модели. Значение элементов матрицы-столбца порядков производных также выставляютчерез интерфейс сопряжения на соот-,ветствующих резисторах модели. Привыходе какой-либо переменной на границу поддиапазона производят ступенчатое изменение масштаба, что означает соответствующее увеличение илиуменьшение порядка на единицу.Ступенчатое изменение масштабапо производной (выход на границу поддиапазона выходной машинной переменной суммирования) приводит к изменению соответствующего элемента в матрице-столбце порядков производныхи одновременному взаимообратному изменению значений управляемых сопротивлений обратной связи усилителя 3 30и на входе усилителя 5,При выходе на границу подобластикакой-либо переменной (выходная машинная переменная интегратора) производится изменение значения соответствующего элемента в нормализованнойматрице порядков с последующей коррекцией значения его мантиссы в матрице мантисс и изменением значенийсоответствующих резисторов на входахусилителей 3, При этом, если значение порядка в нормализованной матрице порядков превышает нулевое значение, то производят нормализацию строки, в которую входит этот элемент,и соответствующую коррекцию значенийэлементов в матрице-столбце порядковпроизводных и в матрице мантисс споследующей выставкой этих значенийна соответствующих резисторах модели. 50В режиме инициализации (фиг.1)по шине 31 ввода кодов мантисс и пошине 32 ввода кодов адресов мантиссна резисторы 1 поступают значениямантисс элементов матрицы мантисс.Эти резисторы выполнены в виде управляемых резистивных матриц КК ссоответствующими регистрами памяти,Одновременно по другим шинам 33 и 1 4.34 вводятся коды порядков и адресовпорядков соответственно. Эта информация поступает на усилитель 6 (блоквыставки порядка), Усилитель 6(фиг.3) представляет собой операционный усилитель 20, на неинвертирующий вход которого подсоединен оезистор 22, а на инвертирующий вход -резистор 21, включенный в обратнуюсвязь этого операционного усилителя,Резисторы 21 и 22 представляют собой последовательно соединенные сопротивления шунтируемые ключами. Сопротивления подобраны так, что коэффициент передачи операционного усилителя 20 изменяется кратно 10 (порядку). Поскольку этот усилитель включен последовательно с блоком 7 переключения емкости, а оба эти блока включены в обратную связь усилителя 5, то изменение коэффициента пере-. дачи усилителя 6 означает изменение на порядок коэффициента передачи усилителя 5. После выставки значений мантисс и порядков АЦВС переходит в режим решения.Пусть на выходе усилителя 2 (фиг.2) аналоговая переменная Х воэрастает в области положительных напряжений. При достижении его верхней границы поддиапазона (Е г) срабатывает схема сравнения блока 11 фиксации границ поддиапазона. Выходной импульс с блока 11 фиксации границ поддиапазона поступает на вход блока 12 запрета ложного импульса. Этот блок осуществляет задержку возникающего импульса от нижней границы поддиапазона (+Е), на которую переводится аналоговая переменная Х , после соответствующего изменения коэффициента передачи усилителя 3.Пропущенный блоком 12 запрета ложного импульса, импульс по шине сложений поступает на вход реверсивного счетчика 13 импульсов и одновременно проходит через элемент ИЛИ 14 на шину 36 вывода кода адреса устройства смены масштаба. На вход элемента ИЛИ 14 подсоединена шина вычитания блока 12 запрета ложного импульса, Поэтому при любом импульсе на выходе элемента ИЛИ 14 образуется информация об адресе устройства смены масштаба,Измененное состояние выходов реверсивного счетчик 13 импульсов поступает на входы элементов И 15, на5 10 15 другие входы которых поступает сигналс элемента ИЛИ 14, Таким образом, нашине У вывода кода номера подобластиобразуется информация о том, в какуюподобласть перешла аналоговая переменная Х 1, Укаэанная информация пошинам 35 и 36 вывода кодов подобласти и адреса устройства смены масштаба поступает в ЦВМ, где в соответст.вии со ступенчатым изменением масштаба изменяется соответствующий элемент в матрице-столбце порядков производных. В результате по шинам 33и 34 ввода кодов порядка и адреса порядка изменяются значения резисторов2 в обратной связи усилителя 3 напорядок, а в усилителе 6 коэффициентпередачи увеличивается на порядок,Аналогично происходит смена масштаба при выходе аналоговой переменной Х на другие границы поддиапазона (+Е Епр у Епг)"Пусть аналоговая переменная Хна выходе усилителя 5 достигла верхней границы (+Е ) поддиапазона, тогда (Фиг.3) на выходе блока 23 Фиксации границ поддиапазона образуетсяимпульс (результат срабатывания схемы сравнения). Этот импульс производит переключение в блоке 7 переключения емкости пар ключей 16-19 или18-17, включенных в плечи моста, вдиагональ которого включен интегрирующий конденсатор 30. В результатена выходе усилителя 5 напряжение изменяет полярность,Одновременно импульс сложения пошине сложения поступает на вход реверсивного счетчика 24 импульсов.06 разование кода области и адреса устройства смены масштаба происходитаналогично указанному, только образуется на выходах элементов И 26 иИПИ 25. Выходы реверсивного счетчика импульсов подсоединены к переключателю 27 Формирователя 9 границы,Здесь происходит подключение опорного напряжения Б к резистору 28. Полярность этого напряжения противоположна полярности, образовавшейся навыходе усилителя 5 при переходе аналоговой переменной в другую подобласть.Таким образом, на выходе усилителя 10 образуется аналоговая переменная Х дальнейшее изменение которойпроисходит в данном случае от нижнейграницы +Е нгОтполцеиие резисторов 29 образует постоянный коэффициентпередачи усилителя 10 по данному входу, Информация о смене масштаба аналоговой переменной на выходе усилите.ля 5 поступает по шинам 35 и 36 вывода кодов подобласти и адреса устройства смены масштабов в ЦВМ, где всоответствии со ступенчатым изменением масштабов происходит изменениена единицу элемента в нормализованной матрице порядков. При этом навходе всех усилителей 3 изменен напорядок коэффициент передачи по входу, соответствующий аналоговой переменной, в данном случае Х, с помощью резисторов 2, включенных навходе усилителя 3. Если соответствующий элемент в нормализованной матрице порядков, к которому прибавляется единица ( так как аналоговая переменная Х возрастает), становится больше нуля, то производится перенормализация всей строки матрицы, где расположен этот элемент, Вынесенный из строки порядок добавляется к порядку соответствующего элемента в матрице порядков производных, Это изменение вызывает изменение соответствующих резисторов 2 и 22 в усилителе 6 и резисторов 2, включенных на входе усилителя 3, Укаэанная информация передается из ЦРМ по шинам 33 и 34 ввода кодов порядков и адреса порядка.Аналогично происходит работа АЦВС при убывающей аналоговой переменной Х (Х) .Таким образом, предлагаемая АЦВС позволяет расширить динамический диапазон машинных переменных практически до 10 (от 10 з до 10"), что обеспечивает повьппение точности как минимум в 2-3 раза по сравнению с известными системами, Устройство автоматической смены масштабов, осуществляющее удержание машинной переменной в границах подобласте.л, не вносит запаздывая в решение, поскольку время его переключения лежит вне полосы частот моделируемых процессов,Ф о рмула изобретения 1, Аналого-цифровая вычислительная система, содержащая шины ввода адресной и числовой информации и решающие ячейки, каждая из которых содержит операционные усилители, о т -7 13208 л и ч а ю щ а я с я тем что, с целью повышения точности решения векторно-матричного уравнения Х = АХ + В с большими значениями элементов матрицы А и вектора-столбца В и расши 5 рения диапазона изменения переменных, в каждую решающую ячейку введены первая и вторая группы из (и+1)-го циф - роуправляемых резисторов (где пколичество переменных), устройство 10 автоматической смены масштаба суммирования, устройство автоматической смены масштаба интегрирования усилитель с управляемым коэффициентом усиления, блок переключения емкости, 15 управляемый источник опорного напряжения и два весовых резистора,причем каждый из и цифроуправляемых резисторов первой группы подключен первымвыводом к соответствующему 20 сигнальному входу решающей ячейки, а вторым выводом - к первому выводу соответствующего цифроуправляемого резистора второй группы, соединенного вторым выводом с входом первого 25 операционного усиления и первым выводом (и+1)-го цифроуправляемого резистора второй группы, второй вывод которого подключен к выходу первого операционного усиления, входу уст- ЗО ройства автоматической смены масштаба суммирования и первому выводу (и+1)-го цифроуправляемого резистора первой группы, соединенного вторым выводом с входом второго операцион ного усилеиия и выходом блока переключения емкости, сигнальный вход которого подключен к выходу усиления с управляющим коэффициентом усиления, соединенного сигнальным входом 40 с выходом второго операционного усилителя,первым выводом первого весового резистора и сигнальным входом устройства автоматической смены масштаба интегрирования, подключенного 45 первым и вторым выходами к управляющим входам блока переключения емкости, а третьим., четвертым и пятым выходами - к входам управления знаком и стробирующему входу управляемого 50 источника опорного напряжения, соединенного выходом с вторым выводом первого весового резистора входомтретьего операционного усилителя и первым вывоДом второго весового ре зистора, второй вывод которого подключен к выходу третьего операционного усилителя и сигнальному выходу 21 8решающей ячейки, при этом управляющие и стробирующие входы Оифрауправляемых резисторов первых групп решающих ячеек соединены с шиной ввода кодов мантиссы и шиной ввода адресов мантиссы соответственно, управ ляющие и стробирующие входы цифроуправляемых резисторов вторых групп и блоков выставки порядка решающих ячеек подключены к шине ввода кодов порядка и шине ввода адресов порядка соответственно, информационные выходы устройств автоматической смены масштаба суммирования и устройств автоматической смены масштаба интегрирования соединены с шиной вывода ко- . дов номера подобласти, инициирующие выходы устройств автоматической смены масштаба суммирования и устройств автоматической смены масштаба интегрирования подключены к шине вывода адреса устройства автоматической смены масштаба, а сигнальные входы и сигнальные выходы решающих ячеек соединены между собой согласно топологии решаемой задачи. 2. Система по п.1, о т л и ч а ющ а я с я тем, что каждое устройство автоматической смены масштаба суммирования содержит блок фиксации границ поддиапазона блок запуска ложного импульса, реверснвный счетчик,элемент ИЛИ и группу элементов И,соединенных выходами с информационнымивыходами устройства автоматическойсмены масштаба суммирования, первыми входами - с выходами разрядов реверсивного счетчика, а вторыми входами - с инициирующим выходом устройства автоматической смены масштаба суммирования и выходом элементаИЛИ, подключенного первым входом кпервому выходу блока запрета ложного импульса и суммирующему входу реверсивного счетчика, а вторым входом - к второму выходу блока запрета ложного импульса н вычитающемувходу реверсивного счетчика, соединенного выходом обнуления с управляющим входом блока запрета ложного импульса, подключенного информационными входами к импульсным выходам достижения минимума и максимума блокафиксации границ поддиапазона, входкоторого соединен с входом устройства автоматической смены масштаба суммирования, 9 1323. Система по и1, о т л и ч а ющ а я с я тем, что каждое устройство автоматической смены масштаба интегрирования содержит блок фиксации границ поддиапаэона, реверсивный счетчик, элемент ИЛИ и группу элементов И, соединенных выходами с информационными выходами устройства автоматической смены масштаба интегрирования, первыми входами - с выходами раэрядов реверсивного счетчика, а вторыми входами - с инициирующим выходом устройства автоматической смены масштаба интегрирования и выходом элемента ИЛИ, подключенного первым входом к суммирующему входу реверсивного счетчика и импульсному выходу 08211 Одостижения максимума блока фиксации границ поддиапазона, соедИненного входом с сигнальным входом устройства автоматической смены масштаба интегрирования, потенциальными выходами достижения максимума и минимумас первым и вторым выходами устройства автоматической смены масштаба интегрирования, а импульсным выходом 10 достижения минимума - с вторым входом элемента ИЛИ и вычитающим входом реверсивного счетчика, подключенного прямым и инверсным выходами знака и выходом обнуления - к третьему, чет вертому и пятому выходам устройстваавтоматической смены масштаба интег"рирования.1320821 Фис. 3 Составитель С. КазиновТехред Н.Глущенко Редактор И. Касарда Корректор С,Шекмар Заказ 2660/52 Тираж 672 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д,4/5 Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная, 4

СмотретьЗаявка

3879688, 02.04.1985

ПРЕДПРИЯТИЕ ПЯ Р-6896

БАДУ ЕФИМ ИОСИФОВИЧ, ДУБАРЕНКО ВЛАДИМИР ВАСИЛЬЕВИЧ, ПЕРЕПЕЧ ВЛАДИМИР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/38

Метки: аналого-цифровая, вычислительная

Опубликовано: 30.06.1987

Код ссылки

<a href="https://patents.su/7-1320821-analogo-cifrovaya-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровая вычислительная система</a>

Предыдущий патент: Устройство для решения систем алгебраических уравнений

Следующий патент: Устройство для измерения вероятностных характеристик фазы случайного сигнала

Случайный патент: Машина для отделки боковых краев поясных ремней