Широкодиапазонный калибратор фазовых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1226339

Автор: Батуревич

Текст

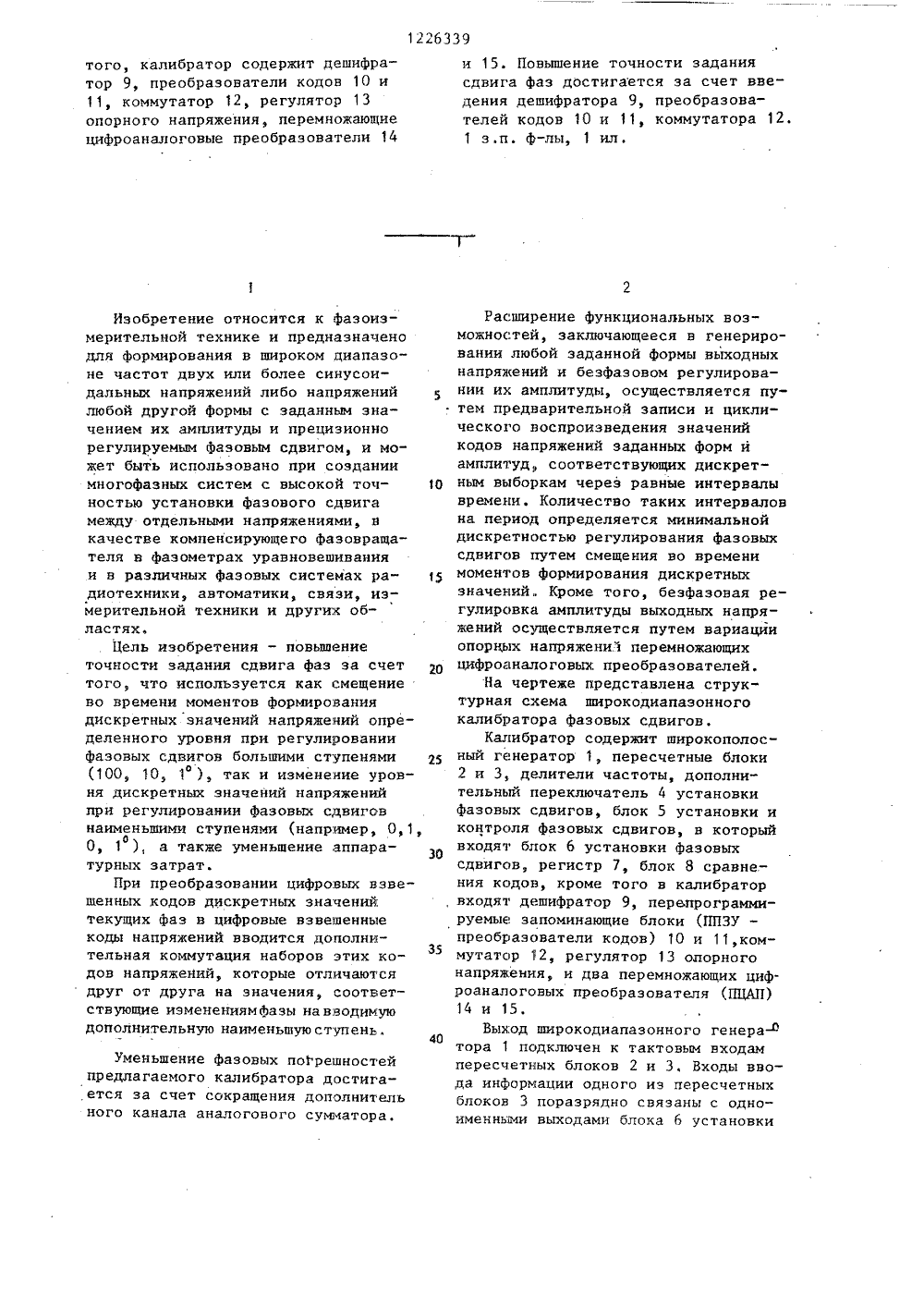

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУ БЛИН 801226339 А ав С 01 К 25/04 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬТИЙ(22) 20,11.84 диапазоне частот двух или более синусоидальных напряжений, или напряжений любой другой формы с заданнымзначением их амплитуды и прецизионно регулируемым фазовым сдвигом,а также при создании многофазныхсистем с высокой точностью установ-ки фазового сдвига между отдельныминапряжениями в качестве компенсирующего фазовращателя в фазометрахуравновешивания. Цель изобретения -ловьипение точности задания сдвигафаз. Калибратор содержит широкополосный генератор 1, делители частоты 2 и 3, переключатель 4 установки фазовых сдвигов, в который входят,блок 6 установки фазовых сдвигов,регистр 7, блок 8 сравнения. Кроме(56) Авторское свидетельство СССРУ 434332, кл . С О 1 К 25/04, 1974.Авторское свидетельство СССРУ 702506, кл. С 01 К 25 И 4, 1979.(54) ШИРОКОДИАПАЗОННЫЙ КАЛИБРАТОРФАЗОВЬИ СДВИГОВ(57) Изобретение может быть использовано для Формирования в широкомтого, калибратор содержит дешифратор 9, преобразователи кодов 10 и11, коммутатор 12, регулятор 13опорного напряжения, перемножающиецифроаналоговые преобразователи 14 1226339 и 15. Повышение точности заданиясдвига Фаз достигается за счет введения дешифратора 9, преобразователей кодов 10 и 11, коммутатора 12.1 э.п. Ф-лы, 1 ил.Изобретение относится к Фаэоизмерительной технике и предназначено для формирования в широком диапазоне частот двух или более синусоидальных напряжений либо напряжений любой другой Формы с заданным значением их амплитуды и прецизионно регулируемым Фазовым сдвигом, и может быть использовано при создании многофазных систем с высокой точ- О ностью установки Фазового сдвига между отдельными напряжениями, в качестве компенсирующего фазовращателя в Фазометрах уравновешивания и в различных Фазовых системах радиотехники, автоматики, связи, измерительной техники и других областях.Цель изобретения - повышение точности задания сдвига Фаз за счет того, что используется как смещение во времени моментов Формирования дискретных значений напряжений определенного уровня при регулировании фазовых сдвигов большими ступенями д (100, 10, 1 ), так и изменение уровня дискретных значений напряжений при регулировании Фазовых сдвигов наименьшими ступенями (например, О, 1,оО, 1 ), а также уменьшение аппаратурных затрат.При преобразовании цифровых взвешенных кодов дискретных значений текущих фаз в цифровые взвешенные коды напряжений вводится дополнительная коммутация наборов этих ко 35 дов напряжений, которые отличаются друг от друга на значения, соответствующие изменениямфазы навводимую дополнительную наименьшую ступень.40Уменьшение Фазовых погрешностейпредлагаемого калибратора достигается за счет сокращения дополнитель ного канала аналогового сумматора. Расширение функциональных воэможностей, заключающееся в генерировании любой заданной формы выходных напряжений и беэфазовом регулировании их амплитуды, осуществляется путем предварительной записи и циклического воспроизведения значений кодов напряжений заданных форм и амплитуд соответствующих дискретным выборкам через равные интервалы времени. Количество таких интервалов на период определяется минимальной дискретностью регулирования фазовых сдвигов путем смещения во времени моментов формирования дискретных значений,. Кроме того, безфаэовая регулировка амплитуды выходных напряжений осуществляется путем вариации опорах напряжениЛ перемножающих цифроаналоговых преобразователей.На чертеже представлена структурная схема широкодиапаэонного калибратора фазовых сдвигов,Калибратор содержит широкополосный генератор 1, пересчетные блоки 2 и 3, делители частоты, дополнительный переключатель 4 установки фазовых сдвигов, блок 5 установки и контроля фазовых сдвигов, в который входят блок 6 установки фазовых сдвигов, регистр 7, блок 8 сравнения кодов, кроме того в калибратор входят дешифратор 9, перепрограммируемые запоминающие блоки (ППЗУ - преобразователи кодов) 10 и 11,коммутатор 12, регулятор 13 олорного напряжения, и два перемножающих цифроаналоговых преобразователя (ПЦАП) 14 и 15.Выход широкодиапазонного генера тора 1 подключен к тактовым входам пересчетных блоков 2 и 3, Входы ввода информации одного иэ пересчетных блоков 3 поразрядно связаны с одноименными выходами блока б установкифазового сдвига. К этим же выходам подсоединена первая группа входов блока 8 сравнения, Вторая группа входов подключена к выходам регистра 7 памяти, информационные входы которо го соединены с выходами разрядов пересчетного блока 3, а вход записи связан с выходом заполнения пере- счетного блока 2, в качестве которогоможет служить его старший разряд. 10 Выход блока 8 сравнения кодов подключен к входу блока 6 управления установки фазового сдвига. Информа.ционные выходы разрядов пересчет- ного блока 2 соединены с входами 15 преобразователя 10 кодов, выходы которого связаны с цифровыми входами перемножающего цифроаналогового преобразователя 14, выход которого является выходом опорного канала 20 широкодиапазонного калибратора фазовых сдвигов. Информационные выходы разрядов пересчетного блока 3 подключены к информационным входам дешифратора 9, имеющего ц групп ин формационных выходов. К каждой группе выходов подсоединены входы преобразователей 11,1-11,и кодов,выходы которых связаны с таким же количеством информационных входов коммутатора 12. Выходы этого коммутатора в свою очередт подключены к цифровым входам перемножающего цифроаналогового преобразователя 15, выход которого является выходом регулируемого канала широ 15 одиапазонного калибратора фазовых сдвигов.В устройство может быть введен некоммутируемый преобразователь 1 1 О кодовинформационные Входы ко 40 торого соединены с выходами разрядов пересчетного блока 3, а выходы связаны с входами старших р разрядов перемножающего в -разрядного цифроаналогового преобразователя, Остальные в- разряды преобразователя подключены к выходам коммутатора 12. Одноименные входы управления дешифратора 9 и коммутатора 12 соединены между собой и связаны с дополнительным переключателем 4 установки фазового сдвига. Аналоговые входы перемножающих цифроаналоговых преобразователей 14 и 15 подключены кдвижкам регулируемых резисторов 55 регулятора 13, питаемого от источника постоянного опорного напряжения "о Устройство работает следующим образом.Непрерывная последовательность импульсов, формируемых широкодиапазонным генератором 1, поступает на тактовые входы пересчетных блоков 2 и 3. Частота повторения импульсов т генератора 1 превышает частотту выходных напряжений Г широкодиапазонного калибратора Фазовых сдвигов в ь раз1,=е ггде ь - коэффициент деления частоты пересчетных блоков 2 и 3 и максимальное количество интервалов аппроксимации выходных напряжений, приходящихся на их период, Коэффициент деления частоты 1 устанавливает также промежуточное значение дискрета регулирования фазовых сдвигов Ц, Изменение фазовых сдвигов калибратора , на значения, кратные д осуществляется путем вариации стационарных значений начальных фаз пересчетных блоков 2 и 3, используемых как управляемые делители частоты где К - код старших разрядов Фазового сдвига, задаваемьн блоком 6установки фазового сдвига и изменяющийся в пределах О --1.Для обеспечения высокой точностивоспроизведения дискретных значенийвыходных напряжений и высокой раз"решающей способности по фазе значение 3 целесообразно увеличивать,а для расширения частотного диапазона калибратора фазовых сдвигов значение 1 необходимо устанавливатькак можно меньшим. Поэтому выборзначения 3 должен быть компромиссньм.Установка старших разрядов заданного значения фазового сдвига в калибраторе осуществляется цифровымвзвешенным кодом при помощи блока6 установки Фазового сдвига. Теку"щие значения кодов пересчетных блоков 2 и 3 8 Ц и Н 0 П Я соответствуют в дискретном выражении значениям текущих фаз Ф и Фвыходных напряжений. Фазовый сдвигмежду выходными напряжениями определяется разностью абсолютных значенийтекущих фаэщ=УЖ- У , 1226339а следовательно, и разностью кодов пересчетных блоковн = н(ц- м,(р)Для установки заданного значения разности кодов и для контроля его при помощи блока 5 используются интервалы времени, в течение которых код одного из пересчетных блоков 2 обращается в нуль Н1,) = О, т.е. интервалы, следующие за моментом заполнения этого пересчетного блока. При атом контроль установленного эна чения фазового сдвига (разности кодов) осуществляется блоком 5 путем записи в регистр 7 в указанный интервал времени кода другого пере- счетного блока 3, Блок 8 сравнения кодов осуществляет поразрядное сравнение кода, задаваемого блоком 6 установки фазового сдвига, с выходным кодом регистра 7, При неравенстве сравниваемых кодов при помощи блока 8 в момент заполнения пере- счетного блока 2, т,е. когда оп Ио) Оз формируется сигнал управления блоком 6 установки Фазового сдвига, Этот блок осуществляет корректировку возникшего рассогласования, занося требуемое значение кода в пересчетный блок 3, независимо от того произошел сбой в работе одного из пересчетных блоков или в блок 6 установки фазового сдвига занесено новое значение кода. Контроль Фазового сдвига и при необходимости его корректировка выполняются в каждом периоде выходных напряжений калибратора.Выходы разрядов пересчетного блока 2 подключены к входам преобразователя 1 С кодов, который преобразует дискретные значения кодов, выражающих текущие фазы выходного напряженияф в строго им соответствующие коды мгновенных значений напряжения а,заданной фор мы. В качестве преобразователя 10 кодов может быть использован постоянный перепрограммируемый запоминающий блок 10 - 11.п. Этот блок программируется, а также сменяется или коммутируется таким образом, чтобы имелись группы наборов мгновенных значений напряжений всех требуемых форм. При формировании синусоидальных сигналов запоминающий блок программируется по выборкам гармонических функцийМаксимальное значение и ограничено разрешающей способностью выходного цифроаналогового преобразователя 15. Так для выходного гармонического напряжения значение эзп / ЗО должно в несколько раэ превышать разрешающую способность выходного преобразователя 15. Выходы .преобразователей соединены с группами входов коммутатора 12, выходы которого подключены к перемножающему цифроаналоговому преобразователю 15, Количество разрядов последнего, определяющее его разрешающую способность, должно быть достаточным для того, чтобы обеспечить требуемую точность воспроизведения мгновенных значений выходного напряжения и для того, чтобы реализовать требуемое значение наименьшей ступени регулирования фазовых сдвигов ЬДешифратор 9 и коммутатор 12 управляются синхронно статическим кодом дополнительного переключате- с ля 4 установки фазовых сдвигов. В первом положении переключателя выходы разрядов пересчетного блока 3 посредством дешифратора 9 подключа-, ются к входам преобразователя 11,1 а,(6)= э 1 и Р,(Ф,),Преобразователь 10 кодов илиППЗУ выбирается таким образом,чтобыколичество их адресных входов не 5превышало количества разрядов пере. счетных блоков 2 и 3, а разрядностьпо выходу совпадала с разрядностьюподсоединенногок нему интегрального перемножающего цифроаналоговогопреобразователя 14, В свою очередьколичество разрядов интегральногоцифроаналогового преобразователя 14выбирается исходя иэ заданной точности воспроизведения мгновенныхзначений выходных напряжений.Выходы разрядов пересчетнбго блока 3 канала с регулируемым фаэовымсдвигом связаны с информационными, входами дешифратора 9. Количество Игрупп выходов дешифратора 9 такжекак и количество подключенных к нимпреобразователей 11.1 - 11. и кодовопределяется значением наименьшей Иступени регулирования Фазовых сдвигов й,.Ь( 7где и - любое целое число из натурального ряда.1226339 Составитель В. ШубинРедактор Р. Цицика Техредл.Олейник Корректор.А. Тяско Заказ 2126/43 Тираж 7,28 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 45Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,4 преобразователей кодов, входы которого подключены к разрядам первогоделителя частоты, а цифровые входывторого перемножающего цифроаналогового преобразователя связаны свыходами коммутатора, между входами .которого и одноименными выходамидешифратора включены остальные ппреобразователей кодов, информационные входы дешифратора соединены свыходами разрядов второго делителячастоты, а одноименные входы управления дешифратора и коммутатора поразрядно подключены к дополнительному переключателю установки фазовых сдвигов. 2. Калибратор по п,1, о т л ич а ю щ и й с я тем, что, с целью уменьшения аппаратурных затрат, в него введен некоммутируемый преобразователь кодов, входы которого совместно с входами регистра и дешифратора подключены к выходам разрядов второго де, лителя частоты, а выходы - к входам р старших разрядов перемножающего цифроаналогового преобразователя, а в -выходов коммутатора соединены с входами ю -младших разрядов перемножающего цифроаналогового преобразова теля.

СмотретьЗаявка

3813833, 20.11.1984

КОНСТРУКТОРСКОЕ БЮРО "ШТОРМ" ПРИ КИЕВСКОМ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКОМ ИНСТИТУТЕ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКБТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

БАТУРЕВИЧ ЕВГЕНИЙ КАРЛОВИЧ

МПК / Метки

МПК: G01R 25/04

Метки: калибратор, сигналов, фазовых, широкодиапазонный

Опубликовано: 23.04.1986

Код ссылки

<a href="https://patents.su/7-1226339-shirokodiapazonnyjj-kalibrator-fazovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Широкодиапазонный калибратор фазовых сигналов</a>

Предыдущий патент: Устройство для поверки фазометров

Следующий патент: Фазосдвигающее устройство

Случайный патент: Теплообменник вращающейся печи