Функциональный преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1115069

Авторы: Корень, Трахтенберг

Текст

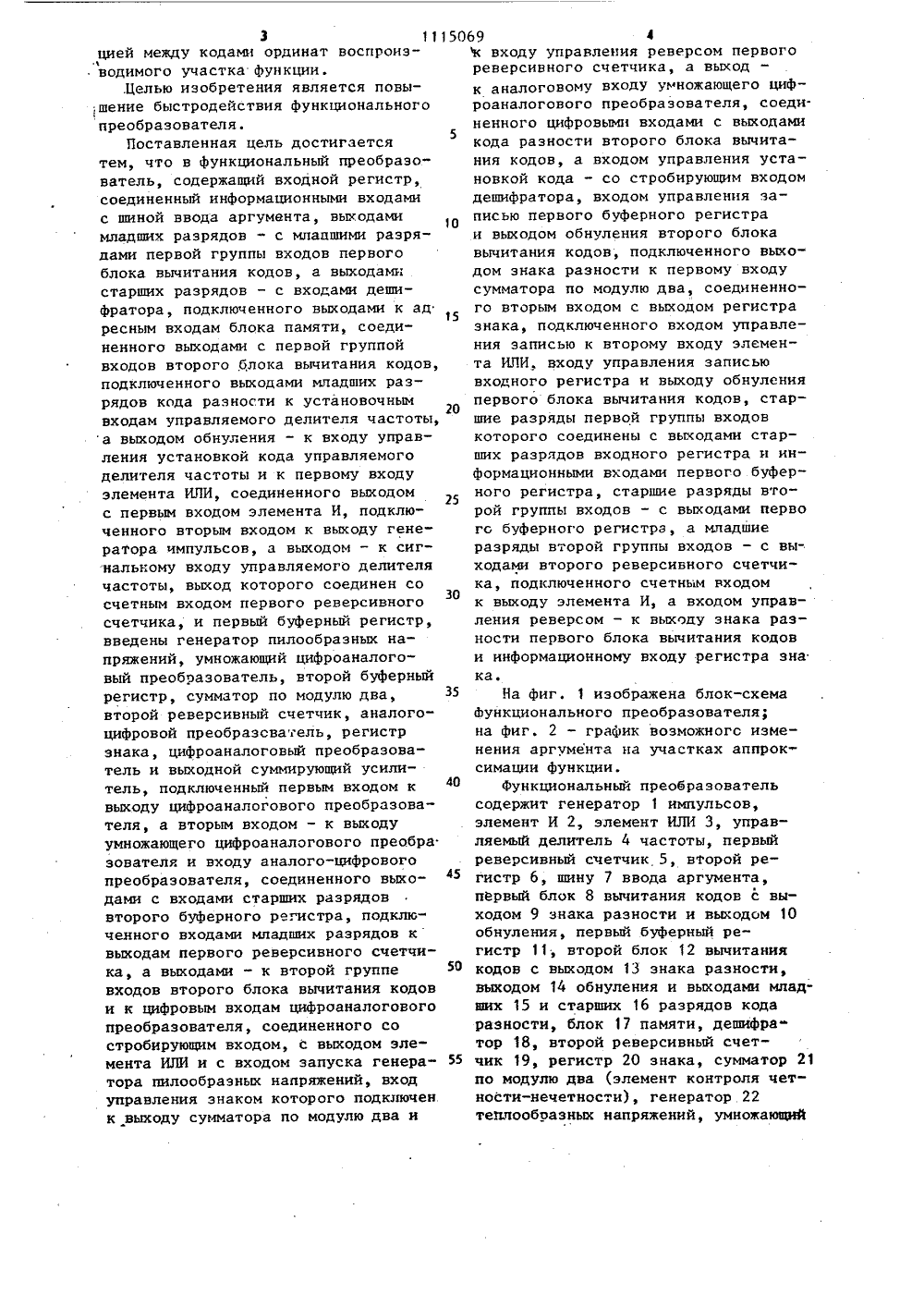

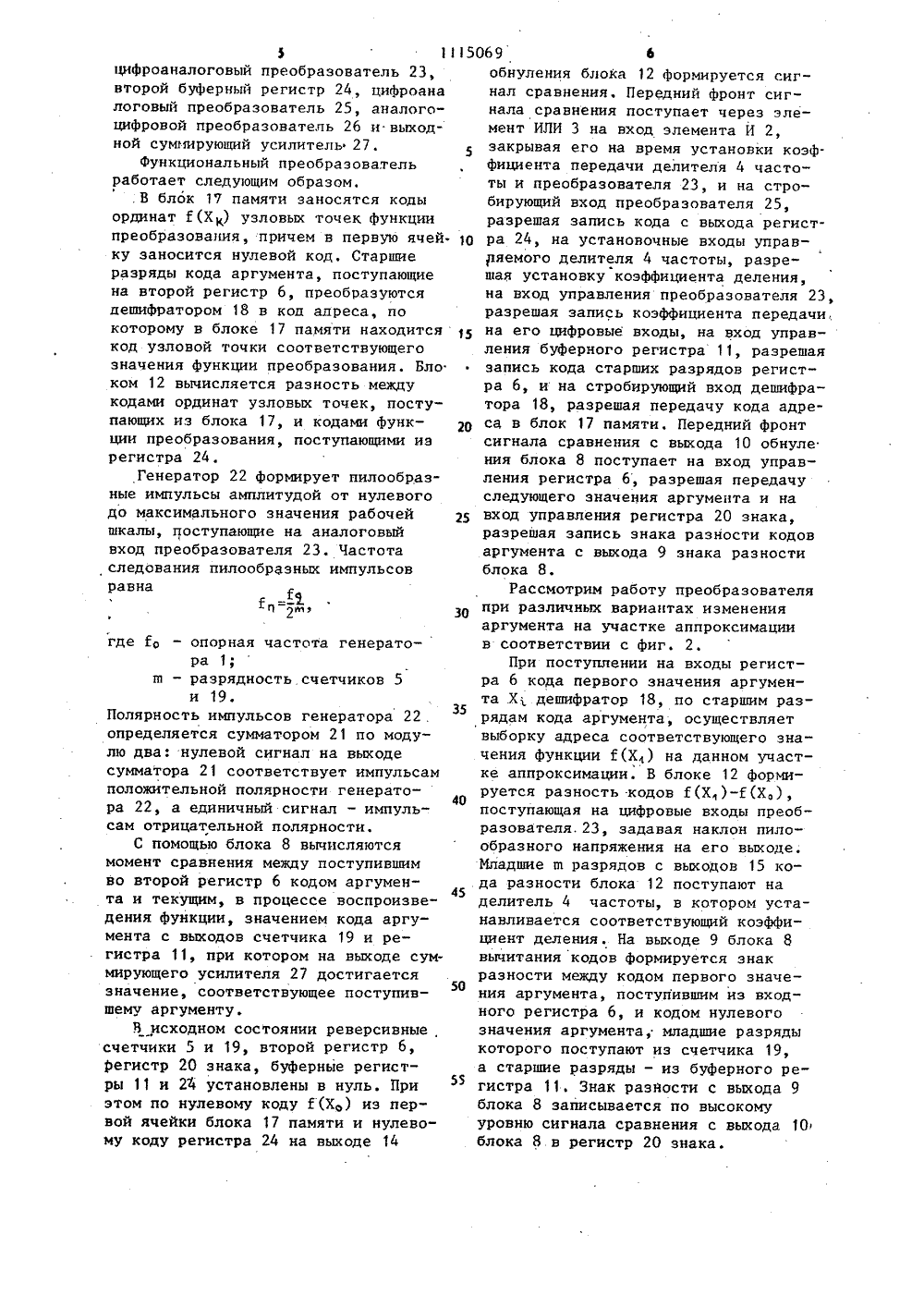

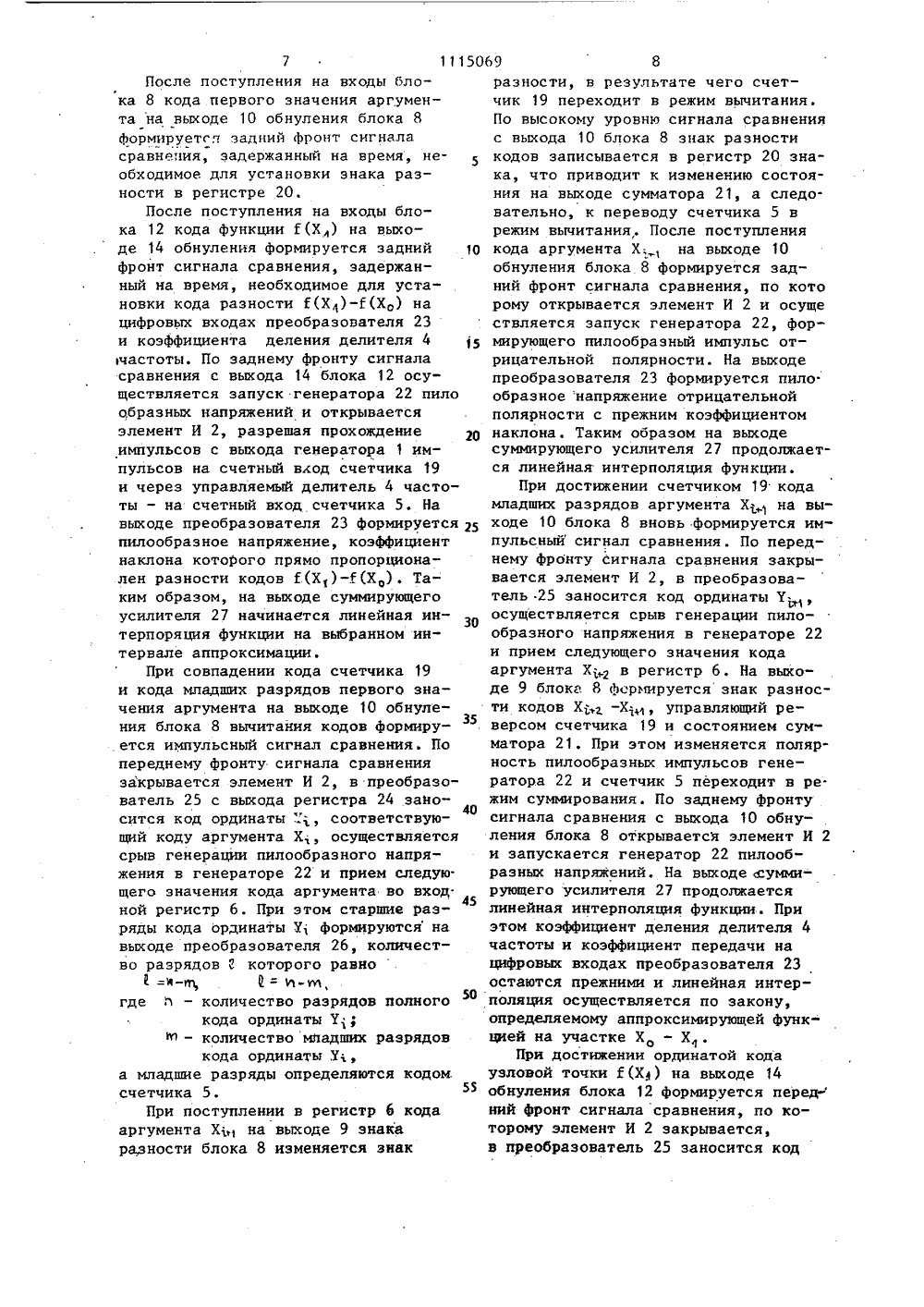

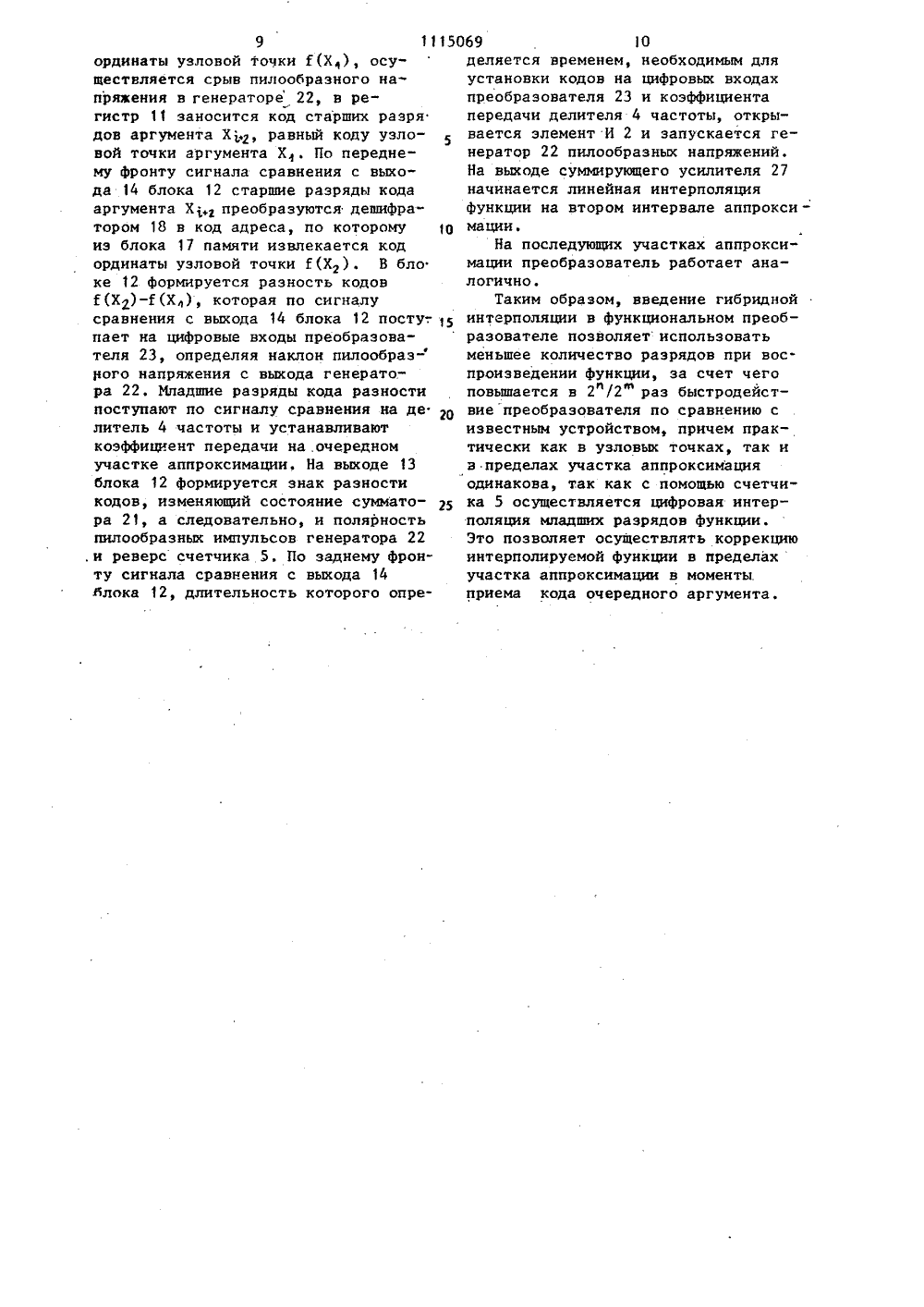

СОЮЗ СОВЕТСНИХ,СОЦИАЛИСТИЧЕОЮХРЕСПУБЛИК ПИСАНИЕ ИЗОБРЕТЕНИЯ ТЕЛЬСТВУ ВТОРСКОМУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) 1. Авторское свидетельство СССРВ 894748, кл. С 06 Л 3/00,С 06 С 7/26, 1980.2. Авторское свидетельство СССРУ 960836, кл. С 06 Г 15/31, 1981(54)(57) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий входной регистр,соединенный информационными входамис шиной ввода аргумента, выходамимладших разрядов - с младшими разрядами первой группы входов первогоблска вычитания кодов, а выходамистарших разрядов - с входами дешифратора, подключенного выходами к адрес.ным входам блока памяти, соединенного выходами с первой группой входоввторого блока вычитания кодов, подключенного выходами младших разрядовкода разности к установочным входамуправляемого делителя частоты, а выходом обнуления - к входу управленияустановкой кода управляемого делителя частоты и к первому входу элемента ИЛИ, соединенного выходом с первым входом элемента И, подключенноговторым входом к выходу генератораимпульсов, а выходом - к сигнальномувходу управляемого делителя частоты,выход которого соединен со счетнымвходом первого реверсивного счетчика,и первый буферный регистр, о т л и -ч а ю щ и й с я тем, что, с целью.повышения быстродействия функционального преобразователя, в него введены генератор пилообразного напряжения, умножающий цифроаналоговый преобразователь, второй буферный регистр, сумматор по модулю два, второй реверсивный счетчик, аналого-цифровой преобразователь, регистр знака, цифроаналоговый преобразователь и выходной суммирующий усилитель, подключенный первым входом к выходу цифроаналогового преобразователя, а вторым входом - к выходу умножающего цифроаналогового преобразователя и входу аналого-цифрового преобразователя соеО диненного выходами с входами старших Щ разрядов второго буферного регистра, подключенного входами младших разрядов к выходам первого реверсивного счетчика, а выходами - к второй группе входов второго блока вы- Я читания кодов и к цифровым входам цифроаналогового преобразователя,эвам соединенного со стробирующим входом, с выходом элемента ИЛИ и с входом запуска генератора пилообразных напряжений, вход управления знаком которого подключен к выходу суммато ф ра по модулю два и к входу управле- ФФ ния реверсом первого реверсивногоФО счетчика, .а выход - к аналоговому входу умножающего цифроаналогового преобразователя, соединенного цифровыми входами с выходами кода разнос Ь ти второго блока вычитания кодов, а входом управления установкой кода со стробирующим входом дешифратора, входом управления записью первого буферного регистра и выходом обнуления второго блока вычитания кодов, подключенного выходом знака разности11 к первому входу сумматора по модулю два, соединенного вторым входом с выходом регистра знака, подключенного входом управления записью к второму входу элемента ИЛИ, входу управления записью входного регистра и выходу обнуления первого блока вычитания кодов, старшие разряды первой группы входов которого соединены с, выходами старших разрядов входного регистра и информационными входами первого 15069буферного регистра, старшие разряды второй группы входов - с выходами первого буферного регистра, а младшие разряды второй группы входов - с выходами второго реверсивного счетчика, подключенного счетным входом к выходу элемента И, а входом управления реверсом - к выходу знака разности первого блока вычитания кодов и информационному входу регистра ,знака, Изобретение относится к автоматике и вычислительной технике, в частности к устройствам кусочно-линейной аппроксимации, и может найти применение в гибридных вычислительных сис темах и комплексах при функциональном преобразователе цифрового кода в аналоговый сигнал.Известен функциональный преобразо-ватель, содержащий генератор импульсов, счетчики, блок сравнения кодов, регистры, преобразователь код - частота, блок памяти, дешифратор, реВерсивный счетчик и выходной цифроаналоговый преобразователь Г 13.Недостатком функционального преобразователя является пониженное быстродействие.Наиболее близким к изобретению является функциональный преобразо ватель, содержащий входной регистр, соединенный информационными входами с шиной ввода аргумента, выходами младших разрядов - с младшими разрядами первой группы входов первого .блока вычитания, а выходами старших разрядов - с входами дешифратора, подключенного выходами к адресным входам блока памяти, соединенного выходами с первой группой входов 30 второго блока вычитания кодов, подключенного выходами кода разности к установочным входам управляемого делителя частоты, а выходом обнуления - к входу управления установкой кода управляемого делителя частоты и к первому входу элемента ИЛИ, сое" диненного выходом с первым входом элемента И, подключенного вторым входом к выходу генератора импульсов, 40 а выходом - к сигнальному входууправляемого делителя частоты, выходкоторого соединен со счетнйм входомпервого реверсивного счетчика, подключенного входом управления реверсом к выходу знака разности второгоблока вычитания, соединенного второйгруппой входов с выходами первогореверсивного счетчика, а выходом обнуления - с первым входом второгоэлемента И и с первым входом триггера, подключенного вторым входом к выходу первого формирователя импульсови к входу управления записью буферного регистра, прямым входом - к первому входу третьего элемента И, аинверсным выходом- - к второму входувторого элемента И, соединенного выходом с первым входом второго элемента ИЛИ, подключенного выходом к входууправления записью входного регистра,а вторым входом через элемент задержки - к выходу второго формирователяимпульсов, второму входу первогоэлемента ИЛИ и к входу обнулениябуферного регистра, соединенного информационными входами с выходамимладшйх разрядов входного регистра,а выходами - с второй группой входовбуферного регистра, подключенноговыходами кода разности к установочным входам вычитающего счетчика, соединенного выходом с входом второгоформирователя импульсов,а счетнымвходом - с выходом третьего элемента И 23. Недостатком известного устройстваявляется пониженное быстродействие,обусловленное цифровой интерполя3 11 цией между кодами ординат воспроизводимого участка функции..Целью изобретения является повы,шение быстродействия функционального преобразователя.Поставленная цель достигается тем, что в Функциональный преобразователь, содержащий входной регистр, соединенный информационными входами с шиной ввода аргумента, выходами младших разрядов - с младшими разрядами первой группы входов первого блока вычитания кодов, а выходами старших разрядов - с входами дешифратора, подключенного выходами к ад ресным входам блока памяти, соединенного выходами с первой группой входов второго блока вычитания кодов, подключенного выходами младших разрядов кода разности к установочным входам управляемого делителя частоты, а выходом обнуления - к входу управления установкой кода управляемого делителя частоты и к первому входу элемента ИЛИ, соединенного выходом с первым входом элемента И, подключенного вторым входом к выходу генератора импульсов, а выходом - к сигнальному входу управляемого делителя частоты, выход которого соединен со счетным входом первого реверсивного счетчика, и первый буферный регистр, введены генератор пилообразных напряжений, умножающий цифроаналоговый преобразователь, второй буферный регистр, сумматор по модулю два, второй реверсивный счетчик, аналогоцифровой преобразователь, регистр знака, цифроаналоговый преобразователь и выходной суммирующий усилитель, подключенный первым входом к выходу цифроаналогового преобразователя, а вторым входом - к выходу умножающего цифроаналогового преобра. зователя и входу аналого-цифрового преобразователя, соединенного выходами с входами старших разрядов второго буферного регистра, подключенного входами младших разрядов к выходам первого реверсивного счетчика, а выходами - к второй группе входов второго блока вычитания кодов и к цифровым входам цифроаналогового преобразователя, соединенного со стробирующим входом, с выходом элемента ИЛИ и с входом запуска генератора пилообразных напряжений, вход управления знаком которого подключен к выходу сумматора по модулю два и15069 4 5 10 15 20 25 30 35 40 45 50 55 к входу управления реверсом первого реверсивного счетчика, а выход к аналоговому входу умножающего цифроаналогового преобразователя, соеди. ненного цифровыми входами с выходами кода разности второго блока вычитания кодов, а входом управления установкой кода - со стробирующим входом дешифратора, входом управления записью первого буферного регистра и выходом обнуления второго блока вычитания кодов, подключенного выходом знака разности к первому входу сумматора по модулю два, соединенного вторым входом с выходом регистра знака, подключенного входом управле - ния записью к второму входу элемента ИЛИ. входу управления записью входного регистра и выходу обнуления первого блока вычитания кодов, старшие разряды первой группы входов которого соединены с выходами старших разрядов входного регистра и информационными входами первого буферного регистра, старшие разряды второй группы входов - с выходами перво го буферного регистра, а младшие разряды второй группы входов - с выходами второго реверсивного счетчика, подключенного счетным входом к выходу элемента И, а входом управления реверсом - к выходу знака разности первого блока вычитания кодов и информационному входу регистра зна ка.На фиг. 1 изображена блок-схема функционального преобразователя;на фиг. 2 - график возможного изменения аргумента на участках аппроксимации функции.Функциональный преобразователь содержит генератор 1 импульсов, элемент И 2, элемент ИЛИ 3, управляемый делитель 4 частоты, первый реверсивный счетчик 5, второй регистр 6, шину 7 ввода аргумента, первый блок 8 вычитания кодов с выходом 9 знака разности и выходом 10 обнуления, первый буферньй регистр 11, второй блок 12 вычитания кодов с выходом 13 знака разности, выходом 14 обнуления и выходами младших 15 и старших 16 разрядов кода разности, блок 17 памяти, дешифратор 18, второй реверсивный счетчик 19, регистр 20 знака, сумматор 21 по модулю два (элемент контроля четности-нечеткости), генератор 22 теплообразных напряжений, умножающий5 11 цифроаналоговый преобразователь 23, второй буферный регистр 24, цифроана логовый преобразователь 25, аналогоцифровой преобразователь 26 и.выходной суммирующий усилитель 27.Функциональный преобразователь работает следующим образом..В блок 17 памяти заносятся коды ординат Е(Хк) узловых точек Функции преобразования, причем в первую ячейку заносится нулевой код. Старшие разряды кода аргумента, поступающие на второй регистр 6, преобразуются дешифратором 18 в код адреса, по которому в блоке 17 памяти находитсякод узловой точки соответствующего значения функции преобразования. Бло ком 12 вычисляется разность между кодами ординат узловых точек, поступающих из блока 17, и кодами Функции преобразования, поступающими из регистра 24.Генератор 22 формирует пилообразные импульсы амплитудой от нулевого до максимального значения рабочей шкалы, поступающие на аналоговый вход преобразователя 23. Частота следования пилообразных импульсов равна где Г - опорная частота генератора 1;ш - разрядность счетчиков 5и 19.Полярность импульсов генератора 22. определяется сумматором 21 по модулю два; нулевой сигнал на выходе сумматора 21 соответствует импульсам положительной полярности генератора 22, а единичный сигнал - импульсам отрицательной полярности.С помощью блока 8 вычисляются момент сравнения между поступившим во второй регистр 6 кодом аргумента и текущим, в процессе воспроизведения Функции, значением кода аргумента с выходов счетчика 19 и регистра 11, при котором на выходе суммирующего усилителя 27 достигается значение, соответствующее поступившему аргументу.В исходном состоянии реверсивные счетчики 5 и 19, второй регистр 6, регистр 20 знака, буферные регистры 11 и 24 установлены в нуль. При этом по нулевому коду Г(Х) иэ первой ячейки блока 17 памяти и нулевому коду регистра 24 на выходе 145069 бобнуления блока 12 Формируется сигнал сравнения. Передний Фронт сигнала сравнения поступает через элемент ИЛИ 3 на вход элемента И 2,закрывая его на время установки коэффициента передачи делителя 4 частоты и преобразователя 23, и на стробирующий вход преобразователя 25,разрешая запись кода с выхода регист ра 24, на установочные входы управляемого делителя 4 частоты, разрешая установку коэффициента деления,на вход управления преобразователя 23,разрешая запись коэффициента передачи,на его цифровые входы, на вход управления буферного регистра 11, разрешаязапись кода старших разрядов регистра 6, и на стробирующий вход дешифратора 18, разрешая передачу кода адре са в блок 17 памяти. Передний фронтсигнала сравнения с выхода 10 обнуления блока 8 поступает на вход управления регистра 6, разрешая передачуследующего значения аргумента и на 25 вход управления регистра 20 знака,разрешая запись знака разности кодоваргумента с выхода 9 знака разностиблока 8.Рассмотрим работу преобразователяпри различных вариантах измененияаргумента на участке аппроксимациив соответствии с Фиг. 2.Прн поступлении на входы регистра 6 кода первого значения аргумента .Х дешифратор 18, по старшим разрядам кода аргумента, осуществляетвыборку адреса соответствующего значения Функции Й(Х) на данном участке аппроксимации. В блоке 12 формируется разность кодов Г(Х)-Е(Х,),поступающая на цифровые входы преобразователя. 23, задавая наклон пилообразного напряжения на его выходе.Младшие ш разрядов с выходов 15 кода разности блока 12 поступают наделитель 4 частоты, в котором устанавливается соответствующий коэффициент деления. На выходе 9 блока 8вычитания кодов формируется знакразности между кодом первого значения аргумента, поступившим из входного регистра 6, и кодом нулевогозначения аргумента, младшие разрядыкоторого поступают из счетчика 19,а старшие разряды - из буферного регистра 11. Знак разности с выхода 9блока 8 записывается по высокомууровню сигнала сравнения с выхода 10блока 8 в регистр 20 знака.15069 5 1 О 15 20 7 11После поступления на входы блока 8 кода первого значения аргумента на выходе 10 обнуления блока 8формируетсп задний фронт сигналасравнения, задержанный на время, необходимое для установки знака разности в регистре 20,После поступления на входы блока 12 кода функции Г(Х) на выходе 14 обнуления формируется заднийфронт сигнала сравнения, задержанный на время, необходимое для установки кода разности Г(Х 4)-Г(ХО) нацифровых входах преобразователя 23и коэффициента деления делителя 4частоты. По заднему фронту сигналасравнения с выхода 14 блока 12 осуществляется запуск генератора 22 пилообразных напряжений и открываетсяэлемент И 2, разрешая прохождениеимпульсов с выхода генератора 1 импульсов на счетный вход счетчика 19и через управляемый делитель 4 частоты - на счетный вход счетчика 5, Навыходе преобразователя 23 формируетсяпилообразное напряжение, коэффициентнаклона которого прямо пропорционален разности кодов Е(Х 1)-Г(Х ). Таким образом, на выходе суммирующегоусилителя 27 начинается линейная интерпоряция функции на выбранном интервале аппроксимации.При совпадении кода счетчика 19и кода младших разрядов первого значения аргумента на выходе 10 обнуления блока 8 вычитания кодов формируется импульсный сигнал сравнения. Попереднему фронту сигнала сравнениязакрывается элемент И 2, в преобразователь 25 с выхода регистра 24 заносится код ординаты "., соответствующий коду аргумента Х осуществляетсясрыв генерации пилообразного напряжения в генераторе 22 и прием следующего значения кода аргумента во вход.ной регистр 6. При этом старшие разряды кода ординаты У, формируются навыходе преобразователя 26, количество разрядов Г которого равно:н-ю, 1 = и-ю,где й - количество разрядов полногокода ординаты Уд - количество мпадших разрядовкода ординаты Уа младшие разряды определяются кодомсчетчика 5.При поступлении в регистр 6 кодааргумента ХЬ, на выходе 9 знакаразности блока 8 изменяется знак разности, в результате чего счетчик 19 переходит в режим вычитания.По высокому уровню сигнала сравненияс выхода 10 блока 8 знак разностикодов записывается в регистр 20 знака, что приводит к изменению состояния на выходе сумматора 21, а следо.вательно, к переводу счетчика 5 врежим вычитания. После поступлениякода аргумента Х;, на выходе 10 обнуления блока 8 формируется задний фронт сигнала сравнения, по которому открывается элемент И 2 и осуществляется запуск генератора 22, формирующего пилообразный импульс отрицательной полярности. На выходепреобразователя 23 формируется пило.образное напряжение отрицательнойполярности с прежним коэффициентомнаклона. Таким образом на выходе суммирующего усилителя 27 продолжается линейная интерполяция функции.При достижении счетчиком 19 кодамладших разрядов аргумента Х 1 на выходе 10 блока 8 вновь формируется импульсный сигнал сравнения. По переднему фронту сигнала сравнения закрывается элемент И 2, в преобразователь 25 заносится код ординаты У;1,осуществляется срыв генерации пилообразного напряжения в генераторе 22и прием следующего значения кодааргумента Х, в регистр 6, На выходе 9 блоке 8 формируется знак разности кодов Х., -Х; управляющий реверсом счетчика 19 и состоянием сумматора 21. При этом изменяется полярность пилообразных импульсов генератора 22 и счетчик 5 переходит в ре.жим суммирования. По заднему фронту 40сигнала сравнения с выхода 10 обнуления блока 8 открывается элемент И 2и запускается генератор 22 пилообразных напряжений. На выходе ауммирующего усилителя 27 продолжается 45линейная интерполяция функции. Приэтом коэффициент деления делителя 4частоты и коэффициент передачи нацифровых входах преобразователя 23остаются прежними и линейная интерполяция осуществляется по закону,определяемому аппроксимирующей функцией на участке Хо - Х.При достижении ординатой кода узловой точки Е(Ку) на выходе 14обнуления блока 12 формируется передний фронт сигнала сравнения, по которому элемент И 2 закрывается,в преобразователь 25 заносится код9 11 ординаты узловой точки Й(Х), осуществляется срыв пилообразного напряжения в генераторе 22, в регистр 11 заносится код старших разря дов аргумента Х, равный коду узловой точки аргумента Х. По переднему фронту сигнала сравнения с выхода 14 блока 12 старшие разряды кода аргумента Х, преобразуются дешифратором 18 в код адреса, по которому иэ блока 17 памяти извлекается код ординаты узловой точки Е(Х). В бло. ке 12 формируется разность кодов Е(Х 2)-Г(Х), которая по сигналу сравнения с выхода 14 блока 12 посту", пает на цифровые входы преобразователя 23, определяя наклон пилообраз- ного напряжения с выхода генератора 22, Младшие разряды кода разности поступают по сигналу сравнения на де. литель 4 частоты и устанавливают коэффициент передачи на .очередном участке аппроксимации. На выходе 13 блока 12 формируется знак разности кодов, изменяющий состояние сумматора 21, а следовательно, и полярность пилообразных импульсов генератора 22 .и реверс счетчика 5, По заднему фронту сигнала сравнения с выхода 14 Блока 12, длительность которого опре 15069 0деляется временем, необходимым дляустановки кодов на цифровых входахпреобразователя 23 и коэффициентапередачи делителя 4 частоты, открывается элемент И 2 и запускается генератор 22 пилообразных напряжений.На выходе суммирующего усилителя 27начинается линейная интерполяцияфункции на втором интервале аппрокси -мации.На последующих участках аппроксимации преобразователь работает аналогично.Таким образом, введение гибриднойинтерполяции в функциональном преобразователе позволяет использоватьменьшее количество разрядов при воспроизведении функции, за счет чегоповышается в 2"/2 раз быстродействие преобразователя по сравнению сизвестным устройством, причем практически как в узловых точках, так ив пределах участка аппроксимацияодинакова, так как с помощью счетчи ка 5 осуществляется цифровая интерполяция младших разрядов функции.Это позволяет осуществлять коррекциюинтерполируемой функции в пределахучастка аппроксимации в моментыприема кода очередного аргумента.во ал ППП фЯатаатф, г.Узгород, ул.Проектная, 4 Х+ 11 15069 Фи акаэ 6772/36 б Х р

СмотретьЗаявка

3602115, 07.06.1983

КИШИНЕВСКИЙ ОРДЕНА "ЗНАК ПОЧЕТА" ЗАВОД СЧЕТНЫХ МАШИН ИМ. 50 ЛЕТИЯ СССР

ТРАХТЕНБЕРГ АЛЕКСАНДР СРУЛЬЕВИЧ, КОРЕНЬ СЕМЕН ДАВИДОВИЧ

МПК / Метки

МПК: G06G 7/26

Метки: функциональный

Опубликовано: 23.09.1984

Код ссылки

<a href="https://patents.su/7-1115069-funkcionalnyjj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Функциональный преобразователь</a>

Предыдущий патент: Функциональный преобразователь многих перемнных

Следующий патент: Имитатор измерительного радиоприемного устройства

Случайный патент: Способ изготовления электросварных прямошовных труб