Цифроаналоговый функциональный преобразователь со степенной характеристикой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1027742

Авторы: Выстропов, Литвинович, Шляхтин, Ямный

Текст

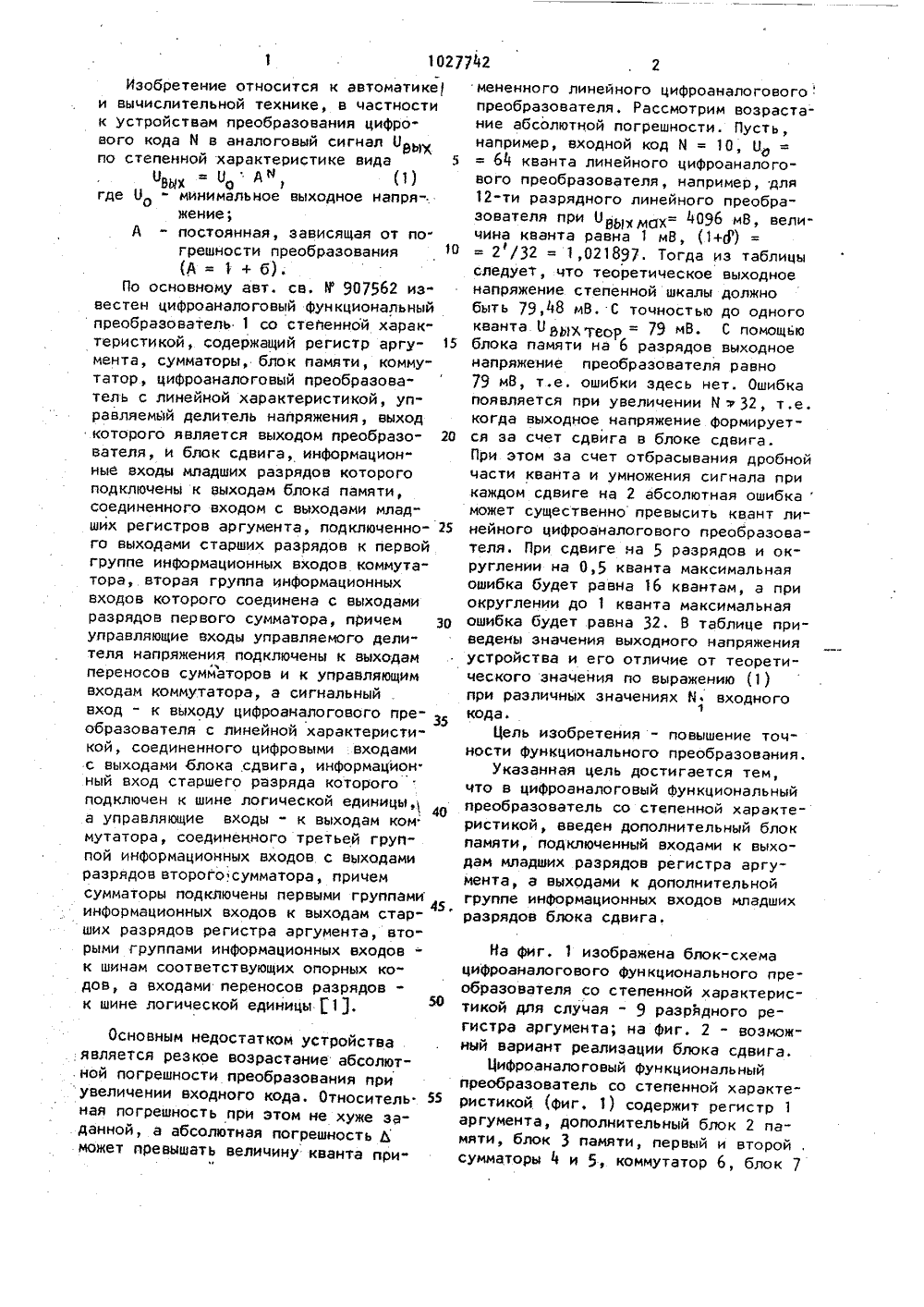

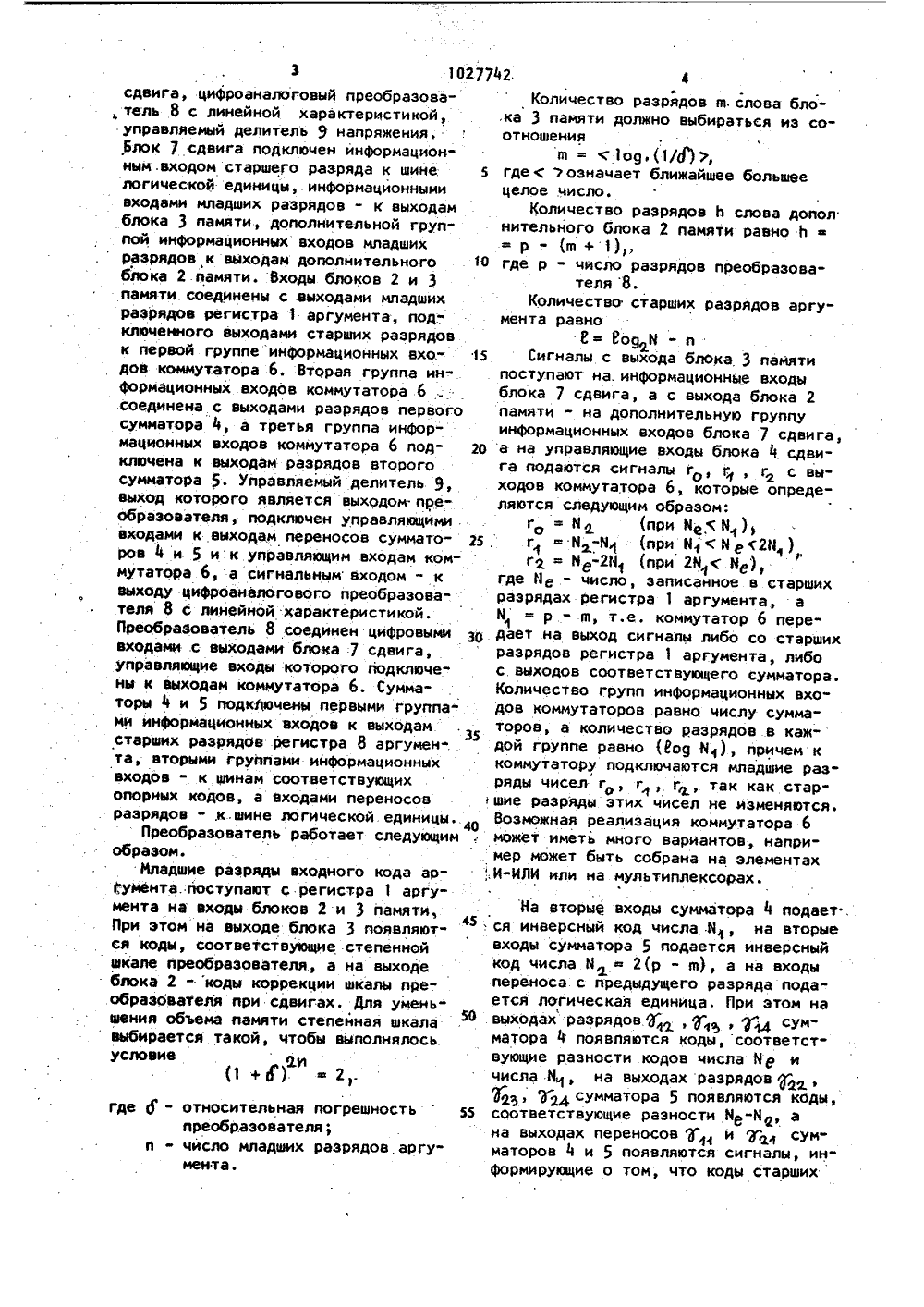

СОВЕТ 7742 ЯО 10 6,1 3/00; 6 06 ОПИСАНИЕ ИЗОБРЕТЕНИЯ ИДЕТЕЛЬСТВУ ВУОРСКОЬ УДФфСТВЕННЫЙ НОМИГЕТ СССРДМш ИОЕВИ Н Н ШННЛа(71) белорусский ордена ТрудовогоКрасного Знамени государственный(56) 1 Авторское свещетельство ССиф 907562, кл. 6. 06 4 3/00,6 06 6 7/20 1980 (прототип).(9)(Б 7) циф однддоговцй функциондль.НЫИ ПРЕОБРАЗОВАТЕЛЬ СО СТЕПЕННОЙХАРАКТЕРИСТИКОЙ по авт. св, В 907562отличающийся тем, что,с целью повышения точности функционального преобразования, в него вве"ден дополнительный блок памяти, под"ключенный входами к выходам младаихразрядов регистра аргумента, а выхо"дами к дополнительной групее информационных входов младших,разрядов бло-".ка сдвига1 1027Изобретение относится к автоматикеи вычислительной технике, в частностик устройствам преобразования цифрового кода М в аналоговый сигнал Цвь 1 Хпо степенной характеристике аида 5(А =+ б),По основному авт. св, И 907562 известен цифроаналоговый функциональныйпреобразователь 1 со степенной характеристикой, содержащий регистр аргумента, сумматоры, блок памяти, коммутатор, цифроаналоговый преобразова"тель с линейной характеристикой, управляемый делитель напряжения, выходкоторого является выходом преобразователя, и блок сдвига, информацион"ные входы младших разрядов которогоподключены к выходам блока памяти,соединенного входом с выходами младших регистров аргумента, подключенного выходами старших разрядов к первойгруппе информационных входов коммутатора, вторая группа информационныхвходов которого соединена с выходамиразрядов первого сумматора, причем ЗОуправляющие входы управляемого делителя напряжения подключены к выходампереносов сумматоров и к управляющимвходам коммутатора, а сигнальныйвход - к выходу цифроаналогового пре-обраэователя с линейной характеристикой, соединенного цифровыми входамис выходами блока сдвига, информацион.ный вход старшего разряда которогоподключен к шине логической единицы,1а управляоцие входы - к выходам ком.мутатора, соединенного третьей группой информационных входов с выходамиразрядов второго сумматора, причемсумматоры подключены первыми группамиинформационных входов к выходам стар 45,ших разрядов регистра аргумента, вторыми группами информационных входовк шинам соответствующих опорных кодов, а входами переносов разрядовк шине логической единицы1),Основным недостатком устройства . является резкое возрастание абсолютной погрешности преобразования приувеличении входного кода, Относитель 55ная погрешность при этом не хуже заданной, а абсолютная погрешность Ьможет превышать величину кванта примененного линейного цифроаналоговогопреобразователя, Рассмотрим возрастание абсолютной погрешности, Пусть,например, входной код М = 10, 0= 64 кванта линейного цифроаналогового преобразователя, например, для12-ти разрядного линейного преобразователя при ОВС 1 у= 4096 м 8, величина кванта равнамВ, (1+сГ) == 2 /32 = 1,021897. Тогда из таблицыследует, что теоретическое выходноенапряжение степенной шкалы должнобыть 79,48 мВ. С точностью до одногокванта О иых теор = 79 мВ. С помощьюблока памяти на 6 разрядов выходноенапряжение преобразователя равно79 мВ, т.е. ошибки здесь нет. Ошибкапоявляется при увеличении М32, т,е.когда выходное напряжение Формируется за счет сдвига в блоке сдвига.При этом за счет отбрасывания дробнойчасти кванта и умножения сигнала прикаждом сдвиге на 2 абсолютная ошибкаможет существенно превысить квант линейного цифроаналогового преобразователя, При сдвиге на 5 разрядов и округлении на 0,5 кванта максимальнаяошибка будет равна 16 квантам, а приокруглении до 1 кванта максимальнаяошибка будет равна 32. В таблице приведены значения выходного напряженияустройства и его отличие от теоретического значения по выражению (1)при различных значениях М входногокода,Цель изобретения - повышение точности функционального преобразования,Указанная цель достигается тем,что в цифроаналоговый Функциональныйпреобразователь со степенной характеристикой, введен дополнительный блокпамяти, подключенный входами к выходам младших разрядов регистра аргумента, а выходами к дополнительнойгруппе информационных входов младшихразрядов блока сдвига,На фиг, 1 изображена блок-схема цифроаналогового Функционального преобразователя со степенной характеристикой для случая - 9 разрядного регистра аргумента; на Фиг. 2 - возможный вариант реализации блока сдвига.Цифроаналоговый функциональный преобразователь со степенной характеристикой (Фиг. 1) содержит регистр аргумента, дополнительный блок 2 памяти, блок 3 памяти, первый и второй, сумматоры 4 и 5, коммутатор 6, блок 73 1027742 4сдвига, цифроаналоговый преобразова-Количество разрядов е слова бло, тель 8 с линейной характеристикой, ка 3 памяти должно выбираться из соуправляемый делитель 9 напряжения. . отношенияБлок 7 сдвига подключен информацион- а = (1 од(1/Д , ным.входом старшего разряда к вине: 5 где7 означает ближайшее большее логической единицы, информационными целое число. входами младших разрядов - к выходам . Количество разрядов Ь слова допол блока 3 памяти, дополнительной груп- нительного блока 2 памяти равно Ьпой информационных входов младших ив р ю (щ +1) разрядов к выходам дополнительного 10 где р " число разрядов преобразоваблока 2.памяти. Входы блоков 2 и 3 теля 8. памяти. соединены с выходами младших Количество старших разрядов аргу- разрядов регистра 1 аргумента, под.-. . мента равноключенного выходами старших разрядов 8= 8 ояй - и к первой группе информационных вхо= 15 Сигналы с выхода блока 3 памяти дов коммутатора 6. Вторая группа ин- поступают на. информационные входы формационных входов коммутатора .6 , блока 7 сдвига, а с выхода блока 2 .соединена с выходами разрядов первого памяти - на дополнительную группу сумматора 4, а третья группа инфор- информационных входов блока 7 сдвига, мационных входов коммутатора б под а на управляющие входы блока ч сдвиключена к выходам разрядов второго га подаются сигналы г г г с вы" сумматора 5, Управляемый делитель 9, ходов коммутатора 6, которые опредевыход которого является выходом пре" ляются следующим образом: образователя, подключен управляющими г й (при йМ )о 2. Е. входами к выходам переносов суммато, г = й -й (при й С й С 2 йе ров 4 и 5 ик.управляющим входам ком- г = й -28 (при 2 й с й )е емутатора 6, а сигнальным входом - к где йе " число, записанное в старших выходу цифроаналогового преобразова- разрядах регистра 1 аргумента, а теля 8 с линейной характеристикой. йр - а, т,е, коммутатор б пере" П реобразователь 8 соединен цифровыми З 0 дает на выход сигналы либо со старших входами .с выходами блока 7 сдвига, разрядов регистра 1 аргумента, либо управляющие входы которого подключе- с. выходов соответствующего сумматора, ны к выходам коммутатора 6. Сумма- . Количество групп информационных вхоторы 4 и 5 подключены первыми группа- дов коммутаторов равно числу сумма" ми информационных входов к выходам. : торов, а количество разрядов в каж 35старших разрядов регистра 8 аргумен-. дой группе равно (8 оц й), причем к та, вторыми группами информационных коммутатору подключаются младшие развходов " к шинам соответствующих ряды чисел г , г , г , так как стар- опорных кодов, а входами переносов вшие разряды этих чисел не изменяются. разрядов -,к.шине логической единицы Возможная реализация коммутатора 640Преобразователь работает следующим , может иметь много вариантов, напри- образом. мер может быть собрана на элементахИладшие разряды входного кода ар- , в .И-ИЛИ или на мультиплексорах. умента. поступают с регистра 1 аргумента на входы блоков 2 и 3 памяти, На втоРы 4 входы сУмматоРа М подает . При этом на выходе блока 3 появляют ся инверсный код числа й, на вторые ся коды, соответствующие степеннойвходы сумматора 5 подается инверсный шкале преобразователя., а на выходе код числа й щ 2(р - а), а на входы блока 2 - коды коррекции шкалы пре-. переноса с йредыдущего разряда пода" образователя при сдвигах, Для умень- ется логическая единица. При этом на шения объема памяти степенная акала . выходах разрядов 92, ф, д сум"50выбирается такой, чтобы выполнялось матора Ь появляются коды, соответстусловиевующие разности кодов числа йр и(1 + К) 2,. числа й,1, на выходах разрядов Я,, , сумматора 5 появляются коды, где О - относительная погрешность55 соответствующие разности й -Й ае я.преобразователя; на выходах переносов Я" и " суми - чйсло младших разрядов. аргу- маторов М и 5 появляются сигналы, ин"мента. формирующие о том, что коды старших40 разрядов входного числа превышают М: или М .Если входной код находится в пределах 0+2 П, то логические уровни на выходам а( с 6, с(1, Ыстарших раз рядов регистра 1 равны нулю, логи" ческие уровни на выходах переносов . сумматоров 4 и 5 также равны нулю. Следовательно коммутатор 6 соединяет соответственно выходы о(,о, оу с управляющими входами блока 7 сдвиДо этого момента работа Функционального цифроаналогового преобразователя не отличается от работы про тотипа.Когда входной код превышает 2 но меньше 2 2 , то на входес появляется "1". Эта "1" йроходит через коммутатор 6 и вызывает смещение всех кодов, поступающих на информационные входы блока 7 сдвига, на один разряд вправо, что соответствует умножению кодов на два, при этом напряжение на выходе преобразователя 8 25 также возрастает в два раза. При этом на освобождающийся при сдвиге младший разряд преобразователя 8 блок 7 сдвига подает старший разряд корректирующего кода, поступающего на дополнительную группу информационных входов с дополнительного блока 2 памяти. Коэффициент деления делителя 9 должен быть равен номинальному значению К 4 . При дальнейшем увеличении входного кода будет увелииваться и выходное напряжение. Соответственно при каждом сдвиге блок 7 подает на освобождающийся младший разряд преобразователя 8 следующий разряд корректирующего кода, снимаемого с выхода блока 2 памяти. Пусть, например, в младших разрядах входного кода записано число 17 (см. таблицу), После 5-го сдвига мы получим число квантов шкалы 2944, в то время как теоретическое рассчитанное число квантов преобразователя 8 должносоставлять 2960. Получаем ошибку в16 квантов,. которая корректируетсяподачей на младшие разряды преобразователя 8, освободившихся при сдвигах, корректирующего кода, снимаемогос выхода блока 2 памяти через блок 7сдвига. В данном случае корректирующий код равен 10000 (см. таблицу).При превышении М) М.1 на выходепереноса . сумматора 4 появляетсялогическая "1", которая изменяет,коэффициент передачи делителя 9. Ондолжен стать равным К 4 /2 М". При этомкоммутатор б соответственно подключает выходы разрядов сумматора 4 куправляющим входам блока 7 сдвига.При дальнейшем увеличении входногокода работа цифроаналогового функционального преобразователя происходит аналогично вышеописанному,При дальнейшем увеличении входного кода ивыполнения условия Мр) Мна выходе переносов сумматора 5 появляется логическая "1", которая изменяет коэффициент передачи делителя9 до величины К/2 М 1. Коммутатор бсоответственно подключает выходы разрядоа сумматора 5 к управляющим входам блока 7 сдвига и далее работабудет происходить аналогично вышеописанному. Конструктивная реализацияблока 7 сдвига может быть выполненапо различным схемам, В частности, нафиг. 2 изображена схема блока 7, выполненная на двух группах мультиплексоров 10, в качестве которых могутбыть использованы микросхемы 155 КП 7Таким образом, предлагаемый преобразователь по сравнению с прототипомпозволяет получить выходное напряжение, изменяющееся по степенному закону в динамическом диапазоне2/1 +(Гс абсолютной погрешностью,не превышающей одного кванта используемого в нем цифроаналогового преобразователя с линейной характеристикой.1027742 ВЬХ г ЬЬЗХР 1-й сдвиг О еыХ т ЭЫх и е и е ю е ЬЫхп Ошибка Теоретическоезначение Прототип Ошибка й +32 О ВЫХт 0,48 158,96 158 162,44 162 166 166169,63 169 173,34 172 177,14 176 181,02 180 184,98 184 0,22 0,82 0,67 0,51 0,49 Продолжение таблицы1027742 4-й сдвиг 5 й сдвиг ее Ошибка ейод+128 й:+160 О ЭЬ 1 Х Ов 0вйх 126 00111 1328 1344 1376 00000 110 10 10010 1 8 417,1 448,2 4799 40 44 143 144 1:45 8 0 10000ееее 141 1357 142 1386,81027742 Ффт АракРи Р писно 1/5 Зэка аж илиал ППП ".Патент", г, Ужгород, ул. Проектная, 4.

СмотретьЗаявка

3403786, 02.03.1982

БЕЛОРУССКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

ЯМНЫЙ ВИТАЛИЙ ЕВГЕНЬЕВИЧ, ЛИТВИНОВИЧ ЮРИЙ МИХАЙЛОВИЧ, ШЛЯХТИН ВЛАДИМИР ВАСИЛЬЕВИЧ, ВЫСТРОПОВ АЛЕКСАНДР ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06J 3/00

Метки: степенной, функциональный, характеристикой, цифроаналоговый

Опубликовано: 07.07.1983

Код ссылки

<a href="https://patents.su/7-1027742-cifroanalogovyjj-funkcionalnyjj-preobrazovatel-so-stepennojj-kharakteristikojj.html" target="_blank" rel="follow" title="База патентов СССР">Цифроаналоговый функциональный преобразователь со степенной характеристикой</a>

Предыдущий патент: Устройство для моделирования вероятностного графа

Следующий патент: Устройство для вывода графической информации

Случайный патент: Инструмент для нарезания резьбы