Устройство для умножения -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

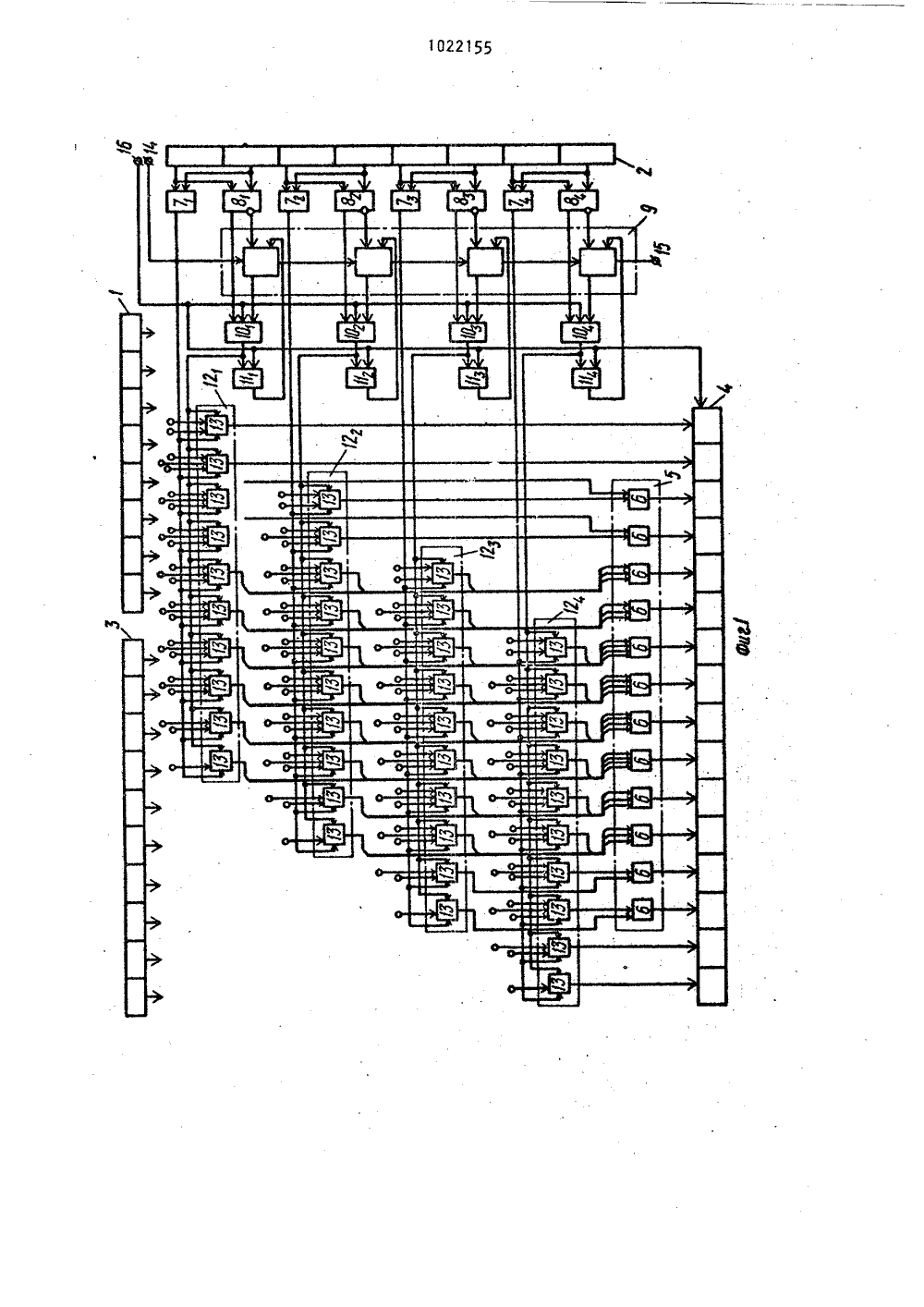

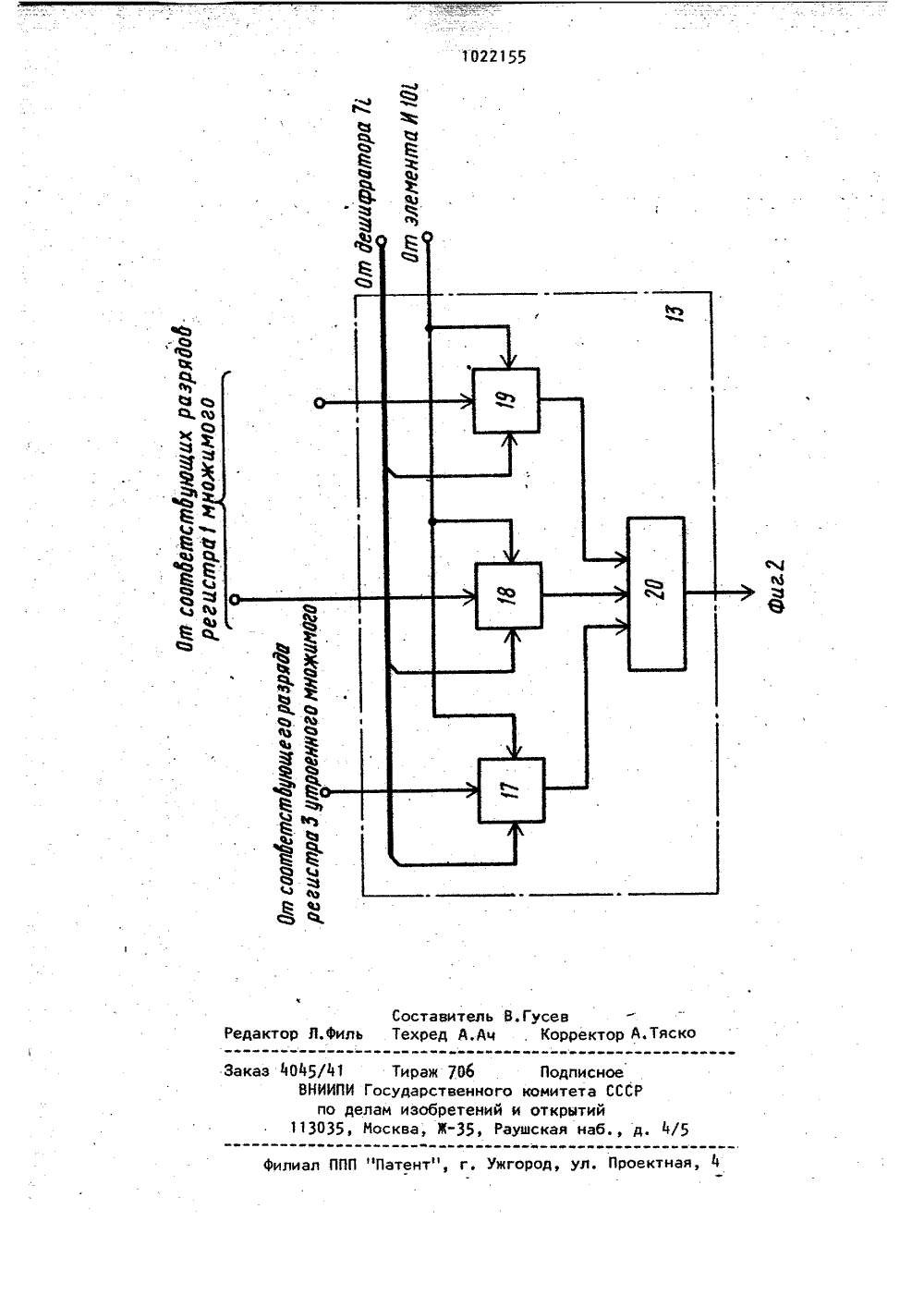

; РЕСПУБЛИК 6 06 Г 7 ГОСУДАРСТВЕННЫЙПО ДЕЛАМ ИЗОБРЕТЕНИ ОПИСАНИЕ ИЗОБРЕТЕН Й Вцфащ аюйффЮфййфЩИ 4 к мк-типо АВТОРСКОМУ СВИДЕТЕЛЬСТ(56) 1. Авторское свидетельство СССРй 623204, кл.6 06 Р 7152, 1977.2. Авторское свидетельство СССРзаявке У 3321307/18-24,кл. О 06 Г 7/52, 23.07.81 (прототип).(54)(Я) УСТРОЙСТВО ДЛЯ УИНОЖЕНИЯи-РАЗРЯДНЫХ ЧИСЕЛ, содержащее регистры множимого и множителя, первый ивторой блоки элементов ИЛИ, блок эле. ментов И, накапливающий сумматор,комбинационный сумматор, буферный ре"гистр, причем. выходы первого блокаэлементов ИЛИ соединены соответствен"но с разрядными входами с третьего по(2 п)-й накапливающего сумматора,выходы комбинационного сумматора со"единены соответственно с первыми входами элементов И блока, вторые входыкоторых объединены и соединены с ши":ной синхронизации устройства, с входом разрешения записи буферного ре-.гистра и с улравляющим входом накап"ливающего сумматора, выходы элементовИ блока соединены соответственно сразрядными входами буферного регистраа вход и выход переноса комбинационного сумматора являются соотеетствен"но управляющим входом устройства ивыходом индикации окончания операцииумножения, о т л и ч а ю щ е е с яТем, что, с целью повышения быстродействия, в него введены регистр утроенного множимого, и/2 дещифраторов и и/2 блоков коммутирующих узлов,. е каждый из которых входят ( и+21 коммутирующих узлов, причем выходы каж.", дой пары раэрядое регистра множителя соединены с первым и вторым входами соответствующего элемента ИЛИ второго блока и первым и вторым входами соот" ветствующего деаифратора, прямые выходы элементов ИЛИ второго блока со" единены соответственно с третьими входами элементов И блока, инверсные выходы элементов ИЛИ второгЬ блока соединены соответственно с входайи первой группы комбинационного сумма" з тора, входы второй группы которого соединены соответственно с разрядными выходами буферного регистра, первые, вторые и третьи информационные входы коммутирующих узлов каждого блока соединены соответственно .с разрядными свыходами регистров множимого и утроен ного множимого , первые и вторые управляющие входы коммутирующих узлов каждого блока соединены соответственно с выходами деаифраторов и элемен" тов И блока, выходы первого и второго .коммутирующих узлов первого блока соединены соответственно с входами первого и второго разрядов накапливающего сумматора, выходы (и)-го и и"го коммутирующих узлов и/2-го блока соединены соответственно с входами (2 п"1)-го и 2 п-го разрядов накапливающего сумматора, выходы остальных коммутирующих узлов блоков соединены соответственно с входами элементов ИЛИ первого блока.102Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа.Известно устройство для умножения и-разрядных чисел, содержащее регистры множимого и множителя, накапливающий сумматор, матрицу элементов И, первый и второй блоки элементов ИЛИ, элементы И и задержки 1 1 .К недостаткам указанного устройства относятся относительно низкое быстродействие и использование низкотехнологичных элементов задержки для высокоплотной интегральной технологии изготовления электронных схем.Наиболее близким по технической .сущности к предлагаемому является устройство для умножения и-разрядных чисел, содержащее регистры множимого и множителя, первый и второй блоки элементов ИЛИ, блок элементов И, накапливающий сумматор, комбинационный сумматор и буферный регистр, причем выходы первого блока элементов ИЛИ соединены соответственно с разрядными . входами с третьего по (2 п) -й накапливающего сумматора, выходы комбинационного сумматора соединены соответственно с первь 1 ми входами элементов И блока, вторые входы которых объединены и соединены с шиной синхронизации устройства, с входом разрешения записи буферного регистра и с управляющим входом накапливающего сумматора, выходы элементов И блока соединены соответственно с разряднымивходами буферного регистра, вход и выход переноса комбинационного сумма" тора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения ( 2Недостатком известного устройства является его относительно низкое быстродействие.Цель изобретения - повышение быст" родействия устройства.21 Я2ными входами с третьего по (2 п)-йнакапливающего сумматора, выходы комбинационного сумматора соединены соот"Эветственно с первыми входами элемен-тов И блока, вторые вхоцы которых объединены и соединены с шиной синхронизации устроиства, с вхоцом разрешенияизаписи буферного регист а и с управ- Оляющим входом накаплива щего сумматора, выходы элементов И блока соединены соответственно с разрядными входа"ми буферного регистра, а вход и выходпереноса комбинационного сумматораявляются соответственно управляющим 5 входом устройства и.выходом индикацииокончания операции умноженияв введеныРегистр утроенного нноеного, и/2 дешифраторов и и/2 блоков коммутирующихузлов, в каждый из которых входят 20(п+2) коммутирующих узлов, причем выходыкаждой пары разрядов регистра множителя соединены с первым и вторым входами соответствующего элемента ИЛИвторого блока и первым и вторым входами соответствующего дешфратора, прямые выходы элементов ИЛ 4 второго блока соединены соответственно с третьими входами элементов И блока, инверс"нье выходы элементов ИЛ второго бло- ЗО ха соединены соответственно с входамипервой группы комбинацирнного сумматора, входы второй группы которогосоединены соответственнр с разряднымивыходами буферного реги тра, первые З 5 вторые и третьи информа ионные входыкоммутирующих узлов каждого блока соединены соответственно с разряднымивыходами регистров множмого и утроенного множимого, первые40- равляющие входы коммути каждого блока соединены но с выходами дешифрато. ментов И блока, выходы рого коммутирующих узло 45 ка соединены соответств первого и второго разряд вающего сумматора, выход и и-го коммутирующих уз ка соединены соответстввторые упующих узлов соответственов и элеервого и втопервого блонно с входами ов накаплиы (и"1)-го ов и/2-го блонно с входами ов накапливаюПоставленная цель достигается тем, что в устройство для умножения и"раз" рядных чисел, содержащее регистры мнажимого и множителя, первый и второй блоки элементов ИЛИ, блок элементов И,5 накапливающий сумматор, комбинацион" ный сумматор и буферный регистр,;причем выходы первого блока элементов ,ИЛИ соединены соответственно с разряд" щего сумматора, выходы остальных ком" мутирующих узлов блоков,соединены соответственно с входаии ровивнтов ИПИ первого блока,Каждый коммутирующий, узел блокасодержит первый, второй и третий элементы И и элемент ИЛИ, причемпервые входы первого, второго и третьего эле ментов И являются соответственно пер3 1022 вым, вторым и третьим информационными входами коммутирующего узла, вторые и третьи входы первого, второго и третьего элементов И являются соответственно первым и вторым уйравляющими входами коммутирующего узла, а выходы первого, второго и третьего элементов И соединены с входами элемента ИЛИ, выход которого является выходом ком" мутирующего узла.ОНа фиг.1 представлена функциональ" ная схема устройства для умножения и"разрядных чисел для случая п=8; нафиг,2; функциональная схема коммутирующего узла.Устройство содержит восьмиразрядный регистр 1 множимого, восьмираэрядный регистр 2 множителя, десяти- разрядный регистр 3 утроенного множимого, шестнадцатиразрядный накапливающий сумматор 4, первый блок 5 кз двенадцати элементов ИЛИ б, дешифраторы 7 - 7 А, второй блок из четырех элементов ИЛИ 81- 8 комбинационный сумматор 9, блок из четырех элементов И 101" 104., четырехразрядный буферный регистр 1 -. 11,1, четыре бло" ка 121- 124. из десяти коммутирующих узлов 13 каждый, управляющий вход 14, 30 выход 1 индикации окончания операции умножения и шину 16 синхронизации, причем первж информационные входы первых восьми коммутирующих узлов 13 каждого из блоков 12 - 12 соединены . с соответствующими разрядными выхо" дами регистра 1 множимого, вторые информационные входы коммутирующих узлов 13 со второго по девятый каждого из блоков 12 - 12,соединены соот ветственно с разрядными выходами регистра 1 множимого, третьи информационные входы коммутирующих узлов 13 с первого по десятый каждого из блоков 12-12 4,соединены соответственно с разрядными выходами регистра 3 утроенного множимого, первые управ" ляющие входы коммутирующих узлов 13 в каждом из блоков 12, -12 объединены и соединены с соответствующими выходами дешифраторов 7-74, вторые 50 управляющие входы коммутирующих узлов 1 З,в каждом иэ блоков 121-. 12 объединены и соединены с соответствующими выходами элементов И 101-10, блока, выходы первого и второго ком" Ы мутирующих узлов 13 блока 12 соединены соответственно с первым и вторым разрядными входами накапливающего 155 асумматора 4, выходы девятого и десятого коммутирующих узлов 13 блока 12 соединены соответственно с входами 15-го и 16-го разрядов накапливающего сумматора 4, остальные выходы коммутирующих узлов 13 блоков 12,-12 соединены с срответствующими входами элементов ИЛИ 6 первого блока 5, выходы которых соответственно соединены с входами 3 - 14-го разрядов накал ливающего сумматора 4, выходы каждой пары разрядов регистра 2 множителя соединены с первым и вторым входами соответствующего элемента ИЛИ 81-84 второго блока и первым и вторым входа ми соответствующего дешифратора 21 -74, инверсные выходы элементов ИЛИ 81 -84 второго блока соединены соответственно с входами первой группы комбина-. ционного сумматора 9, входы второй группы которого соединены соответственно с разрядными выходами буферного регистра 111- 11, а выходы комбинационного сумматора 9 соединены соот. ветственно с первыми входамй элементов И 10,1- 104, блока, вторые входы которых объединены и соединены с шиной 16 синхронизации устройства, с входом разрешения записи буферного регистра 11, - 114. и управляющим входом накапливающего сумматора 4, тре.тьи входы элементов И 10 - 104 соединены соответственно с прямыми выхода ми элементов ИЛИ 8 -84. второго блока, а выходы элементов И 101 - 104, соединены соответственно с разрядными входами буферного регистра 11 -11, вход и выход переноса комбинационного сумматора 9 являются соответственно управляющим входом 14 устройства и выходом 15 индикации окончания операции умножения.Узел 13 коммутации содержит элементы И 17 -19 и элемент ИЛИ 20, причем первые входы элементов И 17, 18 и 19 являются соответственно первым, вторым и третьим информационными входами узла 13 коммутации, вторые и третьи входы элементов И 17-19 являются соответственно первым и вторым управляющими входами узла 13 коммута" ции, а выходы элементов И 17-19 соединены с входами элемента ИЛИ 20, выход которого является выходом узла 13 коммутации.Устройство работает следующим образом.В исходном состоянии в регистрах 1 и 2 хранятся без знаков восьмираэ 10221рядные соответственно множимое и множитель, в регистре 3 - десяти- разрядное утроенное множимое (оно может быть предварительно сформировано либо на сумматоре 4, либо с ис пользованием дополнительной комбина" ционной схемы), сумматор 4 и регистры 11 - 11 обнулены. По значению пар разрядов регистра 2 множителя на выходах дешифраторов 74 - 7, формируются соответствующие управляющие потенциалы, которые действуют на протяжении всего времени умножения чисел, и настраивают блоки 124 - 124 коммутирующих узлов на передачу в накапли вающий сумматор 4 через блок 5 элементов ИЛИ 6 одинарного, удвоенного или утроенного значения множимого, В каждом такте работы устройства про" изводится передача одинарного, уд военного или утроенного значения мно" жимого в накапливающий сумматор 4 с выходов только одного блока 12 коммутирующих узлов, Выбор этого блока осуществляется с помощью управляющего 25 сигнала, который Формируется на выходе элемента И 101 в момент прихода сигнала на шину 16 синхронизации устройства. Подготовка и Формирование этого управляющего сигнала производится одновременно с суммированием очередного частичного произведения в накапливающем сумматоре 4, На управляющий вход 14 устройства на протяжении всего времени умножения подается потенциал, соответствующий значению логической единицы, а наличие сигнала на выходе 15 устройства означает окончание умножения чисел, Болеедетально работу устройства рассмотримна примере умножения множимого Х на множитель У=10001100. С учетом этого в исходном состоянии дешифратор 7 настраивает блок 12 на передачу в накапливающий сумматор 4 УтРоенного .45 значения множимого 3 Х, а дешифратор 7 настраивает блок 12 на передачу в накапливающий сумматор 4 удвоенного значения множимого 2 Х, на выходах дешифраторов 121 и 12 управляющие по 50 тенциалы не формируются, На инверсныа выходах элементов ИЛИ 8-, 84 сформирован код А=0101, который является первым и неизменяющимся слагаемым для сумматора 9. Вторым слагаемым для сумматора 9 служит код В, хранящиися55 в регистре 11 Д.- 111. В исходном состоянии код В=0000, а в процессе умножения он изменяется от такта к такту втаким образом, что к юменту оконца" ния умножения он равен, инверсному значению кода А. Таким обРазом, в исходном состоянии на выходе сумматора 9 с учетом логической единицы, поступающей на управляющий ход 14 устройства, сФормирован код С=А+В+0001= 0101+0000+0001=0110.В первом такте работы устройства при приходе первого синхроимпульса на вход 16 устройства на выходе элемента И 102 формируется управляющий сиг" нал, который осуществляет передачу соответствующим образом сдвинутого утроенного множимого с выходов блока 122 коммутирующих узлов 13 в накапли" вающий сумматор 4 и служит логической единицей на 5-входе синхронного Й 5-триггера 11(запись информации в регистр 111 в 11, осуществляется по синхроимпульсам, поступающим на вход 16 устройства).Одновременнос суммированием внакапливающем сумматоре 4 очередного частичногопроизведения вкомбинационном сумматоре 9 осуществляется суммирование кодов А=0101 и В=0010 суче" том логической единицы на входе 14 устройства, в результате на выходе комбинационного сумматора 9 формирует. ся код суммы С=0101+0010+0001=1000. На втором такте работы устройства на его вход 16 по истечении времени, равного времени суммирования 10-раз" рядных чисел в накапливающем сумматоре 4, поступает второй синхроимпульс. В результате этого на выходе элемента И 10 формируется управляющий сигнал, который осуществляет передачу соответствующим образом сдвинутого удвоенного множимого с выходов блока 12 коммутирующих узлов 13 в накапливающий сумматор 4 и служит логической единицей на 5-входе В 5-триггера 11. Одновременно с суммированием чисел в накапливающем сумматоре 4 в ком. бинационном сумматоре 9 производится сложение кодов А 0101 и В =1010 с учетом логической единицы на входе 14 устройства, врезультате на выходе 15 устройства формируется сигнал, овна" чающий окончание умножений. Таким образом, в рассмотренном случае умножение двух чисел выполнено за два такта, причем длительность такта определяется временем суммирования (и+2)-разрядных чисел в 2 П-разрядном накапливающем сумматоре 4, так как суммирование чисел в комбинационном сумматоре 97 10221 может быть организовано более быстро ввиде его меньшей разрядности.Итак, среднее время умножения двух и-разрядных чисел в предлагаемом устройстве составляет величину 5ф 3Т, ч пцф.ср 0 тогда как среднее время умножения двух и-разрядных чисел в известном 1 о устройстве составляет величину%Р 2 фСМ где и - число разрядов перемножаемыхчисел;с 1,- время суммирования двух иразрядных двоичных чиселТогда выигрыш в быстродействиисоставит величинуТср исл ЪиемЬеРТаюм образом, предлагаемое уст"ройство позволяет сократить времяумнржения двух и разрядных двоичныхчисел примерно в 1,3 раза.з 40 45/41 Тираж 706 Подписное ВНИИПИ Государственного комитета ССС по делам изобретений и открытий 1303 В, Иосква, ЖВ, Раушская наб.,ее е ее е еееееееееее

СмотретьЗаявка

3350066, 29.07.1981

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЛОПАТО ЛИЛИЯ ГРИГОРЬЕВНА, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 07.06.1983

Код ссылки

<a href="https://patents.su/7-1022155-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения -разрядных чисел</a>

Предыдущий патент: Устройство для получения разностной частоты двух импульсных последовательностей

Следующий патент: Устройство для умножения

Случайный патент: Устройство для нанесения надрезов на роговицу глаза