Способ воспроизведения цифровых сигналов и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

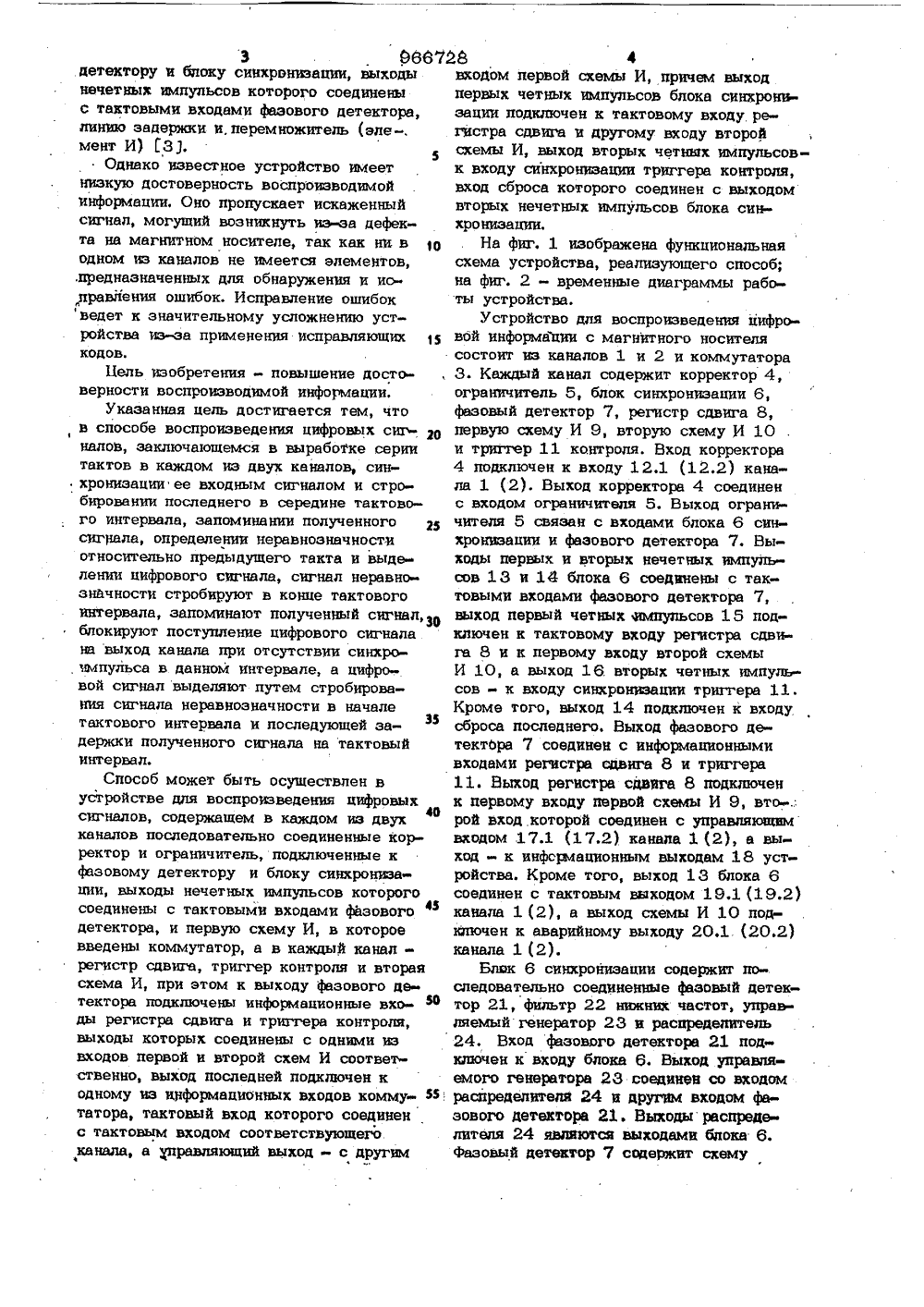

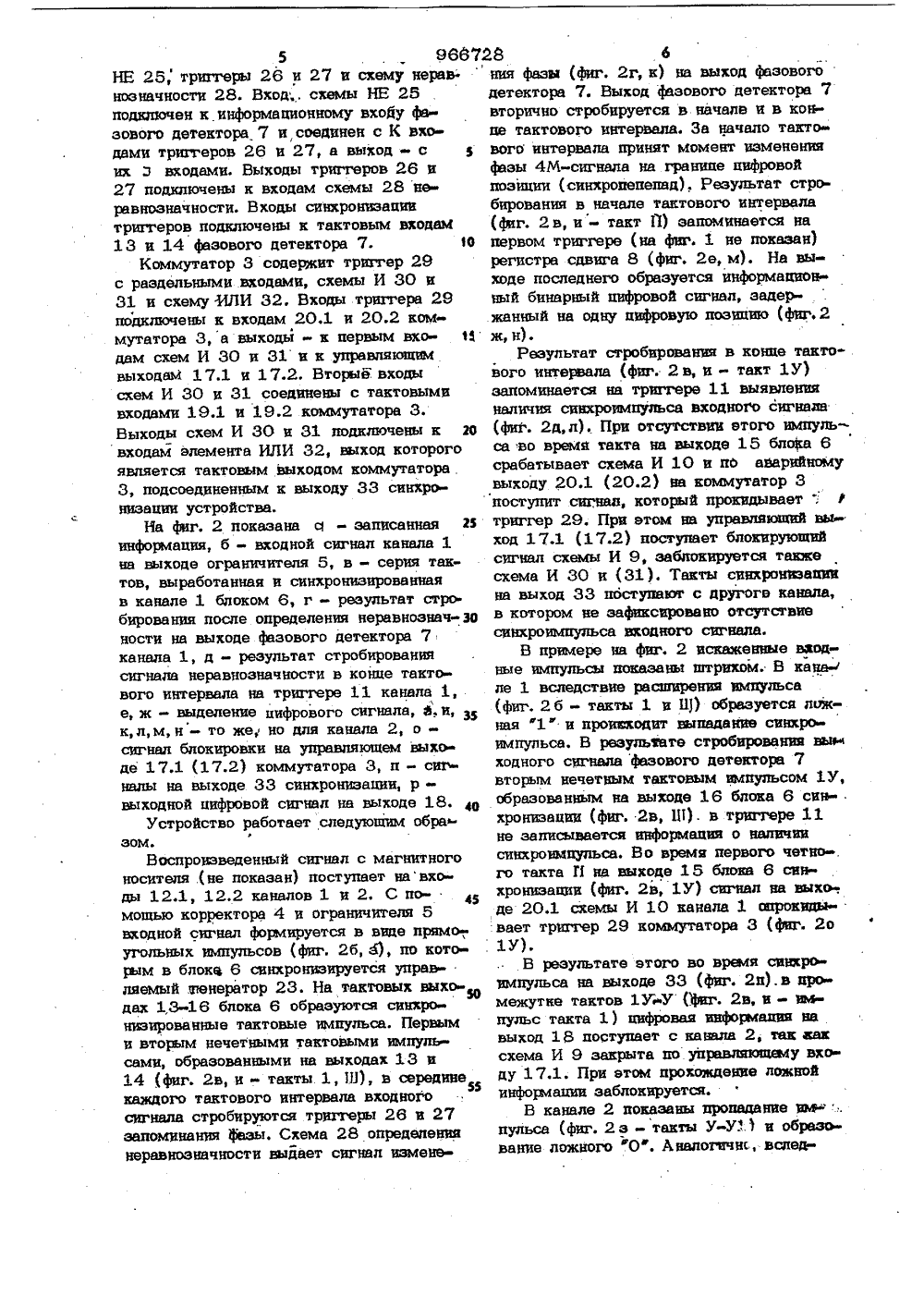

(54) СПОСОБ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВЫХ СИГНАЛО И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ. серии тасигналомредине ка на импульсы феднннпсы Ц.Однако атот спосостоверность воспроиэсигналов. Искажениепрнводнт к появленнюформации на выходе,имеет ннэкую доведення цифровых 20 ходного сигнала недостоверной ин 1 ю соедннензы вдключе нные 1Изобретение относится к вычислительной технике и предназначено для нсполь зовання в запоминающих устройствах с магнитным носителем, например с магнит ной лентой,работающих методами частот ной модуляпни (ЧМ) эапнси ннформацнне 5 ен сцособ воспроизведения цнфформацнн с магнитного носителя,щнй прннцнп сравнения ннформат.сигнала с синхроннэнрукяцнм сигонернруемым импульсной систе- ПЧ, заключающийся в выработкетов, синхроннзацнн ее входнымстробированнн последнего в сеждого тактового интервала И 15м раэделеннн входного сигналан сннхронмпульф Наиболее близкнм техннчесжею решещвем является способ воспронэведення цнф ровых сигналов с магнитного носителя в двухканальной системе с объединенным вы ходом, в котором вырабатывают серию тактов в каждом канале, сннхронвзнруют ее входным снгналом, стробнруют последннй в середине каждого тактового интер вала, запоминают результаты стробнрова ния, определяют неравноэначнОсть отноф сительно предыдущего такта и выделя цнфровой сигнал 2 аОднако известный способ вюеет нвзкую достоверность воспроизводимой информации. Учитывая тр, что в каналах алеет место появление не только ложных уф, но в ложных ф 1 ф, суммнрование по спеднвъ на схеме.ИЛИ дает ошибку.Известно двухканальное устройствовоспроюведення цнфровой ннформааин, реалюацни ювестного способа, содерщее в каждом канале последователье корректур к огранвчатель одновременно к фазовомуИ 10, а выход 16. вторых четных импульсов к входу синхронизации триггера 11. Кроме того, выход 14 подключен к входу сброса последнего, Выход фазового детектора 7 соединен с информационными входами регистра сдвига 8 и триггера 11. Выход регистра сщвега 8 подключен к первому входу первой схемы И 9, вто:,. рой вход которой соединен с управляющим входом 17.1 (17.2) канала 1 (2), а вы ход - к инфсрмационным выходам 18 устройства. Кроме того, выход 13 блока 6 соединен с тактовым выходом 19.1 (19.2) канала 1 (2), а выход схемы И 10 подключен к аварийному выходу 20.1. (20.2) канала 1 (2).Блик 6 синхронизации содержит последовательно соединенные фазовый детектор 21, фильтр 22 нижних частот, управляемый генератор 23 и распределитель 24, Вход фазового детектора 21 подключен к входу блока 6. Выход управляемого генератора 23 соединен со входомраспределителя 24 и другим входом фазового детектора 21. Выходы распределителя 24 являются выходами блока 6.фазовый детектор 7 содержит схему 3 9667 детектору и блоку синхронизации, выходы нечетных импульсов которого соединены с тактовыми входами фазового детектора, линию задержки и, перемножитель (эле-, мент И) 33Однако известное устройство имеет низкую достоверность воспроизводимой информации. Оно пропускает искаженный сигнал, могущий возникнуть иэ за дефекта на магнитном носителе, так как ни в 1 р одном иэ каналов не имеется элементов, ,предназначенных для обнаружения и исправления ошибок. Исправление ошибок ведет к значительному усложнению устройства из-ва применения исправляющих кодов.Цель изобретения - повышение достоверности воспроизводимой информации.Указанная цель достигается тем, что в способе воспроизведения цифровых сиг налов, заключающемся в выработке серии тактов в каждом из двух каналов, синхронизации ее входным сигналом и стробировании последнего в середине тактового интервала, запоминании полученного д сигнала, определении неравнозначности относительно предыдущего такта и выде ленни цифрового сигнала, сигнал неравнозначности стробируют в конце тактового интервала, запоминают полученный сигнал,зй блокируют поступление цифрового сигнала на выход канала при отсутствии синхроимпульса в данном интервале, а цифровой сигнал выделяют путем стробирования сигнала неравнозначности в начале тактового интервала и последующей задержки полученного сигнала на тактовый интервал.Способ может быть осуществлен в устройстве для воспроизведения цифровых сигналов, содержащем в каждом иэ двух40 каналов последовательно соединенные корректор и ограничитель, подключенные к фаэовому детектору и блоку синхрониза ции, выходы нечетных импульсов которого соединены с тактовыми входами фазового детектора, и первую схему И, в которое введены коммутатор, а в каждый канал- регистр сдвига, триггер контроля и вторая схема И, при этом к выходу фазового де тектора подключены информационные вхо фа ды регистра сдвига и триггера контроля, выходы которых соединены с одними иэ входов первой и второй схем И соответственно, выход последней подключен к одному из информационных входов комму-татора, тактовый вход которого соединен с тактовым входом соответствующего, канала, а правляющий выход - с другим входом первой схемы И, причем выходпервых четных импульсов блока синхронизации подключен к тактовому входу регистра сдвига и другому входу второй схемы И, выход вторых четних импульсовк входу синхронизации триггера контроля, вход сброса которого соединен с выходом вторых нечетных импульсов блока синхронизации.На фиг. 1 изображена функциональная схема устройства, реализующего способ; на фиг. 2 - временные диаграммы работы устройства. Устройство для воспроизведения цифрьвой информации с магнитного носителясостоит иэ каналов 1 и 2 и коммутатора3. Каждый канал содержит корректор 4,ограничитель 5, блок синхронизации 6,фазовый детектор 7, регистр сдвига 8,первую схему И 9, вторую схему И 10и триггер 11 контроля. Вход корректора4 подключен к входу 12.1 (12.2) канала 1 (2). Выход корректора 4 соединенс входом ограничителя 5. Выход ограничителя 5 связан с входами блока 6 синхронизации и фазового детектора 7. Выходы первых и вторых нечетных импульсов 13 и 14 блока 6 соединены с тактовыми входами фазового детектора 7,выход первый четных ампупьсов 15 подключен к тактовому входу регистра сдвига 8 и к первому входу второй схемы5 . , 9667 НЕ 25, триггеры 26 и 27 и схему неравнозначности 28. Вход,. схемы НЕ 25 подключен к информационному входу фа зового детектора 7 и,соединен с К входами триггеров 26 и 27, а выход - с их 3 входами. Выходы триггеров 26 и 27 подключены к входам схемы 28 не равнозначности. Входы синхронизации триггеров подключены к тактовым входам 13 и 14 фазового детектора 7. 0Коммутатор 3 содержит триггер 29 с раздельными входами, схемы И 30 и 31 и схему ИЛИ 32, Входы триггера 29 подключены к входам 20,1 и 20.2 коьммутатора 3, а выходы - к первым вхо 1 дам схем И 30 и 31 и к управляющим выходаМ 17.1 и 17.2, Вторые входы схем И 30 и 31 соединены с тактовыми входами 19.1 и 19.2 коммутатора 3. Выходы схем И 30 и 31 подключены к 20 входам элемента ИЛИ 32, выход которого является тактовым выходом коммутатора 3, подсоединенным к выходу 33 синхронизации устройства.Иа фиг. 2 показана с 1 - записанная И информация, б - входной сигнал канала 1 на жходе ограничителя 5, в - серия тактов, выработанная и синхронизированная в канале 1 блоком 6, г - результат стро. бирования после определения неравноэнач- ЭО ности на выходе фазового детектора 7 канала 1, д - результат стробирования сигнала неравнозначностн в конце тактового интервала на триггере 11 канала 1, е, жвыделение цифрового сигнала, Э, и, З к,л,м,н - то же, но для канала 2, осигнал блокировки на управляющем выхо де 17.1 (17.2) коммутатора 3, и - сиг напы на выходе 33 синхронизации, р выходной цифровой сигнал на выходе 18.Устройство работает следующим обрафзом.Воспроизведенный сигнал с магнитного носителя .(не показан) поступает навхо ды 12.1, 12,2 каналов 1 и 2. С помощью корректора 4 и ограничителя 5 входной сигнал формируется в виде прямо; угольных импульсов (фиг, 2 б 4, по которым в блока 6 синхронизируется управляемый ащнератор 23. На тактовых выходах 1,3-16 блока 6 образуются синхро низирова нные тактовые импульса. Первым и вторым нечетными тактовыми импульсами, образованными на выходах 13 и 14 (фиг. 2 в, и - такты 1, Ш), в середине каждого тактового интервала входного сигнала стробируются триггеры 26 и 27 запоминания фазы. Схема 28 определения неравнозначности вадает сигнал изменения фазы (фиг. 2 г, к) на выход фазового детектора 7. Выход фазового детектора 7вторично стробируется в началв и в конце тактового интервала. За ючапо тактового интервала принят момент изменения фазы 4 М-сигнала на границе пифровой позиции (синхропепепад), Результат стробирования в начале тактового интервала (фиг. 2 в, и такт П) запоминается на первом триггере (на фиг. 1 не показан) регистра сдвига 8 (фиг, 2 е, м). На выходе последнего образуется информацион ный бинарный цифровой сигнал, задержанный на одну цифровую позицию (фиг.2ж, н).Результат стробирования в конце тактового интервала (фиг. 2 в, и - такт 1 У) запоминается на триггере 11 выявленияналичия синхроимпульса входного сигнала (фнг. 2 д, л), При отсутствии етого импульса во время такта на выходе 15 блока 6 срабатывает схема И 10 и по аварийному выходу 20.1 (20.2) на коммутатор 3 поступит сигнал, который прокидывает; Ртриггер 29. При этом на управляющий вы ход 17.1 (17.2) поступает блокирующийсигнал схемы И 9, заблокируется такжесхема И 30 и (31). Такты синхроназациина выход 33 поступают с другогв канала,в котором не зафиксировано отсутствиесинхронмпульса входного сигнала.В примере на фиг, 2 искаженные ваоные импульсы показаны штрихом. В кана-спе 1 вследствие расширения импульса(фиг. 2 б - такты 1 и 1 Ц) образуется ложная 1" и проиаходит выпадание синхро-импупьса. В резульжте стробирования мамходного сигнала фазового детектора 7вторым нечетным тактовым импульсом 1 У,образованным на выходе 16 блока 6 синхронизации (фиг, 2 в, 1 И). в триггере 11не записывается информация о наличиисинхронмпупьса. Во время первого четно-.го такта П на выходе 15 блока 6 синхронизации (фиг. 2 в, 1 У) сигнал на иыхо;де 20.1 схемы И 10 канала 1 ацрокидывает триггер 29 коммутатора 3 (фнг. 2 о1 У),В результате этого во время синхрьимпульса на выходе 33 (фиг. 2 п).в промежутке тактов 1 УУ (фнг. 2 в, и - вюпульс такта 1) цифровая информация навыход 18 поступает с каюла 2, так ааксхема И 9 закрыта по управлякяцеюу входу 17.1. При этом прохождение ложнойинформации эабпокируется.В канале 2 показаны пропадание 3 вепульса (фиг. 2 э - такты УУ 1) и образование ложного фОф. Анапогичнс, вслед7 ОМ 72 ствие вынадания синхроеюпульса (Ьо врьмя У) опрокинут триггер 29 коммутато ра 3, и цифровая информация на выход 3.8 сном поступает с канала 1.Применение предлагаемых способа и э устройства дает возможность повысить достоверность воснроизведенной информации. В устройстве блокируется прохож-, дение на выход как ложного "Оф, так и ложной 1". К тому же оно способно ио-правлять групповые ошибки, возникающие в одном из каналов. формула изобретения М 1, Способ воспроизведения цифровых сигналов, заключающийся в выработке серии тактов в каждом из двух каналов, син. хронизации ее входным сигналом и стро бированин последне о в середине тактового интервала, запоминании полученного сигнала, определении неравнозначности относительно предыдущего такта и выделении цифрового сигнала, о т л и ч а ю - 25 щ и й с я тем, что, с целью повышения достоверности воспроизведения, сигнал неравноэначности стробируют в конце тактового интервала; запоминают полученный сигнал, блокируют поступление цифрового ЭО сигнала на выход канала при отсутствии синхроимпульса в данном интервале, а цифровой сигнал выделяют путем стробирования сигнала неравнозначности вначале тактового интервала и последующей задержки полученного сигнала на тактовый интервал.2. Устройство для воспроизведения цифровых сигналов, содержащее в каждом иэ двух каналов последовательно соединенные корректор и ограничитель, подключенные к фазовому детектору и блокусинхронизации, выходы нечетных импульсов которого соединеюа с тактовыми выходами фазового детектора, и первую схе .муИ,отличающееся тем,что, в него введены коммутатор, а в каждый канал - регистр сдвига, триггер контроля и вторая схема И, при этом к вы-.ходу фазового детектора подключены информационные входы регистра сдвига итриггер контроля, выходы которых соединены с одними из входов первой и второй схем И. соответственно, выход последней подключен к одному из информационных входов коммутатора, тактовыйвход которого соединен с тактовым входом соответствующего канала, а управляющий выход - с другим входом первойсхемы И, причем выход первых четныхзмпульсов блока синхронизации подключен к тактовому входу регистра сдвигаи другому входу второй схемы И, выходвторых четных впульсов - к входу синхронизаций триггера контроля, вход сброса которого соединен с выходом вторыхнечетных импульсов блока синхронизации.Источники информации,принятые во внимание при экспертизе1. Рыжков В. А, и др. Внешние ЗУна магнитном носителе. М"Энергияф,1978, с, 208-211.2, Ритлиц М. В, Магнитная запись всистемах передачи информации. МСвязью, 1978, с. 259, 280.Зеказ 7850/68 Уираж 622 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

3220120, 11.12.1980

ПРЕДПРИЯТИЕ ПЯ А-1736

ЗВИРБУЛИС ВИКТОРС ВОЛДЕМАРОВИЧ, КРУМИНЬШ ЯН ЭДУАРДОВИЧ

МПК / Метки

МПК: G11B 5/02

Метки: воспроизведения, сигналов, цифровых

Опубликовано: 15.10.1982

Код ссылки

<a href="https://patents.su/6-966728-sposob-vosproizvedeniya-cifrovykh-signalov-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ воспроизведения цифровых сигналов и устройство для его осуществления</a>

Предыдущий патент: Устройство для разметки магнитного барабана на равные интервалы

Следующий патент: Способ многодорожечной цифровой магнитной записи воспроизведения

Случайный патент: Высотомер