Устройство управления прерыванием программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

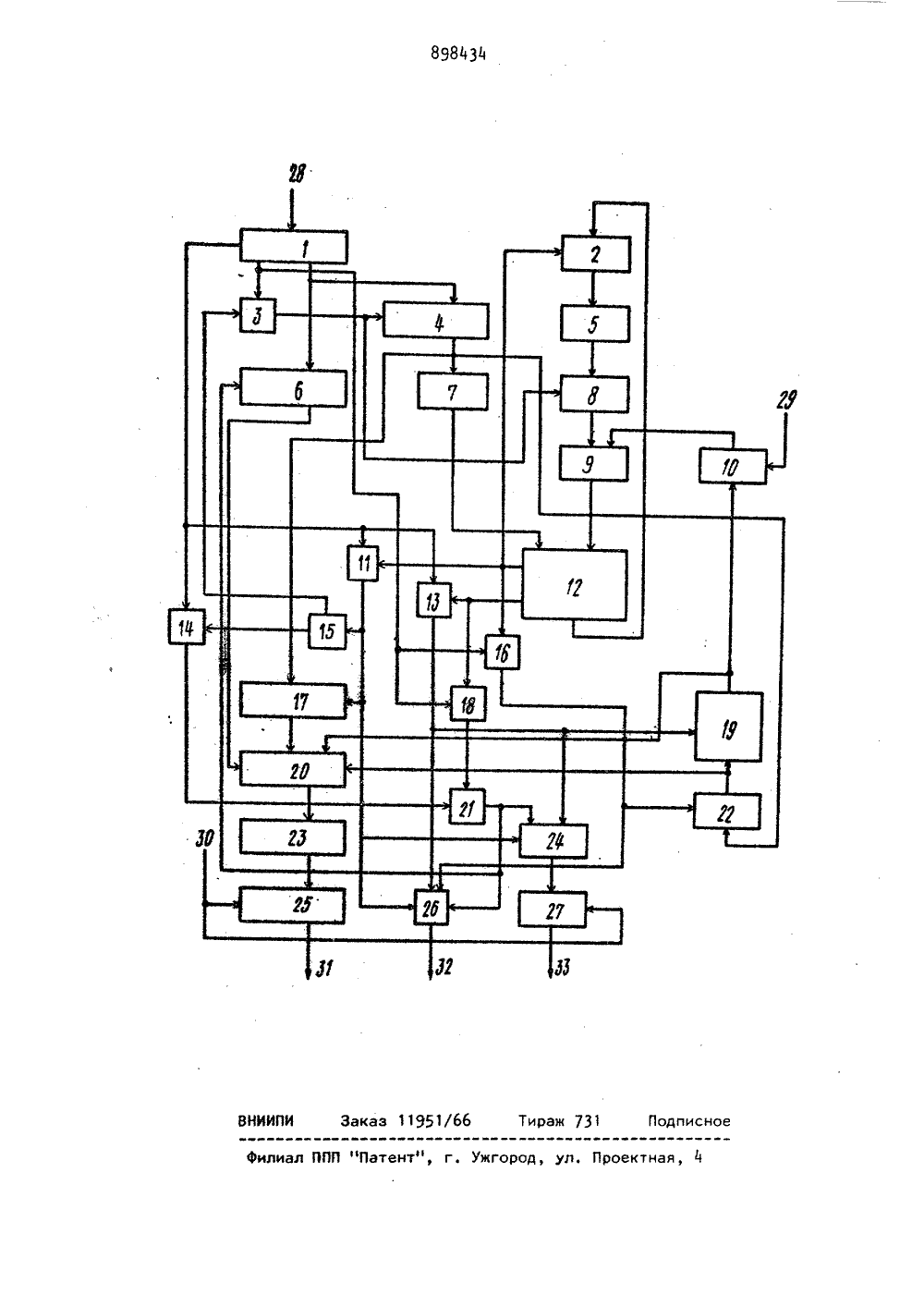

Союз СоветскихСоциалнстическихРеспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 898434вв делан кзабрвтвнкй н открыткиОпубликовано 15. 01.82 Ьтоллетеиь М 2 Дата опубликования описания 17.01,82(54) УСТРОЙСТВО УПРАВЛЕНИЯ ПРЕРЫВРНИЕМ ПРОГРАММИзобретение относится к вычислительной технике и может быть использовано в мультипрограммных вычисли" тельных системах, работающих в реальном масштабе времени.Известно устройство прерывания; содержащее селектор, элементы И, триггер запроса, элемент НЕ, реализующее прерывание системы при пос" туплении запроса 11.Недостаток этого устройства заключается в ограниченных функциональных воэможностях, исключающих применение его в мультипрограммных вычис" -лительных системах.Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для управления прерыванием программ, содержащее регистр запросов, два дешифратора, блок памяти, узел синхронизации, шифратор, регистры, схемы сравнения, элемент ИЛИ, узел приори. тета, группы элементов И 1,2 1. Недостатком этого устройства является ориентация на мультипрограммные системы с разделением памяти нафиксированное число разделов опреде-ленной длины, которая должна преф вышать максимально возможную длинувыполняемых программ, т.е, ограниченная область применения.Цель изобретения - расширениеобласти применения устройства, ОПоставленная цель достигается темячто в устройство управления прерыванием программ, содержащее первый ивторой блоки элементов И, блокпамяти, первый элемент ИЛИ, причем 13первый выход первого регистра соеди"нен с первым входом первого блокаэлементов И, информационный входпервого регистра является запроснымвходом устройства, выход первого элемента ИЛИ является выходом прерывания устройства, выход блока памятисоединен с первым входом второгоблока элементов И, введены блоки40У455055 элементов И с третьего по девятый,первый, второй блоки элементов ИЛИ,блок элементов НЕ, сумматор, элементы И с первого по пятый, второй итретий элементы ИЛИ и триггер, причем второй выход первого регистрасоединен с первым входом второго элемента ИЛИ и с первыми входами первого и второго элементов И, единичный выход триггера соединен со вторым входом второго элемента ИЛИ, выход второго элемента соединен с первым входом третьего блока элементовИи с первым входом четвертого блока элементов И, второй вход третьего блока элементов И соединен с выходом первого регистра, выход тре"тьего блока элементов И Соединен спервым входом пятого блока элементов И, с первым входом шестого блокаэлементов И и через блок элементовНЕ с первым входом сумматора, первыйи второй выходы сумматора соединеныс первыми входами соответственно третьего и четвертого элементов И,вторые входы которых соединены спервым входом пятого элемента И и стретьим выходом первого регистра,единичный выход триггера соединенсо вторым входом пятого элемента И,выход которого соединен с первым входом третьего элемента ИЛИ,. второйвход которого соединен с выходом первого элемента И, второй вход первого элемента И соединен со вторым выходом сумматора, первый выход сумматора соединен со вторым входом второго элемента И и с входом седьмогоблока элементов И, первый вход ко"торого соединен с третьим выходомсумматора, выход седьмого блока элементов И соединен с информационнымвходом второго регистра, выход которого соединен со вторым входом четвертого блока элементов И, выход которого соединен с первым входом первого блока элементов ИЛИ, второй входкоторого соединен с выходом второгоблока элементов И, выход первого блока элементов ИЛИ соединен со вторымвходом сумматора, выход третьегоэлемента И соединен с входом триггера, со вторым входом шестого блока элементов И, с управляющим входом третьего регистра и спервым входом первого элемента ИЛИ,выход второго блока элементов ИЛИсоединен с информационным входомчетвертого регистра, выход четвер 5 10 15 30 И ЗО 35 того регистра соединен с первым входом восьмого блока элементов И, выход которого является первым информационным выходом устройства, выходтретьего элемента ИЛИ соединен со вто.рым входом первого элемента ИЛИ, совторым входом первого блока элементов И и с первым информационным входом третьего регистра, второй информационный вход которого соединен спервым входом блока памяти, с третьимвходом первого элемента ИЛИ и с выходом четвертого элемента И, выходвторого элемента И соединен с четвертым входом первого элемента ИЛИ и совторым входом пятого блока элементовИ, выход которого соединен со вторымвходом блока памяти и с первым входомвторого блока элементов ИЛИ, второйвход которого соединен с выходом блока памяти, выход первого блока элементов И соединен с третьим входомвторого блока элементов ИЛИ, четвертый вход второго блока элементов ИЛИсоединен с выходом шестого блока элементов И, выход третьего регистра соединен с первым входом девятого блока элементов И, второй вход которого соединен с первым управляющим входом устройства и со вторым входомвосьмого блока элементов И, выходдевятого блока элементов И являетсявторым информационным выходом устройства, второй вход второго блока элементов И соединен со вторым управляющим входомустройства. На чертеже приведена структурнаясхема устройства. Устройство содержит регистр 1, блок элементов И 2, элемент ИЛИ 3, блок элементов И 4, регистр 5, блок элементов И б, блок элементов НЕ 7, блок элементов И 8, блок элементов ИЛИ 9, блок элементов И 10, элемент И 11, сумматор 12, элемент И 13, элемент И 14, триггер 15, элемент И 1 б, блок элементов И 17, элемент И 18, блок 19 памяти, блок элементов ИЛИ 20 элемент ИЛИ 21,блок элементов И 22, Регистр 23, регистр 24, блок элементов И 25, элемент ИЛИ 26, блок элементов И 27, информационный вход 28 устройства, управляющие входы 29 и 30 устройства, информационный выход 31 устройства, выход 32 прерывания устройства, информационный выход 33 устройства.5 898434 4Устройство работает следующим об- устанавливается в "1" триггер 15и формируется сигнал прерывания наПо информационному входу 28 в ре- выходе 32. Регистр 24 также устанавгистр 1 вводится поступивший в сис- ливается в нулевое состояние, чтотему код запроса, который содержит в 5 соответствует постановке запроса настаршем разряде признак приоритет- решение,ности, а в остальных - код количест- Вслед за этим срабатывает элева требуемых ресурсов памяти. В за- мент И 16, который своим выходнымвисимости от значений этих парамет- сигналом передает код ресурсов запроров, а также от начального состояния 10 са с выхода группы элементов И 4триггера 15 и регистра 5 устройст- через группу элементов И 22 в блоквом реализуется алгоритм работы. памяти 19 и через блок элементовПусть в системе выполняется при- ИЛИ 20 на Регистр 23,оритетная задача, т.е, триггер 15находится в состоянии "1", старший 15 Бсли Ресурсы в системе меньше реРазряд регистра 1 также - в единиц- сурсов запроса, на сумматоре образуном состоянии и свободные ресурсы, ется разность с отрицательным зна"информация о которых содержится на ком, которая не пересылается на ререгистре 5, превышают ресурсы, тре- гистр 5 В результате срабатываетбуемые запросом, Тогда на обоих вхо- го элемент И 18, выходной сигнал кото"дах элемента И 14 оказываются еди- рого через элемент ИДИ 21 записываетничные сигналы, и его выходной сиг- код в регистр 24, что соответствуетнал через элемент ИЛИ 21 устанавли- операции постановки запроса в оче"вает код на регистре 24, передает Редь, затем через блок элементов И 6содержимое регистра 1 через блоки 25 передает содержимое регистра 1 черезМлементов И 6 и элементов ИЛИ 20 на блок элементов ИЛИ 20 на регистр 23регистр 23 и, наконец, через элемент и, наконец, через элемент ИЛИ 26 фор"ИЛИ 26 с выхода 32 посылает в сис- мирует сигнал прерывания.тему сигнал прерывания. Этим самым Наиболее сложная последовательинициируется работа программы пре- зо ность действий вырабатывается при раРывания в системе, в процессе которой боте Устройства, когда в системе рена управляющий вход 30 поступает сиг- шаются неприоритетные задачи, но длянал, обеспечивающий считывание содер- выполнения поступившего приоритетжимого регистров 23 и 24 через блоки ного запроса не хватает свободныхэлементов И 25 и 27 в систему с вы- Ресурсов памяти, После того, как находов 31 и 33сумматоре появляется отрицательнаяразность, срабатывает элемент И 13,Предположим, что в начальном сос- Его выходной сигнал поступает натоянии система выполняет неприоритет" управляющий вход блока памяти 19 иные программы, т.е. триггер 15 нахо-производит считывание информации одится в нулевом состоянии. Тогда сиг- ресурсах, занимаемых последним поснал с его инверсного выхода через тавленным на решение неприоритетнымэлемент ИЛИ 3 стробирует передачу запросом, Эта информация поступаеткода ресурсов с регистра 1 через блок через блок элементов ИЛИ 20 на реэлементов И 4 и блок элементов НЕ 7 гистр 23. Кроме того, сигнал с выхо"на сумматор 12, а также кода свобод- да элемента И 13 устанавливает наных ресурсов с регистра 5 через блоки регистре 24 операций код и через эле"элементов И 8, ИЛИ 9 в прямом виде, мент ИЛИ 26 формирует сигнал прерываВ данном случае разность на суммато- ния. Программа прерывания, получивРе оказывается с положительным зна- описанным ранее путем информацию ском, т.е. на первом управляющем вы- регистров 23 и 24, производит упряходе сумматора устанавливается еди- тывание последней неприоритетной заничный сигнал. В Результате через дачи, т,е. освобождение занимаемыхблок элементов И 2 содержимое сумма- . ею ресурсов памяти. После завершениятора пересылается в регистр 5 и сра" процесса упрятывания на вход 29 устбатывает элемент И 11, выходным сиг- ройства из системы поступает сигнал 155налом которого содержимое регистра 1 который пересылает код ресурсов за"передается через блоки элементов И 4 дачи через блок элементов ИЛИ 9 ии 17, ИЛИ 20 на регистр 23, а также блок элементов И 10 в прямом видена сумматор. Если результат на сумматоре оказывается опять отрицательным, вновь срабатывает элемент И 13, и цикл повторяется, Так продолжается до тех пор, пока знак результата на сумматоре не становится положительным. Тогда результат через блок элементов И 2 пересылается на регистр 5 и, кроме того, срабатывает элемент И 11. Его выходной сигнал устанавливает в "1" триггер 15 и в нулевое состояние регистр 24, передает через блоки элементов И 17, ИЛИ 20 код запроса с выхода блока элементов И 4 на регистр 23 и через элемент ИЛИ 26 Формирует сигнал пре. рывания.Таким образом, устройство позволяет эффективно загрузить систему поступающими заявками и обеспечить оперативную постановку приоритетных заявок на обслуживание, независимо от наличия свободных ресурсов памяти, что делает возможным применение его 2 ю как е обычных мультипрограммных сис" темах, так и в системах реального времени, т.е. расширить область применения устройства.Формула изобретенияУстройство управления прерываниемпрограмм, содержащее четыре регистра,первый и второй блоки элементов И,блок памяти, первый элемент ИЛИ,причем первый ейход первого регистра соединен с первым входом первого блока элементов И, информацион-ный вход первого регистра является запросным входом устройства, выходпервого элемента ИЛИ является выходом прерывания устройства, выходблока памяти соединен с первым входом второго блока элементов И, о тл и ч а ю щ е е с я тем, что, сцелью расширения области применения,устройство содержит блоки элементовИ с третьего по девятый, первыйвторой блоки элементов ИЛИ, блок элементов НЕ, сумматор, элементы И спервого по пятый, второй и третийэлементы .ИЛИ, триггер, причем второйвыход первого регистра соединен с33первым входом второго элемента ИЛИи с первыми входами первого и второго элементов И, единичный выход триггера соединен со вторым входом второго. элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом третьего блока элементов И и с первым входом четвертого блока элементов И, второй вход третьего блока элементов И соединен с первым выходом первого регистра, выход третьего блока элементов И соединен с первым входом пятого блока элементов И с первым входом шестого блока элементов И и через блок элементов НЕ с первым входом сумматора, первый и второй выходы сумматора соединены с первыми входами соответственно третьего и четвертого элементов И, вторые входы которых соединены с первым входом пятого элемента И,. и с третьим выходам первого регистра, единичный выход триггера соединен со вторым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, второй вход первого элемента И соединен со вторым выходом сумматора, первый выход сумматора соединен со вторым входом второго элемента И и с входом седьмого блока элементов И, первый вход которого соединен с третьим выходом сумматора, выход седьмого блока элементов И соединен с информационным входом второго регистра, выход которого соединен со вторым входом четвертога блока элементов И, выход которого соединен с первым входом первого блока элементов ИЛИ, второй вход которого соединен с выходом второго блока элементов И, выход первого блока элементов ИЛИ соединен со вторым входом сумматора, выход третьего элемента И соединен с входом триггера, са вторым входом шестого блока элементов И, с управляющим входом третьего регистра и с первым входом первого элемента ИЛИ, выход второго блока элементов ИЛИ соединен с информационным входом четвертого регистра, выход четвертого регистра соединен с первым входом восьмого блока элементов И, выход которого является первым информационным выходом устройства, выход третьего элемента ИЛИ соединен со вторым входом первого элемента ИЛИ со вторым входом первого блока элементов И и с первым информациан)ным входом третьего регистра, Втарои информационный Вход которого .лединен с первым входом блока памяти, стретьим входом первого элемента ИЛИи с выходом четвертого элемента И,выход второго элемента И соединен счетвертым входом первого элементаИЛИ и со вторым входом пятого блокаэлементов И, выход которого соединенсо вторым входом блока памяти и спервым входом второго блока элементов ИЛИ, второй вход которого соединен с выходом блока памяти, выходпервого блока элементов И соединенс третьим входом второго блока элементов ИЛИ, четвертый вход второгоблока элементов ИЛИ соединен с вы"ходом шестого блока элементов И, выход третьего регистра соединен с пер 8434 10вым входом девятого блока элементовИ, второй вход которого соединен спервым управляющим входом устройства и со вторым входом восьмого блокау элементов И, выход девятого блокаэлементов И, является вторым информационным выходом устройства, второйвход второго блока элементов И сое"динен со вторым управляющим входом30 устройства.Источники инФормации,принятые во внимание при экспертизе1. Авторское свидетельство СССРй 699523, кл. 6 06 Г 9/18, 1978,1 2. Авторское свидетельство СССРИ 696459, кл. С 06 Г 9/18, 19 У 6 (прототип).

СмотретьЗаявка

2916552, 24.04.1980

ВОЙСКОВАЯ ЧАСТЬ 03444

ВЛАСЕНКО ПЕТР ИВАНОВИЧ, ТУРЛАКОВ ПЕТР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/48

Метки: прерыванием, программ

Опубликовано: 15.01.1982

Код ссылки

<a href="https://patents.su/6-898434-ustrojjstvo-upravleniya-preryvaniem-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления прерыванием программ</a>

Предыдущий патент: Устройство управления обслуживанием запросов

Следующий патент: Устройство для обслуживания запросов

Случайный патент: Способ отверждения новолачных фенолальде-